#### LT3029

#### Dual 500mA/500mA Low Dropout, Low Noise, Micropower Linear Regulator DESCRIPTION

The LT®3029 is a dual, micropower, low noise, low drop-

out linear regulator. The device operates either with a

common input supply or independent input supplies for

each channel, over an input voltage range of 1.8V to 20V.

Each output supplies up to 500mA of output current with

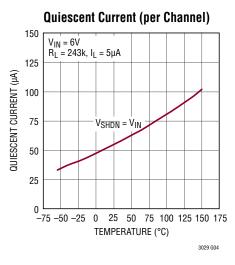

a typical dropout voltage of 300mV. Quiescent current is

well controlled in dropout. With an external 10nF bypass

capacitor, output noise is only 20µV<sub>RMS</sub> over a 10Hz to

100kHz bandwidth. Designed for use in battery-powered

systems, the low 55µA quiescent current per channel

makes it an ideal choice. In shutdown, guiescent current

drops to less than 1µA. Shutdown control is independent

for each channel, allowing for flexible power management.

The LT3029 optimizes stability and transient response with

low ESR ceramic output capacitors, requiring a minimum

of only 3.3µF. The regulator does not require the addition

Internal circuitry provides reverse-battery protection, reverse-current protection, current limiting with foldback and thermal shutdown. The device is available as an

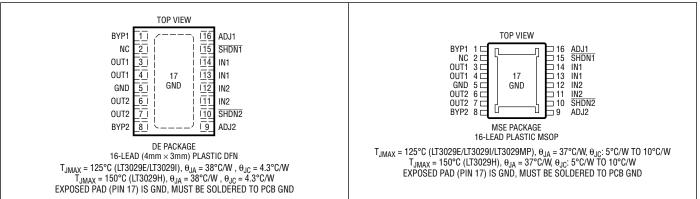

adjustable output voltage device with a 1.215V reference voltage. The LT3029 is offered in the thermally enhanced

16-lead MSOP and 16-lead, low profile  $(4mm \times 3mm \times$

of ESR, as is common with other regulators.

0.75mm) DFN packages.

#### FEATURES

- Output Current: 500mA per Channel

- Low Dropout Voltage: 300mV

- Low Noise: 20µV<sub>RMS</sub> (10Hz to 100kHz)

- Low Quiescent Current: 55µA per Channel

- Wide Input Voltage Range: 1.8V to 20V (Common or Independent Input Supply)

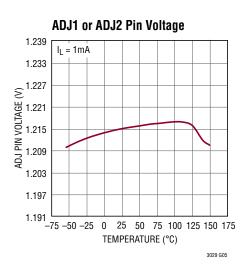

- Adjustable Output: 1.215V Reference Voltage

- Very Low Quiescent Current in Shutdown: <1µA per Channel

- Stable with 3.3µF Minimum Output Capacitor

- Stable with Ceramic, Tantalum or Aluminum Electrolytic Capacitors

- Reverse-Battery and Reverse Output-to-Input Protection

- Current Limit with Foldback and Thermal Shutdown

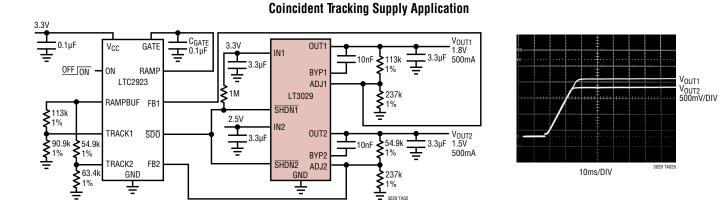

- Tracking/Sequencing Capability: Compatible with LTC292X Power Supply Tracking ICs

- Thermally Enhanced 16-Lead MSOP and 16-Lead (4mm × 3mm) DFN Packages

#### **APPLICATIONS**

- General Purpose Linear Regulator

- Battery-Powered Systems

- Microprocessor Core/Logic Supplies

- Post Regulator for Switching Supplies

- Tracking/Sequencing Power Supplies

## **Δ**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and ThinSOT is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

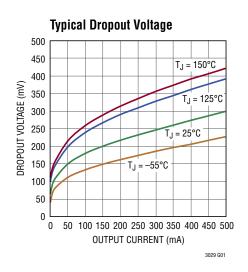

#### **Dropout Voltage vs Load Current** TYPICAL APPLICATION 400 2.5V<sub>IN</sub> to 1.5V/1.8V Application T<sub>J</sub> = 25°C 350 V<sub>OUT1</sub> OUT IN1 1 8V 300 DROPOUT VOLTAGE (mV) LT3029 **≸**113k 500mA 3.3µF IN2 BYP' 1% 250 ADJ1 200 237k SHDN1 1% 150 VOUT2 SHDN2 OUT2 100 500mA 54.9k BYP2 50 ADJ2 0 237k GND 50 100 150 200 250 300 350 400 450 500 0 OUTPUT CUBBENT (mA) 3029 TA01b

# Downloaded from Arrow.com.

#### ABSOLUTE MAXIMUM RATINGS (Note 1)

| IN1, IN2 Pin Voltage                 | ±22V       |

|--------------------------------------|------------|

| OUT1, OUT2 Pin Voltage               |            |

| Input-to-Output Differential Voltage | ±22V       |

| ADJ1, ADJ2 Pin Voltage               | ±9V        |

| BYP1, BYP2 Pin Voltage               | ±0.6V      |

| SHDN1, SHDN2 Pin Voltage             | ±22V       |

| Output Short-Circuit Duration        | Indefinite |

| Operating Junction Temperature (Not  | es 2, 12)      |

|--------------------------------------|----------------|

| LT3029E                              | 40°C to 125°C  |

| LT3029I                              | 40°C to 125°C  |

| LT3029H                              | –40°C to 150°C |

| LT3029MP                             | –55°C to 125°C |

| Storage Temperature Range            | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | )              |

| (MSOP Only)                          | 300°C          |

#### PIN CONFIGURATION

## **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|-------------------|---------------|---------------------------------|-------------------|

| LT3029EDE#PBF     | LT3029EDE#TRPBF   | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3029IDE#PBF     | LT3029IDE#TRPBF   | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3029HDE#PBF     | LT3029HDE#TRPBF   | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 150°C    |

| LT3029EMSE#PBF    | LT3029EMSE#TRPBF  | 3029          | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3029IMSE#PBF    | LT3029IMSE#TRPBF  | 3029          | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3029HMSE#PBF    | LT3029HMSE#TRPBF  | 3029          | 16-Lead Plastic MSOP            | -40°C to 150°C    |

| LT3029MPMSE#PBF   | LT3029MPMSE#TRPBF | 3029          | 16-Lead Plastic MSOP            | -55°C to 125°C    |

| LEAD BASED FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

| LT3029EDE         | LT3029EDE#TR      | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3029IDE         | LT3029IDE#TR      | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LT3029HDE         | LT3029HDE#TR      | 3029          | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 150°C    |

| LT3029EMSE        | LT3029EMSE#TR     | 3029          | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3029IMSE        | LT3029IMSE#TR     | 3029          | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LT3029HMSE        | LT3029HMSE#TR     | 3029          | 16-Lead Plastic MSOP            | -40°C to 150°C    |

| LT3029MPMSE       | LT3029MPMSE#TR    | 3029          | 16-Lead Plastic MSOP            | -55°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2)

| PARAMETER                                                              | CONDITIONS                                                                                                                                                                                                                      |   | MIN                     | ТҮР                               | MAX                               | UNITS                      |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------|-----------------------------------|-----------------------------------|----------------------------|

| Minimum Input Voltage (Notes 3, 11)                                    | I <sub>LOAD</sub> = 500mA                                                                                                                                                                                                       |   |                         | 1.8                               | 2.3                               | V                          |

| ADJ1, ADJ2 Pin Voltage (Notes 3, 4, 9)                                 | $V_{IN} = 2V, I_{LOAD} = 1mA$<br>2.3V < $V_{IN} < 20V, 1mA < I_{LOAD} < 500mA$ (E, I, MP)<br>2.3V < $V_{IN} < 20V, 1mA < I_{LOAD} < 500mA$ (H)                                                                                  | • | 1.203<br>1.191<br>1.173 | 1.215<br>1.215<br>1.215           | 1.227<br>1.239<br>1.239           | V<br>V<br>V                |

| Line Regulation (Note 3)                                               | $\Delta V_{IN} = 2V$ to 20V, $I_{LOAD} = 1$ mA                                                                                                                                                                                  | • |                         | 0.5                               | 5                                 | mV                         |

| Load Regulation (Note 3)                                               | $ \begin{array}{l} V_{IN} = 2.3V, \ \Delta I_{LOAD} = 1 mA \ to \ 500 mA \\ V_{IN} = 2.3V, \ \Delta I_{LOAD} = 1 mA \ to \ 500 mA \ (E, \ I, \ MP) \\ V_{IN} = 2.3V, \ \Delta I_{LOAD} = 1 mA \ to \ 500 mA \ (H) \end{array} $ | • |                         | 2.5                               | 6<br>15<br>32                     | mV<br>mV<br>mV             |

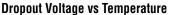

| Dropout Voltage<br>Vin = Vout(nominal)                                 | I <sub>LOAD</sub> = 10mA<br>I <sub>LOAD</sub> = 10mA                                                                                                                                                                            | • |                         | 0.11                              | 0.18<br>0.25                      | V<br>V                     |

| (Notes 5, 6, 11)                                                       | I <sub>LOAD</sub> = 50mA<br>I <sub>LOAD</sub> = 50mA                                                                                                                                                                            | • |                         | 0.16                              | 0.22<br>0.31                      | V<br>V                     |

|                                                                        | I <sub>LOAD</sub> = 100mA<br>I <sub>LOAD</sub> = 100mA                                                                                                                                                                          | • |                         | 0.2                               | 0.25<br>0.34                      | V<br>V                     |

|                                                                        | $I_{LOAD} = 500$ mA<br>$I_{LOAD} = 500$ mA                                                                                                                                                                                      | • |                         | 0.3                               | 0.36<br>0.46                      | V<br>V                     |

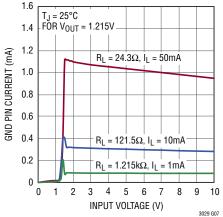

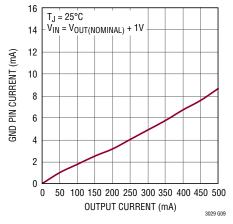

| GND Pin Current (per Channel) $V_{IN} = V_{OUT(NOMINAL)}$ (Notes 5, 7) | $I_{LOAD} = 0mA$ $I_{LOAD} = 1mA$ $I_{LOAD} = 50mA$ $I_{LOAD} = 100mA$ $I_{LOAD} = 250mA$ $I_{LOAD} = 500mA$                                                                                                                    |   |                         | 55<br>90<br>1.1<br>2<br>4.3<br>10 | 150<br>250<br>2<br>3.5<br>8<br>16 | μΑ<br>μΑ<br>mA<br>mA<br>mA |

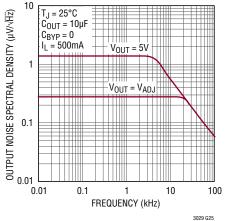

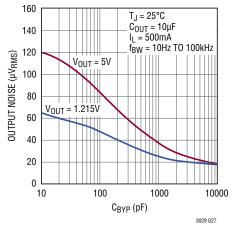

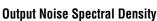

| Output Voltage Noise                                                   | $C_{OUT} = 10\mu$ F, $C_{BYP} = 10$ nF, $I_{LOAD} = 500$ mA, BW = 10Hz to 100kHz                                                                                                                                                |   |                         | 20                                |                                   | µV <sub>RMS</sub>          |

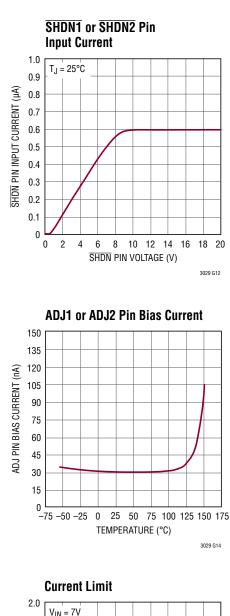

| ADJ1/ADJ2 Pin Bias Current                                             | ADJ1, ADJ2 (Notes 3, 8)                                                                                                                                                                                                         |   |                         | 30                                | 100                               | nA                         |

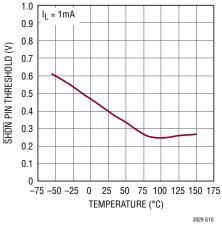

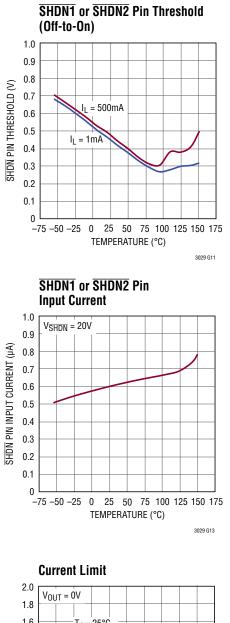

| Shutdown Threshold                                                     | V <sub>OUT</sub> = Off to On<br>V <sub>OUT</sub> = On to Off                                                                                                                                                                    | • | 0.20                    | 0.45<br>0.40                      | 1.1                               | V<br>V                     |

| SHDN1/SHDN2 Pin Current (Note 10)                                      | $V_{\overline{SHDN1}}, V_{\overline{SHDN2}} = 0V$<br>$V_{\overline{SHDN1}}, V_{\overline{SHDN2}} = 20V$                                                                                                                         | • |                         | 0<br>0.6                          | 0.5<br>3                          | μA<br>μA                   |

| Quiescent Current in Shutdown (per Channel)                            | $V_{IN} = 6V$ , $V_{\overline{SHDN1}} = 0V$ , $V_{\overline{SHDN2}} = 0V$                                                                                                                                                       |   |                         | 0.01                              | 0.1                               | μA                         |

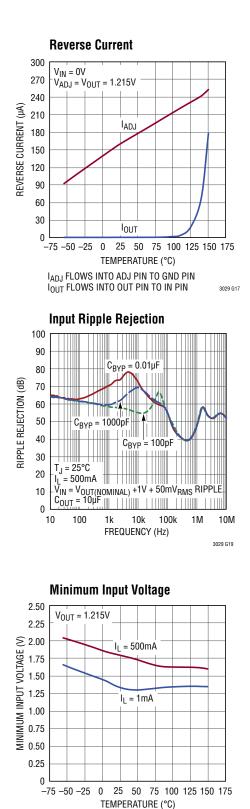

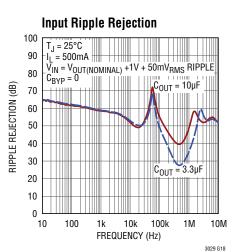

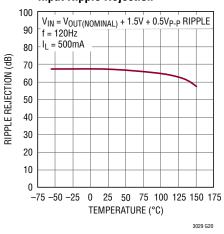

| Ripple Rejection                                                       | $V_{IN}$ = 2.715V (Avg), $V_{RIPPLE}$ = 0.5V <sub>P-P</sub> ,<br>f <sub>RIPPLE</sub> = 120Hz, I <sub>LOAD</sub> = 500mA                                                                                                         |   | 55                      | 67                                |                                   | dB                         |

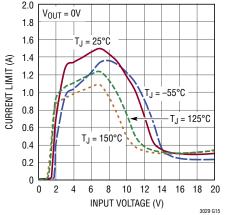

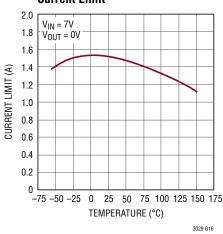

| Current Limit (Note 9)                                                 |                                                                                                                                                                                                                                 | • | 520                     | 1.5                               |                                   | A<br>mA                    |

| Input Reverse Leakage Current                                          | $V_{IN} = -20V, V_{OUT} = 0V$                                                                                                                                                                                                   | • |                         |                                   | 1                                 | mA                         |

| Reverse Output Current                                                 | V <sub>OUT</sub> = 1.215V, V <sub>IN</sub> = 0V                                                                                                                                                                                 |   |                         | 0.5                               | 10                                | μA                         |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT3029 is tested and specified under pulse load conditions such that  $T_J \approx T_A$ . The LT3029E is 100% tested at  $T_A = 25$ °C. Performance of the LT3029E over the full –40°C to 125°C operating junction temperature range is assured by design, characterization and correlation with statistical process controls. The LT3029I is guaranteed over the full –40°C to 125°C operating junction temperature range. The LT3029MP is 100% tested and guaranteed over the –55°C to 125°C operating junction temperature range. The LT3029H is tested at 150°C operating junction temperature. High junction temperatures degrade operating lifetimes. Operating lifetime is derated at junction temperatures greater than 125°C.

**Note 3:** The LT3029 is tested and specified for these conditions with the ADJ1/ADJ2 pin connected to the corresponding OUT1/OUT2 pin.

**Note 4:** Maximum junction temperature limits operating conditions. The regulated output voltage specification does not apply for all possible combinations of input voltage and output current. When operating at maximum input voltage, limit the output current range. When operating at maximum output current, limit the input voltage range.

**Note 5:** To satisfy minimum input voltage requirements, the LT3029 is tested and specified for these conditions with an external resistor divider (two 243k resistors) for an output voltage of 2.437V. The external resistor divider adds  $5\mu$ A of DC load on the output.

**Note 6:** Dropout voltage is the minimum input to output voltage differential needed to maintain regulation at a specified output current. In dropout, the output voltage equals:  $V_{IN} - V_{DROPOUT}$ .

For more information www.linear.com/LT3029

## **ELECTRICAL CHARACTERISTICS**

**Note 7:** GND pin current is tested with  $V_{IN} = 2.437V$  and a current source load. This means the device is tested while operating in its dropout region or at the minimum input voltage specification. This is the worst-case GND pin current. The GND pin current decreases slightly at higher input voltages. Total GND pin current equals the sum of output 1 and output 2 GND pin currents.

Note 8: ADJ1/ADJ2 pin bias current flows into the pin.

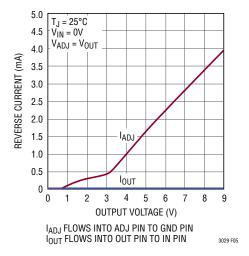

**Note 9:** The LT3029 contains current limit foldback circuitry. See the Typical Performance Characteristics for current limit as a function of the  $V_{IN} - V_{OUT}$  differential voltage.

Note 10: SHDN1/SHDN2 pin current flows into the pin.

**Note 11:** The LT3029 minimum input voltage specification limits dropout voltage under some output voltage/load conditions. See the curve of Minimum Input Voltage in the Typical Performance Characteristics.

**Note 12:** The LT3029 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature exceeds the maximum operating junction temperature when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

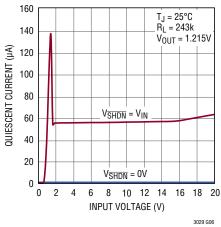

#### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_J = 25^{\circ}C$ , unless otherwise noted.

500 o = TEST POINTS GUARANTEED DROPOUT VOLTAGE (mV) 450 TJ = 150°C 400 350 TJ = 25°C 300 250 200 150 100 50 0 50 100 150 200 250 300 350 400 450 500 0 OUTPUT CURRENT (mA) 3029 G02

#### Guaranteed Dropout Voltage

GND Pin Current (per Channel)

Quiescent Current (per Channel)

**GND Pin Current (per Channel)** 16 T<sub>J</sub> = 25°C FOR V<sub>OUT</sub> = 1.215V 14 12 **GND PIN CURRENT (mA)** 10  $R_L = 2.43\Omega, I_L = 500 \text{mA}$ 8 6  $R_L = 4.05\Omega, I_L = 300 \text{mA}$ 4 Rı = 12.15Ω, IL = 100mA 2 0 0 2 3 4 5 6 7 8 1 9 10 INPUT VOLTAGE (V) 3029 G08

SHDN1 or SHDN2 Pin Threshold

(On-to-Off)

IL\_= 1mA

Downloaded from Arrow.com.

**Input Ripple Rejection**

Downloaded from Arrow.com.

3029 G21

**Output Noise Spectral Density**

RMS Output Noise vs Bypass Capacitor

–75 –50 –25 0 25 50 75 100 125 150 175 TEMPERATURE (°C)

3029 G24

Load Regulation

$\Delta I_L = 1$ mA TO 500mA

0 -2

-4

-6 -8

-10 -12 -14 -16

-18

-20

LOAD REGULATION (mV)

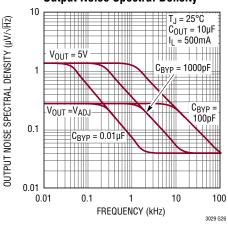

RMS Output Noise vs Load Current

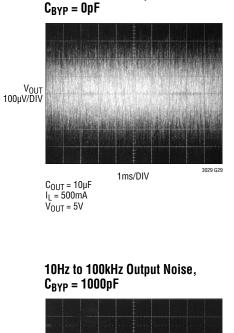

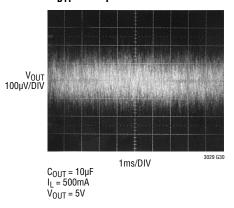

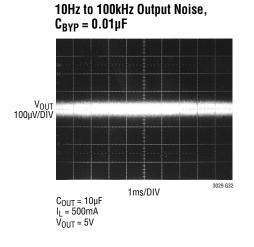

10Hz to 100kHz Output Noise,

V<sub>OUT</sub> 100μV/DIV 100μV/DIV 100μV/DIV

$\begin{array}{l} C_{OUT} = 10 \mu F \\ I_L = 500 m A \\ V_{OUT} = 5 V \end{array}$

10Hz to 100kHz Output Noise,  $C_{BYP} = 100pF$

9

#### PIN FUNCTIONS

**BYP1/BYP2 (Pin 1/Pin 8):** Bypass. Use the BYP1/BYP2 pins to bypass the reference of the LT3029 regulator and achieve low output noise performance. Internal circuitry clamps the BYP1/BYP2 pins to  $\pm 0.6V$  (one V<sub>BE</sub>) from ground. A small capacitor from the corresponding output to this pin bypasses the reference to lower the output voltage noise. Using a maximum value of 10nF reduces the output voltage noise to a typical  $20\mu V_{RMS}$  over a 10Hz to 100kHz bandwidth. If not used, this pin must be left unconnected.

NC (Pin 2): No Connect. This pin is not connected to any internal circuitry. It may be floated, tied to  $V_{IN}$  or tied to GND.

**OUT1/OUT2 (Pins 3, 4/Pins 6, 7):** Output. The outputs supply power to the loads. A minimum 3.3µF output capacitor prevents oscillations on each output. Applications with large output load transients require larger values of output capacitance to limit peak voltage transients. See the Applications Information section for more on output capacitance and reverse output characteristics.

**GND (Pin 5, 17):** Ground. The exposed pad (Pin 17) of the DFN and MSOP packages is an electrical connection to GND. To ensure proper electrical and thermal performance, solder Pin 17 to the PCB ground and tie directly to Pin 5. Connect the bottom of the output voltage setting resistor divider directly to GND (Pin 5) for optimum load regulation performance.

**IN1/IN2 (Pins 13, 14/Pins 11, 12):** Inputs. The IN1/IN2 pins supply power to each channel. The LT3029 requires a bypass capacitor at the IN1/IN2 pins if located more than six inches away from the main input filter capacitor. Include a bypass capacitor in battery-powered circuits,

as a battery's output impedance rises with frequency. A bypass capacitor in the range of  $1\mu$ F to  $10\mu$ F suffices. The LT3029's design withstands reverse voltages on the IN pins with respect to ground and the OUT pins. In the case of a reversed input, which occurs if a battery is plugged in backwards, the LT3029 acts as if a diode is in series with its input. No reverse current flows into the LT3029 and no reverse voltage appears at the load. The device protects itself and the load.

**SHDN1**/**SHDN2** (Pin 15/Pin 10): Shutdown. Pulling the SHDN1 or SHDN2 pin low puts its corresponding LT3029 channel into a low power state and turns its output off. The SHDN1 and SHDN2 pins are completely independent of each other, and each SHDN pin only affects operation on its corresponding channel. Drive the SHDN1 and SHDN2 pins with either logic or an open collector/drain with pull-up resistors. The resistors supply the pull-up current to the open collectors/drains and the SHDN1 or SHDN2 current, typically less than 1 $\mu$ A. If unused, connect the SHDN1 and SHDN2 to their corresponding IN pins. Each channel will be in its low power shutdown state if its corresponding SHDN pin is not connected.

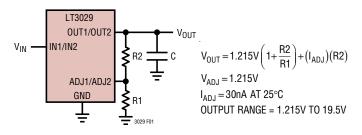

**ADJ1/ADJ2: (Pin 16/Pin 9)** Adjust Pin. These are the error amplifier inputs. These pins are internally clamped to ±9V. A typical input bias current of 30nA flows into the pins (see curve of ADJ1/ADJ2 Pin Bias Current vs Temperature in the Typical Performance Characteristics section). The ADJ1 and ADJ2 pin voltage is 1.215V referenced to ground and the output voltage range is 1.215V to 19.5V.

The LT3029 is a dual 500mA/500mA low dropout regulator with independent inputs, micropower quiescent current and shutdown. The device supplies up to 500mA from each channel's output at a typical dropout voltage of 300mV. The two regulators share a common GND pin and are thermally coupled. However, the two inputs and outputs of the LT3029 operate independently. Each channel can be shut down independently, but a thermal shutdown fault on either channel shuts off the output on both channels. The addition of a 10nF reference bypass capacitor lowers output voltage noise to  $20\mu V_{BMS}$  over a 10Hz to 100kHz bandwidth. Additionally, the reference bypass capacitor improves transient response of the regulator, lowering the settling time for transient load conditions. The low operating quiescent current (55µA per channel) drops to less than 1µA in shutdown. In addition to the low quiescent current, the LT3029 regulator incorporates several protection features that make it ideal for use in batterypowered systems. Most importantly, the device protects itself against reverse input voltages. Current limiting with foldback necessitates a minimum load current of 20µA for input/output voltage differentials of more than 10V to keep the output regulated.

#### Adjustable Operation

Each of the LT3029's channels has an output voltage range of 1.215V to 19.5V. Figure 1 illustrates that output voltage is set by the ratio of two external resistors. The device regulates the output to maintain the corresponding ADJ pin voltage at 1.215V referenced to ground. R1's current equals 1.215V/R1. R2's current equals R1's current plus the ADJ pin bias current. The ADJ pin bias current, 30nA at 25°C, flows through R2 into the ADJ pin. Use the formula in Figure 1 to calculate output voltage. Linear Technology recommends that the value of R1 be less than 243k to minimize errors in the output voltage due to the ADJ pin bias current. In shutdown, the output turns off and the divider current is zero. Curves of ADJ Pin Voltage vs Temperature and ADJ Pin Bias Current vs Temperature appear in the Typical Performance Characteristics section.

Figure 1. Adjustable Operation

Linear Technology tests and specifies each LT3029 channel with its ADJ pin tied to the corresponding OUT pin for a 1.215V output voltage. Specifications for output voltages greater than 1.215V are proportional to the ratio of desired output voltage to 1.215V:

|   | Vol | JT |

|---|-----|----|

| 1 | .21 | 5V |

For example, load regulation on either output for an output current change of 1mA to 500mA is typically –2.5mV at  $V_{OUT}$  = 1.215V. At  $V_{OUT}$  = 2.5V, load regulation is:

$$\frac{2.5V}{1.215V} \bullet (-2.5mV) = -5.14mV$$

Table 1 shows 1% resistor divider values for some common output voltages with a resistor divider current of approximately  $5\mu A$ .

| Table 1. | <b>Output Voltage</b> | <b>Resistor Divider Values</b> |

|----------|-----------------------|--------------------------------|

|----------|-----------------------|--------------------------------|

| V <sub>OUT</sub><br>(V) | R1<br>(k) | R2<br>(k) |

|-------------------------|-----------|-----------|

| 1.5                     | 237       | 54.9      |

| 1.8                     | 237       | 113       |

| 2.5                     | 243       | 255       |

| 3                       | 232       | 340       |

| 3.3                     | 210       | 357       |

| 5                       | 200       | 619       |

#### Bypass Capacitance and Low Noise Performance

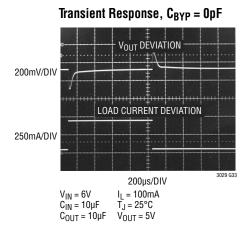

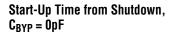

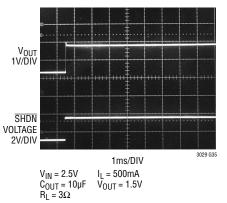

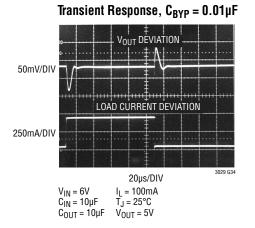

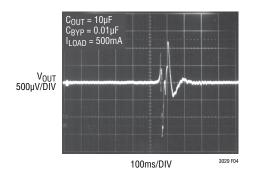

Using a bypass capacitor connected between a channel's BYP pin and its corresponding OUT pin significantly lowers LT3029 output voltage noise, but is not required in all applications. Linear Technology recommends a good guality low leakage capacitor. This capacitor bypasses the regulator's reference, providing a low frequency noise pole. A 10nF bypass capacitor introduces a noise pole that decreases output voltage noise to as low as 20µV<sub>BMS</sub>. Using a bypass capacitor provides the added benefit of improving transient response. With no bypass capacitor, and a 10µF output capacitor, a 100mA to 500mA load step settles to within 1% of its final value in approximately 100µs. With the addition of a 10nF bypass capacitor and evaluating the same load step, output voltage excursion stays within 1% (see Transient Response in the Typical Performance Characteristics section). Using a bypass capacitor makes regulator start-up time proportional to the value of the bypass capacitor. For example, a 10nF bypass capacitor and 10µF output capacitor slow start-up time to 7ms.

#### **Output Capacitance and Transient Response**

The LT3029 design is stable with a wide range of output capacitors. The ESR of the output capacitor affects stability, most notably with small capacitors. Linear Technology recommends a minimum output capacitor of  $3.3\mu$ F with an ESR of  $3\Omega$ , or less, to prevent oscillations. The LT3029 is a micropower device, and output transient response is a function of output capacitance. Larger values of output capacitance decrease the peak deviations and provide improved transient response for larger load current changes.

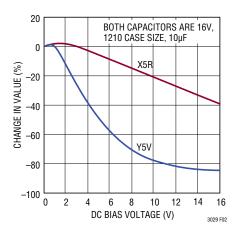

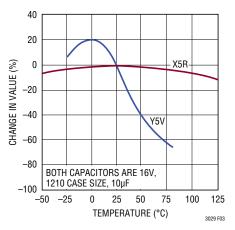

Ceramic capacitors require extra consideration. Manufacturers make ceramic capacitors with a variety of dielectrics, each with different behavior across temperature and applied voltage. The most common dielectrics specify the EIA temperature characteristic codes of Z5U, Y5V, X5R and X7R. Z5U and Y5V dielectrics provide high C-V products in a small package at low cost, but exhibit strong voltage and temperature coefficients, as shown in Figures 2 and 3. When used with a 5V regulator, a 16V 10 $\mu$ F Y5V capacitor can exhibit an effective value as low as 1 $\mu$ F to 2 $\mu$ F for the applied DC bias voltage and over the operating temperature range. X5R and X7R dielectrics result in more stable characteristics and are more suitable for use as the output capacitor. The X7R type has better stability across temperature, while the X5R is less expensive and is available in higher values.

Figure 2. Ceramic Capacitor DC Bias Characteristics

Figure 3. Ceramic Capacitor Temperature Characteristics

Exercise care even when using X5R and X7R capacitors; the X5R and X7R codes only specify operating temperature range and maximum capacitance change over temperature. Capacitance change due to DC bias (voltage coefficient) with X5R and X7R capacitors is better than with Y5V and Z5U capacitors, but can still be significant enough to drop capacitor values below appropriate levels. Capacitor DC bias characteristics tend to improve as case size increases. Linear Technology recommends verifying expected versus actual capacitance values at operating voltage in situ for an application.

Voltage and temperature coefficients are not the only sources of problems. Some ceramic capacitors have a piezoelectric response. A piezoelectric device generates voltage across its terminals due to mechanical stress, similar to the way a piezoelectric accelerometer or microphone works. For a ceramic capacitor, the stress can be induced by vibrations in the system or thermal transients. The resulting voltages produced can cause appreciable amounts of noise, especially when a ceramic capacitor is used for noise bypassing. A ceramic capacitor produced Figure 4's trace in response to light tapping from a pencil. Similar vibration induced behavior can masquerade as increased output voltage noise.

Figure 4. Noise Resulting from Tapping on a Ceramic Capacitor

#### **Thermal Considerations**

The LT3029's power handling capability limits the maximum rated junction temperature (125°C, LT3029E/LT3029I/LT3029MP or 150°C, LT3029H). Two components comprise the power dissipated by each channel:

- 1. Output current multiplied by the input/output voltage differential:  $(I_{OUT})(V_{IN} V_{OUT})$ , and

- 2. GND pin current multiplied by the input voltage: (I\_{GND}) (V\_{IN}).

Ground pin current is found by examining the GND Pin Current curves in the Typical Performance Characteristics section.

Power dissipation for each channel equals the sum of the two components listed above. Total power dissipation for the LT3029 equals the sum of the power dissipated by each channel.

The LT3029's internal thermal shutdown circuitry protects both channels of the device if either channel experiences an overload or fault condition. Activation of the thermal shutdown circuitry turns both channels off. If the overload or fault condition is removed, both outputs are allowed to turn back on. For continuous normal conditions, do not exceed the maximum junction temperature rating of (125°C, LT3029E/LT3029I/LT3029MP or 150°C, LT3029H). Carefully consider all sources of thermal resistance from junction-to-ambient, including additional heat sources mounted in proximity to the LT3029. For surface mount devices, use the heat spreading capabilities of the PC board and its copper traces to accomplish heat sinking. Copper board stiffeners and plated through-holes can also spread the heat generated by power devices.

The following tables list thermal resistance as a function of copper area in a fixed board size. All measurements were taken in still air on a four-layer FR-4 board with 1oz solid internal planes, and 2oz external trace planes with a total board thickness of 1.6mm. For further information on thermal resistance and using thermal information, refer to JEDEC standard JESD51, notably JESD51-12.

| Table 2. | DE | Package, | 16-Lead DFN |

|----------|----|----------|-------------|

|----------|----|----------|-------------|

| COPPE               | R AREA              |                     | THERMAL RESISTANCE    |

|---------------------|---------------------|---------------------|-----------------------|

| TOPSIDE*            | BACKSIDE            | BOARD AREA          | (JUNCTION-TO-AMBIENT) |

| 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 36°C/W                |

| 1000mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 37°C/W                |

| 225mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 38°C/W                |

| 100mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 40°C/W                |

\*Device is mounted on topside.

| Table 3. | MSE | Package, | 16-Lead MSOP |  |

|----------|-----|----------|--------------|--|

|----------|-----|----------|--------------|--|

| COPPE               | R AREA              |                     | THERMAL RESISTANCE    |  |

|---------------------|---------------------|---------------------|-----------------------|--|

| TOPSIDE*            | BACKSIDE            | BOARD AREA          | (JUNCTION-TO-AMBIENT) |  |

| 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 35°C/W                |  |

| 1000mm <sup>2</sup> | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 36°C/W                |  |

| 225mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 37°C/W                |  |

| 100mm <sup>2</sup>  | 2500mm <sup>2</sup> | 2500mm <sup>2</sup> | 39°C/W                |  |

\*Device is mounted on topside.

The junction-to-case thermal resistance ( $\theta_{JC}$ ), measured at the Exposed Pad on the back of the die, is 4.3°C/W for the DFN package, and 5°C/W to 10°C/W for the MSOP package.

#### **Calculating Junction Temperature**

Example: Channel 1's output voltage is set to 1.8V. Channel 2's output voltage is set to 1.5V. Each channel's input voltage is 2.5V. Each channel's output current range is 0mA to 500mA. The application has a maximum ambient temperature of 50°C. What is the LT3029's maximum junction temperature?

The power dissipated by each channel equals:

$I_{OUT(MAX)}(V_{IN} - V_{OUT}) + I_{GND}(V_{IN})$

where for each output:

$I_{OUT(MAX)} = 500 \text{mA}$  $V_{IN} = 2.5 \text{V}$

I<sub>GND</sub> at (I<sub>OUT</sub> = 500mA, V<sub>IN</sub> = 2.5V) = 8.5mA

So, for output 1:

P = 500mA (2.5V - 1.8V) + 8.5mA (2.5V) = 0.37W

For output 2:

P = 500mA (2.5V - 1.5V) + 8.5mA (2.5V) = 0.52W

The thermal resistance is in the range of 35°C/W to 40°C/W, depending on the copper area. So, the junction temperature rise above ambient temperature approximately equals:

(0.37W + 0.52W) 39°C/W = 34.7°C

The maximum junction temperature then equals the maximum ambient temperature plus the maximum junction temperature rise above ambient temperature, or:

$T_{JMAX} = 50^{\circ}C + 34.7^{\circ}C = 84.7^{\circ}C$

#### **Protection Features**

The LT3029 regulator incorporates several protection features that make it ideal for use in battery-powered circuits. In addition to the normal protection features associated with monolithic regulators, such as current limiting and thermal limiting, the device protects itself against reverse input voltages and reverse voltages from output to input. The two regulators have independent inputs, a common GND pin and are thermally coupled. However, the two channels of the LT3029 operate independently. Each channel's output can be shut down independently, and a fault condition on one output does not affect the other output electrically, unless the thermal shutdown circuitry is activated.

Current limit protection and thermal overload protection protect the device against current overload conditions at each output of the LT3029. For normal operation, do not allow the junction temperature to exceed 125°C (LT3029E/ LT3029I/LT3029MP) or 150°C (LT3029H). The typical thermal shutdown temperature threshold is 165°C and the circuitry incorporates approximately 5°C of hysteresis.

Each channel's input withstands reverse voltages of 22V. Current flow into the device is limited to less than 1mA (typically less than  $100\mu$ A) and no negative voltage appears at the respective channel's output. The device protects both itself and the load against batteries that are plugged in backwards.

The LT3029 incurs no damage if either channel's output is pulled below ground. If the input is left open-circuit, or grounded, the output can be pulled below ground by 22V. The output acts like an open circuit, and no current flows from the output. However, current flows in (but is limited by) the external resistor divider that sets the output voltage.

The LT3029 incurs no damage if either ADJ pin is pulled above or below ground by 9V. If the input is left open circuit or grounded, the ADJ pins perform like an open circuit down to -1.5V, and then like a 1.2k resistor down to -9V when pulled below ground. When pulled above ground, the ADJ pins perform like an open circuit up to 0.5V, then like a 5.7k resistor up to 3V, then like a 1.8k resistor up to 9V.

In situations where an ADJ pin connects to a resistor divider that would pull the pin above its 9V clamp voltage if the output is pulled high, the ADJ pin input current must be limited to less than 5mA. For example, assume a resistor divider sets the regulated output voltage to 1.5V, and the output is forced to 20V. The top resistor of the resistor divider must be chosen to limit the current into the ADJ pin to less than 5mA when the ADJ pin is at 9V. The 11V difference between the OUT and ADJ pins divided by the 5mA maximum current into the ADJ pin yields a minimum top resistor value of 2.2k.

In circuits where a backup battery is required, several different input/output conditions can occur. The output voltage may be held up while the input is either pulled to ground, pulled to some intermediate voltage or is left open-circuit. Current flow back into the output follows the curve shown in Figure 5.

Figure 5. Reverse Output Current

If either of the LT3029's IN pins is forced below its corresponding OUT pin, or the OUT pin is pulled above its corresponding IN pin, input current for that channel typically drops to less than  $2\mu$ A. This occurs if the IN pin is connected to a discharged (low voltage) battery, and either a backup battery or a second regulator circuit holds up the output. The state of that channel's SHDN pin has no effect on the reverse output current if the output is pulled above the input.

#### **Overload Recovery**

Like many IC power regulators, the LT3029 has safe operating area (SOA) protection. The safe area protection decreases current limit as input-to-output voltage increases and keeps the power transistor inside a safe operating region for all values of input-to-output voltage. The protective design provides some output current at all values of input-to-output voltage up to the specified maximum operational input voltage of 20V.

When power is first applied, as input voltage rises, the output follows the input, allowing the regulator to start-up into very heavy loads. During start-up, as the input voltage is rising, the input-to-output voltage differential is small, allowing the regulator to supply large output currents. With a high input voltage, an event can occur wherein removal of an output short will not allow the output to recover. The event occurs with a heavy output load when the input voltage is high and the output voltage is low. Common situations occur immediately after the removal of a short-circuit or if the shutdown pin is pulled high after the input voltage has already been turned on. The load line intersects the output current curve at two points creating two stable output operating points for the regulator. With this double intersection, the input power supply may need to be cycled down to zero and brought up again to make the output recover.

#### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

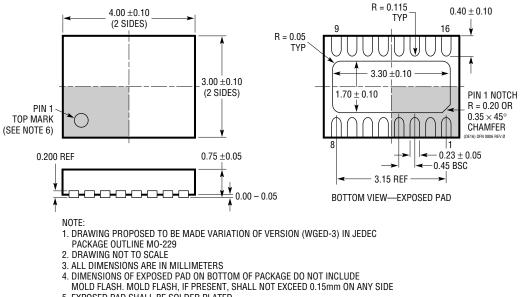

**DE Package** 16-Lead Plastic DFN (4mm  $\times$  3mm) (Reference LTC DWG # 05-08-1732 Rev Ø)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

- 5. EXPOSED PAD SHALL BE SOLDER PLATED 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE

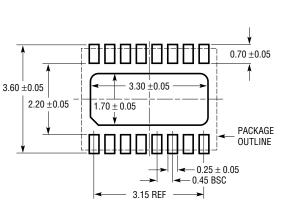

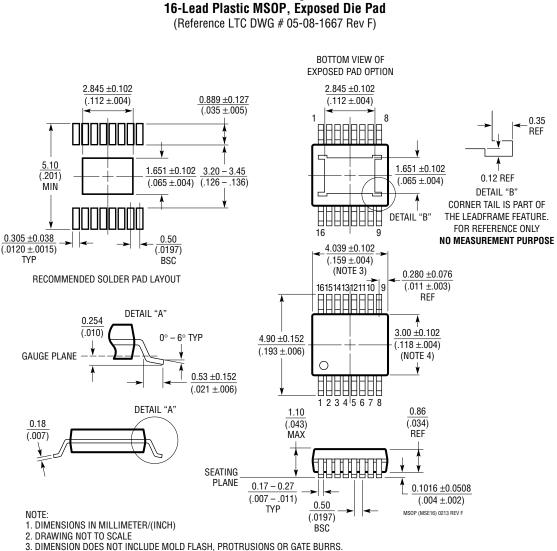

#### PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

**MSE Package**

- MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE

- 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

6. EXPOSED PAD DIMENSION DOES INCLUDE MOLD FLASH. MOLD FLASH ON E-PAD SHALL NOT EXCEED 0.254mm (.010") PER SIDE.

#### **REVISION HISTORY**

| REV | DATE | DESCRIPTION                                                 | PAGE NUMBER |

|-----|------|-------------------------------------------------------------|-------------|

| Α   | 3/11 | Added Overload Recovery section to Applications Information | 16          |

| В   | 4/14 | Added H-grade to the DFN package                            | 2           |

19

#### TYPICAL APPLICATION

## RELATED PARTS

| PART NUMBER         | DESCRIPTION                                                            | COMMENTS                                                                                                                                                                                                                                                                                                                           |

|---------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LT1761              | 100mA, Low Noise Micropower LDO                                        | V <sub>IN</sub> : 1.8V to 20V, V <sub>OUT(MIN)</sub> = 1.22V, V <sub>DO</sub> = 0.3V, I <sub>Q</sub> = 20µA, I <sub>SD</sub> < 1µA,<br>Low Noise < 20µV <sub>RMS</sub> , Stable with 1µF Ceramic Capacitors, ThinSOT <sup>™</sup> Package                                                                                          |

| LT1763              | 500mA, Low Noise Micropower LDO                                        | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.3V, $I_Q$ = 30µA, $I_{SD}$ < 1µA, Low Noise < 20µ $V_{RMS}$ , S8 and DFN Packages                                                                                                                                                                                     |

| LT1963/<br>LT1963A  | 1.5A, Low Noise, Fast Transient<br>Response LDOs                       | $V_{IN}$ : 2.1V to 20V, $V_{OUT(MIN)}$ = 1.21V, $V_{DO}$ = 0.34V, $I_Q$ = 1mA, $I_{SD}$ < 1µA, Low Noise: < 40µV <sub>RMS</sub> , "A" Version Stable with Ceramic Capacitors; DD, TO220-5, SOT223, S8 and TSSOP Packages                                                                                                           |

| LT1964              | 200mA, Low Noise Micropower,<br>Negative LDO                           | $V_{IN}$ : –1.9V to –20V, $V_{OUT(MIN)}$ = –1.22V, $V_{DO}$ = 0.34V, $I_Q$ = 30µA, $I_{SD}$ = 3µA, Low Noise: <30µV <sub>RMS</sub> , Stable with Ceramic Capacitors, ThinSOT Package                                                                                                                                               |

| LT1965              | 1.1A, Low Noise LDO                                                    | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.20V, $V_{DO}$ = 0.31V, $I_Q$ = 0.5mA, $I_{SD}$ < 1µA, Low Noise: <40µ $V_{RMS}$ , Stable with Ceramic Capacitors; 3mm $\times$ 3mm DFN, MS8E, DD-Pak and TO-220 Packages                                                                                                                |

| LT3020              | 100mA, Low Voltage VLDO                                                | $V_{IN}$ : 0.9V to 10V, $V_{OUT(MIN)}$ = 0.20V, $V_{DO}$ = 0.15V, $I_Q$ = 120µA, $I_{SD}$ < 3µA; 3mm $\times$ 3mm DFN and MS8 Packages                                                                                                                                                                                             |

| LT3021              | 500mA, Low Voltage VLDO                                                | $V_{IN}$ : 0.9V to 10V, $V_{OUT(MIN)}$ = 0.20V, $V_{DO}$ = 0.16V, $I_Q$ = 120µA, $I_{SD}$ < 3µA; 5mm $\times$ 5mm DFN and SO8 Packages                                                                                                                                                                                             |

| LT3023              | Dual 100mA, Low Noise,<br>Micropower LDO                               | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.30V, $I_Q$ = 40µA, $I_{SD}$ < 1µA; DFN and MS10E Packages                                                                                                                                                                                                             |

| LT3024              | Dual 100mA/500mA, Low Noise,<br>Micropower LDO                         | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.30V, $I_Q$ = 60µA, $I_{SD}$ < 1µA; DFN and TSSOP-16E Packages                                                                                                                                                                                                         |

| LTC3025             | 300mA, Low Voltage Micropower VLDO                                     | $V_{IN}$ : 0.9V to 5.5V, Low I_Q: 54µA, Low Noise < 80µV_{RMS}, 45mV Dropout Voltage; 2mm $\times$ 2mm 6-Lead DFN Package                                                                                                                                                                                                          |

| LTC3026             | 1.5A, Low Input Voltage VLDO                                           | $V_{IN}$ : 1.14V to 5.5V, Low $I_{\Omega}$ : 950µA, Low Noise < 110µV_{RMS}, 100mV Dropout Voltage; 10-Lead 3mm $\times$ 3mm DFN and MS10E Packages                                                                                                                                                                                |

| LT3027              | Dual 100mA, Low Noise, Micropower<br>LDO with Independent Inputs       | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.30V, $I_Q$ = 50µA, $I_{SD}$ < 1µA; DFN and MS10E Packages                                                                                                                                                                                                             |

| LT3028              | Dual 100mA/500mA, Low Noise, Micropower<br>LDO with Independent Inputs | $V_{IN}$ : 1.8V to 20V, $V_{OUT(MIN)}$ = 1.22V, $V_{DO}$ = 0.32V, $I_Q$ = 60µA, $I_{SD}$ < 1µA; DFN and TSSOP-16E Packages                                                                                                                                                                                                         |

| LT3080/<br>LT3080-1 | 1.1A, Parallelable, Low Noise LDO                                      | $V_{\text{IN}}$ : 1.2V to 36V, $V_{\text{OUT}}$ : 0V to 35.7V, Low Noise < 40µV_{\text{RMS}}, 300mV Dropout Voltage (2-Supply Operation), Current-Based Reference with 1-Resistor V_{OUT} Set, Directly Parallelable (No Op Amp Required), Stable with Ceramic Capacitors; TO-220, SOT-223, MS8E and 3mm $\times$ 3mm DFN Packages |