# Isolated, Loop-Powered Voltage-to-Current Converter

1**B**21

#### **FEATURES**

Wide input range: 0 V to 1 V up to 0 V to 10 V

High CMV isolation: 1500 V rms

Programmable output ranges: 4mA to 20mA

0 to 20 mA

Load resistance range: 0 to 1.35 k $\Omega$  maximum

**High accuracy**

Low offset tempco: ±300 nA/°C Low gain tempco: ±50 ppm/°C Low nonlinearity: ±0.02% High CMR: 90 dB minimum

Small package:  $0.7" \times 2.1" \times 0.35"$

Meets IEEE Standard 472: transient protection (SWC)

#### **APPLICATIONS**

Multichannel process control

DAC—current loop interface

Analog transmitters and controllers

Remote data acquisition systems

#### **GENERAL DESCRIPTION**

The 1B21 is an isolated voltage-to-current converter that incorporates a unique circuit design utilizing transformer-based isolation and automated surface-mount manufacturing technology. It provides an unbeatable combination of versatility and performance in a compact plastic package. Designed for industrial applications, it is especially suited for harsh environments with extremely high common-mode interference.

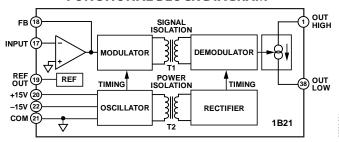

Functionally, the V/I converter consists of four basic sections: input conditioning, modulator, demodulator and current source (see Figure 1). The input is a resistor-programmable gain stage that accepts a 0 V to 1 V up to 0 V to 10 V voltage input. This maps into a 0 mA to 20 mA output or can be offset by 20% using the internal reference for 4 mA to 20 mA operation. The high level signal is modulated and passed across the barrier which provides complete input to output galvanic isolation of  $1500~\rm V$  rms continuous by the use of transformer-coupling techniques. Nonlinearity is an excellent  $\pm 0.05\%$  maximum.

Designed for multichannel applications, the 1B21 requires an external loop supply and can accept up to 30 V maximum. This

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

provides a loop supply compliance of 27V, which is sufficient to drive a 1.35 k $\Omega$  load resistance.

The 1B21 is fully specified over  $-25^{\circ}$ C to  $+85^{\circ}$ C and operates over the industrial ( $-40^{\circ}$ C to  $+85^{\circ}$ C) temperature range.

# **DESIGN FEATURES AND USER BENEFITS**

High CMV Isolation. The 1B21 features high input to output galvanic isolation to eliminate ground loops and offer protection against damage from transients and fault voltages. The isolation barrier will withstand continuous CMV of 1500V rms and meets the IEEE Standard for Transient Voltage Protection (Std. 472-SWC).

Small Size. The 1B21 package size  $(0.7^{\circ} \times 2.1^{\circ})$  DIP) makes it an excellent choice in multichannel systems for maximum channel density. The 0.35° height also facilitates applications with limited board clearance.

Ease of Use. Complete isolated voltage-to-current conversion with minimum external parts required to get a conditioned current signal. No external buffers or drivers are required.

# 1**B**21

# **TABLE OF CONTENTS**

| Features                          | J    |

|-----------------------------------|------|

| Applications                      | 1    |

| Functional Block Diagram          |      |

| General Description               |      |

| Design Features and User Benefits |      |

| Revision History                  |      |

| Specifications                    |      |

| Pin Configuration                 |      |

| · 111 Oo11116 u1 u11011           | •••• |

| Inside the 1B21          | 5 |

|--------------------------|---|

| Using the 1B21           | 5 |

| Applications Information | 7 |

| Output Protection        | 7 |

| Low Drift Input Network  | 7 |

| Multiloop Isoaltion      | 7 |

| Outline Dimensions       | 8 |

| Ordering Guide           | 8 |

# **REVISION HISTORY**

# 12/09—Rev. B to Rev. C

| Updated FormatU                                         | Jniversal |

|---------------------------------------------------------|-----------|

| Changes to Figure 1                                     | 1         |

| Changes to Table 1                                      | 3         |

| Changes to Inside the 1B21 Section, Figure 4, Using the |           |

| 1B21 Section, and Table 2                               |           |

| Changes to TC Considerations of External Resistors Sec  | ction 6   |

| Changes to Figure 8                                     | 7         |

| Added Ordering Guide Section                            | 8         |

6/91—Rev. A to Rev. B

# **SPECIFICATIONS**

Typical at +25°C and  $V_S = \pm 15$  V, unless otherwise noted.

Table 1.

| Table 1.  Parameter                                                  | Specification                |

|----------------------------------------------------------------------|------------------------------|

| INPUT SPECIFICATIONS                                                 | Specification                |

| Input Range                                                          | 0 V to + 10 V                |

| Full-Scale Input                                                     | +1 V min to +10 V max        |

| Input Bias Current                                                   | ±30 pA (±400 pA max)         |

| OUTPUT SPECIFICATIONS                                                | ±30 pA (±400 pA IIIax)       |

|                                                                      | 4 mA to 20 mA, 0 mA to 20 mA |

| Current Output Range<br>Load Compliance at $V_{LOOP} = 30 \text{ V}$ | 27 V min                     |

| Max Output Current @ Input Overload                                  | 25 mA                        |

| Output Noise, 100 Hz Bandwidth                                       |                              |

| NONLINEARITY (% of Span)                                             | 1 μA p-p                     |

| ISOLATION                                                            | ±0.02% (±0.05% max)          |

|                                                                      | 1500 V rms                   |

| CMP o COLL-                                                          |                              |

| CMR @ 60 Hz                                                          | 90 dB min                    |

| Transient Protection                                                 | IEEE-STD 472 (SWC)           |

| ACCURACY Wayne Lin Time to Retail Reviews as                         | Funia                        |

| Warm-Up Time to Rated Performance                                    | 5 min                        |

| Total Output Error @ +25°C (Untrimmed)                               | . 100 A                      |

| Offset $(V_{IN} = 0 V)^T$                                            | ±100 µA                      |

| Span $(V_{IN} = +10 \text{ V})$                                      | ±0.6% FSR                    |

| vs. Temperature (–25°C to +85°C)                                     | 1.200 A //C                  |

| Offset <sup>2</sup>                                                  | ±300 nA/°C                   |

| Span                                                                 | ±50 ppm/°C                   |

| REFERENCE OUTPUT                                                     |                              |

| Voltage                                                              | +6.225 V dc                  |

| Output Error                                                         | ±1.0% max                    |

| Temperature Coefficient                                              | ±15 ppm/°C typ               |

| DYNAMIC RESPONSE                                                     |                              |

| Settling Time to 0.1% of FS for 10 V Step                            | 9 ms                         |

| Small Signal Bandwidth                                               | 100 Hz                       |

| POWER SUPPLY                                                         |                              |

| Input Side                                                           |                              |

| Operating Voltage                                                    | ±15 V ±5%                    |

| Quiescent Current                                                    | 40. 4                        |

| +15 V Supply                                                         | 10 mA                        |

| –15 V Supply                                                         | 5 mA                         |

| Power Supply Rejection                                               | ±0.01% V                     |

| Loop Side                                                            |                              |

| Operating Voltage                                                    | +15 V to +30 V               |

| Maximum Current                                                      | 25 mA                        |

| ENVIRONMENTAL                                                        |                              |

| Temperature Range                                                    |                              |

| Rated Performance                                                    | -25°C to +85°C               |

| Operating                                                            | -40°C to +85°C               |

| Storage                                                              | -40°C to +85°C               |

| Relative Humidity, Noncondensing                                     | 0 to 95% @ +60°C             |

| CASE SIZE                                                            | 0.7" × 2.1" × 0.35"          |

|                                                                      | (17.8 × 53.3 × 8.9) mm       |

$<sup>^1</sup>$  For 0 mA to 20 mA mode. For 4 mA to 20 mA mode, an additional 60  $\mu\text{A}$  is contributed by the  $\pm1.0\%$  reference error on the 4 mA output.  $^2$  For a complete discussion of the temperature effects of the offset resistor and reference, refer to the Using the 1B21 section.

1**B**21

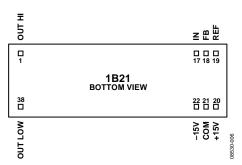

# PIN CONFIGURATION

Figure 2. Pin Configuration

# **INSIDE THE 1B21**

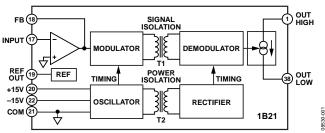

Referring to the functional block diagram (see Figure 3), the  $\pm 15$  V power inputs provide power to both the input side circuitry and the power oscillator. The 25 kHz power oscillator provides both the timing information for the signal modulator and drives transformer T2 for the output side power supplies. The secondary winding of T2 is full wave rectified and filtered to create the output side power.

Figure 3. 1B21 Functional Block Diagram

The input stage is configured as an inverting amplifier with three user-supplied resistors for gain, offset, and feedback. The conditioned signal is modulated to generate a square wave with a peak-to-peak amplitude proportional to  $V_{\rm IN}$ . The signal drives the signal transformer T1. An internal reference with a nominal output voltage of +6.225 V and tempco of ±15 ppm/°C is provided to develop a 4 mA offset for 4 mA to 20 mA current loop applications.

After passing through signal transformer T1, the amplitude modulated signal is demodulated and filtered by a single pole filter. Timing information for the output side is derived from the power transformer T2. The filtered output provides the control signal for the voltage-to-current converter stage. An external power supply is required in series with the load to complete the current loop.

# **USING THE 1B21**

# **Input Configurations**

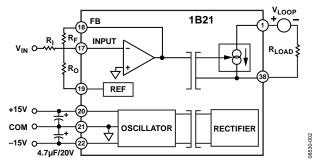

The 1B21 has been designed with a flexible input stage for a variety of input and output ranges. The basic interconnection for setting gain and offset is shown in Figure 4. The output of the internal amplifier is constrained to 0 to -5 V, which maps into 0 to 20 mA across the isolation barrier. Thus to create a 4 mA offset at the output, the input amplifier has to be offset by 1 V.

For example, for 0 to 20 mA operation, the transfer function for the input stage is

$$5/V_{IN} = R_F/R_I$$

and no offset resistor is needed. For 4 mA to 20 mA operation one gets

$$4/V_{IN} = R_F/R_I$$

This maps the input voltage into a 4 V span. To create a 1 V offset at the output of the internal amplifier (4 mA at the output of the 1B21) a current derived from the reference can be fed into the summing node. The offset resistor (for a 1 V output offset) is given by the equation:  $R_{\rm O}=6.225~R_{\rm F}.$  For most applications, it is recommended that  $R_{\rm F}$  be in the 25 k $\Omega$  ±20% range. Resistor values for typical input and output ranges are shown in Table 2.

Figure 4. Basic Interconnections

**Table 2. Resistor Values for Typical Ranges**

| Input Volts | Output mA | R <sub>I</sub> kΩ | $R_F k\Omega$ | R <sub>o</sub> kΩ |

|-------------|-----------|-------------------|---------------|-------------------|

| 0 to 5      | 0-20      | 25                | 25            | Open              |

| 0 to 10     | 0-20      | 50                | 25            | Open              |

| 0 to 5      | 4-20      | 25                | 20            | 124.3             |

| 0 to 10     | 4-20      | 50                | 20            | 124.3             |

| 1 to 5      | 4-20      | 25                | 25            | Open              |

#### **Adjustments**

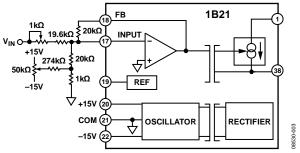

Figure 5 is an example of using potentiometers for trimming gain and offset for a 0 V to 5 V input and 0 V to 20 mA output. The network for offset adjustment keeps the resistors relatively small to minimize noise effects while giving a sensitivity of  $\pm 1\%$  of span. For more adjustment range, resistors smaller than 274 k can be used. Resistor values from Table 2 can be substituted for other input and output ranges.

In general, any bipolar voltage can be input to the 1B21 as long as it is offset to meet the 0 V to -5 V constraint of the modulator and the input signal range is 1 V minimum.

Figure 5. Offset and Span Adjustment

# 1**B**21

#### TC Considerations of External Resistors

The specifications for gain and offset temperature coefficient (TC) for the IB21 excluded the effects of external components. The total gain TC for the circuit in Figure 4 is

Gain

$$TC = 1B21$$

Gain  $TC + (Tracking TC of R_F and R_I)$

The offset TC is also affected by the thermal stability of the internal voltage reference and its contribution is

Ref

$$TC = (V_{REF})(R_F/R_O)(4 \text{ mA/V})(TC \text{ of } V_{REF} + Tracking TC \text{ of } R_F \text{ and } R_O)/1 \times 10^6$$

Total Offset  $TC = 1B21$  Offset  $TC + Ref TC$

Specifically using  $R_F$ ,  $R_I$  and  $R_O$  from Case 3 in Table 2, with absolute TCs of  $\pm 25$  ppm/°C

Gain

$$TC = 50 + (25 + 25) = 100 \text{ ppm/}^{\circ}\text{C}$$

Offset  $TC = 300 + (6.225 \text{ V})(20\text{k}/124.3 \text{ k})(4 \text{ mA/V})$

$(20 + 25 + 25)/1 \times 10^{6} = \pm 580 \text{ nA/}^{\circ}\text{C}$

Similarly, when using a resistor network with a tracking spec of  $\pm 5$  ppm/°C, the total gain TC is  $\pm 55$  ppm/°C and the total offset TC is  $\pm 400$  nA/°C.

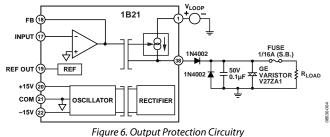

# APPLICATIONS INFORMATION OUTPUT PROTECTION

In many industrial applications, it may be necessary to protect the current output from accidental shorts to ac line voltages in addition to high common-mode voltages and short circuits to ground. The circuit show in Figure 6 can be used for this purpose. The maximum permissible load resistance will be lowered by the fuse resistance (typically 8  $\Omega$ ) when protection circuitry is utilized.

rigure o. Output riotection circu

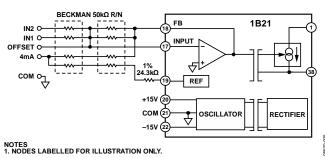

# **LOW DRIFT INPUT NETWORK**

Figure 7 shows a configuration suitable for applications where errors have to be minimized over a wide temperature range. A temperature tracking network such as a 50 k Beckman (PN 698-3R50KD) can be used to implement both offset and gain for either 0 mA to 20 mA or 4 mA to 20 mA current loops. For 0 V to 10 V signals either IN1 or IN2 can be used for input. For 0 V to 5 V signals, jumper In1 to In2. Similarly, for 4 mA to 20 mA operation the 4 mA node should be jumpered to OFFSET, while for 0 mA to 20 mA it should be tied to COM.

Figure 7. Low Tempco Resistor Network Configuration

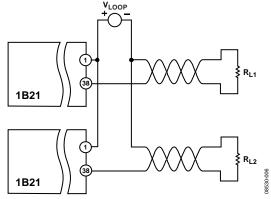

# **MULTILOOP ISOALTION**

Multiple 1B21s can be connected to a single loop supply in parallel as show in Figure 8. The amperage of the loop supply should be sufficient to drive all the loops at full-scale output.

Figure 8. Multiple 1B21s with Single Loop Supply

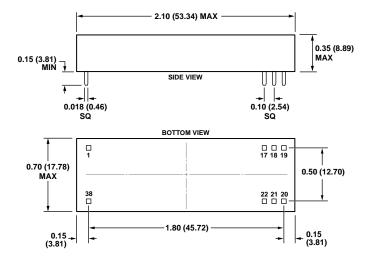

# **OUTLINE DIMENSIONS**

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 9. 1B21 DIP Package (1B21-N-08) [8-Lead Count with 38-Lead Spacing] Dimensions shown in inches and (millimeters)

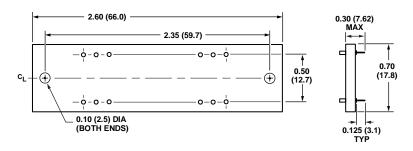

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 10. AC1060 Mating Socket Dimensions shown in inches and (millimeters)

# **ORDERING GUIDE**

| Model  | Temperature Range | Package Description         | Package Option |

|--------|-------------------|-----------------------------|----------------|

| 1B21AN | −25°C to +85°C    | 8-Lead Nonstandard 1B21 DIP | 1B21-N-08      |

©1991–2009 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

D08530-0-12/09(C)

www.analog.com