# **Phase Detector/Frequency Synthesizer**

## **Enhanced Product**

# **ADF4002-EP**

### **FEATURES**

400 MHz bandwidth 2.7 V to 3.3 V power supply Separate charge pump supply (V<sub>P</sub>) allows extended tuning voltage in 3 V systems Programmable charge pump currents 3-wire serial interface Analog and digital lock detect Hardware and software power-down mode 104 MHz phase frequency detector

### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard) Military temperature range: -55°C to +125°C **Controlled manufacturing baseline** One assembly/test site **One fabrication site Product change notification Qualification data available on request**

### **APPLICATIONS**

**Clock conditioning Clock generation IF LO generation**

### **GENERAL DESCRIPTION**

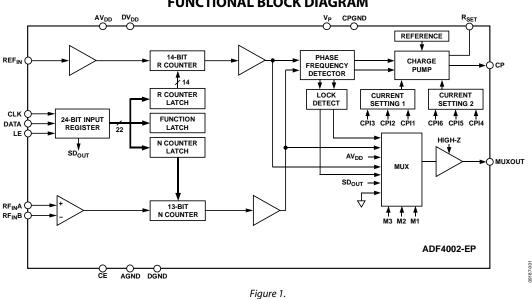

The ADF4002-EP frequency synthesizer is used to implement local oscillators in the upconversion and downconversion sections of wireless receivers and transmitters. It consists of a low noise digital phase frequency detector (PFD), a precision charge pump, a programmable reference divider, and a programmable N divider. The 14-bit reference counter (R counter) allows selectable REFIN frequencies at the PFD input. A complete phase-locked loop (PLL) can be implemented if the synthesizer is used with an external loop filter and voltage controlled oscillator (VCO). In addition, by programming R and N to 1, the part can be used as a standalone PFD and charge pump.

Additional application and technical information can be found in the ADF4002 data sheet.

### FUNCTIONAL BLOCK DIAGRAM

#### Rev. A

#### **Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2010-2018 Analog Devices, Inc. All rights reserved. **Technical Support** www.analog.com

## TABLE OF CONTENTS

| Features                  | 1 |

|---------------------------|---|

| Enhanced Product Features | 1 |

| Applications              | 1 |

| General Description       | 1 |

| Functional Block Diagram  | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Timing Characteristics    | 4 |

## **REVISION HISTORY**

### 9/2018—Rev. 0 to Rev. A

| Changes to Features Section             | 1 |

|-----------------------------------------|---|

| Added Enhanced Product Features Section | 1 |

| Changes to Figure 4 and Figure 5        |   |

| Changes to Ordering Guide               |   |

|                                         |   |

### 11/2010—Revision 0: Initial Version

| Absolute Maximum Ratings                    | 5 |

|---------------------------------------------|---|

| Thermal Characteristics                     | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

| Typical Performance Characteristics         | 7 |

| Outline Dimensions                          | 8 |

| Ordering Guide                              | 8 |

|                                             |   |

## **SPECIFICATIONS**

$AV_{DD} = DV_{DD} = 3 V \pm 10\%$ ,  $AV_{DD} \le V_P \le 5.5 V$ , AGND = DGND = CPGND = 0 V,  $R_{SET} = 5.1 k\Omega$ , dBm referred to 50  $\Omega$ ,  $T_A = T_{MAX}$  to  $T_{MIN}$ , unless otherwise noted. Operating temperature range is  $-55^{\circ}$ C to  $+125^{\circ}$ C.

| Table 1.                                                            |                      |      |           |        |                                                                      |

|---------------------------------------------------------------------|----------------------|------|-----------|--------|----------------------------------------------------------------------|

| Parameter                                                           | Min                  | Тур  | Max       | Unit   | Test Conditions/Comments                                             |

| RF CHARACTERISTICS                                                  |                      |      |           |        |                                                                      |

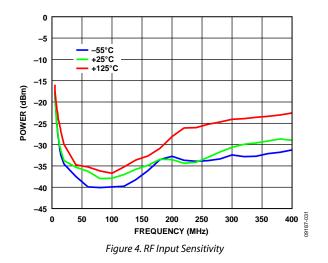

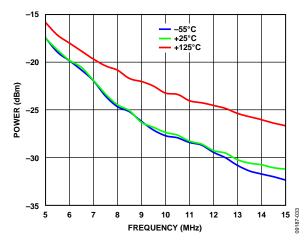

| RF Input Sensitivity                                                | -10                  |      | 0         | dBm    |                                                                      |

| RF Input Frequency (RF <sub>IN</sub> )                              | 5                    |      | 400       | MHz    | For RF <sub>IN</sub> < 5 MHz, ensure slew rate (SR) > 4 V/ $\mu$ s   |

| REFIN CHARACTERISTICS                                               |                      |      |           |        |                                                                      |

| REF <sub>IN</sub> Input Frequency                                   | 20                   |      | 300       | MHz    | For REF <sub>IN</sub> < 20 MHz, ensure SR > 50 V/µs                  |

| REF <sub>IN</sub> Input Sensitivity <sup>1</sup>                    | 0.8                  |      | $AV_{DD}$ | V p-р  | Biased at $AV_{DD}/2$ (ac coupling ensures $AV_{DD}/2$ bias)         |

| REF <sub>IN</sub> Input Capacitance                                 |                      |      | 10        | pF     |                                                                      |

| REF <sub>IN</sub> Input Current                                     |                      |      | ±100      | μA     |                                                                      |

| PHASE FREQUENCY DETECTOR (PFD)                                      |                      |      |           |        |                                                                      |

| Phase Detector Frequency <sup>2</sup>                               |                      |      | 104       | MHz    | ABP[2:1] = 00 (2.9 ns antibacklash pulse width)                      |

| CHARGE PUMP                                                         |                      |      |           |        | Programmable                                                         |

| Ic₂ Sink/Source                                                     |                      |      |           |        |                                                                      |

| High Value                                                          |                      | 5    |           | mA     | $R_{SET} = 5.1 \ k\Omega$                                            |

| Low Value                                                           |                      | 625  |           | μA     |                                                                      |

| Absolute Accuracy                                                   |                      | 2.5  |           | %      | $R_{SET} = 5.1 \ k\Omega$                                            |

| R <sub>SET</sub> Range                                              | 3.0                  |      | 11        | kΩ     |                                                                      |

| I <sub>CP</sub> Three-State Leakage                                 |                      | 1    |           | nA     | $T_A = 25^{\circ}C$                                                  |

| ICP VS. VCP                                                         |                      | 1.5  |           | %      | $0.5 \text{ V} \le \text{V}_{CP} \le (\text{V}_{P} - 0.5 \text{ V})$ |

| Sink and Source Current Matching                                    |                      | 2    |           | %      | $0.5 \text{ V} \le \text{V}_{CP} \le (\text{V}_{P} - 0.5 \text{ V})$ |

| I <sub>CP</sub> vs. Temperature                                     |                      | 2    |           | %      | $V_{CP} = V_P/2$                                                     |

| LOGIC INPUTS                                                        |                      |      |           |        |                                                                      |

| Input High Voltage, V⊩                                              | 1.4                  |      |           | V      |                                                                      |

| Input Low Voltage, V <sub>IL</sub>                                  |                      |      | 0.6       | V      |                                                                      |

| Input Current, I <sub>INH</sub> , I <sub>INL</sub>                  |                      |      | ±1        | μA     |                                                                      |

| Input Capacitance, C <sub>IN</sub>                                  |                      |      | 10        | pF     |                                                                      |

| LOGIC OUTPUTS                                                       |                      |      |           |        |                                                                      |

| Output High Voltage, V <sub>он</sub>                                | 1.4                  |      |           | V      | Open-drain output, 1 k $\Omega$ pull-up resistor to 1.8 V            |

|                                                                     | DV <sub>DD</sub> – 0 | 0.4  |           | V      | CMOS output                                                          |

| Output High Current, Iон                                            |                      |      | 100       | μA     |                                                                      |

| Output Low Voltage, Vol                                             |                      |      | 0.4       | V      | $I_{OL} = 500 \ \mu A$                                               |

| POWER SUPPLIES                                                      |                      |      |           |        |                                                                      |

| AV <sub>DD</sub>                                                    | 2.7                  |      | 3.3       | V      |                                                                      |

|                                                                     | AV <sub>DD</sub>     |      |           | V      |                                                                      |

| VP                                                                  | AV <sub>DD</sub>     |      | 5.5       | V      | $AV_{DD} \le V_P \le 5.5 V$                                          |

| $I_{DD}^{3} (AI_{DD} + DI_{DD})$                                    |                      | 5.0  | 6.0       | mA     |                                                                      |

| Ip                                                                  |                      |      | 0.4       | mA     | $T_A = 25^{\circ}C$                                                  |

| Power-Down Mode                                                     |                      | 1    |           | μA     | Al <sub>DD</sub> + Dl <sub>DD</sub>                                  |

| NOISE CHARACTERISTICS                                               |                      |      |           |        |                                                                      |

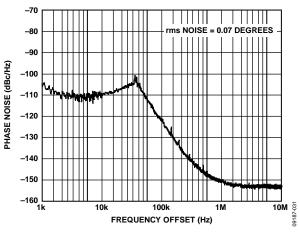

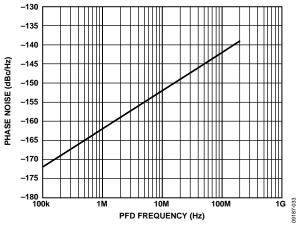

| Normalized Phase Noise Floor (PN <sub>SYNTH</sub> ) <sup>4, 5</sup> |                      | -222 |           | dBc/Hz | PLL loop bandwidth = 500 kHz                                         |

| Normalized $1/f$ Noise (PN <sub>1_f</sub> ) <sup>4, 6</sup>         |                      | -119 |           | dBc/Hz | Measured at 10 kHz offset; normalized to 1 GHz                       |

$^{1}$  AV<sub>DD</sub> = DV<sub>DD</sub> = 3 V.

<sup>2</sup> Guaranteed by design. Sample tested to ensure compliance.

${}^{3}T_{A} = 25^{\circ}C$ ; AV<sub>DD</sub> = DV<sub>DD</sub> = 3 V; RF<sub>IN</sub> = 350 MHz. The current for any other setup (25°C, 3.0 V) in mA is given by 2.35 + 0.0046 (REF<sub>IN</sub>) + 0.0062 (RF); RF frequency and REF<sub>IN</sub> frequency in MHz.

<sup>4</sup> All phase noise measurements were performed with a Rohde & Schwarz FSUP26 phase noise test system using the EVAL-ADF4002EBZ1 evaluation board and the ultralow noise, 100 MHz OCXO from Wenzel (Part No. 501-16843) as the PLL reference.

<sup>5</sup> The synthesizer phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20logN (where N is the N divider value) and 10logf<sub>PFD</sub>. PN<sub>SYNTH</sub> = PN<sub>TOT</sub> - 10logf<sub>PFD</sub> - 20logN.

<sup>6</sup> The PLL phase noise is composed of 1/f (flicker) noise plus the normalized PLL noise floor. The formula for calculating the 1/f noise contribution at an RF frequency (f<sub>8</sub>) and at a frequency offset (f) is given by PN = P<sub>1.f</sub> + 10log(10 kHz/f) + 20log(f<sub>8</sub>/r / 1 GHz). Both the normalized phase noise floor and the flicker noise are modeled in ADIsimPLL.

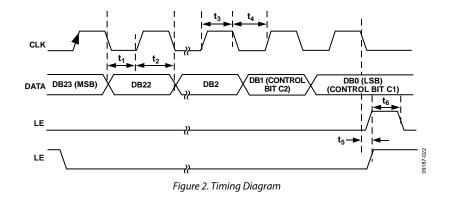

## TIMING CHARACTERISTICS

$AV_{DD} = DV_{DD} = 3 V \pm 10\%$ ,  $AV_{DD} \le V_P \le 5.5 V$ , AGND = DGND = CPGND = 0 V,  $R_{SET} = 5.1 k\Omega$ , dBm referred to 50  $\Omega$ ,  $T_A = T_{MAX}$  to  $T_{MIN}$ , unless otherwise noted. Operating temperature range is  $-55^{\circ}$ C to  $+125^{\circ}$ C.

| Table 2 | 2. |

|---------|----|

|---------|----|

| Parameter      | Limit <sup>1</sup> | Unit   | Description            |

|----------------|--------------------|--------|------------------------|

| t <sub>1</sub> | 10                 | ns min | DATA to CLK setup time |

| t <sub>2</sub> | 10                 | ns min | DATA to CLK hold time  |

| t <sub>3</sub> | 25                 | ns min | CLK high duration      |

| t <sub>4</sub> | 25                 | ns min | CLK low duration       |

| t <sub>5</sub> | 10                 | ns min | CLK to LE setup time   |

| t <sub>6</sub> | 20                 | ns min | LE pulse width         |

<sup>1</sup> Guaranteed by design, but not production tested.

### **Timing Diagram**

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}C$ , unless otherwise noted.

#### Table 3.

| 1 4010 01                               |                                    |

|-----------------------------------------|------------------------------------|

| Parameter                               | Rating                             |

| AV <sub>DD</sub> to GND <sup>1</sup>    | -0.3 V to +3.6 V                   |

| AV <sub>DD</sub> to DV <sub>DD</sub>    | –0.3 V to +0.3 V                   |

| V <sub>P</sub> to GND <sup>1</sup>      | –0.3 V to +5.8 V                   |

| V <sub>P</sub> to AV <sub>DD</sub>      | –0.3 V to +5.8 V                   |

| Digital I/O Voltage to GND <sup>1</sup> | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Analog I/O Voltage to GND <sup>1</sup>  | -0.3 V to V <sub>P</sub> + 0.3 V   |

| REFIN, RFINA, RFINB to GND <sup>1</sup> | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| Operating Temperature Range             |                                    |

| Industrial                              | –55°C to +125°C                    |

| Storage Temperature Range               | –65°C to +125°C                    |

| Maximum Junction Temperature            | 150°C                              |

| Lead Temperature, Soldering             |                                    |

| Vapor Phase (60 sec)                    | 215℃                               |

| Infrared (15 sec)                       | 220°C                              |

| Transistor Count                        |                                    |

| CMOS                                    | 6425                               |

| Bipolar                                 | 303                                |

|                                         |                                    |

This device is a high performance RF integrated circuit with an ESD rating of <2 kV, and it is ESD sensitive. Proper precautions should be taken for handling and assembly.

## THERMAL CHARACTERISTICS

#### Table 4. Thermal Impedance

| Package Type  | θ <sub>JA</sub> | Unit |

|---------------|-----------------|------|

| TSSOP (RU-16) | 150.4           | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$^{1}$  GND = AGND = DGND = CPGND = 0 V.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## **ADF4002-EP**

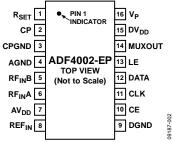

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                            |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | R <sub>set</sub>   | Connecting a resistor between this pin and CPGND sets the maximum charge pump output current. The nominal voltage potential at the R <sub>SET</sub> pin is 0.66 V. The relationship between I <sub>CP</sub> and R <sub>SET</sub> is $I_{CPMAX} = \frac{25.5}{R_{SET}}$ |

|         |                    | where $R_{SET} = 5.1 \text{ k}\Omega$ and $I_{CPMAX} = 5 \text{ mA}$ .                                                                                                                                                                                                 |

| 2       | СР                 | Charge Pump Output. When enabled, this output provides $\pm I_{CP}$ to the external loop filter that, in turn, drives the external VCO.                                                                                                                                |

| 3       | CPGND              | Charge Pump Ground. This is the ground return path for the charge pump.                                                                                                                                                                                                |

| 4       | AGND               | Analog Ground. This is the ground return path of the RF input.                                                                                                                                                                                                         |

| 5       | RFıℕB              | Complementary Input to the RF Input. This pin must be decoupled to the ground plane with a small bypass capacitor, typically 100 pF.                                                                                                                                   |

| 6       | RF <sub>IN</sub> A | Input to the RF Input. This small-signal input is ac-coupled to the external VCO.                                                                                                                                                                                      |

| 7       | AV <sub>DD</sub>   | Analog Power Supply. This can range from 2.7 V to 3.3 V. Decoupling capacitors to the analog ground plane should be placed as close as possible to the AV <sub>DD</sub> pin. AV <sub>DD</sub> must be the same value as DV <sub>DD</sub> .                             |

| 8       | REF <sub>IN</sub>  | Reference Input. This CMOS input has a nominal threshold of AV <sub>DD</sub> /2 and a dc equivalent input resistance of 100 k $\Omega$ . This input can be driven from a TTL or CMOS crystal oscillator or it can be ac-coupled.                                       |

| 9       | DGND               | Digital Ground.                                                                                                                                                                                                                                                        |

| 10      | CE                 | Chip Enable. A logic low on this pin powers down the device and puts the charge pump output into three-<br>state mode. Taking this pin high powers up the device, depending on the status of the Power-Down Bit PD1.                                                   |

| 11      | CLK                | Serial Clock Input. The serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This input is a high impedance CMOS input.                                                       |

| 12      | DATA               | Serial Data Input. The serial data is loaded MSB first; the two LSBs are the control bits. This input is a high impedance CMOS input.                                                                                                                                  |

| 13      | LE                 | Load Enable. When LE goes high, the data stored in the shift registers is loaded into one of the four latches; the latch is selected using the control bits. This input is a high impedance CMOS input.                                                                |

| 14      | MUXOUT             | Multiplexer Output. This output allows the lock detect, the scaled RF, or the scaled reference frequency to be accessed externally.                                                                                                                                    |

| 15      | DVDD               | Digital Power Supply. This can range from 2.7 V to 3.3 V. Decoupling capacitors to the digital ground plane should be placed as close as possible to the DV <sub>DD</sub> pin. DV <sub>DD</sub> must be the same value as AV <sub>DD</sub> .                           |

| 16      | VP                 | Charge Pump Power Supply. This should be greater than or equal to $AV_{DD}$ . In systems where $AV_{DD}$ is 3 V, $V_P$ can be set to 5.5 V and used to drive a VCO with a tuning voltage of up to 5 V.                                                                 |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

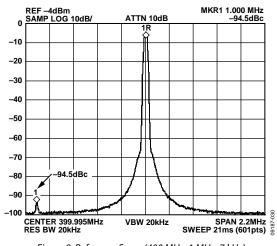

Figure 5. RF Input Sensitivity, Low Frequency

Figure 6. Integrated Phase Noise (400 MHz, 1 MHz, 50 kHz)

Figure 7. Phase Noise (Referred to CP Output) vs. PFD Frequency

Figure 8. Reference Spurs (400 MHz, 1 MHz, 7 kHz)

## ADF4002-EP

## **OUTLINE DIMENSIONS**

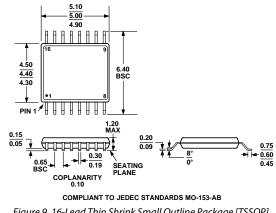

Figure 9. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| ADF4002SRU-EP      | –55°C to +125°C   | 16-Lead TSSOP       | RU-16          |

| ADF4002SRU-EP-RL7  | −55°C to +125°C   | 16-Lead TSSOP       | RU-16          |

| ADF4002SRUZ-EP     | −55°C to +125°C   | 16-Lead TSSOP       | RU-16          |

| ADF4002SRUZ-EP-RL7 | −55°C to +125°C   | 16-Lead TSSOP       | RU-16          |

<sup>1</sup> Z = RoHS Compliant Part

©2010–2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09187-0-9/18(A)

www.analog.com