# 12-Bit-ADC with **Microprocessor Interface**

**AD574S**

#### 1.0 **SCOPE**

This specification documents the detailed requirements for Analog Devices space qualified die including die qualification as described for Class K in MIL-PRF-38534, Appendix C, Table C-II except as modified herein.

The manufacturing flow described in the STANDARD DIE PRODUCTS PROGRAM brochure at http://www.analog.com/marketSolutions/militaryAerospace/pdf/Die Broc.pdf is to be considered a part of this specification.

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at www.analog.com/AD574

Part Number. The complete part number(s) of this specification follow: 2.0

> Part Number Description

AD574-000C 12-Bit-ADC with Microprocessor Interface

AD574R000C Radiation Tested 12-Bit-ADC with Microprocessor Interface

#### 3.0 Die Information

#### 3.1 **Die Dimensions**

| Die Size  | Die Thickness  | Bond Pad Metalization |

|-----------|----------------|-----------------------|

| 179 x 180 | 19 mil ± 2 mil | Al/Cu                 |

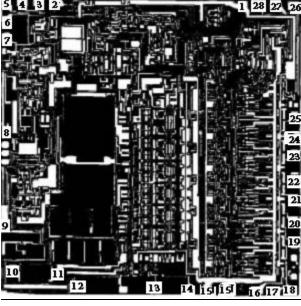

#### **Die Picture** 3.2

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

| 10 11 13 14 jejie 16 17 18                                                                                                                                                                                                                                                                                                                                                    |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| ASD0012706 Rev. J<br>Information furnished by Analog Devices is believed to be accurate and reliable.<br>However, no responsibility is assumed by Analog Devices for its use, nor for any<br>infringements of patents or other rights of third parties that may result from its use.<br>Specifications subject to change without notice. No license is granted by implication | One Techn |

| $1 V_{LOGIC}$               | 28 STATUS        |

|-----------------------------|------------------|

| $2 \frac{12}{8}$            | 27 DB11          |

|                             | 26 DB10          |

| 3 CS                        | 25 DB9           |

| $\frac{4}{5} \frac{A_0}{R}$ | 24 DB8           |

| 5 R/C                       | 23 DB7           |

| 6 CE                        | 22 DB6           |

| $7 V_{CC}$                  | 21 DB5           |

| 8 REF <sub>OUT</sub>        | 20 DB4           |

| 9 AC                        | 19 DB3           |

| $10 \text{ REF}_{IN}$       | 19 DB3<br>18 DB2 |

| $11 V_{EE}$                 | -                |

| 12 BIP OFF                  | 17 DB1           |

| $13\ 10V_{IN}$              | 16 DB0           |

| $14.20V_{\rm IN}$           | 15 DC            |

|                             |                  |

### 3.3 Absolute Maximum Ratings

| V <sub>CC</sub> to Digital Common                                                     | 0 to +16.5V dc                             |

|---------------------------------------------------------------------------------------|--------------------------------------------|

| V <sub>EE</sub> to Digital Common                                                     |                                            |

| V <sub>LOG</sub> to Digital Common                                                    | 0 to +7V dc                                |

| Analog to Digital Common                                                              | ±1V dc                                     |

| Control Inputs (CE, $\overline{CS}$ , Ao, 12/8, R/ $\overline{C}$ ) to Digital Common | 0.5V dc to                                 |

|                                                                                       | $V_{LOG}$ +0.5V dc                         |

| Analog Inputs (REF IN, BIP OFF, 10 V <sub>IN</sub> ) to Analog Common                 | $\dots$ V <sub>EE</sub> to V <sub>CC</sub> |

| 20 V <sub>IN</sub> Analog Input Voltage to Analog Common                              | ±24V dc                                    |

| V <sub>ref out</sub>                                                                  | Indefinite short to                        |

|                                                                                       |                                            |

|                                                                                       | short to V <sub>CC</sub>                   |

| Storage Temperature                                                                   | 65°C to +150°C                             |

| Junction Temperature (T <sub>J</sub> )                                                | +175°C                                     |

| Operating Temperature Range                                                           | 55°C to +125°C                             |

### 4.0 <u>Die Qualification</u>

In accordance with class-K version of MIL-PRF-38534, Appendix C, Table C-II, except as modified herein.

- (a) Qual Sample Size and Qual Acceptance Criteria 10/0

- (b) Qual Sample Package Ceramic DIP

- (c) Pre-screen electrical test over temperature performed post-assembly prior to die qualification.

| Table I - Dice Electrical Characteristics                                                                                 |                 |                         |            |           |             |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|------------|-----------|-------------|--|--|

| Parameter                                                                                                                 | Symbol          | Conditions<br><u>1/</u> | Limit Min  | Limit Max | Units       |  |  |

| Power Supply Current From V <sub>LOG</sub>                                                                                | llog            |                         |            | 40        | mA          |  |  |

| Power Supply Current From Vcc                                                                                             | lcc             |                         |            | 5         | mA          |  |  |

| Power Supply Current From VEE                                                                                             | lee             |                         | -30        |           | mA          |  |  |

| Resolution                                                                                                                |                 |                         | 12         |           | Bits        |  |  |

| Integral Linearity Error Differential<br>Linearity Error (Minimum<br>Resolution For Which No Missing<br>Codes Guaranteed) | ILE<br>DLE      |                         | -0.5<br>12 | 0.5       | LSB<br>Bits |  |  |

| Unipolar Offset Voltage Error                                                                                             | V <sub>IO</sub> |                         | -2.0       | 2.0       | LSB         |  |  |

| Table I – Dice Electrical Characteristics (Continued)      |                                        |                                                                  |                                |           |           |  |  |

|------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------|--------------------------------|-----------|-----------|--|--|

| Parameter                                                  | Symbol                                 | Conditions<br><u>1</u> /                                         | Limit<br>Min                   | Limit Max | Units     |  |  |

| Bipolar Offset Voltage Error                               | Bz                                     |                                                                  | -4.0                           | 4.0       | LSB       |  |  |

| Gain Error                                                 | ΔΑε                                    | With 50Ω resistor from REF<br>OUT to REF IN                      |                                | .25       | % of F.S. |  |  |

| Power Supply Sensitivity                                   | +P <sub>SS1</sub><br>+P <sub>SS2</sub> | $+13.5V \le V_{CC} \le +16.5V$<br>$+11.4V \le V_{CC} \le +12.6V$ | -1.0                           | 1.0       |           |  |  |

| (Maximum Change In Full Scale                              | +P <sub>SS3</sub>                      | $+4.5V \le V_{LOG} \le +5.5V$                                    | -0.5                           | 0.5       | LSB       |  |  |

| Calibration)                                               | -P <sub>SS1</sub>                      | -16.5V ≤ V <sub>EE</sub> ≤ -13.5V                                | $-16.5V \le V_{EE} \le -13.5V$ |           |           |  |  |

|                                                            | -P <sub>SS2</sub>                      | -12.6V ≤ V <sub>EE</sub> ≤ -11.4V                                | -1.0                           | 1.0       |           |  |  |

| Input Impedance                                            | Z <sub>IN</sub>                        | 10V span                                                         | 3                              | 7         | kΩ        |  |  |

| input impedance                                            | ZIN                                    | 20V span                                                         | 6                              | 14        | KL2       |  |  |

| Internal Reference Voltage                                 | V <sub>REF</sub>                       | <u>2</u> /                                                       | 9.98                           | 10.02     | V         |  |  |

| Input Voltage (CE, $\overline{	ext{CS}}$ ,                 | V <sub>IH</sub>                        | Logic "1"                                                        | 2.0                            | 5.5       |           |  |  |

| 12/8, R/ $\overline{\overline{C}}$ , Ao) $\underline{3}$ / | VIL                                    | Logic "0"                                                        | -0.5                           | 0.8       | V         |  |  |

| Input Current                                              | I <sub>IN</sub>                        |                                                                  | -20                            | +20       | μΑ        |  |  |

| Output Voltage<br>(DB11-DB0,STS)                           | V <sub>OL</sub>                        | Logic "0",<br>I <sub>SINK</sub> =+1.6mA                          |                                | 400       | mV        |  |  |

| Output Voltage<br>(DB11-DB0)                               | V <sub>OH</sub>                        | Logic "1",<br>Isourc=+500μA                                      | 2.4                            |           | V         |  |  |

| High Impedance State<br>Output Current                     | Iz                                     | High-Z state,<br>DB11 – DB0 only                                 | -20                            | +20       | μА        |  |  |

### Table I Notes:

- $V_{\text{CC}} = \pm 15 \text{V}, \ V_{\text{LOG}} = +5 \text{V}, \ V_{\text{EE}} = -15 \text{V}, \ T_{\text{A}} = 25 ^{\circ}\text{C}, \ \text{unless otherwise specified}.$  The reference voltage external load current shall be a constant dc and shall not exceed 1.5 mA. Reference should be buffered for operation of  $\pm 12 \text{V}$  supplies. External load should not change during conversion. <u>1/</u> <u>2</u>/

- <u>3</u>/ 12/8 is not TTL compatible and must be hard wired to  $\ensuremath{V_{LOG}}$  or digital ground.

## **AD574S**

| Table II - Electrical Characteristics for Qual Samples                            |                                  |                                   |                          |                |              |              |           |

|-----------------------------------------------------------------------------------|----------------------------------|-----------------------------------|--------------------------|----------------|--------------|--------------|-----------|

| Parameter                                                                         | Symbol                           | Conditions <u>1</u> /             |                          | Sub-<br>groups | Limit<br>Min | Limit<br>Max | Units     |

| De la Caral Caral Frank                                                           |                                  |                                   |                          | 1, 2, 3        |              | 40           |           |

| Power Supply Current From V <sub>LOG</sub>                                        | I <sub>LOG</sub>                 |                                   | M, D, L, R <u>5</u> /    | 1              |              | 40           |           |

| Power Supply Current From                                                         |                                  |                                   |                          | 1, 2, 3        |              | 5            | A         |

| $V_{cc}$                                                                          | lcc                              |                                   | M, D, L, R <u>5</u> /    | 1              |              | 5            | − mA      |

| Power Supply Current From                                                         |                                  |                                   |                          | 1, 2, 3        | -30          |              |           |

| $V_{EE}$                                                                          | I <sub>EE</sub>                  |                                   | M, D, L, R <u>5</u> /    | 1              | -30          |              |           |

|                                                                                   |                                  |                                   |                          | 1              | -0.5         | 0.5          |           |

| Integral Linearity Error                                                          | ILE                              |                                   |                          | 2, 3           | -1.0         | 1.0          | LSB       |

|                                                                                   |                                  |                                   | M, D, L, R <u>5</u> /    | 1              | -1.0         | 1.0          |           |

| Differential Linearity Error (Minimum                                             | 51.5                             |                                   |                          | 1              | 12           |              | 5         |

| Resolution For Which No Missing<br>Codes Guaranteed) <u>6</u> /                   | DLE                              |                                   |                          | 2, 3           | 12           |              | Bits      |

|                                                                                   |                                  | Using interr                      | nal reference            | 1              | -2.0         | 2.0          |           |

| Unipolar Offset Voltage Error                                                     | V <sub>IO</sub>                  |                                   | M, D, L, R <u>5</u> /    | 1              | -3.0         | 3.0          |           |

| Unipolar Offset Drift <u>6</u> /                                                  | $\frac{\Delta V_{IO}}{\Delta T}$ | Using internal reference          |                          | 2, 3           | -1.0         | 1.0          |           |

|                                                                                   | _                                | Using interr                      | nal reference            | 1              | -4.0         | 4.0          | LSB       |

| Bipolar Offset Voltage Error                                                      | Bz                               |                                   | M, D, L, R <u>5</u> /    | 1              | -5.0         | 5.0          |           |

| Bipolar Zero Offset Drift <u>6</u> /                                              | $\frac{\Delta B_Z}{T}$           | Using interr                      | nal reference            | 2, 3           | -2.0         | +2.0         |           |

| Gain Error                                                                        | Δ Αε                             |                                   | or from REF OUT<br>EF IN | 1              |              | .25          | % of F.S. |

|                                                                                   |                                  |                                   | M, D, L, R <u>5</u> /    | 1              |              | .35          |           |

| Gain Error Drift <u>6</u> /                                                       | $\frac{\Delta A_E}{\Delta T}$    | Using interr                      | Using internal reference |                | -25.0        | 25.0         | ppm/°C    |

|                                                                                   | +P <sub>SS1</sub>                | +13.5V ≤ V <sub>CC</sub> ≤ +16.5V |                          |                |              |              |           |

|                                                                                   | +P <sub>SS2</sub>                | +11.4V ≤ V <sub>CC</sub> ≤ +12.6V |                          | 1              | -1.0         | 1.0          |           |

| Power Supply Sensitivity (Maximum<br>Change In Full Scale Calibration) <u>6</u> / | +P <sub>SS3</sub>                | +4.5V ≤ V <sub>LOG</sub> ≤ +5.5V  |                          | 1              | -0.5         | 0.5          | LSB       |

|                                                                                   | -P <sub>SS1</sub>                | -16.5V≤V                          | <sub>ree</sub> ≤ -13.5V  |                |              |              |           |

|                                                                                   | -P <sub>SS2</sub>                |                                   | <sub>ZEE</sub> ≤ -11.4V  | 1              | -1.0         | 1.0          |           |

|                                                                                   |                                  | 10V span                          |                          | 1              | 3            | 7            |           |

| Input Impedance <u>6</u> /                                                        | Z <sub>IN</sub> 20V span         |                                   | 1                        | 6              | 14           | kΩ           |           |

| Table II - Electrical Characteristics for Qual Samples                |                         |                                                                    |                |              |              |       |  |

|-----------------------------------------------------------------------|-------------------------|--------------------------------------------------------------------|----------------|--------------|--------------|-------|--|

| Parameter                                                             | Symbol Conditions 1/    |                                                                    | Sub-<br>groups | Limit<br>Min | Limit<br>Max | Units |  |

| Output Voltage<br>(DB11-DB0, STS) <u>6</u> /                          | V <sub>OL</sub>         | Logic "0", $T_A = +25$ °C,<br>$I_{SINK} = +1.6$ mA                 | 1, 2, 3        |              | 400          | mV    |  |

| Output Voltage<br>(DB11-DB0) <u>6</u> /                               | Vон                     | Logic "1", T <sub>A</sub> = +25°C,<br>I <sub>SOURCE</sub> = +500μA | 1              | 2.4          |              | V     |  |

| High Impedance State Output Current<br><u>6</u> /                     | lz                      | High-Z state, $T_A = +25^{\circ}C$ , DB11-DB0 only                 | 1              | -20          | +20          | μА    |  |

| Low R/ $\overline{C}$ Pulse Width $4/6$                               | t <sub>HRL</sub>        |                                                                    | 9              | 250          |              | ns    |  |

| STS Delay from R/ $\overline{C}$ 4/6/                                 | <b>t</b> <sub>DS</sub>  |                                                                    | 9              |              | 600          | ns    |  |

| Data Valid After R/ $\overline{C}$ Low $\underline{4}/\underline{6}/$ | <b>t</b> hdr            |                                                                    | 9              |              | 25           | ns    |  |

| STS Delay After Valid Data <u>4</u> / <u>6</u> /                      | <b>t</b> HS             |                                                                    | 9              | 300          | 1000         | ns    |  |

| High R/ $\overline{C}$ Pulse Width $\underline{6}$ /                  | t <sub>HRH</sub>        |                                                                    | 9              | 300          |              | ns    |  |

| Data Access Time <u>6</u> /                                           | <b>t</b> <sub>DDR</sub> |                                                                    | 9              |              | 250          | ns    |  |

| STS Delay from CE <u>6</u> /                                          | <b>t</b> <sub>DSC</sub> |                                                                    | 9              |              | 350          | ns    |  |

| CE Pulse Width 6/                                                     | <b>t</b> hec            |                                                                    | 9              | 300          |              | ns    |  |

| Conversion Time 6/                                                    | +-                      | 8-bit cycle 9 10                                                   |                | 24           |              |       |  |

| Conversion time o/                                                    | <b>t</b> c -            | 12-bit cycle                                                       | 9              | 15           | 35           | μS    |  |

| Access Time (from CE) <u>6</u> /                                      | <b>t</b> <sub>DD</sub>  |                                                                    | 9              |              | 200          | ns    |  |

### Table II Notes:

$<sup>\</sup>underline{1}/ \hspace{1cm} V_{CC} = \pm 15 \text{V}, \ V_{LOG} = +5 \text{V}, \ V_{EE} = -15 \text{V}, \ -55 ^{\circ}\text{C} \leq T_{A} \leq +125 ^{\circ}\text{C}, \ unless otherwise specified}.$

The reference voltage external load current shall be a constant dc and shall not exceed 1.5 mA. Reference sho<u>uld be buffered for operation of ±12V supplies.</u> External load should not change during conversion.

$<sup>\</sup>underline{3}$ / 12/8 is not TTL compatible and must be hard wired to  $V_{LOG}$  or digital ground.

$<sup>\</sup>underline{4}$  Subgroups 10 and 11, if not tested, shall be guaranteed to the specified limits.

<sup>5/</sup> Tested at 100Krad

<sup>6/</sup> Not Tested Post Irradiation.

## **AD574S**

| Table III - Delta Parameter Table |                     |        |                    |      |                      |      |           |          |

|-----------------------------------|---------------------|--------|--------------------|------|----------------------|------|-----------|----------|

| Parameter                         | Cala al             | Sub-   | Post Burn In Limit |      | Post Life Test Limit |      | Life Test | l locito |

| raiametei                         | Symbol              | groups | Min                | Max  | Min                  | Max  | Delta     | Units    |

| Unipolar Offset Voltage Error     | Uni V <sub>IO</sub> | 1      | -2.0               | 2.0  | -2.5                 | 2.5  | ±0.5      | LSB      |

| Bipolar Offset Voltage Error      | Bpze                | 1      | -4.0               | 4.0  | -5.0                 | 5.0  | ±1.0      | LSB      |

| Gain Error                        | A <sub>E</sub>      | 1      | -0.25              | 0.25 | -0.25                | 0.35 | ±.10      | %FSR     |

### 5.0 <u>Life Test/Burn-In Information</u>

- 5.1 HTRB is not applicable for this drawing.

- 5.2 Burn-in is per MIL-STD-883 Method 1015 test condition B or C.

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

| Rev | Description of Change                                                                                                                                                                         | Date           |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Α   | Initiate                                                                                                                                                                                      | 04-Oct-2001    |

| В   | Update web address                                                                                                                                                                            | Jan. 25, 2002  |

| С   | Update web address. Add Radiation limits and part number.                                                                                                                                     | 4-Mar-03       |

| D   | Update 1.0 Scope description.                                                                                                                                                                 | 2 Aug. 2007    |

| Е   | Update header/footer & add to 1.0 Scope description.                                                                                                                                          | Feb. 14, 2008  |

| F   | Remove reference to condition <u>5</u> / note on Table I & add Junction Temperature (T <sub>J</sub> ) +175°C & Operating Temperature Range55°C to +125°C to Section 3.3-Absolute Max. Ratings | March 27, 2008 |

| G   | Updated Section 4.0c note to indicate pre-screen temp testing being performed.                                                                                                                | 6-JUN-2009     |

| Н   | Updated Font and Font Size to Standardize to ADI format                                                                                                                                       | 20-Sep-2011    |

| I   | Correct typo from mA to mV in output voltage of table II                                                                                                                                      | 17-MAR-2014    |

| J   | Append S to Aerospace Generic Title                                                                                                                                                           | 21-Mar-2014    |

www.analog.com