# Hot Swap Controller

## **FEATURES**

- Adjustable Undervoltage and Overvoltage Protection

- Foldback Current Limit

- Adjustable Current Limit Time-Out

- Protected Against Surges to 33V

- Single Channel NFET Driver

- Latch Off or Automatic Retry on Current Fault

- Driver for SCR Crowbar on Overvoltage

- Adjustable Reset Timer

- Reference Output with Uncommitted Comparator

- 16-Pin SSOP Package

## **APPLICATIONS**

- Hot Board Insertion

- Electronic Circuit Breaker

- InfiniBand<sup>™</sup> Systems

## DESCRIPTION

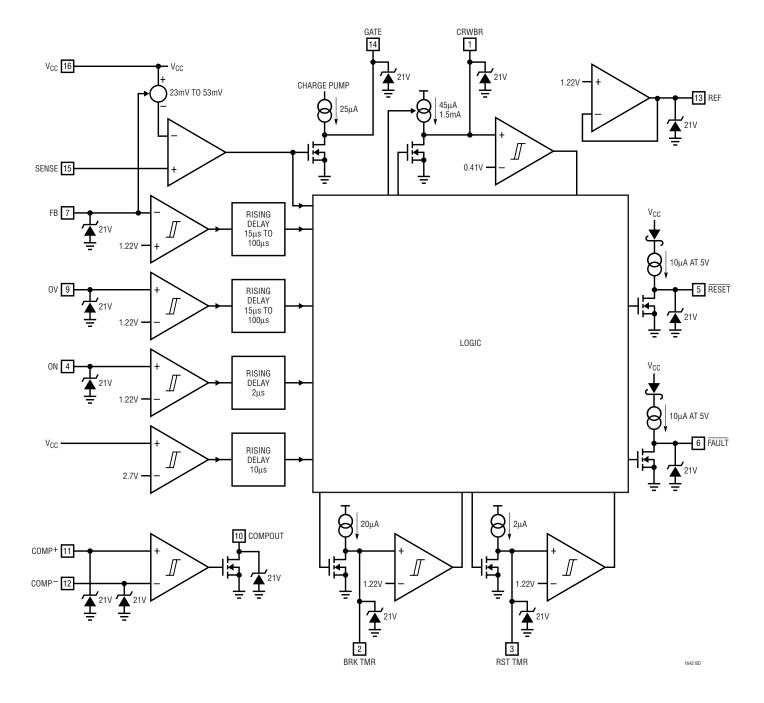

The LTC®1642 is a 16-pin Hot Swap™ controller that allows a board to be safely inserted and removed from a live backplane. Using an external N-Channel pass transistor, the board supply voltage can be ramped up at an adjustable rate. A high side switch driver controls the N-Channel gate for supply voltages above 2.97V.

The SENSE pin allows foldback limiting of the load current, with circuit breaker action after an adjustable delay time. The delay allows the part to power-up in current limit. The CRWBR output can be used to trigger an SCR for crowbar protection of the load if the input supply exceeds an adjustable threshold. The RESET output can generate a system reset with adjustable delay when the supply voltage falls below an adjustable threshold. The ON pin cycles the board power. The LTC1642 is available in the 16-pin SSOP package.

7, LTC and LT are registered trademarks of Linear Technology Corporation. Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

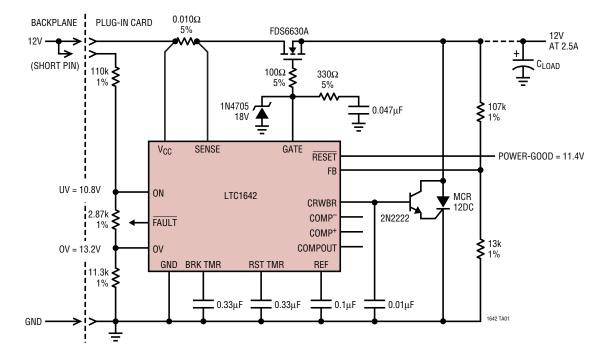

## TYPICAL APPLICATION

## **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                     |

|----------------------------------------------|

| Supply Voltage (V <sub>CC</sub> )0.3V to 33V |

| SENSE Pin $-0.3V$ to $(V_{CC} + 0.3V)$       |

| ON, FB, OV, COMP+, COMP-                     |

| RESET, FAULT, COMPOUT0.3V to 18.5V           |

| Operating Temperature Range                  |

| LTC1642C0°C to 70°C                          |

| LTC1642I40°C to 85°C                         |

| Storage Temperature Range65°C to 150°C       |

| Lead Temperature (Soldering, 10 sec)300°C    |

|                                              |

The LTC1642A is Recommended for Applications Where  $V_{CC}$  is Higher Than 12V.

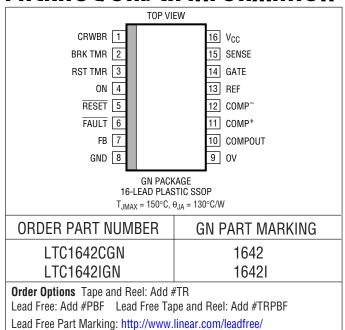

## PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

## DC ELECTRICAL CHARACTERISTICS

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$  unless otherwise specified.

| SYMBOL              | PARAMETER                                       | CONDITIONS                                      |   | MIN   | TYP   | MAX   | UNITS   |

|---------------------|-------------------------------------------------|-------------------------------------------------|---|-------|-------|-------|---------|

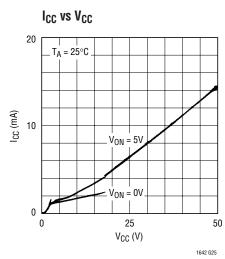

| V <sub>CC</sub>     | Operating Voltage Range                         |                                                 | • | 2.97  |       | 16.5  | V       |

| I <sub>CC</sub>     | V <sub>CC</sub> Supply Current                  | ON = V <sub>CC</sub>                            | • |       | 1.25  | 3.0   | mA      |

| $V_{LKHI}$          | V <sub>CC</sub> Undervoltage Lockout            | V <sub>CC</sub> Rising                          | • | 2.55  | 2.73  | 2.95  | V       |

| $V_{LKLO}$          | V <sub>CC</sub> Undervoltage Lockout            | V <sub>CC</sub> Falling                         | • | 2.35  | 2.50  | 2.95  | V       |

| V <sub>LKHYST</sub> | V <sub>CC</sub> Undervoltage Lockout Hysteresis |                                                 |   |       | 230   |       | mV      |

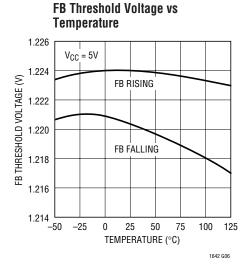

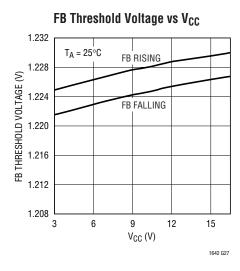

| $\overline{V_{FB}}$ | FB Pin Voltage Threshold                        | FB Falling                                      | • | 1.208 | 1.220 | 1.232 | V       |

| $\Delta V_{FB}$     | FB Pin Threshold Supply Variation               | FB Falling, $2.97V \le V_{CC} \le 16.5V$        | • |       | 5     | 15    | mV      |

| V <sub>FBHST</sub>  | FB Pin Voltage Threshold Hysteresis             |                                                 |   |       | 3     |       | mV      |

| I <sub>FB(IN)</sub> | FB Pin Input Current                            | V <sub>OV</sub> = 5V                            | • |       | 0     | ±1    | μА      |

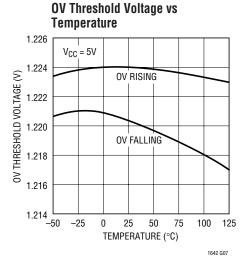

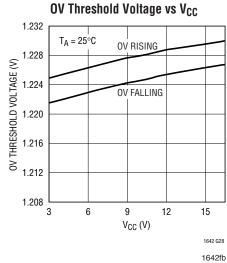

| V <sub>OV</sub>     | OV Pin Voltage Threshold                        | OV Rising                                       | • | 1.208 | 1.220 | 1.232 | V       |

| $\Delta V_{OV}$     | OV Pin Threshold Supply Variation               | OV Rising, $2.97V \le V_{CC} \le 16.5V$         | • |       | 5     | 15    | mV      |

| V <sub>OVHYST</sub> | OV Pin Voltage Threshold Hysteresis             |                                                 |   |       | 3     |       | mV      |

| I <sub>OV(IN)</sub> | OV Pin Input Current                            | V <sub>FB</sub> = 5V                            | • |       | 0     | ±1    | μА      |

| V <sub>RST</sub>    | RST TMR Pin Voltage Threshold                   | RST TMR Rising                                  | • | 1.200 | 1.220 | 1.250 | V       |

| $\Delta V_{RST}$    | RST TMR Pin Threshold Supply Variation          | RST TMR Rising, 2.97V ≤ V <sub>CC</sub> ≤ 16.5V | • |       | 5     | 15    | mV      |

| I <sub>RST</sub>    | RST TMR Pin Current                             | Timer On                                        | • | -1.5  | -2.0  | -2.5  | μA      |

|                     | DDV TMD Dis Valtage Threehold                   | Timer Off, V <sub>RSTTMR</sub> = 1.5V           | - | 1 000 | 10    | 1.050 | mA<br>V |

| $V_{BRK}$           | BRK TMR Pin Voltage Threshold                   | BRK TMR Rising                                  | • | 1.200 | 1.220 | 1.250 |         |

| $\Delta V_{BRK}$    | BRK TMR Pin Threshold Supply Variation          | BRK TMR Rising, $2.97V \le V_{CC} \le 16.5V$    | • |       | 5     | 15    | mV      |

| $I_{BRK}$           | BRK TMR Pin Current                             | Timer On                                        | • | -15   | -20   | -30   | μΑ      |

|                     |                                                 | Timer Off, V <sub>BRKTMR</sub> = 1.5V           |   |       | 10    |       | mA      |

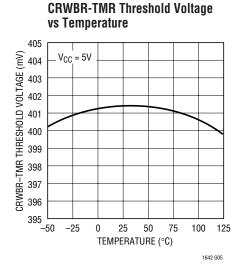

| V <sub>CR</sub>     | CRWBR Pin Voltage Threshold                     | CRWBR Rising                                    | • | 375   | 410   | 425   | mV      |

| $\Delta V_{CR}$     | CRWBR Pin Threshold Supply Variation            | $2.97V \le V_{CC} \le 16.5V$                    | • |       | 4     | 15    | mV      |

|                     |                                                 |                                                 |   |       |       |       | 1642fb  |

## DC ELECTRICAL CHARACTERISTICS

The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$  unless otherwise specified.

| SYMBOL                | PARAMETER                       | CONDITIONS                                                                                                                                                  |   | MIN              | TYP                 | MAX             | UNITS          |

|-----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------|---------------------|-----------------|----------------|

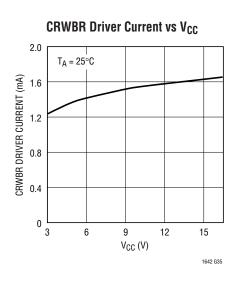

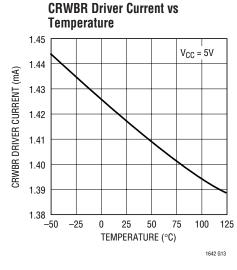

| I <sub>CR</sub>       | CRWBR Pin Current               | CRWBR On, V <sub>CRWBR</sub> = 0V<br>CRWBR On, V <sub>CRWBR</sub> = 2.1V<br>CRWBR Off, V <sub>CRWBR</sub> = 1.5V                                            | • | -30<br>-1000     | -45<br>-1500<br>2.3 | -60             | μA<br>μA<br>mA |

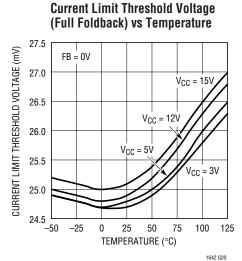

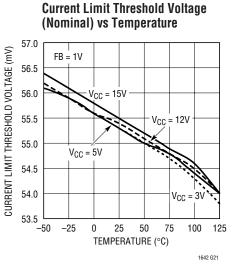

| V <sub>CB</sub>       | Circuit Breaker Trip Voltage    | $V_{CB} = (V_{CC} - V_{SENSE}), V_{FB} = GND$<br>$V_{CB} = (V_{CC} - V_{SENSE}), V_{FB} = 1V$                                                               | • | 15<br>45         | 25<br>52.5          | 36<br>60        | mV<br>mV       |

|                       |                                 | $\begin{array}{l} 2.97V \leq V_{CC} \leq 16.5V, \\ V_{CB} = (V_{CC} - V_{SENSE}),  V_{FB} = GND \\ V_{CB} = (V_{CC} - V_{SENSE}),  V_{FB} = 1V \end{array}$ | • | 12<br>42         | 25<br>52.5          | 39<br>63        | mV<br>mV       |

| I <sub>SENSE</sub>    | SENSE Pin Input Bias Current    | $V_{CC} = V_{SENSE} = 16.5V$                                                                                                                                | • |                  |                     | 0.5             | μА             |

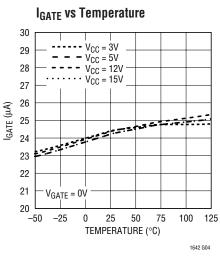

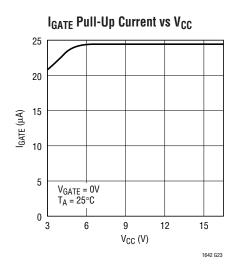

| I <sub>GATE</sub>     | GATE Pin Output Current         | Charge Pump On, V <sub>GATE</sub> = GND<br>Charge Pump Off, V <sub>GATE</sub> = 5V                                                                          | • | -20              | -25<br>10           | -30             | μA<br>mA       |

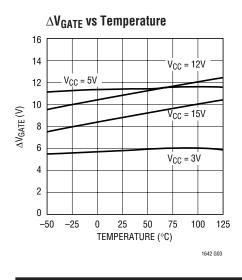

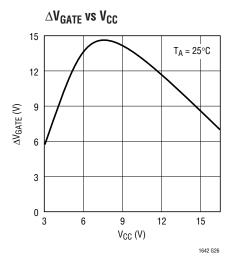

| $\Delta V_{GATE}$     | External N-Channel Gate Drive   | $V_{GATE} - V_{CC}, V_{CC} = 2.97V$ $V_{GATE} - V_{CC}, V_{CC} = 5V$ $V_{GATE} - V_{CC}, V_{CC} = 15V$                                                      | • | 4.5<br>10<br>4.5 | 5.9<br>11.5<br>8.5  | 8.0<br>14<br>18 | V<br>V<br>V    |

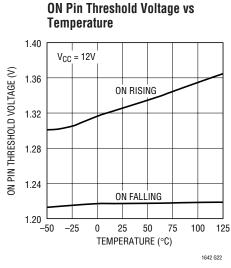

| V <sub>ONHI</sub>     | ON Pin Threshold                | ON Rising                                                                                                                                                   |   | 1.30             | 1.34                | 1.38            | V              |

| $\overline{V_{ONLO}}$ | ON Pin Threshold                | ON Falling                                                                                                                                                  | • | 1.20             | 1.22                | 1.26            | V              |

| V <sub>ONHYST</sub>   | ON Pin Hysteresis               |                                                                                                                                                             |   |                  | 110                 |                 | mV             |

| I <sub>ON(IN)</sub>   | ON Pin Input Current            | V <sub>ON</sub> = 5V                                                                                                                                        | • |                  | 0                   | ±1              | μА             |

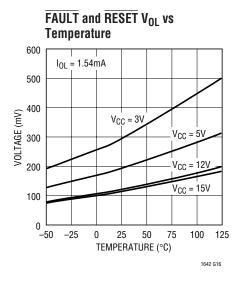

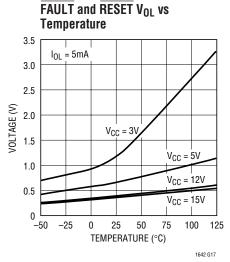

| V <sub>OL</sub>       | Output Low Voltage              | $\overline{\text{RESET}}$ , $\overline{\text{FAULT}}$ , COMPOUT I <sub>OL</sub> = 1.54mA RESET, $\overline{\text{FAULT}}$ I <sub>O</sub> = 5mA              | • |                  |                     | 0.4<br>2        | V              |

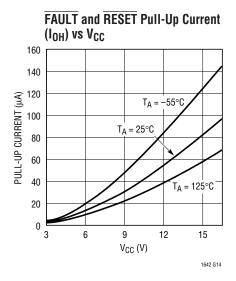

| I <sub>PU</sub>       | Logic Output Pull-Up Current    | RESET, FAULT = GND                                                                                                                                          |   |                  | -15                 |                 | μА             |

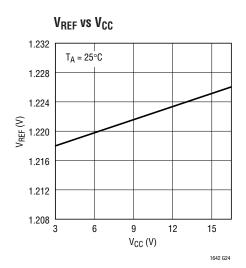

| $\overline{V_{REF}}$  | Reference Output Voltage        | No Load                                                                                                                                                     | • | 1.208            | 1.220               | 1.232           | V              |

| $\Delta V_{LNR}$      | Reference Supply Variation      | $2.97V \le V_{CC} \le 16.5V$ , No Load                                                                                                                      | • |                  | 5                   | 15              | mV             |

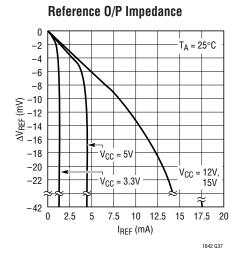

| $\Delta V_{LDR}$      | Reference Load Regulation       | I <sub>O</sub> = 0mA to -1mA, Sourcing Only                                                                                                                 | • |                  | 2.5                 | 7.5             | mV             |

| I <sub>RSC</sub>      | Reference Short-Circuit Current | V <sub>REF</sub> = 0V                                                                                                                                       |   |                  | 4.5                 |                 | mA             |

| $\overline{V_{COS}}$  | Comparator Offset Voltage       | V <sub>CM</sub> = V <sub>REF</sub>                                                                                                                          | • |                  |                     | ±10             | mV             |

| V <sub>CHYST</sub>    | Comparator Hysteresis           | V <sub>CM</sub> = V <sub>REF</sub>                                                                                                                          |   |                  | 3                   |                 | mV             |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

LINEAR TECHNOLOGY

## TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**CRWBR (Pin 1):** Overvoltage Crowbar Circuit Timer and Trigger. This pin controls an external overvoltage crowbar circuit. A capacitor from the pin to ground sets a 9ms/ $\mu$ F delay after an overvoltage occurs until an external SCR is triggered. See Applications Information. Ground the CRWBR pin if unused.

**BRK TMR (Pin 2):** Circuit Breaker Timer. Connect a capacitor from BRK TMR to ground to set a  $60 \text{ms/}\mu\text{F}$  delay from the time the sense resistor current reaches its limit until the FET is shut off. FAULT output is then asserted and the FET remains off until the chip is reset. Ground BRK TMR to allow the part to remain in current limit indefinitely.

**RST TMR (Pin 3):** Analog System/Reset Timer. A capacitor from this pin to ground sets a  $0.6s/\mu F$  delay from the ON pin going high to the start of the GATE pin's ramp. It also sets the delay from output voltage good, as sensed by the FB pin, to RESET going high.

**ON (Pin 4):** ON Contro<u>l Input</u>. When ON is low the GATE pin is grounded and FAULT goes high. The GATE pin voltage starts ramping up one RST TMR timing cycle after ON goes high. Pulsing the ON pin low for at least  $2\mu s$  resets the chip if it latches off after a sustained overvoltage or current limit. The threshold for a low to high transition is 1.34V with 110mV of hysteresis. A 21V zener clamp limits the voltage at this pin. The pin can be safely tied to  $V_{CC} > 21V$  through a series resistor that limits the current below 1mA.

**RESET** (**Pin 5**): Open Drain Reset Output. RESET is pulled low if the voltage at the FB pin is below its trip point. RESET goes high one RESET timing cycle after the FB voltage exceeds its trip point plus 3mV of hysteresis. RESET has a weak pull-up to one diode drop below  $V_{CC}$  and an external resistor can pull the pin above  $V_{CC}$ . A 21V zener clamp limits the voltage at this pin. The pin can be safely tied to  $V_{CC} > 21V$  through a series resistor that limits the current below 1mA.

**FAULT (Pin 6):** Open Drain Fault Output. FAULT is pulled low when the part turns off following a sustained overvoltage or current limit. It goes high  $2\mu s$  after the ON pin goes low. FAULT has a weak pull-up to one diode drop below  $V_{CC}$  and an external resistor can pull the pin above  $V_{CC}$ . A 21V zener clamp limits the voltage at this pin. The pin can be safely tied to  $V_{CC} > 21V$  through a series resistor that limits the current below 1mA.

**FB** (**Pin 7**): Output Voltage Monitor and Foldback Input. The FB comparator can be used with an external resistive divider to monitor the output supply voltage. When the FB voltage is lower than 1.22V the RESET pin is pulled low. RESET goes high one system timing cycle after the voltage at FB exceeds its threshold by 3mV of hysteresis. A low pass filter at the comparator's output prevents negative voltage glitches from triggering a false reset.

**GND (Pin 8):** Chip Ground.

## PIN FUNCTIONS

**OV** (**Pin 9**): Overvoltage Input. When the voltage on OV exceeds its trip point the GATE pin is pulled low immediately and the CRWBR timer starts. If OV remains above its trip point (minus 3mV of hysteresis) long enough for CRWBR to reach its trip point, then the part turns off until reset by pulsing the ON pin low. Otherwise, the GATE pin begins ramping up one RST TMR timing cycle after OV goes below its trip point. Ground the OV pin to disable overvoltage protection.

**COMPOUT (Pin 10):** Uncommitted Comparator's Open Drain Output.

**COMP**<sup>+</sup> (**Pin 11**): Uncommitted Comparator's Noninverting Input.

**COMP**<sup>-</sup> (**Pin 12**): Uncommitted Comparator's Inverting Input.

**REF (Pin 13):** Reference Voltage Output. The 1.22V  $\pm 1\%$  reference should be bypassed with a  $0.1\mu F$  compensation capacitor. For  $V_{CC}=5V$  it can source 1mA.

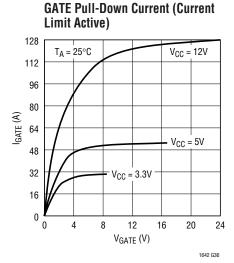

**GATE (Pin 14):** Gate Drive for the External N-Channel MOSFET. An internal charge pump provides at least 4.5V of gate drive and sources  $25\mu$ A. The pin requires an external series RC network to ground to compensate the current limit loop and to limit the ramp rate. A resistor of  $100\Omega$  is also recommended in series with the MOSFET

gate to suppress high frequency oscillations. GATE is immediately pulled to ground when the overvoltage comparator trips or the input supply is below the undervoltage lockout trip point. During current limit the GATE voltage is adjusted to maintain constant load current until the circuit breaker timer trips. At that point GATE is pulled to ground until the chip is reset. Clamp the GATE pin with an 18V zener diode (IN4705) to ground if the supply is 8V or higher.

**SENSE (Pin 15):** Current Sense Input. To use the current limit place a sense resistor in the supply path between  $V_{CC}$  and SENSE. When the drop across the resistor exceeds a threshold voltage, the GATE pin is adjusted to maintain a constant load current and the circuit breaker timer is started. A foldback feature reduces the current limit as the voltage at FB approaches ground. Short SENSE to  $V_{CC}$  to disable the current limiting.

$V_{CC}$  (Pin 16): Positive Supply Voltage. An internal undervoltage lockout circuit holds the GATE pin at ground until  $V_{CC}$  exceeds 2.73V. If  $V_{CC}$  exceeds 16.5V an internal shunt regulator protects the chip from  $V_{CC}$  and SENSE pin voltages up to 33V. In this case the GATE pin voltage will usually be low but this is not guaranteed; use the OV pin to ensure that the pass device is off. The  $V_{CC}$  pin also provides a high side connection to the SENSE resistor.

# **BLOCK DIAGRAM**

#### **Hot Circuit Insertion**

When a circuit board is inserted into a live backplane its supply bypass capacitors can draw large currents from the backplane power bus as they charge. These currents can permanently damage connector pins and can glitch the backplane supply, resetting other boards in the system. The LTC1642 limits the charging currents drawn by a board's capacitors, allowing safe insertion into a live backplane.

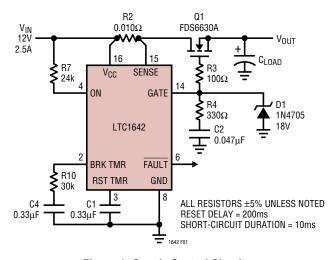

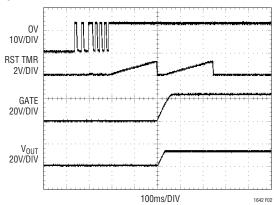

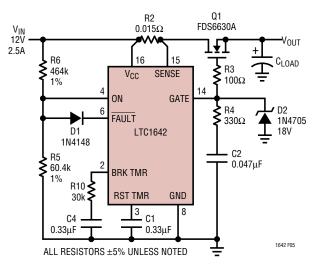

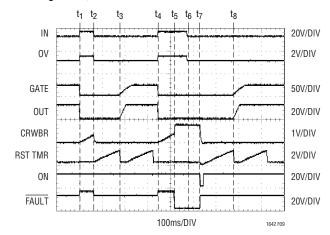

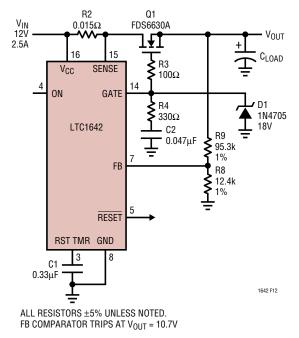

In the circuit shown in Figure 1 the LTC1642 and the external NMOS pass transistor Q1 work together to limit charging currents. Waveforms at board insertion are shown in Figure 2. When power is first applied to  $V_{CC}$  the chip holds Q1's gate at ground. After an adjustable delay a 25 $\mu$ A current source begins to charge the external capacitor C2, so choose C2 to limit the inrush current  $I_{INRUSH}$  charging the board's bypass capacitance  $C_{LOAD}$  according to the equation:

$$C2 = C_{LOAD} \bullet \frac{25\mu A}{I_{INRUSH}}$$

An internal charge pump supplies the  $25\mu A$  gate current, ensuring sufficient gate drive to Q1. At  $3VV_{CC}$  the minimum gate drive is 4.5V; at  $5VV_{CC}$  the minimum is 10V; at  $15VV_{CC}$  the minimum is again 4.5V, due to an internal zener clamp from the GATE pin to ground. Resistor R3 limits this zener's transient current during board insertion and removal and protects against high frequency oscillations in Q1. D1 provides additional protection against supply spikes.

Figure 1. Supply Control Circuitry

The delay before the GATE pin voltage begins ramping is determined by the system timer. It comprises an external capacitor C1 from the RST TMR pin to ground; an internal  $2\mu A$  current source feeding RSTTMR from  $V_{CC}$ ; an internal comparator, with the noninverting input tied to RST TMR and the inverting input tied to the 1.22V reference; and an internal NMOS pull-down. In standby, the NMOS holds RST TMR at ground. When the timer starts the NMOS turns off and the RST TMR voltage ramps up as the current source charges the capacitor. When RST TMR reaches 1.22V the timer comparator trips, the GATE voltage begins ramping up and RST TMR returns to ground. The timer delay is:

$$t_{RSTTMR} = (615ms/\mu F) C1.$$

The second RST TMR cycle indicates that  $V_{OUT}$  is within tolerance; it is discussed in the Undervoltage Monitor section.

Figure 2. Timing at Board Insertion

#### **Powering-Up in Current Limit**

Ramping the GATE pin voltage limits the current to  $I = 25\mu A \cdot C_{LOAD}/C2$ , where C2 is the external capacitor connected to the GATE and  $C_{LOAD}$  is the load capacitance. If the value of  $C_{LOAD}$  is uncertain, then a worst-case design can often result in needlessly long ramp times, and it may be better to limit the charging current by powering up in current limit.

### **Current Limiting and Solid-State Circuit Breaker**

The current can be limited by connecting a sense resistor between the LTC1642's  $V_{CC}$  and SENSE pins. When the voltage drop across this resistor reaches a limiting value,

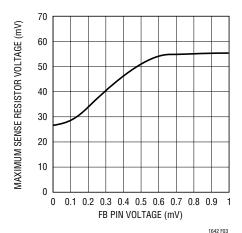

an internal servo loop adjusts the GATE pin voltage such that Q1 acts as a constant current source. The voltage limit across R2 increases as the output charges; this foldback in the current limit helps to even out Q1's power dissipation. The output is sensed at the FB pin. When FB is grounded, the sense voltage is limited to 26mV. When FB is greater than 0.7V, the limit is 56mV and the full dependence is shown in Figure 3.

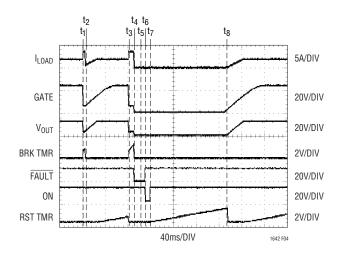

When the sense resistor voltage is 3mV below its limit, the circuit breaker timer starts. Once BRK TMR reaches its threshold, the circuit breaker opens, the GATE pin is pulled to ground (cutting off Q1) and FAULT is asserted.

The parameter  $V_{CB}$  specified in the DC electrical characteristics refers to the voltage difference between the  $V_{CC}$  and SENSE pins needed to start the circuit breaker timer. The limiting value maintained by the servo loop is 3mV higher than  $V_{CB}$ .

Should the sense resistor voltage drop below its limit before the timer trips, the GATE voltage begins ramping back up immediately and the BRK TMR pin returns to ground. However, due to the slow gate ramp, Q1 continues to dissipate substantial power for some time. Connecting R10 in series with timing capacitor C4 (as shown in Figure 1) ensures that the circuit breaker trips in the event of repetitive, but brief, load shorts. The delay before the circuit breaker opens is:

$t_{BRKTMR} = C4 (61k\Omega - R10).$

Once the circuit breaker trips, GATE and FAULT remain at ground until the chip is restarted. To restart, hold the ON

Figure 3. Foldback Current Limit

pin low for at least 2µs and FAULT will go high. Then take ON high again and the GATE will ramp up after a system timing cycle. Or, configure the LTC1642 to restart itself after the circuit breaker trips by connecting FAULT to the ON pin, as shown in the next section.

The servo loop controlling Q1 during current limit has a unity-gain frequency of about 125kHz. In Figure 1, R4 and C2 provide compensation. To ensure stability the product  $1/(2 \bullet \pi \bullet R4 \bullet C2)$  should be kept below the unity-gain frequency, and C2 should be more than Q1's input capacitance  $C_{ISS}$ . A good starting point for C2 is  $0.047\mu F$  and R4 is  $330\Omega$ . Keep  $R4 \ge 100\Omega$ .

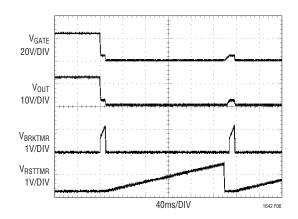

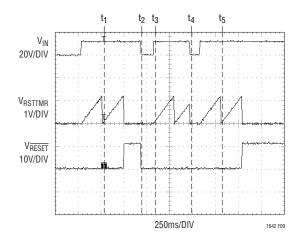

Typical waveforms during a load short to ground are shown in Figure 4. The load is shorted to ground at time 1. The GATE voltage drops until the load current equals its maximum limit, and the circuit breaker timer starts. The short is cleared at time 2, before the timer trips. The BRK TMR pin returns to ground, and the GATE voltage begins ramping up. At time 3 the load is shorted again and at time 4 the timer trips, pulling the GATE to ground and asserting FAULT. Although the short is cleared at time 5, FAULT doesn't go high until the ON pin is pulled low at time 6. At time 7 ON goes high and the system timer starts. When it trips at time 8 the GATE voltage begins ramping.

To disable current limit and electronic circuit breaker protection, tie the SENSE pin to  $V_{CC}$ , the BRK TMR pin to GND and omit compensating resistor R4.

Figure 4. Current Limit and Circuit Breaker Timing

#### **Automatic Restart After the Circuit Breaker Opens**

The LTC1642 will automatically attempt to restart itself after the circuit breaker opens if the FAULT output is tied to the ON pin. The circuit is shown in Figure 5. Diode D1 blocks the weak FAULT pull-up current source from unbalancing the R6-R5 divider.

During a continuous current limit such as a load short, Q1's duty cycle is equal to the circuit breaker timer period, divided by the sum of the circuit breaker and system timer periods:

Short-Circuit Duty Cycle =

$$\frac{C4}{C4 + 10 \cdot C1}$$

The duty cycle is 9% for the Figure 5 circuit. Waveforms during a load short are shown in Figure 6.

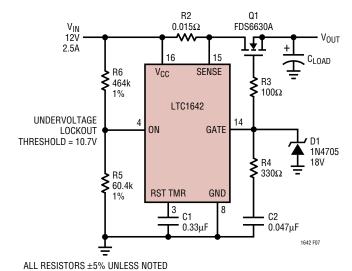

#### **Undervoltage Lockout**

An internal undervoltage lockout circuit holds the charge pump off until  $V_{CC}$  exceeds 2.73V. If  $V_{CC}$  falls below 2.5V, it turns off the charge pump and clears overvoltage and current limit faults.

For higher lockout thresholds tie the ON pin to a resistor divider driven from  $V_{CC}$ , as shown in Figure 7. This circuit keeps the charge pump off until  $V_{CC}$  exceeds  $(1+R6/R5) \cdot 1.34V$ , and also turns it off if  $V_{CC}$  falls below  $(1+R6/R5) \cdot 1.22V$ .

Figure 5. Automatic Restart Circuit

Figure 6. Automatic Retry Following a Load Short

Figure 7. Setting a Higher Undervoltage Lockout

### **Overvoltage Protection**

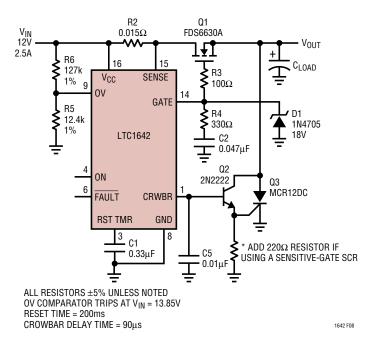

The LTC1642 can protect a load from overvoltages by turning off the pass transistor if the supply voltage exceeds an adjustable limit, and by triggering a crowbar SCR if the overvoltage lasts longer than an adjustable time. The part can also be configured to automatically restart when the overvoltage clears.

The overvoltage protection circuitry is shown in Figure 8. The external components comprise a resistor divider driving the OV pin, timing capacitor C5, NPN emitter follower Q2, and crowbar SCR Q3. Because the MCR12DC is not a sensitive-gate device, the optional resistor shunting the SCR gate to ground is omitted. The internal components comprise a comparator, 1.22V bandgap reference, two current sources, and a timer at the CRWBR pin. When V<sub>CC</sub> exceeds (1+R6/R5) • 1.22V the comparator's output goes high and internal logic turns off Q1 and starts the timer. This timer has a 0.410V threshold and uses the CRWBR pin; when CRWBR reaches 0.410V the timer comparator trips, and the current sourced from V<sub>CC</sub> increases to 1.5mA. Emitter follower Q2 boosts this current to trigger crowbar SCR Q3. The ramp time ∆t needed to trip the comparator is:

$t_{CRWBR} = 9.1 (ms/\mu F) C5$

Figure 8. Overvoltage Protection Circuitry

Once the CRWBR timer trips the LTC1642 latches off: after the overvoltage clears GATE and FAULT remain at ground and CRWBR continues sourcing 1.5mA. To restart the part after the overvoltage clears, hold the ON pin low for at least 2µs and then bring it high. The GATE voltage will begin ramping up one system timing cycle later. The part will restart itself if FAULT and ON are connected.

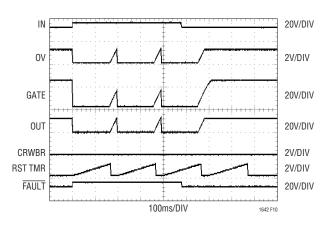

Figure 9 shows typical waveforms when the divider is driven from  $V_{CC}$ . The OV comparator goes high at time 1, causing the chip to pull the GATE pin to ground and start the CRWBR timer. At time 2, before the timer's comparator trips, OV falls below its threshold; the timer resets and GATE begins charging one system timing cycle later at time 3. Another overvoltage begins at time 4, and at time 5 the CRWBR timer trips; FAULT goes low and the CRWBR pin begins sourcing 1.5mA. Even after OV falls below 1.22V at time 6, GATE and FAULT stay low, and CRWBR continues to source 1.5mA. FAULT goes high when ON goes low at time 7, and GATE begins charging at time 8, one RST TMR cycle after FAULT goes high.

Figure 10 shows typical waveforms when the OV divider is driven from the N-Channel's output side. Because the voltage driving the divider collapses after the OV comparator trips, FAULT stays high and CRWBR stays near ground, which prevents the pin from triggering an SCR. The GATE voltage begins ramping up after a RST TMR timing cycle.

To disable overvoltage protection completely, tie the OV and CRWBR pins to GND. For overvoltage protection at the GATE pin, but without latch off or a crowbar SCR such as Q3 in Figure 1, tie CRWBR to GND.

Figure 9. Overvoltage Timing (Input Side)

#### **Automatic Restart**

If there is an overvoltage, and the resistor divider feeding OV is connected to the output of the N-Channel pass transistor, the LTC1642 will automatically restart even if FAULT is not tied to ON. If the divider is connected to the input side, the LTC1642 will restart itself only if FAULT is tied to ON, and only after the overvoltage clears.

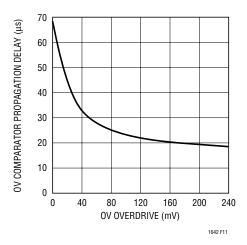

## The OV and FB Comparators

The propagation delay through the OV and FB comparators on low to high transitions depends strongly on the differential input voltage. The relationship is shown in Figure 11. The minimum propagation delay for large overdrives is about  $20\mu s$ . In addition the comparators have 3mV of hysteresis.

#### **Internal Voltage Clamp Protection**

The LTC1642 includes a shunt regulator to protect itself from  $V_{CC}$  and SENSE pin voltages up to 33V. The regulator turns on when  $V_{CC}$  exceeds 16.5V and limits most of the chip's circuitry to 15V. When it is on the chip functions normally with one exception: if the charge pump is on, the GATE voltage is usually near ground but this is not guaranteed. Use the OV pin to ensure that GATE is grounded.

The pull-up voltage on the  $\overline{RESET}$  and  $\overline{FAULT}$  pins follows  $V_{CC}$  until the shunt regulator turns on. When the regulator is on the pull-up voltage is 14.4V.

### **Undervoltage Monitor**

The LTC1642 will assert RESET if a monitored voltage falls below an adjustable minimum. When the monitored voltage has exceeded its minimum for at least one system timing cycle, RESET goes high. The monitoring circuitry comprises an internal 1.22V bandgap reference, an internal precision voltage comparator and an external resistive divider to monitor the output supply voltage.

The circuit is shown in Figure 12, and typical waveforms in Figure 13. When the voltage at the FB pin rises above its reset threshold (1.22V), the comparator output goes low and a timing cycle starts (times 1 and 5). Following the cycle RESET is pulled high. At time 2 the voltage at FB drops below the comparator's threshold and RESET is pulled low. If the FB pin rises above the reset threshold for less than a timing cycle the RESET output will remain low (time 3 to time 4). The 15 $\mu$ A pull-up current source to V<sub>CC</sub> on RESET has a series diode so the pin can be pulled above V<sub>CC</sub> by an external pull-up resistor without forcing current back into the supply.

Figure 10. Overvoltage Timing (Output Side)

Figure 11. OV Comparator Propagation Delay vs Overdrive Voltage

The undervoltage monitor behaves differently if FB is <u>above</u> its threshold when the GATE begins ramping: RESET goes high as soon as the GATE ramp begins.

RESET goes low immediately if  $V_{CC}$  falls below the chip's 2.5V internal undervoltage lockout threshold.

To disable the undervoltage monitor, tie FB to REF and ground RESET.

#### Reference

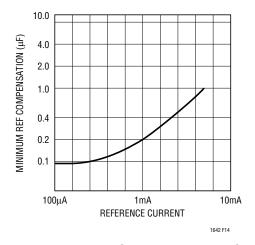

The LTC1642's internal voltage reference is buffered and brought out to the REF pin. The buffer amplifier should be compensated with a capacitor connected between REF and ground. If no DC current is drawn from REF,  $0.1\mu F$  ensures an adequate phase margin, but the minimum compensation increases if REF sources a substantial DC current, as shown in Figure 14.

Figure 12. Undervoltage Monitoring Circuitry

Figure 13. Supply Monitor Waveforms

Figure 14. Minimum REF Compensation vs REF Current

LINEAR TECHNOLOGY

### **Uncommitted Comparator**

The uncommitted comparator has an open drain output. The comparator has 3mV of hysteresis: the output goes high when the differential input voltage exceeds 1.5mV and goes low when the differential input is less than -1.5mV.

The comparator's input transistors are MOSFETs so the input bias and offset currents are very small: typically picoamps at 25°C, increasing to nanoamps at 90°C. If the auxiliary comparator is unused, the COMP+, COMP- and COMPOUT pins may be left floating.

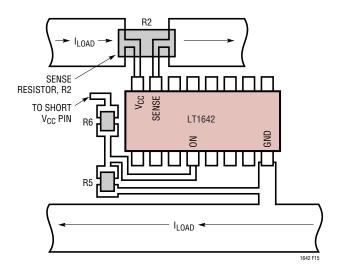

#### **Layout Considerations**

One ounce copper exhibits a sheet resistance of  $530\mu\Omega$  per square. To minimize self-heating, traces should be at least 0.02" wide per ampere of current and 0.03" is recommended.

In high current applications, the voltage drop along traces can be appreciable. Connect the LTC1642's  $V_{CC}$  and SENSE pins *directly* across sense resistor R2 to prevent the power trace's resistance from adding to R2. It is also a good practice to keep the resistor divider to the ON pin close to the chip and the divider's connections to the  $V_{CC}$  and GND pins short. Figure 15 shows an example layout.

Figure 15. Recommended Layout for R1, R2 and R5

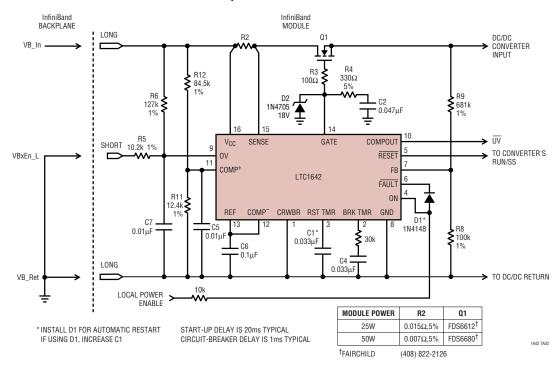

## TYPICAL APPLICATION

#### 12V Hot Swap Circuit for InfiniBand Modules

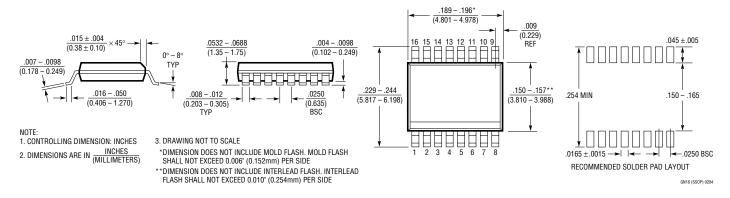

## PACKAGE DESCRIPTION

#### **GN Package** 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

## **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                            | COMMENTS                                                  |

|-------------|--------------------------------------------------------|-----------------------------------------------------------|

| LTC1421     | Hot Swap Controller                                    | Two Supplies from 3V to 12V and -12V                      |

| LTC4211     | Hot Swap Controller with Multifunction Current Control | Single Supply from 2.5V to 16.5V, MSOP Package            |

| LT4250      | Negative Voltage Hot Swap Controller in SO-8           | -48V Supplies, Active Current Limit                       |

| LTC1643     | PCI-Bus Hot Swap Controller                            | 3.3V, 5V, ±12V Supplies for PCI Bus, Active Current Limit |

|             | ·                                                      | 1642fb                                                    |

LT/LT 0805 REV B • PRINTED IN USA © LINEAR TECHNOLOGY CORPORATION 1999