## S72VS-R MCP

256 Mb (16M x 16 bit), 1.8V Burst Mode Flash DDR DRAM on Split Bus

# Features

- Power supply voltage of 1.7V to 1.95V

- Burst Speeds

Flash = 83 MHz or 108 MHz

DDR DRAM = 166 MHz

- Packages 8.0 × 8.0 mm, 133-ball MCP

- Operating Temperature

□ Wireless, -25 °C to +85 °C

□ Industrial, -40 °C to +85 °C

# **General Description**

This document contains information on the S72VS-R MCP stacked products. Refer to the S29VS/XS-R datasheet (002-00833) for full electrical specifications of the Flash memory component.

The S72VS Series is a product line of stacked products (MCPs), and consists of:

- S29VS family Address-Data Multiplexed Flash memory die

- DDR DRAM

The products covered by this document are listed in the below tables below.

| Flash Density | DRAM Density (256 Mb) |

|---------------|-----------------------|

| 256 Mb        | S72VS256RE0           |

# **DDR Specification Reference**

| Density | Reference Name                 | Document Identification Number |

|---------|--------------------------------|--------------------------------|

| 256 Mb  | 256 Mb (16M x 16 bit) DDR DRAM | SDM256D166D1R/D3R              |

### **Electronic Serial Number**

For applicable devices, the Factory Secured Silicon Area contains a random, 128-bit ESN, stored in the address range 000000h-000007h.

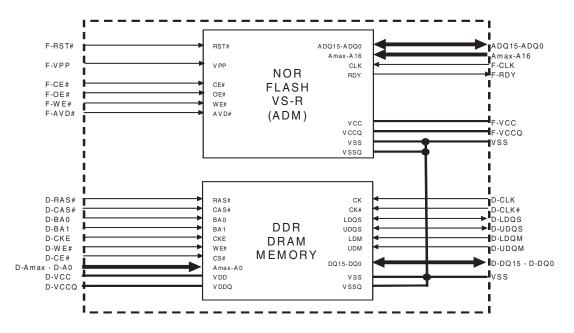

### Product Block Diagram

#### Notes

1. Amax indicates highest address bit for memory component: a. Amax = A23 for VS256R.

b. Amax = A12 for 256 Mb DDR DRAM.

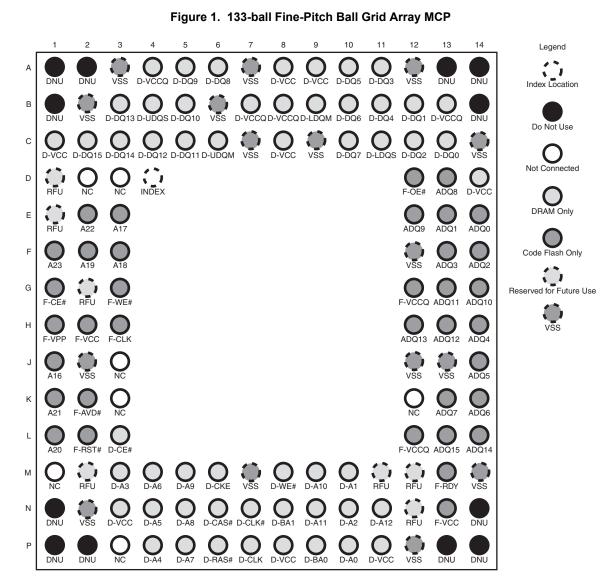

### **Connection Diagrams**

| MCP         | Flash Amax | DDR DRAM Density | D-Amax |  |

|-------------|------------|------------------|--------|--|

| S72VS256RE0 | A23        | 256 Mb           | D-A12  |  |

## Input/Output Description

#### Table 1. Input/Output Description

| Symbol          | Symbol Description                                                                                                                                                                                                                                                                              |   |   |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|--|--|

| Amax – A16      | Flash Address inputs                                                                                                                                                                                                                                                                            | Х | _ |  |  |

| ADQ15 – ADQ0    | Flash multiplexed Address and Data                                                                                                                                                                                                                                                              | Х | _ |  |  |

| F-CE#           | Flash Chip-enable input.                                                                                                                                                                                                                                                                        | Х | _ |  |  |

| F-OE#           | Flash Output Enable input. Asynchronous relative to CLK for Burst mode.                                                                                                                                                                                                                         | Х | _ |  |  |

| F-WE#           | Flash Write Enable input                                                                                                                                                                                                                                                                        | Х | _ |  |  |

| F-VCC           | Flash device power supply (1.7 V to 1.95 V)                                                                                                                                                                                                                                                     | Х | _ |  |  |

| F-VCCQ          | Flash Input/Output Buffer power supply                                                                                                                                                                                                                                                          | Х | _ |  |  |

| VSS             | Ground                                                                                                                                                                                                                                                                                          | Х | Х |  |  |

| F-RDY           | Flash ready output. Indicates the status of the Burst read. $V_{OL}$ = data invalid. $V_{OH}$ = data valid.                                                                                                                                                                                     | х | _ |  |  |

| F-CLK           | Flash Clock. The first rising edge of CLK in conjunction with AVD# low latches the address input and activates burst mode operation. After the initial word is output, subsequent rising edges of CLK increment the internal address counter. CLK should remain low during asynchronous access. | х | _ |  |  |

| F-AVD#          | Flash Address Valid input. Indicates to device that the valid address is present on the address inputs. $V_{IL}$ = for asynchronous mode, indicates valid address; for burst mode, causes starting address to be latched on rising edge of CLK. $V_{IH}$ = device ignores address inputs        | Х | _ |  |  |

| F-RST#          | Flash hardware reset input. $V_{\rm IL}\text{=}$ device resets and returns to reading array data                                                                                                                                                                                                | х | _ |  |  |

| F-VPP           | Flash accelerated input. At V <sub>HH</sub> , accelerates programming; automatically places device in unlock bypass mode. At V <sub>IL</sub> , disables all program and erase functions. Should be at V <sub>IH</sub> for all other conditions.                                                 | Х | _ |  |  |

| D-Amax – D-A0   | DRAM Address inputs.                                                                                                                                                                                                                                                                            | _ | Х |  |  |

| D-DQ15 – D-DQ0  | DRAM Data input/output                                                                                                                                                                                                                                                                          | _ | Х |  |  |

| D-CLK           | DRAM System Clock                                                                                                                                                                                                                                                                               | _ | Х |  |  |

| D-CE#           | DRAM Chip Select                                                                                                                                                                                                                                                                                | _ | Х |  |  |

| D-CKE           | DRAM Clock Enable                                                                                                                                                                                                                                                                               | _ | Х |  |  |

| D-BA1 – BA0     | DRAM Bank Select                                                                                                                                                                                                                                                                                | _ | Х |  |  |

| D-RAS#          | DRAM Row Address Strobe                                                                                                                                                                                                                                                                         | _ | Х |  |  |

| D-CAS#          | DRAM Column Address Strobe                                                                                                                                                                                                                                                                      | _ | Х |  |  |

| D-UDQM – D-LDQM | DRAM Data Input Mask                                                                                                                                                                                                                                                                            | _ | Х |  |  |

| D-WE#           | DRAM Write Enable input                                                                                                                                                                                                                                                                         | _ | Х |  |  |

| D-VCCQ          | DRAM Input/Output Buffer power supply                                                                                                                                                                                                                                                           | _ | х |  |  |

| D-VCC           | DRAM device power supply                                                                                                                                                                                                                                                                        | _ | х |  |  |

| D-UDQS          | DRAM Upper Data Strobe, output with read data and input with write data                                                                                                                                                                                                                         | _ | х |  |  |

| D-LDQS          | DRAM Lower Data Strobe, output with read data and input with write data                                                                                                                                                                                                                         | _ | х |  |  |

| D-CLK#          | DDR Clock for negative edge of CLK                                                                                                                                                                                                                                                              | _ | Х |  |  |

#### Table 1. Input/Output Description (Continued)

| Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Flash | RAM |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| RFU    | Reserved for Future Use. No device internal signal is currently connected to the package connector but there is potential future use for the connector for a signal. It is recommended to not use RFU connectors for PCB routing channels so that the PCB may take advantage of future enhanced features in compatible footprint devices.                                                                                                                                                                                                             | _     | _   |

| NC     | Not Connected. No device internal signal is connected to the package connector nor is there any future plan to use the connector for a signal. The connection may safely be used for routing space for a signal on a Printed Circuit Board (PCB).                                                                                                                                                                                                                                                                                                     | _     | _   |

| DNU    | Do Not Use. A device internal signal may be connected to the package connector. The connection may be used by Spansion for test or other purposes and is not intended for connection to any host system signal. Any DNU signal related function will be inactive when the signal is at $V_{IL}$ . The signal has an internal pull-down resistor and may be left unconnected in the host system or may be tied to $V_{SS}$ . Do not use these connections for PCB signal routing channels. Do not connect any host system signal to these connections. | _     | _   |

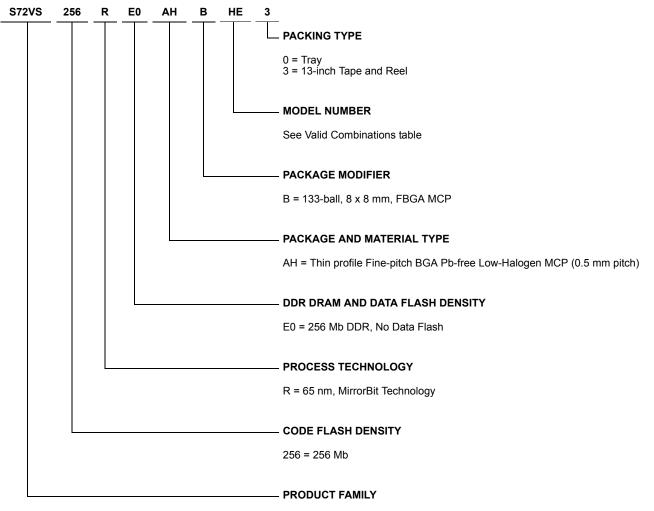

## **Ordering Information**

The order number (Valid Combination) is formed by the following:

S72VS Multi-Chip Product (MCP) 1.8V Address-Data Multiplexed, SRW, Burst Mode Flash and DDR DRAM on Split Bus

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| Base OPN    | Package | Model<br>Number | Packing<br>Type     | Flash<br>Boot | Temp<br>Range | Electronic<br>Serial<br>Number | Flash<br>Density | DDR<br>DRAM<br>Density | Flash<br>Speed<br>(MHz) | DRAM<br>Speed<br>(MHz) | DRAM<br>Specification | Package                                  |

|-------------|---------|-----------------|---------------------|---------------|---------------|--------------------------------|------------------|------------------------|-------------------------|------------------------|-----------------------|------------------------------------------|

| S72VS256RE0 | AHB     | H1              |                     | Тор           | Wireless      | Yes                            | 256 Mb           | lb 256 Mb              | 108                     | 166                    | SDM256D166D<br>1R     | 8.0 x 8.0 mm<br>133-ball MCP<br>(RSC133) |

|             |         | J1              | 0. 3 <sup>[2]</sup> | Bottom        | WII CICSS     | No                             |                  |                        |                         |                        |                       |                                          |

|             |         | НН              | 0, 3                | Тор           | - Industrial  | Yes                            |                  |                        |                         |                        | SDM256D166D           |                                          |

|             |         | JH              |                     | Bottom        |               | Yes                            |                  |                        |                         |                        | 3R                    |                                          |

Note

Packing Type 0 is standard. Specify other options as required.

BGA package marking omits leading "S" and packing type designator from ordering part number.

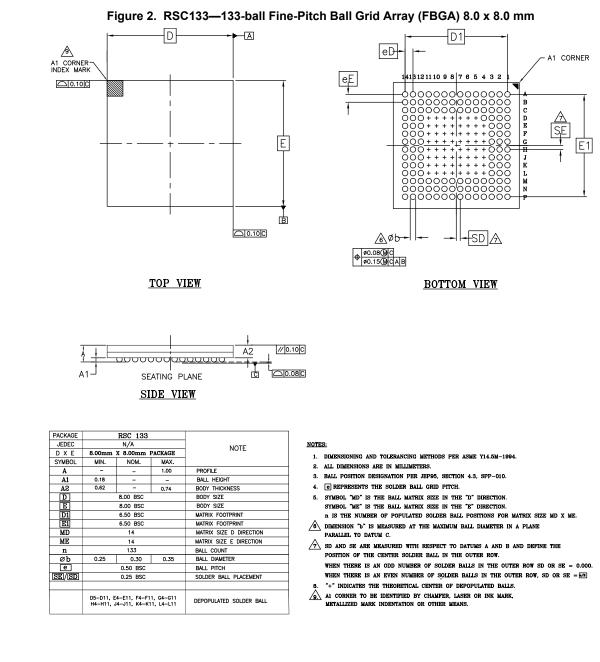

#### **Physical Dimensions**

3643/16-038.63/12.16.09

# **Revision History**

# **Document History Page**

| Document Title: S72VS-R MCP, 256 Mb (16M x 16 bit), 1.8V Burst Mode Flash DDR DRAM on Split Bus<br>Document Number: 002-00773 |         |                    |                    |                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision                                                                                                                      | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                              |  |

| **                                                                                                                            | _       | _                  | 07/21/2010         | Initial release                                                                                                                                    |  |

| *A                                                                                                                            | _       | _                  | 08/24/2010         | Global: Added information for OPN S72VS256RE0AHBH1                                                                                                 |  |

| *В                                                                                                                            | _       | _                  | 12/10/2010         | Global: Updated 256 Mb DRAM specification reference                                                                                                |  |

| *C                                                                                                                            | _       | _                  | 03/18/2011         | Global: Added OPN S72VS256RE0AHBJ1                                                                                                                 |  |

| *D                                                                                                                            | _       | _                  | 10/05/2011         | Ordering Information: Replaced Product Selector Guide section<br>Valid Combinations:<br>Made a separate section<br>Added OPNs: S72VS256RE0AHBHH/JH |  |

| *E                                                                                                                            | _       | _                  | 04/17/2012         | Ordering Information: Added ESN support for S72VS256RE0AHBH1                                                                                       |  |

| *F                                                                                                                            | 5185100 | TOCU               | 03/22/2016         | Updated to Cypress template.<br>Removed any occurrence of 128 Mb and 8M in the document.                                                           |  |

### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Lighting & Power Control                              | cypress.com/powerpsoc  |

| Memory                                                | cypress.com/memory     |

| PSoC                                                  | cypress.com/psoc       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless/RF                                           | cypress.com/wireless   |

#### **PSoC<sup>®</sup> Solutions**

cypress.com/psoc PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/support

© Cypress Semiconductor Corporation 2010-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.