### LTC6915

Zero Drift, Precision Instrumentation Amplifier with Digitally Programmable Gain

### FEATURES

- 14 Levels of Programmable Gain

- 125dB CMRR Independent of Gain

- Gain Accuracy 0.1% (Typ)

- Maximum Offset Voltage of 10µV

- Maximum Offset Voltage Drift: 50nV/°C

- Rail-to-Rail Input and Output

- Parallel or Serial (SPI) Interface for Gain Setting

- Supply Operation: 2.7V to ±5.5V

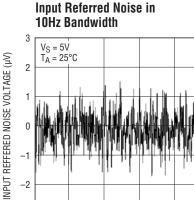

- Typical Noise: 2.5µV<sub>P-P</sub> (0.01Hz to 10Hz)

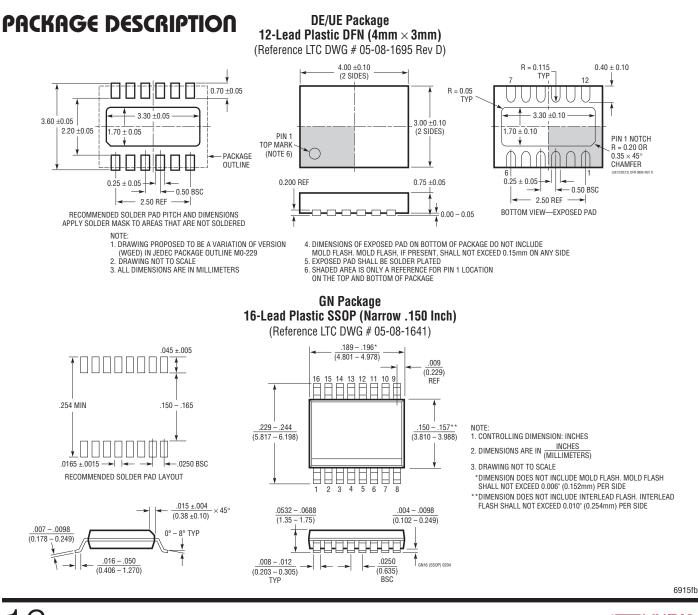

- 16-Lead SSOP and 12-Lead DFN Packages

### **APPLICATIONS**

- Thermocouple Amplifiers

- Electronic Scales

- Medical Instrumentation

- Strain Gauge Amplifier

- High Resolution Data Acquisition

### DESCRIPTION

The LTC<sup>®</sup>6915 is a precision programmable gain instrumentation amplifier. The gain can be programmed to 0, 1, 2, 4, 8, 16, 32, 64, 128, 256, 512, 1024, 2048, or 4096 through a parallel or serial interface. The CMRR is typically 125dB with a single 5V supply with any programmed gain. The offset is below 10 $\mu$ V with a temperature drift of less than 50nV/°C.

The LTC6915 uses charge balanced sampled data techniques to convert a differential input voltage into a single ended signal that is in turn amplified by a zero-drift operational amplifier.

The differential inputs operate from rail-to-rail and the single-ended output swings from rail-to-rail. The LTC6915 can be used in single power supply applications as low as 2.7V, or with dual ±5V supplies. The LTC6915 is available in a 16-lead SSOP package and a 12-lead DFN surface mount package.

**Δ7**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners

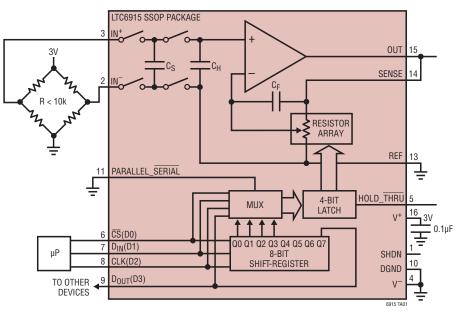

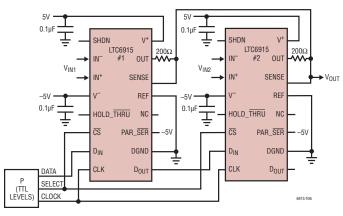

### TYPICAL APPLICATION

Differential Bridge Amplifier with Gain Programmed through the Serial Interface

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| Total Supply Voltage (V <sup>+</sup> to V <sup>-</sup> ) | 11V                              |

|----------------------------------------------------------|----------------------------------|

| Input Current                                            | ±10mA                            |

| $ V_{IN}^+ - V_{REF} $                                   | 5.5V                             |

| $ V_{IN}^ V_{REF} $                                      | 5.5V                             |

| $ V^+ - V_{DGND} $                                       | 5.5V                             |

| $ V_{DGND} - V^- $                                       | 5.5V                             |

| Digital Input Voltage                                    | V <sup>-</sup> to V <sup>+</sup> |

| Operating Temperature Range                              |                                  |

| LTC6915C                                                 | 0°C to 70°C                      |

| LTC6915I<br>LTC6915H                 |                |

|--------------------------------------|----------------|

| Junction Temperature                 | 40 0 10 125 0  |

| (GN Package)                         | 150°C          |

| (DFN Package)                        | 125°C          |

| Storage Temperature                  |                |

| (GN Package)                         | –65°C to 150°C |

| (DFN Package)                        | –65°C to 125°C |

| Lead Temperature (Soldering 10 sec). | 300°C          |

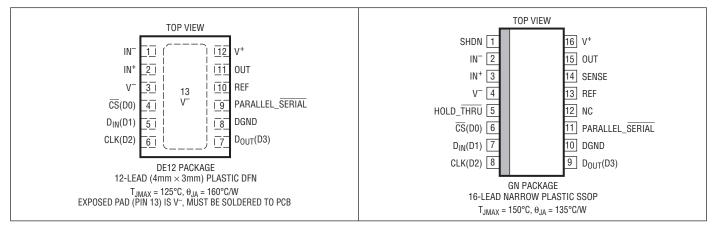

### PIN CONFIGURATION

### ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL    | PART MARKING  | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|------------------|---------------|---------------------------------|-------------------|

| LTC6915CDE#PBF    | LTC6915CDE#TRPBF | 6915          | 12-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC6915IDE#PBF    | LTC6915IDE#TRPBF | 69151         | 12-Lead (4mm × 3mm) Plastic DFN | –40°C to 85°C     |

| LTC6915CGN#PBF    | LTC6915CGN#TRPBF | 6915          | 16-Lead Narrow Plastic SSOP     | 0°C to 70°C       |

| LTC6915IGN#PBF    | LTC6915IGN#TRPBF | 69151         | 16-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC6915HGN#PBF    | LTC6915HGN#TRPBF | 6915H         | 16-Lead Narrow Plastic SSOP     | -40°C to 125°C    |

| LEAD BASED FINISH | TAPE AND REEL    | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

| LTC6915CDE        | LTC6915CDE#TR    | 6915          | 12-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC6915IDE        | LTC6915IDE#TR    | 69151         | 12-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC6915CGN        | LTC6915CGN#TR    | 6915          | 16-Lead Narrow Plastic SSOP     | 0°C to 70°C       |

| LTC6915IGN        | LTC6915IGN#TR    | 69151         | 16-Lead Narrow Plastic SSOP     | -40°C to 85°C     |

| LTC6915HGN        | LTC6915HGN#TR    | 6915H         | 16-Lead Narrow Plastic SSOP     | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ .

| SYMBOL          | PARAMETER                                                 | CONDITIONS                                                                                                                                                                                                                                                                                       |                  | MIN                           | ТҮР               | MAX         | UNITS                      |

|-----------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|-------------------|-------------|----------------------------|

| V+ = 3V, V-     | = 0V, V <sub>REF</sub> = 200mV                            | ,                                                                                                                                                                                                                                                                                                |                  |                               |                   |             |                            |

|                 | Gain Error (Note 2)                                       | $A_V = 1 (R_L = 10k)$                                                                                                                                                                                                                                                                            |                  | -0.075                        | 0                 | 0.075       | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 2 to 32 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                                  | •                | -0.5                          | 0                 | 0.5         | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 64 to 1024 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                               | •                | -0.6                          | -0.1              | 0.6         | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 2048, 4096 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                               | •                | -1                            | -0.2              | 1.0         | %                          |

|                 | Gain Nonlinearity                                         | A <sub>V</sub> = 1                                                                                                                                                                                                                                                                               | •                |                               | 3                 | 15          | ppm                        |

| V <sub>OS</sub> | Input Offset Voltage (Note 3)                             | V <sub>CM</sub> = 200mV                                                                                                                                                                                                                                                                          |                  |                               | -3                | ±10         | μV                         |

|                 | Average Input Offset Drift (Note 3)                       | $T_A = -40^{\circ}$ C to 85°C<br>$T_A = 85^{\circ}$ C to 125°C                                                                                                                                                                                                                                   | •                |                               |                   | ±50<br>±100 | nV/°C<br>nV/°C             |

| IB              | Average Input Bias Current (Note 4)                       | V <sub>CM</sub> = 1.2V                                                                                                                                                                                                                                                                           |                  |                               | 5                 | 10          | nA                         |

| l <sub>os</sub> | Average Input Offset Current (Note 4)                     | V <sub>CM</sub> = 1.2V                                                                                                                                                                                                                                                                           | •                |                               | 1.5               | 3           | nA                         |

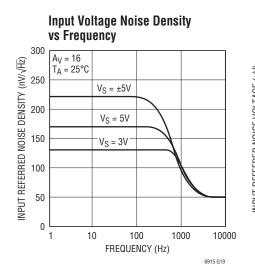

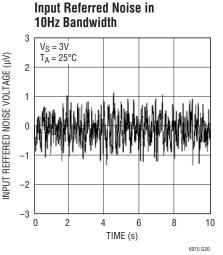

| en              | Input Noise Voltage                                       | DC to 10Hz                                                                                                                                                                                                                                                                                       |                  |                               | 2.5               |             | μV <sub>P-P</sub>          |

| V+ = 3V, V-     | = 0V, V <sub>REF</sub> = 200mV                            |                                                                                                                                                                                                                                                                                                  |                  |                               |                   |             |                            |

| CMRR            | Common Mode Rejection Ratio                               | $ \begin{array}{l} A_V = 1024,  V_{CM} = 0V \ to \ 3V,  LTC6915C \\ A_V = 1024,  V_{CM} = 0.1V \ to \ 2.9V,  LTC6915I \\ A_V = 1024,  V_{CM} = 0V \ to \ 3V,  LTC6915I \\ A_V = 1024,  V_{CM} = 0.1V \ to \ 2.9V,  LTC6915H \\ A_V = 1024,  V_{CM} = 0V \ to \ 2.97V,  LTC6915H \\ \end{array} $ | •<br>•<br>•<br>• | 100<br>100<br>95<br>100<br>85 | 119<br>119<br>119 |             | dB<br>dB<br>dB<br>dB<br>dB |

| PSRR            | Power Supply Rejection Ratio (Note 5)                     | V <sub>S</sub> = 2.7V to 6V                                                                                                                                                                                                                                                                      | •                | 110                           | 116               |             | dB                         |

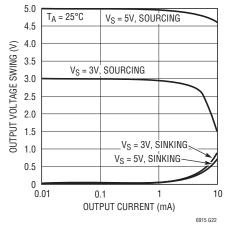

|                 | Output Voltage Swing High (Referenced to V <sup>-</sup> ) | Sourcing 200µA<br>Sourcing 2mA                                                                                                                                                                                                                                                                   | •                | 2.95<br>2.75                  | 2.98<br>2.87      |             | V<br>V                     |

|                 | Output Voltage Swing Low (Referenced to V <sup>-</sup> )  | Sinking 200µA<br>Sinking 2mA                                                                                                                                                                                                                                                                     | •                |                               | 18<br>130         | 50<br>300   | mV<br>mV                   |

|                 | Supply Current, Parallel Mode                             | No Load at OUT, $V_{CM}$ = 200mV                                                                                                                                                                                                                                                                 | •                |                               | 0.88              | 1.3         | mA                         |

|                 | Supply Current, Serial Mode (Note 6)                      | No Load at OUT, Capacitive Load at $D_{OUT}$ (C <sub>L</sub> ) = 15pF, Continuous CLK Frequency = 4MHz, $\overline{CS}$ = LOW, Gain Control Code = 0001                                                                                                                                          | •                |                               | 1.1               | 1.65        | mA                         |

|                 | Supply Current Shutdown                                   | V <sub>SHDN</sub> = 2.7V (Hardware Shutdown)<br>V <sub>SHDN</sub> = 1V, Gain Control Code = 0000<br>(Software Shutdown)                                                                                                                                                                          | •                |                               | 1<br>125          | 4<br>180    | μΑ<br>μΑ                   |

|                 | SHDN Input High                                           |                                                                                                                                                                                                                                                                                                  | •                | 2.7                           |                   |             | V                          |

|                 | SHDN Input Low                                            |                                                                                                                                                                                                                                                                                                  |                  |                               |                   | 1           | V                          |

|                 | SHDN and HOLD_THRU Input Current (Note 2)                 |                                                                                                                                                                                                                                                                                                  |                  |                               |                   | 5           | μA                         |

|                 | Internal Op Amp Gain Bandwidth                            |                                                                                                                                                                                                                                                                                                  |                  |                               | 200               |             | kHz                        |

|                 | Slew Rate                                                 |                                                                                                                                                                                                                                                                                                  |                  |                               | 0.2               |             | V/µs                       |

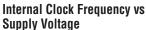

|                 | Internal Sampling Frequency                               |                                                                                                                                                                                                                                                                                                  |                  |                               | 3                 |             | kHz                        |

| $V^+ = 5V, V^-$ | = 0V, V <sub>REF</sub> = 200mV                            |                                                                                                                                                                                                                                                                                                  |                  |                               |                   |             |                            |

|                 | Gain Error (Note 2)                                       | $A_V = 1 \ (R_L = 10k)$                                                                                                                                                                                                                                                                          | •                | -0.075                        | 0                 | 0.075       | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 2 to 32 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                                  | •                | -0.5                          | 0                 | 0.5         | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 64 to 1024 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                               |                  | -0.6                          | -0.1              | 0.6         | %                          |

|                 | Gain Error (Note 2)                                       | A <sub>V</sub> = 2048, 4096 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                               |                  | -1                            | -0.2              | 1           | %                          |

|                 | Gain Nonlinearity                                         | A <sub>V</sub> = 1                                                                                                                                                                                                                                                                               | •                |                               | 3                 | 15          | ppm                        |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| V <sub>OS</sub>        | Input Offset Voltage (Note 3)                 | V <sub>CM</sub> = 200mV                                                                                                                                                                                                                                                                     |                  |                               | -3                | ±10         | μV                         |

|------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------|-------------------|-------------|----------------------------|

|                        | Average Input Offset Drift (Note 3)           | $ \begin{array}{l} T_A = -40^\circ C \ to \ 85^\circ C \\ T_A = 85^\circ C \ to \ 125^\circ C \end{array} $                                                                                                                                                                                 | •                |                               |                   | ±50<br>±100 | nV/°C<br>nV/°C             |

|                        | Average Input Bias Current (Note 4)           | V <sub>CM</sub> = 1.2V                                                                                                                                                                                                                                                                      |                  |                               | 5                 | 10          | nA                         |

| l <sub>OS</sub>        | Average Input Offset Current (Note 4)         | V <sub>CM</sub> = 1.2V                                                                                                                                                                                                                                                                      |                  |                               | 1.5               | 3           | nA                         |

| CMRR                   | Common Mode Rejection Ratio                   | $\begin{array}{l} A_V = 1024,  V_{CM} = 0V \ to \ 5V,  LTC6915C \\ A_V = 1024,  V_{CM} = 0.1V \ to \ 4.9V,  LTC6915I \\ A_V = 1024,  V_{CM} = 0V \ to \ 5V,  LTC6915I \\ A_V = 1024,  V_{CM} = 0.1V \ to \ 4.9V,  LTC6915H \\ A_V = 1024,  V_{CM} = 0V \ to \ 4.97V,  LTC6915H \end{array}$ | •<br>•<br>•<br>• | 105<br>105<br>95<br>100<br>85 | 125<br>125<br>125 |             | dB<br>dB<br>dB<br>dB<br>dB |

| PSRR                   | Power Supply Rejection Ratio (Note 5)         | V <sub>S</sub> = 2.7V to 6V                                                                                                                                                                                                                                                                 |                  | 110                           | 116               |             | dB                         |

|                        | Output Voltage Swing High                     | Sourcing 200µA<br>Sourcing 2mA                                                                                                                                                                                                                                                              | •                | 4.95<br>4.80                  | 4.99<br>4.93      |             | V<br>V                     |

|                        | Output Voltage Swing Low                      | Sinking 200µA<br>Sinking 2mA                                                                                                                                                                                                                                                                | •                |                               | 17<br>120         | 50<br>300   | mV<br>mV                   |

| V <sup>+</sup> = 5V, V | / <sup>-</sup> = 0V, V <sub>REF</sub> = 200mV |                                                                                                                                                                                                                                                                                             |                  |                               |                   |             |                            |

|                        | Supply Current, Parallel Mode                 | No Load at OUT, V <sub>CM</sub> = 200mV                                                                                                                                                                                                                                                     |                  |                               | 0.95              | 1.48        | mA                         |

|                        | Supply Current, Serial Mode (Note 6)          | No Load at OUT, Capacitive Load at $D_{OUT}$ (C <sub>L</sub> ) = 15pF, Continuous CLK Frequency = 4MHz, $\overline{CS}$ = LOW, Gain Control Code = 0001                                                                                                                                     | •                |                               | 1.4               | 2           | mA                         |

|                        | Supply Current, Shutdown                      | V <sub>SHDN</sub> = 4.5V (Hardware Shutdown)<br>V <sub>SHDN</sub> = 1V, Gain Control Code = 0000<br>(Software Shutdown)                                                                                                                                                                     | •                |                               | 2<br>135          | 10<br>200   | μΑ<br>μΑ                   |

|                        | SHDN Input High                               |                                                                                                                                                                                                                                                                                             |                  | 4.5                           |                   |             | V                          |

|                        | SHDN Input Low                                |                                                                                                                                                                                                                                                                                             |                  |                               |                   | 1           | V                          |

|                        | SHDN and HOLD_THRU Input Current (Note 2)     |                                                                                                                                                                                                                                                                                             |                  |                               |                   | 5           | μA                         |

|                        | Internal Op Amp Gain Bandwidth                |                                                                                                                                                                                                                                                                                             |                  |                               | 200               |             | kHz                        |

|                        | Slew Rate                                     |                                                                                                                                                                                                                                                                                             |                  |                               | 0.2               |             | V/µs                       |

|                        | Internal Sampling Frequency                   |                                                                                                                                                                                                                                                                                             |                  |                               | 3                 |             | kHz                        |

| V <sup>+</sup> = 5V, V | / <sup>-</sup> = -5V, V <sub>REF</sub> = 0V   |                                                                                                                                                                                                                                                                                             |                  |                               |                   |             |                            |

|                        | Gain Error (Note 2)                           | $A_{V} = 1 \ (R_{L} = 10k)$                                                                                                                                                                                                                                                                 |                  | -0.075                        | 0                 | 0.075       | %                          |

|                        | Gain Error (Note 2)                           | A <sub>V</sub> = 2 to 32 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                             | •                | -0.5                          | 0                 | 0.5         | %                          |

|                        | Gain Error (Note 2)                           | A <sub>V</sub> = 64 to 1024 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                          | •                | -0.6                          | -0.1              | 0.6         | %                          |

|                        | Gain Error (Note 2)                           | A <sub>V</sub> = 2048, 4096 (R <sub>L</sub> = 10k)                                                                                                                                                                                                                                          | •                | -1                            | -0.2              | 1           | %                          |

|                        | Gain Nonlinearity                             | A <sub>V</sub> = 1                                                                                                                                                                                                                                                                          |                  |                               | 3                 | 15          | ppm                        |

| V <sub>OS</sub>        | Input Offset Voltage (Note 3)                 | V <sub>CM</sub> = 0mV                                                                                                                                                                                                                                                                       |                  |                               | 5                 | ±20         | μV                         |

|                        | Average Input Offset Drift (Note 3)           | $ \begin{array}{l} T_A = -40^\circ C \ to \ 85^\circ C \\ T_A = 85^\circ C \ to \ 125^\circ C \end{array} $                                                                                                                                                                                 | •                |                               |                   | ±50<br>±100 | nV/°C<br>nV/°C             |

| l <sub>os</sub>        | Average Input Bias Current (Note 4)           | V <sub>CM</sub> = 1V                                                                                                                                                                                                                                                                        |                  |                               | 4                 | 10          | nA                         |

|                        | Average Input Offset Current (Note 4)         | V <sub>CM</sub> = 1V                                                                                                                                                                                                                                                                        |                  |                               | 1.5               | 3           | nA                         |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C.

| CMRR            | Common Mode Rejection Ratio                                 | $ \begin{array}{l} A_V = 1024,  V_{CM} = -5V \ to \ 5V,  LTC6915C \\ A_V = 1024,  V_{CM} = -4.9V \ to \ 4.9V,  LTC6915I \\ A_V = 1024,  V_{CM} = -5V \ to \ 5V,  LTC6915I \\ A_V = 1024,  V_{CM} = -4.9V \ to \ 4.9V,  LTC6915H \\ A_V = 1024,  V_{CM} = -5V \ to \ 4.97V,  LTC6915H \\ \end{array} $ | •<br>•<br>•<br>• | 105<br>105<br>100<br>100<br>90 | 123<br>123<br>123 |                | dB<br>dB<br>dB<br>dB<br>dB |

|-----------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|-------------------|----------------|----------------------------|

| PSRR            | Power Supply Rejection Ratio (Note 5)                       | $V_{\rm S} = 2.7$ V to 11V                                                                                                                                                                                                                                                                            | •                | 110                            | 116               |                | dB                         |

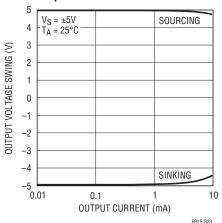

|                 | Output Voltage Swing High                                   | Sourcing 200µA<br>Sourcing 2mA                                                                                                                                                                                                                                                                        | •                | 4.97<br>4.90                   | 4.99<br>4.96      |                | V<br>V                     |

|                 | Output Voltage Swing Low                                    | Sinking 200µA<br>Sinking 2mA                                                                                                                                                                                                                                                                          | •                |                                | -4.98<br>-4.90    | -4.92<br>-4.70 | V<br>V                     |

|                 | Supply Current, Parallel Mode                               | No Load, V <sub>CM</sub> = 0mV                                                                                                                                                                                                                                                                        |                  |                                | 1.1               | 1.6            | mA                         |

|                 | Supply Current, Serial Mode (Note 6)                        | No Load at OUT, Capacitive Load at $D_{OUT}$ (C <sub>L</sub> ) = 15pF, Continuous CLK Frequency = 4MHz, $\overline{CS}$ = LOW, Gain Control Code = 0001                                                                                                                                               | •                |                                | 1.73              | 2.48           | mA                         |

|                 | Supply Current, Shutdown                                    | V <sub>SHDN</sub> = 4V (Hardware Shutdown)<br>V <sub>SHDN</sub> = 1V, Gain Control Code = 0000<br>(Software Shutdown)                                                                                                                                                                                 | •                |                                | 160               | 25<br>240      | μΑ<br>μΑ                   |

|                 | SHDN Input High                                             |                                                                                                                                                                                                                                                                                                       | •                | 4                              |                   |                | V                          |

|                 | SHDN Input Low                                              |                                                                                                                                                                                                                                                                                                       | ٠                |                                |                   | 1              | V                          |

| V+ = 5V,        | $V^- = -5V, V_{\text{REF}} = 0V$                            |                                                                                                                                                                                                                                                                                                       |                  |                                |                   |                |                            |

|                 | SHDN and HOLD_THRU Input Current (Note 2)                   |                                                                                                                                                                                                                                                                                                       |                  |                                |                   | 5              | μA                         |

|                 | Internal Op Amp Gain Bandwidth                              |                                                                                                                                                                                                                                                                                                       |                  |                                | 200               |                | kHz                        |

|                 | Slew Rate                                                   |                                                                                                                                                                                                                                                                                                       |                  |                                | 0.2               |                | V/µs                       |

|                 | Internal Sampling Frequency                                 |                                                                                                                                                                                                                                                                                                       |                  |                                | 3                 |                | kHz                        |

| Digital I,      | /O, All Digital I/O Voltage Referenced to DGND              |                                                                                                                                                                                                                                                                                                       |                  |                                |                   |                |                            |

| V <sub>IH</sub> | Digital Input High Voltage                                  |                                                                                                                                                                                                                                                                                                       | •                | 2.0                            |                   |                | V                          |

| V <sub>IL</sub> | Digital Input Low Voltage                                   |                                                                                                                                                                                                                                                                                                       | •                |                                |                   | 0.8            | V                          |

| V <sub>OH</sub> | Digital Output High Voltage                                 | Sourcing 500µA                                                                                                                                                                                                                                                                                        | •                | V <sup>+</sup> - 0.3           |                   |                | V                          |

| V <sub>OL</sub> | Digital Output Low Voltage                                  | Sinking 500µA                                                                                                                                                                                                                                                                                         | •                |                                |                   | 0.3            | V                          |

|                 | Digital Input Leakage                                       | $V^+ = 5V, V^- = -5V, V_{IN} = 0V$ to 5V                                                                                                                                                                                                                                                              | •                |                                |                   | ±2             | μA                         |

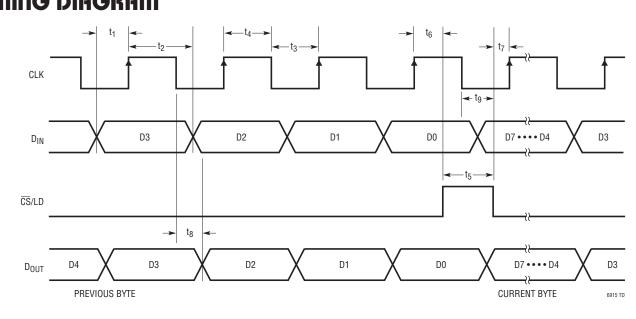

| Timing,         | V <sup>+</sup> = 2.7V to 4.5V, V <sup>-</sup> = 0V (Note 7) | T                                                                                                                                                                                                                                                                                                     |                  |                                |                   |                |                            |

| t <sub>1</sub>  | D <sub>IN</sub> Valid to CLK Setup                          |                                                                                                                                                                                                                                                                                                       | •                | 60                             |                   |                | ns                         |

| t <sub>2</sub>  | D <sub>IN</sub> Valid to CLK Hold                           |                                                                                                                                                                                                                                                                                                       | •                | 0                              |                   |                | ns                         |

| t <sub>3</sub>  | CLK Low                                                     |                                                                                                                                                                                                                                                                                                       | •                | 100                            |                   |                | ns                         |

| t <sub>4</sub>  | CLK High                                                    |                                                                                                                                                                                                                                                                                                       | •                | 100                            |                   |                | ns                         |

| t <sub>5</sub>  | CS/LD Pulse Width                                           |                                                                                                                                                                                                                                                                                                       | •                | 60                             |                   |                | ns                         |

| t <sub>6</sub>  | LSB CLK to CS/LD                                            |                                                                                                                                                                                                                                                                                                       | •                | 60                             |                   |                | ns                         |

| t <sub>7</sub>  | CS/LD Low to CLK                                            |                                                                                                                                                                                                                                                                                                       | •                | 30                             |                   |                | ns                         |

| t <sub>8</sub>  | D <sub>OUT</sub> Output Delay                               | C <sub>L</sub> = 15pF                                                                                                                                                                                                                                                                                 | •                |                                |                   | 125            | ns                         |

| t9              | CLK Low to CS/LD Low                                        |                                                                                                                                                                                                                                                                                                       |                  | 0                              |                   |                | ns                         |

### ELECTRICAL CHARACTERISTICS The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .

| Timing         | , $V^+ = 4.5V$ to 5.5V, $V^- = 0V$ (Note 7)       |                       |      |    |    |

|----------------|---------------------------------------------------|-----------------------|------|----|----|

| t <sub>1</sub> | D <sub>IN</sub> Valid to CLK Setup                |                       | • 30 |    | ns |

| t <sub>2</sub> | D <sub>IN</sub> Valid to CLK Hold                 |                       | • 0  |    | ns |

| t <sub>3</sub> | CLK Low                                           |                       | • 50 |    | ns |

| t4             | CLK High                                          |                       | • 50 |    | ns |

| t <sub>5</sub> | CS/LD Pulse Width                                 |                       | • 40 |    | ns |

| t <sub>6</sub> | LSB CLK to CS/LD                                  |                       | • 40 |    | ns |

| t <sub>7</sub> | CS/LD Low to CLK                                  |                       | • 20 |    | ns |

| t <sub>8</sub> | D <sub>OUT</sub> Output Delay                     | C <sub>L</sub> = 15pF | •    | 85 | ns |

| t9             | CLK Low to CS/LD Low                              |                       | • 0  |    | ns |

| Timing         | , Dual $\pm 4.5V$ to $\pm 5.5V$ Supplies (Note 7) | · · · · ·             |      |    |    |

| t <sub>1</sub> | D <sub>IN</sub> Valid to CLK Setup                |                       | • 30 |    | ns |

| t <sub>2</sub> | D <sub>IN</sub> Valid to CLK Hold                 |                       | • 0  |    | ns |

| t <sub>3</sub> | CLK High                                          |                       | • 50 |    | ns |

| t <sub>4</sub> | CLK Low                                           |                       | • 50 |    | ns |

| t <sub>5</sub> | CS/LD Pulse Width                                 |                       | • 40 |    | ns |

| t <sub>6</sub> | LSB CLK to CS/LD                                  |                       | • 40 |    | ns |

| t <sub>7</sub> | CS/LD Low to CLK                                  |                       | • 20 |    | ns |

| t <sub>8</sub> | D <sub>OUT</sub> Output Delay                     | C <sub>L</sub> = 15pF | •    | 85 | ns |

| t9             | CLK Low to CS/LD Low                              |                       | • 0  |    | ns |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: These parameters are tested at  $\pm$ 5V supply; at 3V and 5V supplies they are guaranteed by design.

**Note 3:** These parameters are guaranteed by design. Thermocouple effects preclude measurement of these voltage levels in high speed automatic test systems.  $V_{OS}$  is measured to a limit set by test equipment capability.

**Note 4:** If the total source resistance is less than 10k, no DC errors result from the input bias current or mismatch of the input bias currents or the mismatch of the resistances connected to IN<sup>-</sup> and IN<sup>+</sup>.

**Note 5:** The PSRR measurement accuracy depends on the proximity of the power supply bypass capacitor to the device under test. Because of this, the PSRR is 100% tested to relaxed limits at final test. However, their values are guaranteed by design to meet the data sheet limits.

**Note 6:** Supply current is dependent on the clock frequency. A higher clock frequency results in higher supply current.

Note 7: Guaranteed by design, not subject to test.

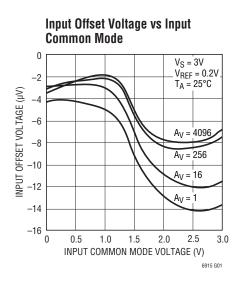

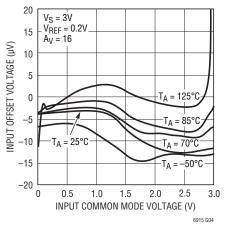

### **TYPICAL PERFORMANCE CHARACTERISTICS**

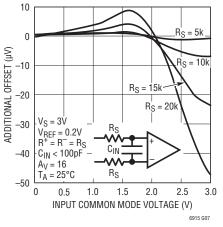

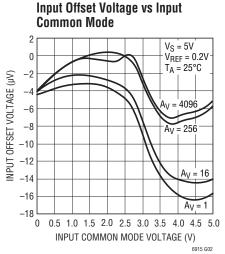

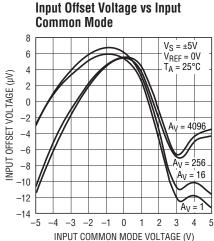

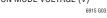

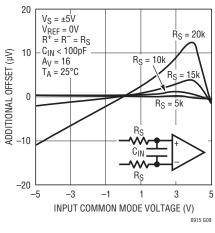

Input Offset Voltage vs Input Common Mode

Input Offset Voltage vs Input Common Mode

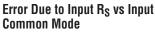

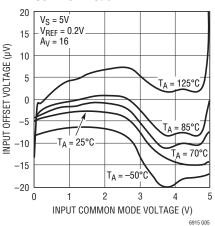

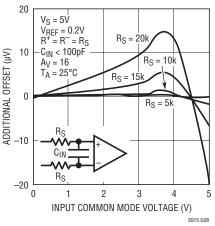

Error Due to Input R<sub>S</sub> vs Input Common Mode

#### Input Offset Voltage vs Input Common Mode

Error Due to Input R<sub>S</sub> vs Input Common Mode

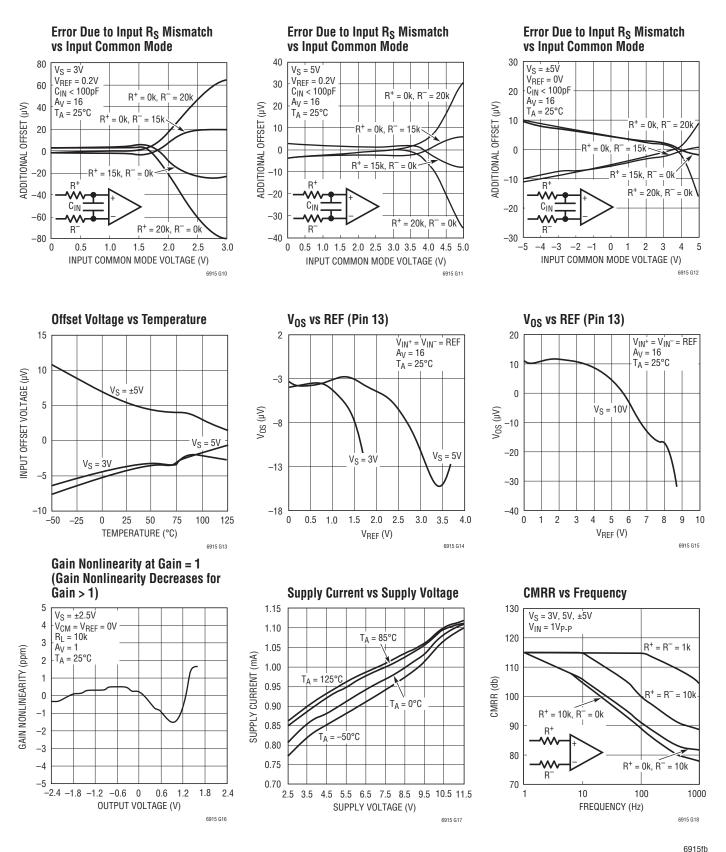

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### **TYPICAL PERFORMANCE CHARACTERISTICS**

\_1

-2

-3

0

2

**Output Voltage Swing vs Output Current**

**Output Voltage Swing vs Output Current**

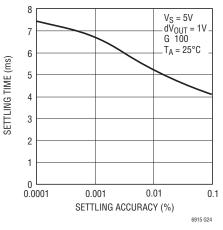

Low Gain Settling Time vs Settling Accuracy

4

6

TIME (s)

8

10

6915 G21

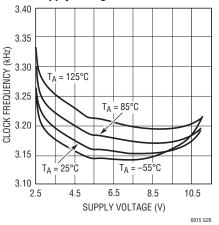

Additional Gain Error vs Load Resistance

### PIN FUNCTIONS (DFN/GN)

IN<sup>-</sup> (Pin 1/Pin 2): Inverting Analog Input.

**SHDN (Pin 1 GN Package Only):** Shutdown Pin. The IC is shut down when SHDN is tied to V<sup>+</sup>. An internal current source pulls this pin to V<sup>-</sup> when floating.

**IN<sup>+</sup> (Pin 2/Pin 3):** Noninverting Analog Input.

V<sup>-</sup> (Pin 3/Pin 4): Negative Supply.

**CS(D0) (Pin 4/Pin 6):** TTL Level Input. When in serial control mode, this pin is the chip select input (active low); in parallel control mode, this pin is the LSB of the parallel gain control code.

$D_{IN}(D1)$  (Pin 5/Pin 7): TTL Level Input. When in serial control mode, this pin is the serial input data; in parallel mode, this pin is the second LSB of the parallel gain control code.

**HOLD\_THRU** (Pin 5 GN Package Only): TTL Level Input for Parallel Control Mode. When HOLD\_THRU is high, the parallel data is latched in an internal D-latch.

**CLK(D2) (Pin 6/Pin 8):** TTL Level Input. When in serial control mode, this pin is the clock of the serial interface; in parallel mode, this pin is the third LSB of the parallel gain control code.

**D**<sub>OUT</sub>(D3) (Pin 7/Pin 9): TTL Level Input. When in serial control mode, this pin is the output of the serial data; in parallel mode, this pin is the MSB of the 4-bit parallel

gain control code. In parallel mode operation, if the data in to  $D_{OUT}$  (Pin 9) is from a voltage source greater than V<sup>+</sup> (Pin 12), then connect a resistor between the voltage source and  $D_{OUT}$  to limit the current into Pin 9 to 5mA or less.

DGND (Pin 8/Pin 10): Digital Ground.

**PARALLEL\_SERIAL** (Pin 9/Pin 11): Interface Selection Input. When tied to V<sup>+</sup>, the interface is in parallel mode, i.e., the PGA gain is defined by the parallel codes (D3 ~ D0), i.e.,  $\overline{CS}(D0)$ , DATA(D1), CLK(D2), and D<sub>OUT</sub>(D3). When PARALLEL\_SERIAL pin is tied to V<sup>-</sup>, the PGA gain is set by the serial interface.

**REF (Pin 10/Pin 13):** Voltage Reference for PGA output.

**OUT (Pin 11/Pin 15):** Amplifier Output. The typical current sourcing/sinking of the OUT pin is 1mA. For minimum gain error, the load resistance should be 1k or greater (refer to the Output Voltage Swing vs Output Current and Gain Error vs Load Resistance in the Typical Performance Characteristics section).

V<sup>+</sup> (Pin 12/Pin 16): Positive Supply.

**SENSE (Pin 14 GN Package Only):** Sense Pin. When the PGA drives a low resistance load and the interconnect resistance between the OUT pin and the load is not negligible, tying the SENSE pin as close as possible to the load can improve the gain accuracy.

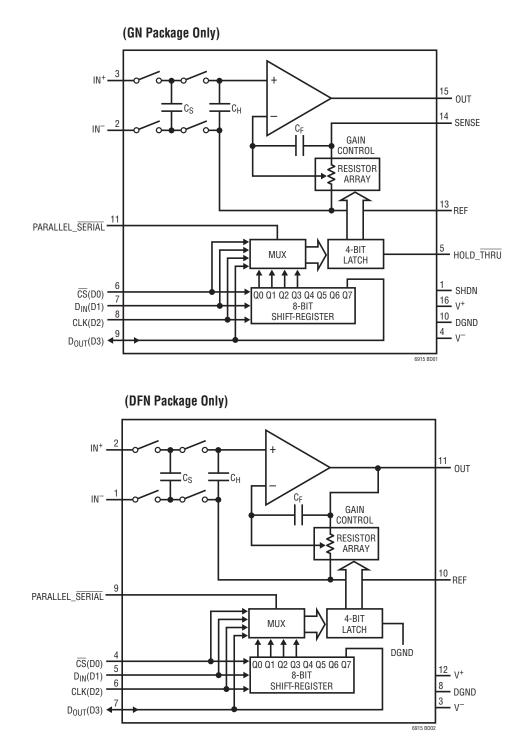

### **BLOCK DIAGRAMS**

### TIMING DIAGRAM

### OPERATION

#### Theory of Operation (Refer to Block Diagrams)

The LTC6915 uses an internal capacitor  $(C_S)$  to sample a differential input signal riding on a DC common mode voltage (the sampling rate is 3kHz and the input switchon resistance is 1k to 2k, depending on the power supply voltage). This capacitor's charge is transferred to a second internal hold capacitor  $(C_H)$  translating the common mode voltage of the input differential signal to that of REF pin. The resulting signal is amplified by a zero-drift op amp in the noninverting configuration. Gain control within the amplifier occurs by switching resistors from a matched resistor array. The LTC6915 has 14 levels of gain, controlled by the parallel or serial interface. A feedback capacitor C<sub>F</sub> helps to reduce the switching noise. Due to the input sampling, an LTC6915 may produce aliasing errors for input signals greater than 1.5kHz (one half the 3kHz sampling frequency). However, if the input signal is bandlimited to less than 1.5kHz then an LTC6915 is useful as instrumentation or as a differential to single-ended AC amplifier with programmable gain.

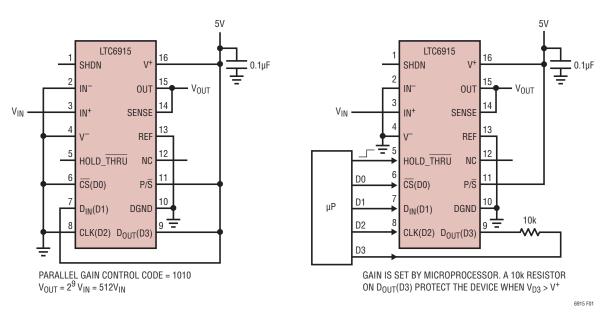

#### Parallel Interface

As shown in Figure 1, connecting PARALLEL\_SERIAL to V<sup>+</sup> allows the gain control code to be set through the parallel lines (D3, D2, D1, D0). When HOLD\_THRU is

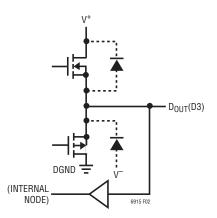

low (referenced to DGND) or floating, the parallel gain control bits (D3 ~ D0) directly control the PGA gain. When HOLD\_THRU is high, the parallel gain control bits are read into and held by a 4-bit latch. Any change at D3 ~ D0 will not affect the PGA gain when HOLD\_THRU is high. Note that the DFN12 package does not have the HOLD\_THRU pin. Instead, it is tied to DGND internally. The D<sub>OUT</sub>(D3) pin is bidirectional (output in serial mode, input in parallel mode). In parallel mode, the voltage at D<sub>OUT</sub>(D3) cannot exceed V<sup>+</sup>; otherwise, large currents can be injected to V<sup>+</sup> through the parasitic diode (see Figure 2). Connecting a 10k resistor at the D<sub>OUT</sub>(D3) pin if parallel mode is selected (see Figure 1) is recommended for current limiting. **Serial Interface**

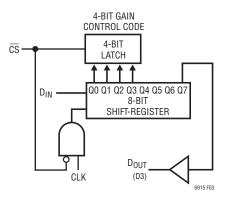

Connecting PARALLEL\_SERIAL to V<sup>-</sup> allows the gain control code to be set through the serial interface. When  $\overline{CS}$  is low, the serial data on D<sub>IN</sub> is shifted into an 8-bit shift-register on the rising edge of the clock, with the MSB transferred first (see Figure 3). Serial data on D<sub>OUT</sub> is shifted out on the clock's falling edge. A high  $\overline{CS}$  will load the 4 LSBs of the shift-register into a 4-bit D-latch, which are the gain control bits. The clock is disabled internally when  $\overline{CS}$  is pulled high. Note: CLK must be low before  $\overline{CS}$ is pulled low to avoid an extra internal clock pulse.

### OPERATION

$D_{OUT}$  is always active in serial mode (never tri-stated). This simplifies the daisy chaining of the multiple devices.  $D_{OUT}$  cannot be "wire-or" to other SPI outputs. In addition,  $D_{OUT}$  does not return to zero at the end of transmission, i.e. when  $\overline{CS}$  is pulled high.

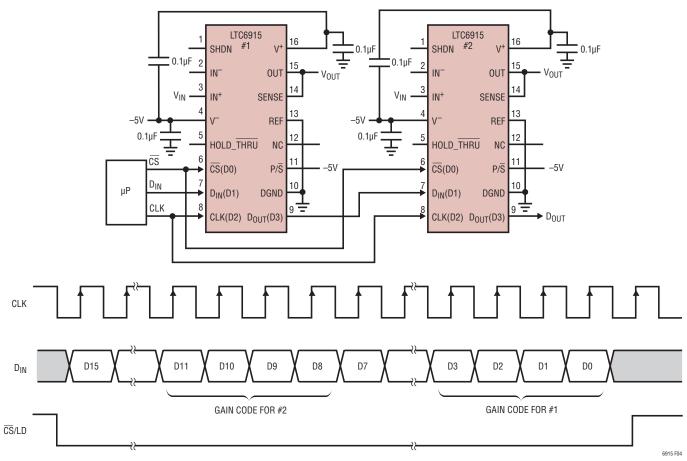

A LTC6915 may be daisy-chained with other LTC6915s or other devices having serial interfaces by connecting

the  $D_{OUT}$  to the  $D_{IN}$  of the next chip while CLK and  $\overline{CS}$  remain common to all chips in the daisy chain. The serial data is clocked to all the chips then the  $\overline{CS}$  signal is pulled high to update all of them simultaneously. Figure 4 shows an example of two LTC6915s in a daisy chained SPI configuration.

Figure 2. Bidirectional Nature of  $D_{OUT}/D3$  Pin

Figure 3. Diagram of Serial Interface (MSB First Out)

### LTC6915

### OPERATION

Figure 4. 2 PGAs in a Daisy Chain

The amplifier's gain is set as follows:

| D3, D2, D1, D0 | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101~<br>1111 |

|----------------|------|------|------|------|------|------|------|------|------|------|------|------|------|---------------|

| Gain           | 0    | 1    | 2    | 4    | 8    | 16   | 32   | 64   | 128  | 256  | 512  | 1024 | 2048 | 4096          |

#### Input Voltage Range

The input common mode voltage range of the LTC6915 is rail-to-rail. However, the following equation limits the size of the differential input voltage:

$$V^{-} \le (V_{IN}^{+} - V_{IN}^{-}) + V_{REF} \le V^{+} - 1.3$$

Where  $V_{IN}^{+}$  and  $V_{IN}^{-}$  are the voltage of the differential input pins, V<sup>+</sup> and V<sup>-</sup> are the positive and negative supply voltages respectively and  $V_{REF}$  is the voltage of REF pin. In addition,  $V_{IN}^{+}$  and  $V_{IN}^{-}$  must not exceed the power supply voltages, i.e.,

$V^- < V_{IN}{}^+ < V^+$  and  $V^- < V_{IN}{}^- < V^+$

#### ±5 Volt Operation

When using the LTC6915 with supplies over 5.5V, care must be taken to limit the maximum difference between any of the input pins ( $IN^+$  or  $IN^-$ ) and the REF pin to 5.5V, i.e.,

$$|V_{IN}^+ - V_{REF}| < 5.5$$

and  $|V_{IN}^- - V_{REF}| < 5.5$

If not, the device will be damaged. For example, if railto-rail input operation is desired when the supplies are at  $\pm$ 5V, the REF pin should be 0,  $\pm$ 0.5V. As a second example, if the V<sup>+</sup> pin is 10V, and the V<sup>-</sup> and REF pins are at 0, the inputs should not exceed 5.5V.

### OPERATION

#### Settling Time

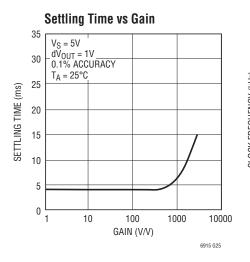

The sampling rate is 3kHz and the input sampling period during which  $C_S$  is charged to the input differential voltage,  $V_{IN}$ , is approximately 150 $\mu$ s. First assume that on each input sampling period,  $C_{S}$  is charged fully to  $V_{\text{IN}}.$  Since  $C_S = C_H$  (= 1000pF), a change in the input will settle to N bits of accuracy at the op amp noninverting input after N clock cycles or 333µs(N). The settling time at the OUT pin is also affected by the internal op amp. Since the gain bandwidth of the internal op amp is typically 200kHz, the settling time is dominated by the switched-capacitor front end for gains below 100 (see the Low Gain Settling Time vs Settling Accuracy and the Settling Time vs Gain graphs in the Typical Performance Characteristics section). In addition, the worst case settling time after a device-enable (active low on Pin 1 of a GN package) is equal to the settling due to the gain plus the input settling time  $(333\mu s \cdot N)$ . For example, if an LTC6915 is enabled with a logic high on Pin 1 then, the maximum settling time to 10 bits of accuracy (0.1%) and a gain equal to 100 is 8.33ms ([333µs • 1024] + 5ms).

#### Input Current

Whenever the differential input V<sub>IN</sub> changes, C<sub>H</sub> must be charged up to the new input voltage via C<sub>S</sub>. This results in an input charging current during each input sampling period. Eventually, C<sub>H</sub> and C<sub>S</sub> will reach V<sub>IN</sub> and ideally, the input current would go to zero for DC inputs.

In reality, there are additional parasitic capacitors which disturb the charge on  $C_S$  every cycle even if  $V_{IN}$  is a DC voltage. For example, the parasitic bottom plate capacitor on  $C_S$  must be charged from the voltage on the REF pin to the voltage on the IN<sup>-</sup> pin every cycle. The resulting input charging current decays exponentially during each input sampling period with a time constant equal to  $R_SC_S$ . If the voltage disturbance due to these currents settles before the end of the sampling period, there will be no errors due to source resistance or the source resistance mismatch between IN<sup>+</sup> and IN<sup>-</sup>. With  $R_S$  less than 10k, no DC errors occur due to input current mismatch.

In the Typical Performance Characteristics section of this data sheet, there are curves showing the additional error from non-zero source resistance in the inputs. If there are no large capacitors across the inputs, the amplifier is less sensitive to source resistance and source resistance mismatch. When large capacitors are placed across the

inputs, the input charging currents are placed across the inputs. The input charging currents described above result in larger DC errors, especially with source resistor mismatches.

#### **Power Supply Bypassing**

In a dual supply operation, connect a  $0.1\mu$ F bypass capacitor from each power supply pin (V<sup>+</sup> and V<sup>-</sup>) to an analog round plance surrounding an LTC6915. The bypass capacitor trace to the supply pins must be less than 0.2 inches (an X7R or X5R capacitor type is recommended). In single supply operation, connect the V<sup>-</sup> pin to the analog ground plane and bypass the V<sup>+</sup> pin.

#### **Shutdown Modes**

The IC has two shutdown modes, hardware shutdown and software shutdown. When SHDN is tied to V<sup>+</sup>, the IC is in hardware shutdown mode. During this shutdown mode, the gain setting digital interface (serial or parallel) and the main op amp are both disabled, thus the PGA dissipates very small supply current (see the Electrical Characteristic table). When SHDN is floating, an internal current source will pull it down to V<sup>-</sup>. The digital interface is turned on to read the gain setting codes. The IC is in normal amplification mode as long as the gain control code is other than 0000. If the gain control code is 0000, the IC operates in software shutdown mode, i.e., the main op amp is turned off so that the PGA dissipates less power. The DFN package does not have hardware shutdown.

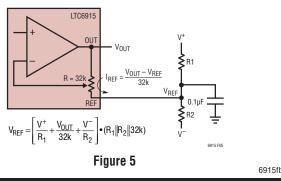

#### Setting the Voltage at the REF Pin

The current coming out of the REF pin may affect the reference voltage at the REF pin ( $V_{REF}$ ). If  $V_{REF}$  is set by a resistive divider then the  $V_{REF}$  voltage is a function of the  $V_{OUT}$  voltage (see Figure 5). In order to minimize the  $V_{REF}$  variations, the total resistance of R1 plus R2 should be much less than 32k (5k or less) or use a voltage reference to set  $V_{REF}$ .

### TYPICAL APPLICATION

#### Multiplexing Two LTC6915's

Send a gain code of 0000 to one IC to set its output to a high impedance state and send a gain code other than 0000 to the second IC to set it for normal amplification. If both devices are ON, the  $200\Omega$  resistors protect the outputs. The sense pin connection maintains gain accuracy for loads 1k or greater.

Figure 6. A 2:1 Multiplexing Two LTC6915's with Daisy Chained Gain Control

### **REVISION HISTORY** (Revision history begins at Rev B)

| REV | DATE | DESCRIPTION                                          | PAGE NUMBER |

|-----|------|------------------------------------------------------|-------------|

| В   | 6/11 | Revised units for PSRR in Electrical Characteristics | 5           |

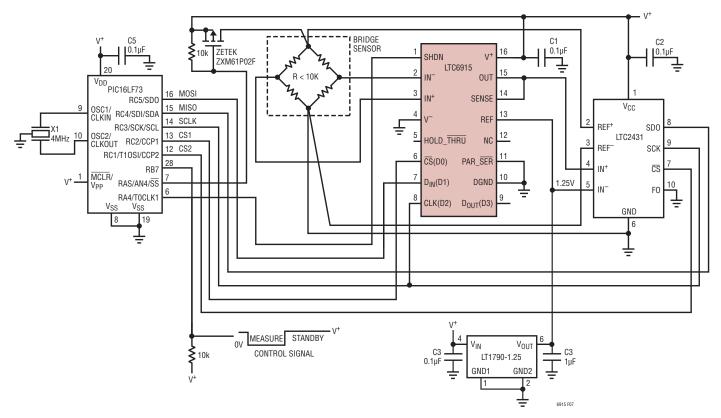

### TYPICAL APPLICATION

Figure 7. Bridge Amplifier with Programmable Gain and Analog to Digital Conversion. (Standby Current Less than 100µA)

### **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                                                            | COMMENTS                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| LTC1043     | Dual Precision Instrumentation Switched-Capacitor<br>Building Block                                    | Rail-to-Rail Input, 120dB CMRR                                              |

| LTC1100     | Precision Zero-Drift Instrumentation Amplifier                                                         | Fixed Gains of 10 or 100, 10µV Offset, 50pA Input Bias Current              |

| LTC1101     | Precision, Micropower, Single Supply Instrumentation<br>Amplifier                                      | Fixed Gain of 10 or 100, I <sub>S</sub> < 105µA                             |

| LTC1167     | Single Resistor Gain Programmable, Precision<br>Instrumentation Amplifier                              | Single Gains Set Resistor, G = 1 to 10,000 Low Noise: $7.5$ nV/ $\sqrt{Hz}$ |

| LTC1168     | Low Power Single Resistor Gain Programmable,<br>Precision Instrumentation Amplifiers                   | I <sub>S</sub> = 530μA                                                      |

| LTC1789-1   | Single Supply, Rail-to-Rail Output, Micropower<br>Instrumentation Amplifier                            | I <sub>S</sub> = 80µA Max                                                   |

| LTC2050     | Zero-Drift Operational Amplifier                                                                       | SOT-23 Package                                                              |

| LTC2051     | Dual Zero-Drift Operational Amplifier                                                                  | MS8 Package                                                                 |

| LTC2052     | Quad Zero-Drift Operational Amplifier                                                                  | GN16 Package                                                                |

| LTC2053     | Rail-to-Rail Input and Output, Zero-Drift Instrumentation<br>Amplifier with Resistor-Programmable Gain | MS8 Package, 10µV Max V <sub>OS</sub> , 50nV/°C Max Drift                   |

| LTC6800     | Rail-to-Rail Input and Output, Instrumentation Amplifier with Resistor-Programmable Gain               | MS8 Package, 100µV Max V <sub>OS</sub> , 250nV/°C Max Drift                 |