# Low Distortion, High Speed Rail-to-Rail Input/Output Amplifiers

AD8027/AD8028

#### **FEATURES**

High speed

190 MHz, -3 dB bandwidth (G = +1)

100 V/µs slew rate

Low distortion

120 dBc @ 1 MHz SFDR

80 dBc @ 5 MHz SFDR

Selectable input crossover threshold

Low noise

4.3 nV/√Hz

1.6 pA/√Hz

Low offset voltage: 900 µV max

Low power: 6.5 mA/amplifier supply current

Power-down mode

No phase reversal:  $V_{IN} > |V_S| + 200 \text{ mV}$ Wide supply range: 2.7 V to 12 V

Small packaging: SOIC-8, SOT-23-6, MSOP-10

### **APPLICATIONS**

**Filters**

**ADC** drivers

**Level shifting**

**Buffering**

**Professional video**

Low voltage instrumentation

### **GENERAL DESCRIPTION**

The AD8027/AD8028¹ are high speed amplifiers with rail-to-rail input and output that operate on low supply voltages and are optimized for high performance and wide dynamic signal range. The AD8027/AD8028 have low noise (4.3 nV/ $\sqrt{\text{Hz}}$ , 1.6 pA/ $\sqrt{\text{Hz}}$ ) and low distortion (120 dBc at 1 MHz). In applications that use a fraction of, or the entire input dynamic range and require low distortion, the AD8027/AD8028 are ideal choices.

Many rail-to-rail input amplifiers have an input stage that switches from one differential pair to another as the input signal crosses a threshold voltage, which causes distortion. The AD8027/AD8028 have a unique feature that allows the user to select the input crossover threshold voltage through the SELECT pin. This feature controls the voltage at which the complementary transistor input pairs switch. The AD8027/AD8028 also have intrinsically low crossover distortion.

#### Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

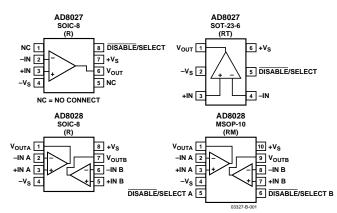

### **CONNECTION DIAGRAMS**

Figure 1. Connection Diagrams (Top View)

With their wide supply voltage range (2.7 V to 12 V) and wide bandwidth (190 MHz), the AD8027/AD8028 amplifiers are designed to work in a variety of applications where speed and performance are needed on low supply voltages. The high performance of the AD8027/AD8028 is achieved with a quiescent current of only 6.5 mA/amplifier typical. The AD8027/AD8028 have a shutdown mode that is controlled via the SELECT pin.

The AD8027/AD8028 are available in SOIC-8, MSOP-10, and SOT-23-6 packages. They are rated to work over the industrial temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

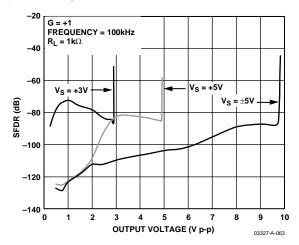

Figure 2. SFDR vs. Output Amplitude

<sup>1</sup>Protected by U.S. patent numbers 6,486,737B1; 6,518,842B1

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

# IMPORTANT LINKS for the <u>AD8027\_8028</u>\*

Last content update 08/18/2013 09:13 pm

#### **DOCUMENTATION**

AN-649: Using the Analog Devices Active Filter Design Tool

**AN-581:** Biasing and Decoupling Op Amps in Single Supply Applications

**AN-402:** Replacing Output Clamping Op Amps with Input Clamping Amps

**AN-417:** Fast Rail-to-Rail Operational Amplifiers Ease Design Constraints in Low Voltage High Speed Systems

**MT-060:** Choosing Between Voltage Feedback and Current Feedback Op Amps

**MT-059:** Compensating for the Effects of Input Capacitance on VFB and CFB Op Amps Used in Current-to-Voltage Converters

MT-058: Effects of Feedback Capacitance on VFB and CFB Op Amps

MT-056: High Speed Voltage Feedback Op Amps

MT-053: Op Amp Distortion: HD, THD, THD + N, IMD, SFDR, MTPR

MT-052: Op Amp Noise Figure: Don't Be Mislead

**MT-050:** Op Amp Total Output Noise Calculations for Second-Order System

**MT-049:** Op Amp Total Output Noise Calculations for Single-Pole System

MT-047: Op Amp Noise

MT-033: Voltage Feedback Op Amp Gain and Bandwidth

MT-032: Ideal Voltage Feedback (VFB) Op Amp

A Stress-Free Method for Choosing High-Speed Op Amps

### FOR THE AD8027

**UG-127:** Universal Evaluation Board for High Speed Op Amps in SOT-23-5/SOT-23-6 Packages

**UG-101:** Evaluation Board User Guide

Op Amps Increasingly Swing Rail-to-Rail

Low-Cost Video Multiplexing Using High-Speed Amplifiers

#### FOR THE AD8028

AD8028-KGD-CHIP: Low Distortion, High Speed Rail-to-Rail Input/Output Amplifier Data Sheet

**UG-128:** Universal Evaluation Board for Dual High Speed Op Amps in SOIC Packages

### **DESIGN TOOLS, MODELS, DRIVERS & SOFTWARE**

dBm/dBu/dBv Calculator

Power Dissipation vs Die Temp

Analog Filter Wizard 2.0

### ADIsimOpAmp™

**OpAmp Stability**

AD8027 SPICE Macro-Model

AD8028 SPICE Macro-Model

#### PARAMETRIC SELECTION TABLES

Find Similar Products By Operating Parameters for the AD8027 Find Similar Products By Operating Parameters for the AD8028 High Speed Amplifiers Selection Table

#### **EVALUATION KITS & SYMBOLS & FOOTPRINTS**

View the Evaluation Boards and Kits page for the AD8027 View the Evaluation Boards and Kits page for the AD8028 Symbols and Footprints for the AD8027 Symbols and Footprints for the AD8028

#### **DESIGN COLLABORATION COMMUNITY**

<u>Collaborate Online</u> with the ADI support team and other designers about select ADI products.

Follow us on Twitter: www.twitter.com/ADI News

Like us on Facebook: www.facebook.com/AnalogDevicesInc

### **DESIGN SUPPORT**

Submit your support request here: <u>Linear and Data Converters</u> <u>Embedded Processing and DSP</u>

Telephone our Customer Interaction Centers toll free:

Americas: 1-800-262-5643 Europe: 00800-266-822-82 China: 4006-100-006 India: 1800-419-0108 Russia: 8-800-555-45-90

**Quality and Reliability Lead(Pb)-Free Data**

#### **SAMPLE & BUY**

AD8027

**AD8028**

- View Price & Packaging

- Request Evaluation Board

- Request Samples Check Inventory & Purchase

Find Local Distributors

\* This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page (labeled 'Important Links') does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Wideband Operation                 | 19 |

|------------------------------------|----|

| Circuit Considerations             | 19 |

| Applications                       | 21 |

| Using the SELECT Pin               | 21 |

| Driving a 16-Bit ADC               | 21 |

| Band-Pass Filter                   | 22 |

| Design Tools and Technical Support | 22 |

| Outline Dimensions                 | 23 |

| Ordering Guide                     | 24 |

3/03—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{S}}=\pm 5~V$  at  $T_{\text{A}}=25^{\circ}\text{C},~R_{\text{L}}=1~\text{k}\Omega$  to midsupply, G=1, unless otherwise noted.

Table 1.

| Parameter                                        | Conditions                                                                                           | Min                    | Тур                           | Max                        | Unit    |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------|-------------------------------|----------------------------|---------|

| DYNAMIC PERFORMANCE                              |                                                                                                      |                        | /r                            | -                          |         |

| –3 dB Bandwidth                                  | $G = 1, V_0 = 0.2 \text{ V p-p}$                                                                     | 138                    | 190                           |                            | MHz     |

|                                                  | $G = 1, V_0 = 2 V p-p$                                                                               | 20                     | 32                            |                            | MHz     |

| Bandwidth for 0.1 dB Flatness                    | $G = 2, V_0 = 0.2 \text{ V p-p}$                                                                     |                        | 16                            |                            | MHz     |

| Slew Rate                                        | $G = +1, V_0 = 3.2 \text{ V p p}$<br>$G = +1, V_0 = 2 \text{ V step/G} = -1, V_0 = 2 \text{ V step}$ |                        | 90/100                        |                            | V/µs    |

|                                                  | 1                                                                                                    |                        |                               |                            | -       |

| Settling Time to 0.1%                            | $G = 2$ , $V_0 = 2$ V step                                                                           |                        | 35                            |                            | ns      |

| NOISE/DISTORTION PERFORMANCE                     | 6 4441 1/ 21/ 2 2422                                                                                 |                        | 120                           |                            | 10      |

| Spurious-Free Dynamic Range (SFDR)               | $f_c = 1 \text{ MHz}, V_o = 2 \text{ V p-p}, R_F = 24.9 \Omega$                                      |                        | 120                           |                            | dBc     |

|                                                  | $f_{c} = 5 \text{ MHz}, V_{O} = 2 \text{ V p-p}, R_{F} = 24.9 \Omega$                                |                        | 80                            |                            | dBc     |

| Input Voltage Noise                              | f = 100 kHz                                                                                          |                        | 4.3                           |                            | nV/√Hz  |

| Input Current Noise                              | f = 100 kHz                                                                                          |                        | 1.6                           |                            | pA/√Hz  |

| Differential Gain Error                          | NTSC, $G = 2$ , $R_L = 150 \Omega$                                                                   |                        | 0.1                           |                            | %       |

| Differential Phase Error                         | NTSC, $G = 2$ , $R_L = 150 \Omega$                                                                   |                        | 0.2                           |                            | Degrees |

| Crosstalk, Output to Output                      | $G = 1$ , $R_L = 100 \Omega$ , $V_{OUT} = 2 V p-p$ ,                                                 |                        | -93                           |                            | dB      |

| D.C. 0505001444465                               | V <sub>S</sub> = ±5 V @ 1 MHz                                                                        |                        |                               |                            |         |

| DC PERFORMANCE                                   | SELECT II I I I DAID II                                                                              |                        | 200                           | 000                        | ١,,     |

| Input Offset Voltage                             | SELECT = three-state or open, PNP active                                                             |                        | 200                           | 800                        | μV      |

|                                                  | SELECT = high NPN active                                                                             |                        | 240                           | 900                        | μV      |

| Input Offset Voltage Drift                       | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                 |                        | 1.50                          |                            | μV/°C   |

| Input Bias Current <sup>1</sup>                  | $V_{CM} = 0 \text{ V, NPN active}$                                                                   |                        | 4                             | 6                          | μΑ      |

| Input Bias Current  Input Offset Current         | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                 |                        | 4                             |                            | μΑ      |

|                                                  | $V_{CM} = 0 \text{ V, PNP active}$                                                                   |                        | -8                            | -11                        | μΑ      |

|                                                  | T <sub>MIN</sub> to T <sub>MAX</sub>                                                                 |                        | -8                            |                            | μΑ      |

| •                                                |                                                                                                      |                        | ±0.1                          | ±0.9                       | μΑ      |

| Open-Loop Gain                                   | $V_0 = \pm 2.5 \text{ V}$                                                                            | 100                    | 110                           |                            | dB      |

| INPUT CHARACTERISTICS                            |                                                                                                      |                        |                               |                            |         |

| Input Impedance                                  |                                                                                                      |                        | 6                             |                            | ΜΩ      |

| Input Capacitance                                |                                                                                                      |                        | 2                             |                            | pF      |

| Input Common-Mode Voltage Range                  | V                                                                                                    |                        | -5.2 to +5.2                  |                            | V       |

| Common-Mode Rejection Ratio                      | $V_{CM} = \pm 2.5 \text{ V}$                                                                         | 90                     | 110                           |                            | dB      |

| SELECT PIN                                       | The second state of 20. A                                                                            |                        | 224                           |                            | .,      |

| Crossover Low, Selection Input Voltage           | Three-state < ±20 μA                                                                                 |                        | -3.3 to +5                    |                            | V       |

| Crossover High, Selection Input Voltage          |                                                                                                      |                        | -3.9 to -3.3                  |                            | V       |

| Disable Input Voltage<br>Disable Switching Speed | 50% of input to <10% of final V <sub>o</sub>                                                         |                        | −5 to −3.9<br>980             |                            |         |

|                                                  | 30% of input to < 10% of final V <sub>0</sub>                                                        |                        |                               |                            | ns      |

| Enable Switching Speed                           |                                                                                                      |                        | 45                            |                            | ns      |

| OUTPUT CHARACTERISTICS                           |                                                                                                      |                        |                               |                            |         |

| Output Overdrive Recovery Time                   | $V_1 = +6 \text{ V to } -6 \text{ V, G} = -1$                                                        |                        | 40/45                         |                            | ns      |

| (Rising/Falling Edge) Output Voltage Swing       |                                                                                                      | -V <sub>s</sub> + 0.10 | +V <sub>s</sub> - 0.06,       | +V <sub>s</sub> - 0.10     | V       |

| Output voltage swing                             |                                                                                                      | $-v_s + 0.10$          | $-V_s - 0.06$ , $-V_s + 0.06$ | + <b>v</b> s - <b>0.10</b> | V       |

| Short-Circuit Output                             | Sinking and Sourcing                                                                                 |                        | 120                           |                            | mA      |

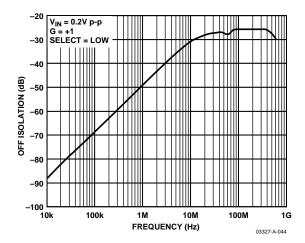

| Off Isolation                                    | $V_{IN} = 0.2 \text{ V p-p, f} = 1 \text{ MHz, SELECT} = \text{low}$                                 |                        | –49                           |                            | dB      |

| Capacitive Load Drive                            | 30% overshoot                                                                                        |                        | 20                            |                            | pF      |

| POWER SUPPLY                                     | 20 /0 OVEISHOOL                                                                                      | <del> </del>           | 20                            |                            | Pi      |

| Operating Range                                  |                                                                                                      | 2.7                    |                               | 12                         | V       |

| Quiescent Current/Amplifier                      |                                                                                                      | 2.7                    | 6.5                           | 8.5                        | mA      |

| Quiescent Current (Disabled)                     | SELECT = low                                                                                         |                        | 370                           | 500                        | μΑ      |

|                                                  |                                                                                                      | 00                     |                               | 500                        | -       |

| Power Supply Rejection Ratio                     | $V_S \pm 1 V$                                                                                        | 90                     | 110                           |                            | dB      |

$<sup>^{1}</sup>$  No sign or a plus sign indicates current into the pin; a minus sign indicates current out of the pin.

$V_{\text{S}}$  = 5 V at  $T_{\text{A}}$  = 25°C,  $R_{\text{L}}$  = 1  $k\Omega$  to midsupply, unless otherwise noted.

Table 2.

| Parameter                                        | Conditions                                                               | Min             | Тур            | Max                        | Unit        |

|--------------------------------------------------|--------------------------------------------------------------------------|-----------------|----------------|----------------------------|-------------|

| DYNAMIC PERFORMANCE                              |                                                                          |                 | •              |                            |             |

| −3 dB Bandwidth                                  | $G = 1, V_0 = 0.2 \text{ V p-p}$                                         | 131             | 185            |                            | MHz         |

|                                                  | $G = 1, V_0 = 2 V p-p$                                                   | 18              | 28             |                            | MHz         |

| Bandwidth for 0.1 dB Flatness                    | $G = 2, V_0 = 0.2 \text{ V p-p}$                                         |                 | 12             |                            | MHz         |

| Slew Rate                                        | $G = +1, V_0 = 2 \text{ V step/G} = -1, V_0 = 2 \text{ V step}$          |                 | 85/100         |                            | V/µs        |

| Settling Time to 0.1%                            | $G = 2$ , $V_0 = 2$ V step                                               |                 | 40             |                            | ns          |

| NOISE/DISTORTION PERFORMANCE                     | G = 2, v <sub>0</sub> = 2 v step                                         |                 | 10             |                            | 113         |

| Spurious-Free Dynamic Range (SFDR)               | $f_C = 1 \text{ MHz}, V_O = 2 \text{ V p-p}, R_F = 24.9 \Omega$          |                 | 90             |                            | dBc         |

| Spanous-riee Dynamic Nange (51 DN)               |                                                                          |                 | 64             |                            | dBc         |

| Lean (Malkara Nicha)                             | $f_c = 5 \text{ MHz}, V_o = 2 \text{ V p-p}, R_F = 24.9 \Omega$          |                 |                |                            |             |

| Input Voltage Noise                              | f = 100 kHz                                                              |                 | 4.3            |                            | nV/√Hz      |

| Input Current Noise<br>Differential Gain Error   | f = 100  kHz<br>NTSC, $G = 2$ , $R_L = 150 \Omega$                       |                 | 1.6<br>0.1     |                            | pA/√Hz<br>% |

| Differential Phase Error                         | NTSC, $G = 2$ , $R_L = 150 \Omega$<br>NTSC, $G = 2$ , $R_L = 150 \Omega$ |                 | 0.1            |                            | Degrees     |

| Crosstalk, Output to Output                      | $G = 1$ , $R_L = 100 \Omega$ , $V_{OUT} = 2 V p-p$ ,                     |                 | -92            |                            | dB          |

| Crosstant, output to output                      | $V_s = \pm 5 \text{ V } @ 1 \text{ MHz}$                                 |                 | 72             |                            | ub.         |

| DC PERFORMANCE                                   | 13 = 1 € 1 1111                                                          |                 |                |                            |             |

| Input Offset Voltage                             | SELECT = three-state or open, PNP active                                 |                 | 200            | 800                        | μV          |

| ·                                                | SELECT = high NPN active                                                 |                 | 240            | 900                        | μV          |

| Input Offset Voltage Drift                       | T <sub>MIN</sub> to T <sub>MAX</sub>                                     |                 | 2              |                            | μV/°C       |

|                                                  | $V_{CM} = 2.5 \text{ V, NPN active}$                                     |                 | 4              | 6                          | μΑ          |

| Input Bias Current <sup>1</sup>                  | T <sub>MIN</sub> to T <sub>MAX</sub>                                     |                 | 4              |                            | μΑ          |

|                                                  | $V_{CM} = 2.5 \text{ V}$ , PNP active                                    |                 | -8             | -11                        | μA          |

|                                                  | T <sub>MIN</sub> to T <sub>MAX</sub>                                     |                 | -8             |                            | μA          |

| Input Offset Current                             |                                                                          |                 | ±0.1           | ±0.9                       | μΑ          |

| Open-Loop Gain                                   | $V_0 = 1 \text{ V to } 4 \text{ V}$                                      | 96              | 105            |                            | dB          |

| INPUT CHARACTERISTICS                            |                                                                          |                 |                |                            |             |

| Input Impedance                                  |                                                                          |                 | 6              |                            | ΜΩ          |

| Input Capacitance                                |                                                                          |                 | 2              |                            | pF          |

| Input Common-Mode Voltage Range                  |                                                                          |                 | -0.2 to +5.2   |                            | V           |

| Common-Mode Rejection Ratio                      | $V_{CM} = 0 \text{ V to } 2.5 \text{ V}$                                 | 90              | 105            |                            | dB          |

| SELECT PIN                                       |                                                                          |                 |                |                            |             |

| Crossover Low, Selection Input Voltage           | Three-state < ±20 μA                                                     |                 | 1.7 to 5       |                            | V           |

| Crossover High, Selection Input Voltage          |                                                                          |                 | 1.1 to 1.7     |                            | V           |

| Disable Input Voltage                            | FOOV of input to (100) of finally                                        |                 | 0 to 1.1       |                            | V           |

| Disable Switching Speed                          | 50% of input to <10% of final V <sub>o</sub>                             |                 | 1100           |                            | ns          |

| Enable Switching Speed                           |                                                                          |                 | 50             |                            | ns          |

| OUTPUT CHARACTERISTICS                           | V 4V 5V 6 4                                                              |                 | 50/50          |                            |             |

| Overdrive Recovery Time<br>(Rising/Falling Edge) | $V_1 = -1 \text{ V to } +6 \text{ V, G} = -1$                            |                 | 50/50          |                            | ns          |

| Output Voltage Swing                             | $R_1 = 1 \text{ k}\Omega$                                                | $-V_{s} + 0.08$ | $+V_{s}-0.04,$ | +V <sub>s</sub> - 0.08     | V           |

| Output voltage swing                             | $n_L - 1 K22$                                                            | -VS + 0.08      | $-V_s + 0.04$  | + <b>V</b> S - <b>0.08</b> | v           |

| Off Isolation                                    | $V_{IN} = 0.2 \text{ V p-p, } f = 1 \text{ MHz, SELECT} = \text{low}$    |                 | -49            |                            | dB          |

| Short-Circuit Current                            | Sinking and sourcing                                                     |                 | 105            |                            | mA          |

| Capacitive Load Drive                            | 30% overshoot                                                            |                 | 20             |                            | pF          |

| POWER SUPPLY                                     |                                                                          |                 |                |                            | İ           |

| Operating Range                                  |                                                                          | 2.7             |                | 12                         | V           |

| Quiescent Current/Amplifier                      |                                                                          |                 | 6              | 8.5                        | mA          |

| Quiescent Current (Disabled)                     | SELECT = low                                                             |                 | 320            | 450                        | μΑ          |

| Power Supply Rejection Ratio                     | $V_s \pm 1 V$                                                            | 90              | 105            |                            | dB          |

$<sup>^{\</sup>rm 1}$  No sign or a plus sign indicates current into the pin; a minus sign indicates current out of the pin.

$V_S$  = 3 V at  $T_A$  = 25°C,  $R_L$  = 1 k $\Omega$  to midsupply, unless otherwise noted.

Table 3.

| Parameter                                               | Conditions                                                            | Min             | Тур                             | Max                    | Unit     |

|---------------------------------------------------------|-----------------------------------------------------------------------|-----------------|---------------------------------|------------------------|----------|

| DYNAMIC PERFORMANCE                                     |                                                                       |                 |                                 |                        |          |

| –3 dB Bandwidth                                         | $G = 1, V_0 = 0.2 \text{ V p-p}$                                      | 125             | 180                             |                        | MHz      |

|                                                         | $G = 1, V_0 = 2 V p-p$                                                | 19              | 29                              |                        | MHz      |

| Bandwidth for 0.1 dB Flatness                           | $G = 2, V_0 = 0.2 \text{ V p-p}$                                      |                 | 10                              |                        | MHz      |

| Slew Rate                                               | $G = +1$ , $V_0 = 2 \text{ V step/G} = -1$ , $V_0 = 2 \text{ V step}$ |                 | 73/100                          |                        | V/µs     |

| Settling Time to 0.1%                                   | $G = 2$ , $V_0 = 2$ V step                                            |                 | 48                              |                        | ns       |

| NOISE/DISTORTION PERFORMANCE                            | C 2,10 213tcp                                                         |                 | 10                              |                        | 113      |

| Spurious-Free Dynamic Range (SFDR)                      | $f_{c} = 1 \text{ MHz}, V_{o} = 2 \text{ V p-p}, R_{F} = 24.9 \Omega$ |                 | 85                              |                        | dBc      |

| Spanous Free Dynamic hange (St Dh)                      | $f_c = 5 \text{ MHz}, V_0 = 2 \text{ V p-p}, R_F = 24.9 \Omega$       |                 | 64                              |                        | dBc      |

| Innut Valtage Neige                                     | f = 100  kHz                                                          |                 | 4.3                             |                        | nV/√Hz   |

| Input Voltage Noise<br>Input Current Noise              | f = 100 kHz                                                           |                 | 4.3<br>1.6                      |                        | pA/√Hz   |

| Differential Gain Error                                 | NTSC, $G = 2$ , $R_L = 150 \Omega$                                    |                 | 0.15                            |                        | %        |

| Differential Phase Error                                | NTSC, $G = 2$ , $R_L = 150 \Omega$                                    |                 | 0.20                            |                        | Degrees  |

| Crosstalk, Output to Output                             | $G = 1$ , $R_L = 100 \Omega$ , $V_{OUT} = 2 V p-p$ ,                  |                 | -89                             |                        | dB       |

|                                                         | V <sub>s</sub> = 3 V @ 1 MHz                                          |                 | <del>-</del> -                  |                        |          |

| DC PERFORMANCE                                          |                                                                       |                 |                                 |                        |          |

| Input Offset Voltage                                    | SELECT = three-state or open, PNP active                              |                 | 200                             | 800                    | μV       |

|                                                         | SELECT = high NPN active                                              |                 | 240                             | 900                    | μV       |

| Input Offset Voltage Drift                              | T <sub>MIN</sub> to T <sub>MAX</sub>                                  |                 | 2                               |                        | μV/°C    |

| Input Bias Current <sup>1</sup>                         | $V_{CM} = 1.5 \text{ V, NPN active}$                                  |                 | 4                               | 6                      | μΑ       |

|                                                         | T <sub>MIN</sub> to T <sub>MAX</sub>                                  |                 | 4                               |                        | μA       |

|                                                         | $V_{CM} = 1.5 \text{ V, PNP active}$                                  |                 | -8                              | -11                    | μΑ       |

| land Offert Comment                                     | T <sub>MIN</sub> to T <sub>MAX</sub>                                  |                 | -8                              | .00                    | μΑ       |

| Input Offset Current                                    | V - 1V+0 2V                                                           | 90              | ±0.1<br>100                     | ±0.9                   | μA<br>dB |

| Open-Loop Gain INPUT CHARACTERISTICS                    | $V_0 = 1 \text{ V to } 2 \text{ V}$                                   | 90              | 100                             |                        | ив       |

|                                                         |                                                                       |                 | 6                               |                        | ΜΩ       |

| Input Impedance<br>Input Capacitance                    |                                                                       |                 | 6<br>2                          |                        | pF       |

| Input Capacitance Input Common-Mode Voltage Range       | $R_1 = 1 k\Omega$                                                     |                 | -0.2 to +3.2                    |                        | V        |

| Common-Mode Rejection Ratio                             | $V_{CM} = 0 \text{ V to } 1.5 \text{ V}$                              | 88              | 100                             |                        | dB       |

| SELECT PIN                                              | VCM = 0 V to 1.3 V                                                    | 00              | 100                             |                        | UD       |

| Crossover Low, Selection Input Voltage                  | Three-state < ±20 μA                                                  |                 | 1.7 to 3                        |                        | V        |

| Crossover High, Selection Input Voltage                 | Timee state < ±20 µA                                                  |                 | 1.1 to 1.7                      |                        | V        |

| Disable Input Voltage                                   |                                                                       |                 | 0 to 1.1                        |                        | V        |

| Disable Switching Speed                                 | 50% of input to <10% of final V <sub>o</sub>                          |                 | 1150                            |                        | ns       |

| Enable Switching Speed                                  |                                                                       |                 | 50                              |                        | ns       |

| OUTPUT CHARACTERISTICS                                  |                                                                       |                 |                                 |                        |          |

| Output Overdrive Recovery Time<br>(Rising/Falling Edge) | $V_1 = -1 \text{ V to } +4 \text{ V, G} = -1$                         |                 | 55/55                           |                        | ns       |

| Output Voltage Swing                                    | $R_L = 1 \text{ k}\Omega$                                             | $-V_{s} + 0.07$ | $+V_{s}-0.03,$<br>$-V_{s}+0.03$ | +V <sub>s</sub> - 0.07 | V        |

| Short-Circuit Current                                   | Sinking and sourcing                                                  |                 | 72                              |                        | mA       |

| Off Isolation                                           | $V_{IN} = 0.2 \text{ V p-p, f} = 1 \text{ MHz, SELECT} = \text{low}$  |                 | -49                             |                        | dB       |

| Capacitive Load Drive                                   | 30% Overshoot                                                         |                 | 20                              |                        | pF       |

| POWER SUPPLY                                            |                                                                       |                 |                                 |                        | _        |

| Operating Range                                         |                                                                       | 2.7             |                                 | 12                     | V        |

| Quiescent Current/Amplifier                             |                                                                       |                 | 6.0                             | 8.0                    | mA       |

| Quiescent Current (Disabled)                            | SELECT = low                                                          |                 | 300                             | 420                    | μA       |

| Power Supply Rejection Ratio $V_S \pm 1 \text{ V}$      |                                                                       | 88              | 100                             |                        | dB       |

$<sup>^{\</sup>rm 1}$  No sign or a plus sign indicates current into the pin; a minus sign indicates current out of the pin.

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                    | Rating                |

|----------------------------------------------|-----------------------|

| Supply Voltage                               | 12.6 V                |

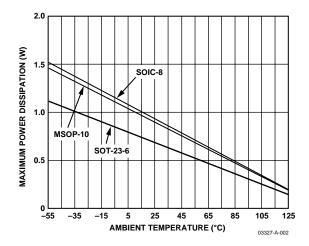

| Power Dissipation                            | See Figure 3          |

| Common-Mode Input Voltage                    | $\pm V_{S} \pm 0.5 V$ |

| Differential Input Voltage                   | ±1.8 V                |

| Storage Temperature                          | −65°C to +125°C       |

| Operating Temperature Range                  | -40°C to +125°C       |

| Lead Temperature Range<br>(Soldering 10 sec) | 300°C                 |

| Junction Temperature                         | 150℃                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **MAXIMUM POWER DISSIPATION**

The maximum safe power dissipation in the AD8027/AD8028 package is limited by the associated rise in junction temperature (T<sub>1</sub>) on the die. The plastic encapsulating the die locally reaches the junction temperature. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the AD8027/AD8028. Exceeding a junction temperature of 175°C for an extended period of time can result in changes in the silicon devices, potentially causing failure.

The still-air thermal properties of the package and PCB ( $\theta_{JA}$ ), ambient temperature ( $T_A$ ), and the total power dissipated in the package ( $P_D$ ) determine the junction temperature of the die. The junction temperature can be calculated as

$$T_I = T_A + (P_D \times \theta_{IA})$$

The power dissipated in the package  $(P_{\rm D})$  is the sum of the quiescent power dissipation and the power dissipated in the package due to the load drive for all outputs. The quiescent power is the voltage between the supply pins  $(V_s)$  times the quiescent current (Is). Assuming the load  $(R_L)$  is referenced to midsupply, then the total drive power is  $V_s/2 \times I_{\rm OUT}$ , some of which is dissipated in the package and some in the load  $(V_{\rm OUT} \times I_{\rm OUT})$ . The difference between the total drive power and the load power is the drive power dissipated in the package.

$P_D = Quiescent Power + (Total Drive Power - Load Power)$

$$P_D = \left(V_S \times I_S\right) + \left(\frac{V_S}{2} \times \frac{V_{OUT}}{R_L}\right) - \frac{V_{OUT}^2}{R_L}$$

RMS output voltages should be considered. If  $R_L$  is referenced to  $V_{S-}$ , as in single-supply operation, then the total drive power is  $V_S \times I_{\rm OUT}$ .

If the rms signal levels are indeterminate, then consider the worst case, when  $V_{OUT} = V_S/4$  for  $R_L$  to midsupply.

$$P_D = \left(V_S \times I_S\right) + \frac{\left(V_S/4\right)^2}{R_I}$$

In single-supply operation with  $R_L$  referenced to  $V_s$ -, worst case is  $V_{\rm OUT} = V_s/2$ .

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . Also, more metal directly in contact with the package leads from metal traces, through holes, ground, and power planes reduces the  $\theta_{JA}$ . Care must be taken to minimize parasitic capacitances at the input leads of high speed op amps, as discussed in the PCB Layout section.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Figure 3 shows the maximum safe power dissipation in the package vs. the ambient temperature for the SOIC-8 (125°C/W), SOT-23-6 (170°C/W), and MSOP-10 (130°C/W) packages on a JEDEC standard 4-layer board.

### **Output Short Circuit**

Shorting the output to ground or drawing excessive current from the AD8027/AD8028 can likely cause catastrophic failure.

Figure 3. Maximum Power Dissipation vs. Ambient Temperature

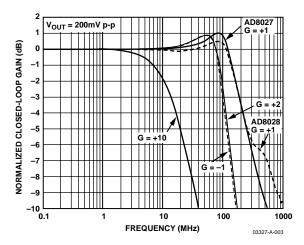

### TYPICAL PERFORMANCE CHARACTERISTICS

Default conditions:  $V_S = 5 \text{ V}$  at  $T_A = 25$ °C,  $R_L = 1 \text{ k}\Omega$ , unless otherwise noted.

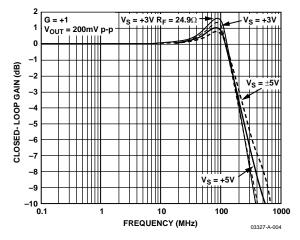

Figure 4. Small Signal Frequency Response for Various Gains

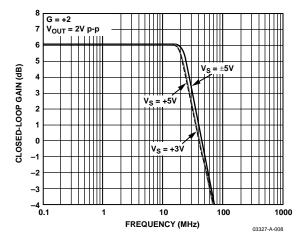

Figure 5. AD8027 Small Signal Frequency Response for Various Supplies

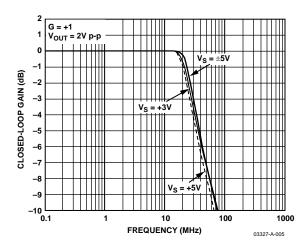

Figure 6. Large Signal Frequency Response for Various Supplies

Figure 7. Small Signal Frequency Response for Various Supplies

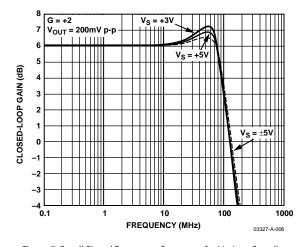

Figure 8. AD8028 Small Signal Frequency Response for Various Supplies

Figure 9. Large Signal Frequency Response for Various Supplies

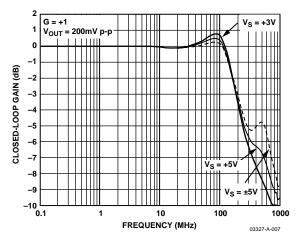

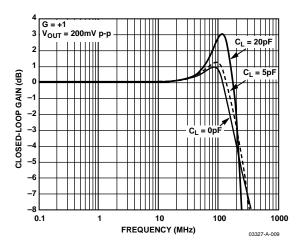

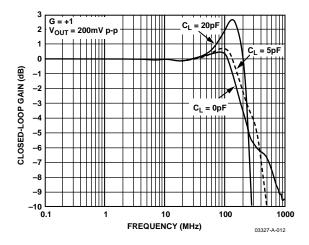

Figure 10. AD8027 Small Signal Frequency Response for Various CLOAD

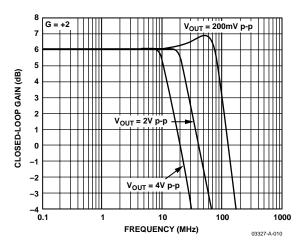

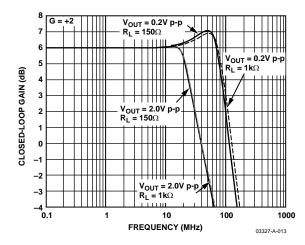

Figure 11. Frequency Response for Various Output Amplitudes

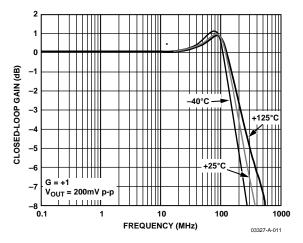

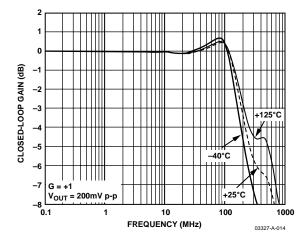

Figure 12. AD8027 Small Signal Frequency Response vs. Temperature

Figure 13. AD8028 Small Signal Frequency Response for Various CLOAD

Figure 14. Small Signal Frequency Response for Various RLOAD Values

Figure 15. AD8028 Small Signal Frequency Response vs. Temperature

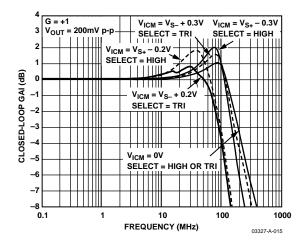

Figure 16. Small Signal Frequency Response vs. Input Common-Mode Voltages

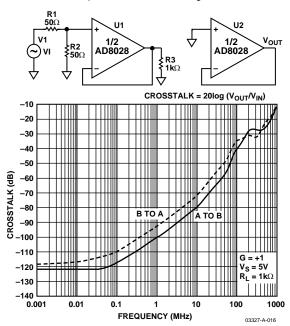

Figure 17. AD8028 Crosstalk Output to Output

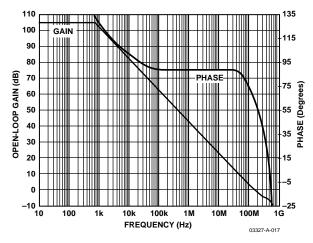

Figure 18. Open-Loop Gain and Phase vs. Frequency

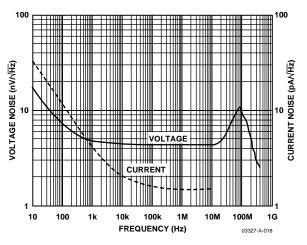

Figure 19. Voltage and Current Noise vs. Frequency

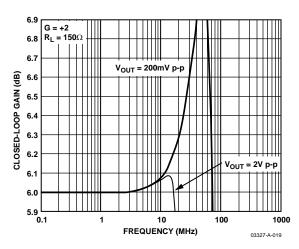

Figure 20. 0.1 dB Flatness Frequency Response

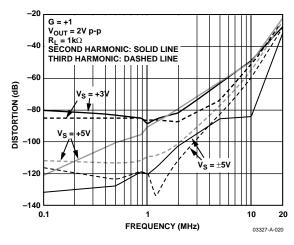

Figure 21. Harmonic Distortion vs. Frequency and Supply Voltage

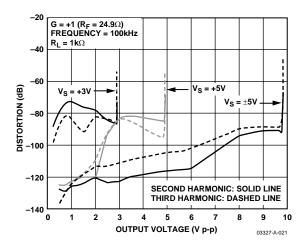

Figure 22. Harmonic Distortion vs. Output Amplitude

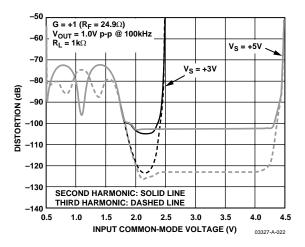

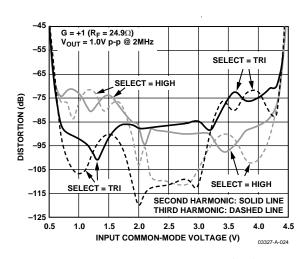

Figure 23. Harmonic Distortion vs. Input Common-Mode Voltage, SELECT = High

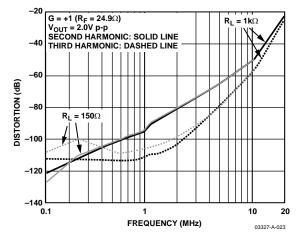

Figure 24. Harmonic Distortion vs. Frequency and Load

Figure 25. Harmonic Distortion vs. Input Common-Mode Voltage,  $V_S = 5 V$

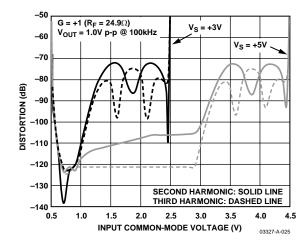

Figure 26. Harmonic Distortion vs. Input Common-Mode Voltage, SELECT = Three-State or Open

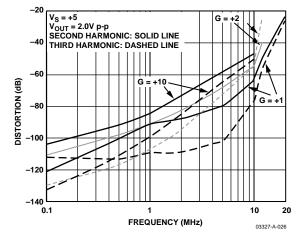

Figure 27. Harmonic Distortion vs. Frequency and Gain

Figure 28. Small Signal Transient Response

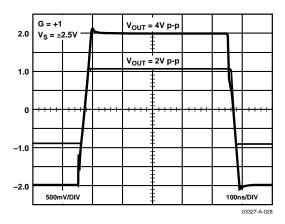

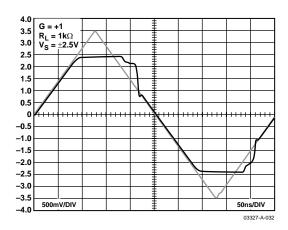

Figure 29. Large Signal Transient Response, G = +1

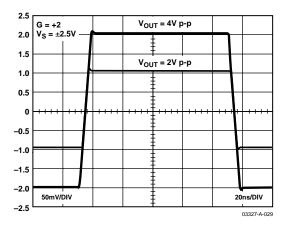

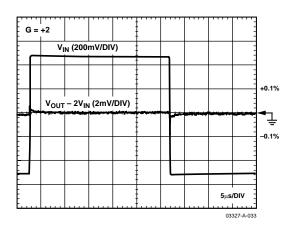

Figure 30. Large Signal Transient Response, G = +2

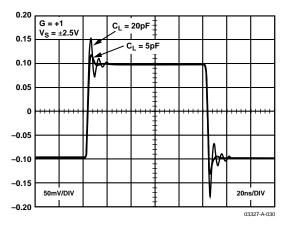

Figure 31. Small Signal Transient Response with Capacitive Load

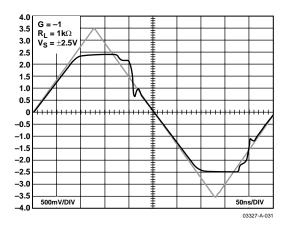

*Figure 32. Output Overdrive Recovery*

Figure 33. Input Overdrive Recovery

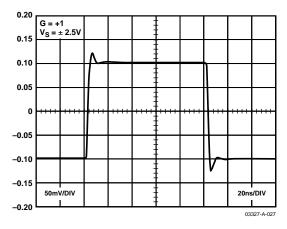

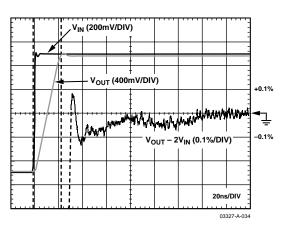

Figure 34. Long-Term Settling Time

Figure 35. 0.1% Short-Term Settling Time

Figure 36. Input Bias Current vs. Temperature

Figure 37. Input Bias Current vs. Input Common-Mode Voltage

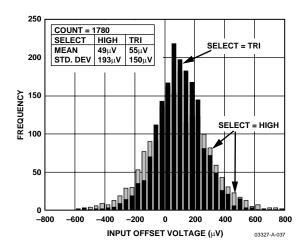

Figure 38. Input Offset Voltage Distribution

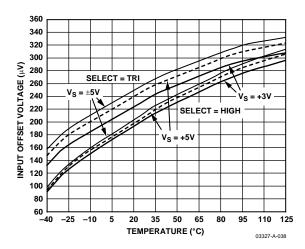

Figure 39. Input Offset Voltage vs. Temperature

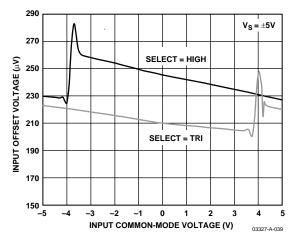

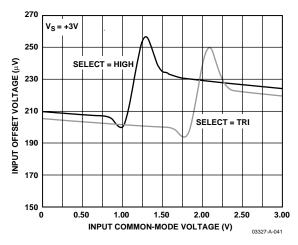

Figure 40. Input Offset Voltage vs. Input Common-Mode Voltage,  $V_S = \pm 5$

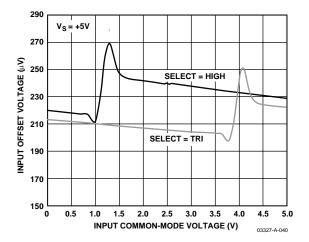

Figure 41. Input Offset Voltage vs. Input Common-Mode Voltage,  $V_S = 5$

Figure 42. Input Offset Voltage vs. Input Common-Mode Voltage,  $V_S = 3$

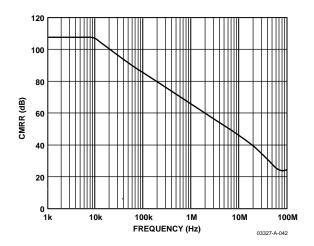

Figure 43. CMRR vs. Frequency

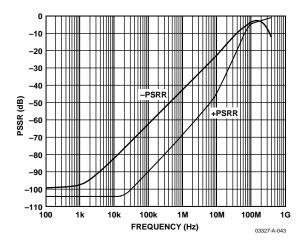

Figure 44. PSRR vs. Frequency

Figure 45. Off Isolation vs. Frequency

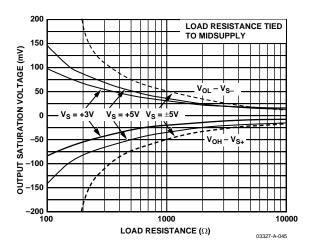

Figure 46. Output Saturation Voltage vs. Output Load

Figure 47. Output Enabled—Impedance vs. Frequency

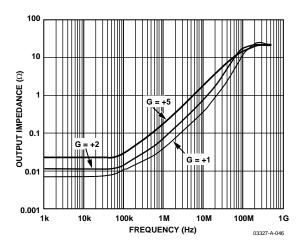

Figure 48. Output Saturation Voltage vs. Temperature

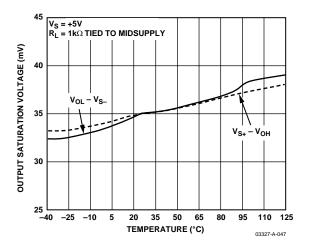

Figure 49. Open-Loop Gain vs. Load Current

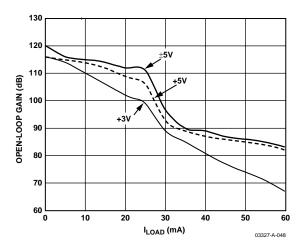

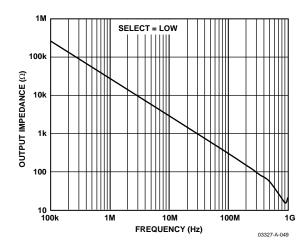

Figure 50. Output Disabled—Impedance vs. Frequency

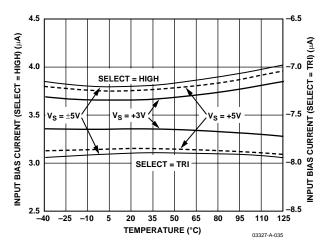

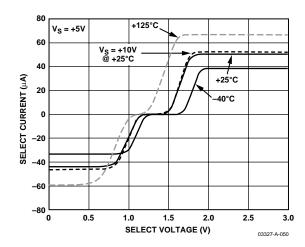

Figure 51. SELECT Pin Current vs. SELECT Pin Voltage and Temperature

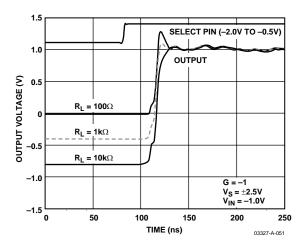

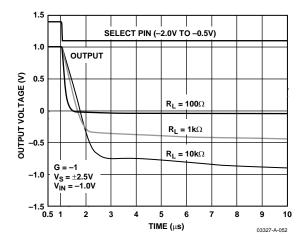

Figure 52. Enable Turn-On Timing

Figure 53. Disable Turn-Off Timing

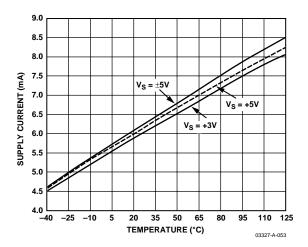

Figure 54. Quiescent Supply Current vs. Supply Voltage and Temperature

### THEORY OF OPERATION

The AD8027/AD8028 are rail-to-rail input/output amplifiers designed in the Analog Devices XFCB process. The XFCB process enables the AD8027/AD8028 to run on 2.7 V to 12 V supplies with 190 MHz of bandwidth and over 100 V/µs of slew rate. The AD8027/AD8028 have 4.3 nV/√Hz of wideband noise with 17 nV/ $\sqrt{\text{Hz}}$  noise at 10 Hz. This noise performance, with an offset and drift performance of less than 900 µV maximum and 1.5  $\mu$ V/°C typical, respectively, makes the AD8027/AD8028 ideal for high speed, precision applications. Additionally, the input stage operates 200 mV beyond the supply rails and shows no phase reversal. The amplifiers feature overvoltage protection on the input stage. Once the inputs exceed the supply rails by 0.7 V, ESD protection diodes are turned on, drawing excessive current through the differential input pins. A series input resistor should be included to limit the input current to less than 10 mA.

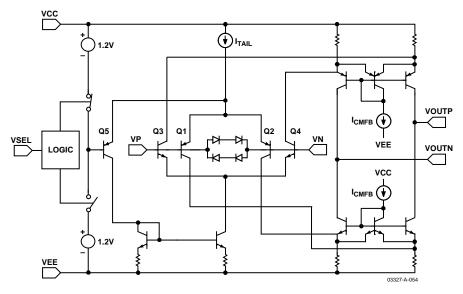

### **INPUT STAGE**

The rail-to-rail input performance is achieved by operating complementary input pairs. Which pair is on is determined by the common-mode level of the differential input signal. As shown in Figure 55, a tail current ( $I_{TAIL}$ ) is generated that sources the PNP differential input structure consisting of Q1 and Q2. A reference voltage is generated internally that is connected to the base of Q5. This voltage is continually compared against the common-mode input voltage. When the common-mode level exceeds the internal reference voltage, Q5 diverts the tail current ( $I_{TAIL}$ ) from the PNP input pair to a current mirror that sources the NPN input pair consisting of Q3 and Q4.

The NPN input pair can now operate at 200 mV above the positive rail. Both input pairs are protected from differential input signals above 1.4 V by four diodes across the input (see Figure 55). In the event of differential input signals that exceed 1.4 V, the diodes conduct and excessive current flows through them. A series input resistor should be included to limit the input current to 10 mA.

### **CROSSOVER SELECTION**

The AD8027/AD8028 have a feature called crossover selection, which allows the user to choose the crossover point between the PNP/NPN differential pairs. Although the crossover region is small, operating in this region should be avoided, because it can introduce offset and distortion to the output signal. To help avoid operating in the crossover region, the AD8027/AD8028 allow the user to select from two preset crossover locations (voltage levels) using the SELECT pin. As shown in Figure 55, the crossover region is about 200 mV and is defined by the voltage level at the base of Q5. Internally, two separate voltage sources are created approximately 1.2 V from either rail. One or the other is connected to Q5, based on the voltage applied to the SELECT pin. This allows either dominant PNP pair operation, when the SELECT pin is left open, or dominant NPN pair operation, when the SELECT pin is pulled high.

The SELECT pin also provides the traditional power-down function when it is pulled low. This allows the designer to achieve the best precision and ac performance for high-side and low-side signal applications. See Figure 50 through Figure 53 for SELECT pin characteristics.

Figure 55. Simplified Input Stage

In the event that the crossover region cannot be avoided, specific attention has been given to the input stage to ensure constant transconductance and minimal offset in all regions of operation. The regions are PNP input pair running, NPN input pair running, and both running at the same time (in the 200 mV crossover region). Maintaining constant transconductance in all regions ensures the best wideband distortion performance when going between these regions. With this technique, the AD8027/AD8028 can achieve greater than 80 dB SFDR for a 2 V p-p, 1 MHz, and G=1 signal on  $\pm 1.5$  V supplies. Another requirement needed to achieve this level of distortion is that the offset of each pair must be laser trimmed to achieve greater than 80 dB SFDR, even for low frequency signals.

### **OUTPUT STAGE**

The AD8027/AD8028 use a common-emitter output structure to achieve rail-to-rail output capability. The output stage is designed to drive 50 mA of linear output current, 40 mA within 200 mV of the rail, and 2.5 mA within 35 mV of the rail. Loading of the output stage, including any possible feedback network, lowers the open-loop gain of the amplifier. Refer to Figure 49 for the loading behavior. Capacitive load can degrade the phase margin of the amplifier. The AD8027/AD8028 can drive up to 20 pF, G = 1, as shown in Figure 10. A small (25  $\Omega$  to 50  $\Omega$ ) series resistor,  $R_{\text{SNUB}}$ , should be included, if the capacitive load is to exceed 20 pF for a gain of 1. Increasing the closed-loop gain increases the amount of capacitive load that can be driven before a series resistor needs to be included.

### **DC ERRORS**

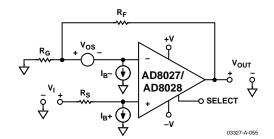

The AD8027/AD8028 use two complementary input stages to achieve rail-to-rail input performance, as mentioned in the Input Stage section. To use the dc performance over the entire common-mode range, the input bias current and input offset voltage of each pair must be considered.

Referring to Figure 56, the output offset voltage of each pair is calculated by

$$V_{OS, PNP, OUT} = V_{OS, PNP} \left( \frac{R_G + R_F}{R_G} \right),$$

$$V_{OS, NPN, OUT} = V_{OS, NPN} \left( \frac{R_G + R_F}{R_G} \right)$$

where the difference of the two is the discontinuity experienced when going through the crossover region. The size of the discontinuity is defined as

$$V_{DIS} = \left(V_{OS, PNP} - V_{OS, NPN}\right) \times \left(\frac{R_G + R_F}{R_G}\right)$$

Using the crossover select feature of the AD8027/AD8028 helps to avoid this region. In the event that the region cannot be avoided, the quantity ( $V_{OS, PNP} - V_{OS, NPN}$ ) is trimmed to minimize this effect.

Because the input pairs are complementary, the input bias current reverses polarity when going through the crossover region shown in Figure 37. The offset between pairs is described by

$$V_{OS,PNP} - V_{OS,NPN} = \left(I_{B,PNP} - I_{B,NPN}\right) \times \left[R_{S}\left(\frac{R_{G} + R_{F}}{R_{G}}\right) - R_{F}\right]$$

$I_{B,\,PNP}$  is the input bias current of either input when the PNP input pair is active, and  $I_{B,\,NPN}$  is the input bias current of either input pair when the NPN pair is active. If  $R_S$  is sized so that when multiplied by the gain factor it equals  $R_F$ , this effect is eliminated. It is strongly recommended to balance the impedances in this manner when traveling through the crossover region to minimize the dc error and distortion. As an example, assuming that the PNP input pair has an input bias current of 6  $\mu A$  and the NPN input pair has an input bias current of  $-2~\mu A$ , a 200  $\mu V$  shift in offset occurs when traveling through the crossover region with  $R_F$  equal to 0  $\Omega$  and  $R_S$  equal to 25  $\Omega$ .

In addition to the input bias current shift between pairs, each input pair has an input bias current offset that contributes to the total offset in the following manner:

$$\Delta V_{OS} = I_{B+} R_S \left( \frac{R_G + R_F}{R_G} \right) - I_{B-} R_F$$

Figure 56. Op Amp DC Error Sources

### WIDEBAND OPERATION

Voltage feedback amplifiers can use a wide range of resistor values to set their gain. Proper design of the application's feedback network requires consideration of the following issues:

- Poles formed by the amplifier's input capacitances with the resistances seen at the amplifier's input terminals

- Effects of mismatched source impedances

- Resistor value impact on the application's voltage noise

- Amplifier loading effects

The AD8027/AD8028 have an input capacitance of 2 pF. This input capacitance forms a pole with the amplifier's feedback network, destabilizing the loop. For this reason, it is generally desirable to keep the source resistances below 500  $\Omega$ , unless some capacitance is included in the feedback network. Likewise, keeping the source resistances low also takes advantage of the AD8027/AD8028's low input referred voltage noise of 4.3 nV/ $\sqrt{\rm Hz}$ .

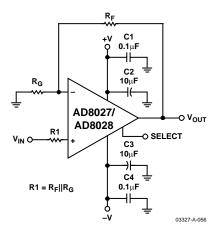

With a wide bandwidth of over 190 MHz, the AD8027/AD8028 have numerous applications and configurations. The AD8027/AD8028 part shown in Figure 57 is configured as a noninverting amplifier. An easy selection table of gain, resistor values, bandwidth, slew rate, and noise performance is presented in Table 5, and the inverting configuration is shown in Figure 58.

Figure 57. Wideband Noninverting Gain Configuration

Table 5. Component Values, Bandwidth, and Noise Performance ( $V_s = \pm 2.5 \text{ V}$ )

| Noise Gain<br>(Noninverting) | R <sub>SOURCE</sub> (Ω) | R <sub>F</sub> (Ω) | R <sub>G</sub> (Ω) | -3 dB<br>SS BW<br>(MHz) | Output<br>Noise with<br>Resistors<br>(nV/√Hz) |

|------------------------------|-------------------------|--------------------|--------------------|-------------------------|-----------------------------------------------|

| 1                            | 50                      | 0                  | N/A                | 190                     | 4.4                                           |

| 2                            | 50                      | 499                | 499                | 95                      | 10                                            |

| 10                           | 50                      | 499                | 54.9               | 13                      | 45                                            |

Figure 58. Wideband Inverting Gain Configuration

# CIRCUIT CONSIDERATIONS Balanced Input Impedances

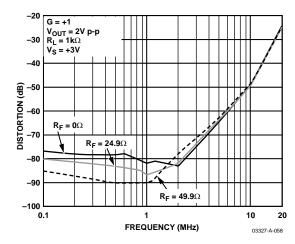

Balanced input impedances can help to improve distortion performance. When the amplifier transitions from PNP pair to NPN pair operation, a change in both the magnitude and direction of the input bias current occurs. When multiplied times imbalanced input impedances, a change in offset can result. The key to minimizing this distortion is to keep the input impedances balanced on both inputs. Figure 59 shows the effect of the imbalance and degradation in distortion performance for a 50  $\Omega$  source impedance, with and without a 50  $\Omega$  balanced feedback path.

Figure 59. SFDR vs. Frequency and Various R<sub>F</sub>

### **PCB Layout**

As with all high speed op amps, achieving optimum performance from the AD8027/AD8028 requires careful attention to PCB layout. Particular care must be exercised to minimize lead lengths of the bypass capacitors. Excess lead inductance can influence the frequency response and even cause high frequency oscillations. The use of a multilayer board with an internal ground plane can reduce ground noise and enable a tighter layout.

To achieve the shortest possible lead length at the inverting input, the feedback resistor,  $R_F$ , should be located beneath the board and span the distance from the output, Pin 6, to the input, Pin 2. The return node of the resistor,  $R_G$ , should be situated as closely as possible to the return node of the negative supply bypass capacitor connected to Pin 4.

On multilayer boards, all layers underneath the op amp should be cleared of metal to avoid creating parasitic capacitive elements. This is especially true at the summing junction (the –input). Extra capacitance at the summing junction can cause increased peaking in the frequency response and lower phase margin.

### Grounding

To minimize parasitic inductances and ground loops in high speed, densely populated boards, a ground plane layer is critical. Understanding where the current flows in a circuit is critical in the implementation of high speed circuit design. The length of the current path is directly proportional to the magnitude of the parasitic inductances and, therefore, the high frequency impedance of the path. Fast current changes in an inductive ground return can create unwanted noise and ringing.

The length of the high frequency bypass capacitor pads and traces is critical. A parasitic inductance in the bypass grounding works against the low impedance created by the bypass capacitor. Because load currents flow from supplies as well as ground, the load should be placed at the same physical location as the bypass capacitor ground. For large values of capacitors, which are intended to be effective at lower frequencies, the current return path length is less critical.

### **Power-Supply Bypassing**

Power-supply pins are actually inputs, and care must be taken to provide a clean, low noise, dc voltage source to these inputs. The bypass capacitors have two functions:

- Provide a low impedance path for unwanted frequencies from the supply inputs to ground, thereby reducing the effect of noise on the supply lines.

- Provide sufficient localized charge storage, for fast switching conditions and minimizing the voltage drop at the supply pins and the output of the amplifier. This is usually accomplished with larger electrolytic capacitors.

Decoupling methods are designed to minimize the bypassing impedance at all frequencies. This can be accomplished with a combination of capacitors in parallel to ground.

Good-quality ceramic chip capacitors should be used and always kept as close as possible to the amplifier package . A parallel combination of a 0.01  $\mu F$  ceramic and a 10  $\mu F$  electrolytic covers a wide range of rejection for unwanted noise. The 10  $\mu F$  capacitor is less critical for high frequency bypassing, and, in most cases, one per supply line is sufficient.

### **APPLICATIONS**

### **USING THE SELECT PIN**

The AD8027/AD8028's unique SELECT pin has two functions:

- The power-down function places the AD8027/AD8028 into low power consumption mode. In power-down mode, the amplifiers draw 450 μA (typical) of supply current.

- The second function, as mentioned in the Theory of Operation section, shifts the crossover point (where the NPN/PNP input differential pairs transition from one to the other) closer to either the positive supply rail or the negative supply rail. This selectable crossover point allows the user to minimize distortion based on the input signal and environment. The default state is 1.2 V from the positive power supply, with the SELECT pin left floating or in three-state.

Table 6 lists the SELECT pin's required voltages and modes.

Table 6. SELECT Pin Mode Control

|                                                      | SELECT Pin Voltage (V) |                       |                       |  |

|------------------------------------------------------|------------------------|-----------------------|-----------------------|--|

| Mode                                                 | $V_s = \pm 5 V$        | V <sub>s</sub> = +5 V | V <sub>s</sub> = +3 V |  |

| Disable                                              | −5 to −4.2             | 0 to 0.8              | 0 to 0.8              |  |

| Crossover Referenced<br>–1.2 V to Positive<br>Supply | -4.2 to<br>-3.3        | 0.8 to 1.7            | 0.8 to 1.7            |  |

| Crossover Referenced<br>+1.2 V to Negative<br>Supply | -3.3 to +5             | 1.7 to 5.0            | 1.7 to 3.0            |  |

When the input stage transitions from one input differential pair to the other, there is virtually no noticeable change in the output waveform.

The disable time of the AD8027/AD8028 amplifiers is load-dependent. Typical data is presented in Table 7. See Figure 52 and Figure 53 for the actual switching measurements.

Table 7. DISABLE Switching Speeds

| ,                | Supply Voltages ( $R_L = 1 \text{ k}\Omega$ ) |         |         |  |

|------------------|-----------------------------------------------|---------|---------|--|

| Time             | ±5 V                                          | +5 V    | +3 V    |  |

| ton              | 45 ns                                         | 50 ns   | 50 ns   |  |

| t <sub>OFF</sub> | 980 ns                                        | 1100 ns | 1150 ns |  |

### **DRIVING A 16-BIT ADC**

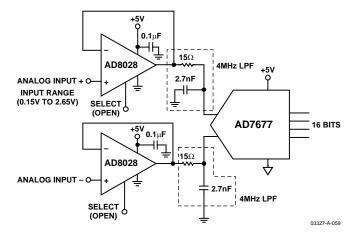

With the adjustable crossover distortion selection point and low noise, the AD8028 is an ideal amplifier for driving or buffering input signals into high resolution ADCs such as the AD7767, a 16-bit, 1 LSB INL, 1 MSPS differential ADC. Figure 60 shows the typical schematic for driving the ADC. The AD8028 driving the AD7677 offers performance close to non-rail-to-rail amplifiers and avoids the need for an additional supply other than the single 5 V supply already used by the ADC.

In this application, the SELECT pins are biased to avoid the crossover region of the AD8028 for low distortion operation.

Summary test data for the schematic shown in Figure 60 is listed in Table 8.

Figure 60. Unity Gain Differential Drive

Table 8. ADC Driver Performance,  $f_C$  = 100 kHz,  $V_{\rm OUT}$  = 4.7 V p-p

| Parameter                  | Measurement |

|----------------------------|-------------|

| Second Harmonic Distortion | –105 dB     |

| Third Harmonic Distortion  | -102 dB     |

| THD                        | -102 dB     |

| SFDR                       | +105 dBc    |

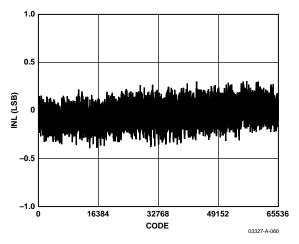

As shown in Figure 61, the AD8028 and AD7677 combination offers excellent integral nonlinearity (INL).

Figure 61. Integral Nonlinearity

### **BAND-PASS FILTER**

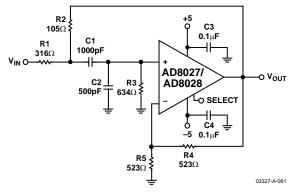

In communication systems, active filters are used extensively in signal processing. The AD8027/AD8028 are excellent choices for active filter applications. In realizing this filter, it is important that the amplifier have a large signal bandwidth of at least  $10\times$  the center frequency, fo. Otherwise, a phase shift can occur in the amplifier, causing instability and oscillations.

In Figure 62, the AD8027/AD8028 part is configured as a 1 MHz band-pass filter. The target specifications are  $f_{\rm O}=1$  MHz and a -3 dB pass band of 500 kHz. To start the design, select  $f_{\rm O}$ , Q, C1, and R4. Then use the following equations to calculate the remaining variables:

$$Q = \frac{f_O \text{ (MHz)}}{Band Pass \text{ (MHz)}}$$

$k = 2\pi f_0 C1$

C2 = 0.5C1

R1 = 2/k, R2 = 2/(3k), R3 = 4/k

H = 1/3(6.5 - 1/Q)

R5 = R4/(H-1)

Figure 62. Band-Pass Filter Schematic

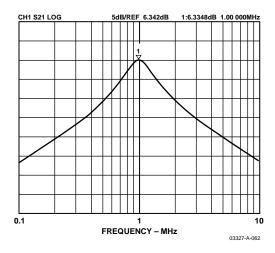

The test data shown in Figure 63 indicates that this design yields a filter response with a center frequency of  $f_0$  = 1 MHz, and a bandwidth of 450 kHz.

Figure 63. Band-Pass Filter Response

### **DESIGN TOOLS AND TECHNICAL SUPPORT**

Analog Devices, Inc. (ADI) is committed to simplifying the design process by providing technical support and online design tools. ADI offers technical support via free evaluation boards, sample ICs, interactive evaluation tools, data sheets, spice models, application notes, and phone and email support available at www. analog.com.

## **OUTLINE DIMENSIONS**

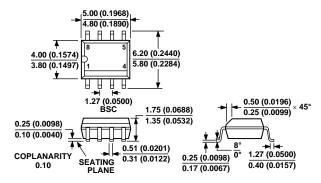

COMPLIANT TO JEDEC STANDARDS MS-012AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 64. 8-Lead Standard Small Outline Package [SOIC] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

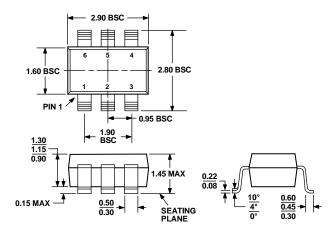

### COMPLIANT TO JEDEC STANDARDS MO-178AB

Figure 65. 6-Lead Small Outline Transistor Package [SOT-23] (RT-6) Dimensions shown in millimeters

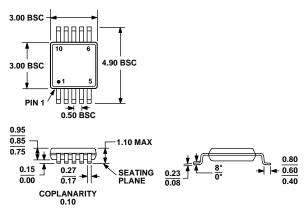

#### COMPLIANT TO JEDEC STANDARDS MO-187BA

Figure 66. 10-Lead Mini Small Outline Package [MSOP] (RM-10) Dimensions shown in millimeters

Rev. C | Page 23 of 24

### **ORDERING GUIDE**

| Model                         | Minimum<br>Ordering Quantity | Temperature Range | Package Description | Package Option | Branding |

|-------------------------------|------------------------------|-------------------|---------------------|----------------|----------|

| AD8027AR                      | 1                            | -40°C to +125°C   | 8-Lead SOIC         | R-8            | <u> </u> |

| AD8027AR-REEL                 | 2,500                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8027AR-REEL7                | 1,000                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8027ARZ <sup>1</sup>        | 1                            | −40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8027ARZ-REEL <sup>1</sup>   | 2,500                        | −40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8027ARZ-REEL7 <sup>1</sup>  | 1,000                        | −40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8027ART-R2                  | 250                          | -40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B      |

| AD8027ART-REEL                | 10,000                       | −40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B      |

| AD8027ART-REEL7               | 3,000                        | −40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B      |

| AD8027ARTZ-R2 <sup>1</sup>    | 250                          | -40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B#     |

| AD8027ARTZ-REEL <sup>1</sup>  | 10,000                       | -40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B#     |

| AD8027ARTZ-REEL7 <sup>1</sup> | 3,000                        | -40°C to +125°C   | 6-Lead SOT-23       | RT-6           | H4B#     |

| AD8028AR                      | 1                            | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028AR-REEL                 | 2,500                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028AR-REEL7                | 1,000                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028ARZ <sup>1</sup>        | 1                            | −40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028ARZ-REEL <sup>1</sup>   | 2,500                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028ARZ-REEL7 <sup>1</sup>  | 1,000                        | -40°C to +125°C   | 8-Lead SOIC         | R-8            |          |

| AD8028ARM                     | 1                            | -40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B      |

| AD8028ARM-REEL                | 3,000                        | −40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B      |

| AD8028ARM-REEL7               | 1,000                        | -40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B      |

| AD8028ARMZ <sup>1</sup>       | 1                            | -40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B#     |

| AD8028ARMZ-REEL <sup>1</sup>  | 3,000                        | -40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B#     |

| AD8028ARMZ-REEL7 <sup>1</sup> | 1,000                        | -40°C to +125°C   | 10-Lead MSOP        | RM-10          | H5B#     |

$<sup>^{1}</sup>$  Z = Pb-free part, # denotes lead-free, may be top or bottom marked.