## DEMO MANUAL DC2707B

## LTC4418 Dual Channel Prioritized PowerPath Controller

### DESCRIPTION

Demonstration circuit 2707B uses the LTC<sup>®</sup>4418 to arbitrate between two input supply rails, selecting the highest priority, valid supply to power the load. The V1 rail is defined to have higher priority and the V2 rail has lower priority. Both rails have individual overvoltage and undervoltage comparators for setting valid window thresholds with external resistive dividers. If the highest priority rail voltage V1 falls out of the defined window (overvoltage or undervoltage), the V2 rail, if it is valid, is enabled and powers the load. Two or more LTC4418s can be cascaded to provide switchover between more than two rails.

Design files for this circuit board are available at http://www.analog.com/DC2707B

All registered trademarks and trademarks are the property of their respective owners.

#### PERFORMANCE SUMMARY

Specifications are at  $T_A = 25^{\circ}C$

| SYMBOL                     | PARAMETER                                                | CONDITIONS                                                      | MIN     | ТҮР       | MAX         | UNITS    |

|----------------------------|----------------------------------------------------------|-----------------------------------------------------------------|---------|-----------|-------------|----------|

| V1, V2, V <sub>OUT</sub>   | V1, V2, V <sub>OUT</sub> Operating Supply Range          |                                                                 | 2.5     |           | 40          | V        |

| VINTVCC                    | V <sub>INTVCC</sub> Voltage                              |                                                                 | 2.5     | 3.3       | 4           | V        |

| $\Delta V_{G}$             | Open Clamp Voltage (V <sub>S</sub> –V <sub>G</sub> )     | V <sub>OUT</sub> = 11V, G1 = G2 = Open                          | 5.4     | 6.2       | 6.7         | V        |

| $\Delta V_{G(SOURCE)}$     | Sourcing (V <sub>S</sub> –V <sub>G</sub> ) Clamp Voltage | V <sub>OUT</sub> = 11V, I = -10µA                               | 5.8     | 6.6       | 7           | V        |

| ΔV <sub>G(SINK)</sub>      | Sinking (V <sub>S</sub> –V <sub>G</sub> ) Clamp Voltage  | V <sub>OUT</sub> = 11V, I = 10μA                                | 4.5     | 5.2       | 6           | V        |

| $\Delta V_{G(OFF)}$        | Gate Off Threshold                                       | VS1 = VS2 = 2.8V, V <sub>OUT</sub> = 11V, Gate Rising           | 0.2     | 0.3       | 0.4         | V        |

| I <sub>G(DN)</sub>         | Gate Pull-Down Current                                   | VG = 3V, VS Floating                                            | 28      | 60        | 120         | mA       |

| V <sub>REV</sub>           | Reverse Voltage Threshold                                | Measure (V1 or V2) – V <sub>OUT</sub> Falling                   | 75      | 125       | 185         | mV       |

| t <sub>G(SWITCHOVER)</sub> | Break-Before-Make Time                                   | $V_{OUT} = 11V, C_{GATE} = 10nF$                                | 1       | 2.7       | 4           | μs       |

| t <sub>SS</sub>            | Soft-Start Timeout                                       |                                                                 | 20      | 35        | 70          | ms       |

| V <sub>EN(TH)</sub>        | EN Threshold Voltage                                     | EN Rising                                                       | 0.6     | 1         | 1.4         | V        |

| V <sub>SHDN</sub> (TH)     | SHDN Threshold Voltage                                   | SHDN Rising                                                     | 0.6     | 1         | 1.4         | V        |

| V <sub>SHDN_EN(HYS)</sub>  | SHDN, EN Threshold Hysteresis                            |                                                                 |         | 130       |             | mV       |

| I <sub>CTRL</sub>          | SHDN, EN Pull-Up Current                                 | SHDN = EN = 0V                                                  | -1.5    | -3.2      | -5.5        | μA       |

| V <sub>TH</sub>            | OV/UV Comparator Threshold                               | V <sub>OUT</sub> = 11V, OV Rising, UV Falling                   | 0.985   | 1         | 1.015       | V        |

| V <sub>HYS(INT)</sub>      | OV/UV Comparator Hysteresis                              | V <sub>OUT</sub> = 11V,                                         | 15      | 30        | 45          | mV       |

| I <sub>LEAK</sub>          | OV/UV Leakage Current                                    | OV = 1.015V, UV = 0.985V                                        |         |           | ±10         | nA       |

| I <sub>TMR</sub>           | TMR Pull-Up Current<br>TMR Pull-Down Current             | Timer On, $V_{TMRM} \le 600mV$<br>Timer On, $V_{TMRM} \ge 1.6V$ | -1<br>1 | -2<br>2   | -3.5<br>3.5 | μΑ<br>μΑ |

| t <sub>VALID</sub>         | OV, UV Validation Time                                   | TMR = V <sub>INTVCC</sub><br>CTMR = 1nF                         | 2<br>9  | 3.5<br>16 | 7<br>32     | μs<br>ms |

| V1                         | Operating Voltage of Channel V1                          |                                                                 | 9.35    | 12        | 14.65       | V        |

| V2                         | Operating Voltage of Channel V2                          |                                                                 | 18.45   | 24        | 29.4        | V        |

| I <sub>LOAD</sub>          | Load Current                                             |                                                                 | 0       | 1         |             | A        |

| AVI                        | Auxiliary Voltage Input                                  |                                                                 | 6       |           | 24          | V        |

| External 3.3V              | Input Voltage Range                                      |                                                                 | 3.0     | 3.3       | 3.5         | V        |

UG-1312 Rev A

# OVERVIEW

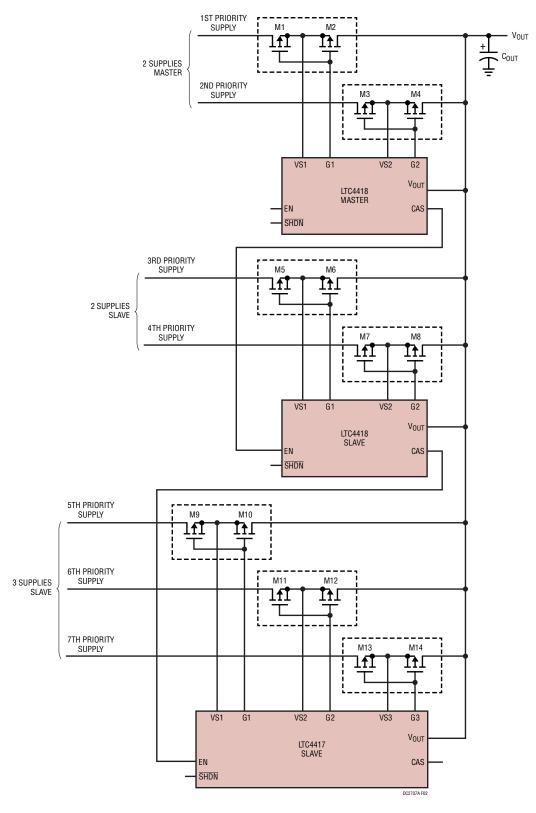

The LTC4418 controls two sets of external back-to-back P-channel MOSFETs to connect the proper supply rail to the load. Precision comparators monitor both rails continuously against their OV/UV window. The highest priority input supply whose voltage is within its OV/UV window for the adjustable validation time of 15.8ms or 3.5µs (selectable on the board) is considered valid and connected to the load. A low signal on the VALID1 and VALID2 pins indicates validation of the V1 and V2 voltages. Connecting the CAS output to the EN pin on another LTC4418 or LTC4417 increases the number of multiplexed input supplies. Figure 2 demonstrates cascading prioritized controllers.

DC2707B is designed to operate from 12V and 24V, applied to V1 and V2 respectively. The valid range of both supplies is approximately 20% as set by OV and UV comparators and their associated resistive dividers. The board V1 and V2 inputs are protected from positive and negative glitches with bidirectional TVS diodes that can continuously tolerate input voltages up to  $\pm 30V$  while the LTC4418 V1 and V2 pins can tolerate  $\pm 60V$  and -42V. Maximum continuous load current is 2.5A (limited by the MOSFET), and a maximum pulse drain current of this MOSFET is 30A.

LEDs with accompanying circuitry are included to provide visual information about the operating status of the rails V1 and V2. This LED circuit is powered from the 3.3V auxiliary rail with two options of getting power: from external power supply connected directly to auxiliary rail or from the low dropout linear regulator LT3060 (U5) installed on the board with the input voltage range 6V to 24V.

One of the rails V1 or V2 can be used to power LT3060 when its voltage is within the LT3060 input voltage range.

The auxiliary 3.3V rail also powers 100k  $\Omega$  pull-ups for both VALID pins.

## **OPERATING PRINCIPLES**

To eliminate back-and-forth switching during switchover, the LTC4418 provides a fixed 30mV hysteresis in the OV and UV comparator and an externally adjustable current mode hysteresis using the OV/UV resistive dividers. The JP1 (HYS) jumper allows selection of a fixed 30mV or adjustable hysteresis.

The controller's "break-before-make" switching method prevents cross conduction between input channels and reverse current from the output capacitor into the selected input supply.

Each channel's control circuit has a REV comparator that delays the connection until the output voltage droops 125mV below the input voltage. This prevents reverse current.

The LTC4418 has two common control pins: EN and  $\overline{\rm SHDN}.$

Pulling the EN pin below 1V turns off all external back-toback P-channel MOSFETs. When this pin is driven above 1V, the highest priority valid channel is connected to the load without resetting the adjustable OV/UV timers. Pulling the SHDN pin below 1.0V turns off all external back-to-back P-channel MOSFETs, placing the controller in a low current state and resetting the adjustable timers used to validate the input rail voltages. It requires a timer interval to validate each rail voltage after the SHDN pin signal goes high.

To minimize inrush current at start-up, the gate driver softstarts the gate drive of the first input to connect to  $V_{OUT}$ . The gate pin is regulated to create an approximately 4V/ ms slew rate on  $V_{OUT}$ . Logic level P-channel MOSFETs with a threshold below 1V will result in faster soft-start slew rate on  $V_{OUT}$ . Slew rate control is terminated when any channel disconnects or a time period of 35ms has elapsed. Once soft-start has terminated, the gate driver operates normally. A SHDN low to high transition reactivates softstart, provided  $V_{OUT}$  drops below 2.3V before SHDN is high.  $V_{OUT}$  dropping below 1.7V also reactivates soft-start.

When connecting a high voltage supply to a lower voltage output, significant inrush current can occur while charging an output capacitor with low ESR. Inrush current during a switchover can cause two issues, P-channel MOSFETs are subjected to damaging power dissipation UG-1312 Rev A

# **OPERATING PRINCIPLES**

and an undesirable UV fault from significant input voltage droop also known as motorboating.

With the LTC4418, inrush current can be reduced by slew rate limiting the output voltage. The gate driver can be configured to slew rate limit the output voltage with

a resistor, capacitor and Schottky diode, as shown in Figure 4 of the data sheet.

The LTC4418 does not actively protect against output short circuit events and there may be some cases where the output short may cause the MOSFET to fail.

## TURRETS

**V1 (12V):** 12V supply input, do not exceed +30V or -30V due to protection TVS present on the board.

**V2 (24V):** 24V supply input, do not exceed +30V or -30V due to protection TVS present on the board.

**GND:** Adjacent ground connection for input supplies and for load.

**V**<sub>OUT</sub>: Output for the load. Designed for 2.5A maximum continuous current (with component selected).

**6V to 24V:** Auxiliary voltage input (AVI) converted by an LDO U5 to 3.3V for LEDs, logic, and pull-ups.

**3.3V:** 3.3V output provided by U5 or by external supply.

Each of the following turrets is directly connected to the LTC4418 pin of the same name:

**VALID1:** Pulled up with 100k $\Omega$  to auxiliary 3.3V supply.

**VALID2:** Pulled up with 100k $\Omega$  to auxiliary 3.3V supply.

**EN:** Pulled up by internal 3.2µA to  $INTV_{CC}$  or by  $10k\Omega$  to external 3.3V.

**SHDN**: Pulled up by internal 3.2 $\mu$ A to INTV<sub>CC</sub> or by 100k $\Omega$  to external 3.3V.

**CAS:** Used to cascade a second LTC4418 or LTC4417.

Connect the CAS turret of the high priority LTC4418 to the EN pin of the lower priority LTC4418.

## JUMPERS

**JP1**, **HYS**: Add 30mV fixed hysteresis to the OV and UV comparators or 3% referred to actual supply input. In the RHYS position input referred hysteresis is set to 0.25V as controlled by R15. Default position is 30mV.

Note: Be careful when changing hysteresis. It affects the risk of motorboating.

**JP2, EN:** Controls EN pin. Default position (EXT + 3.3V) connects EN to the auxiliary 3.3V supply. Changing the jumper position connects EN to GND.

**JP3, SHDN:** Controls **SHDN** pin. Default position (EXT + 3.3V) connects **SHDN** to the auxiliary 3.3V supply. Changing the jumper position connects **SHDN** to GND. Do not change the JP3 position on the fly.

**JP4**, **VALIDATION TIME:** Allows to set 3.5µs or 15.8ms validation time. Default position is 3.5µs.

## LEDS

**D6:** Indicates power present at  $V_{OUT}$ .

D7: Indicates power being taken from V1.

**D8:** Indicates power being taken from V2.

D9: Indicates validation of V1.

D10: Indicates validation of V2.

D11: Indicates auxiliary 3.3V supply.

UG-1312 Rev A

## **QUICK START PROCEDURE**

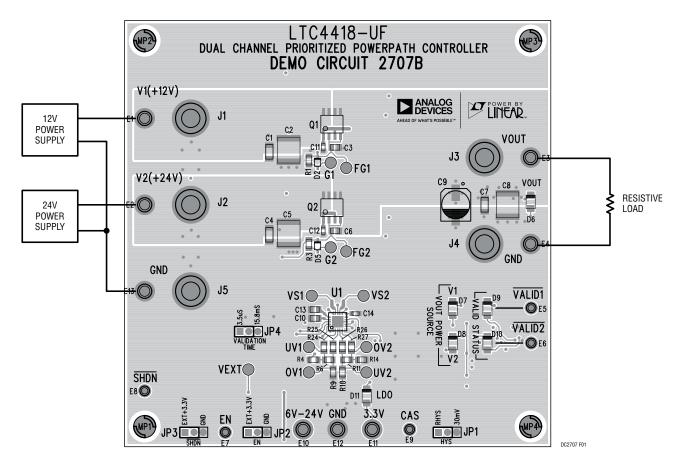

Refer to Figure 1 for proper measurement equipment setup and follow the procedure below:

- 1. Disconnect both power supply inputs from the board.

- Connect the auxiliary power source (6V to 24V) to the DC2707B. The green LED (LD0-D11) lights up, indicating the presence of auxiliary 3.3V supply for powering logic.

- 3. With power off, connect two power supplies with output voltage 12V and 24V to the corresponding DC2707B turrets or banana jacks V1 (+12V), V2 (+24V) and GND.

- 4. Connect  $10\Omega$  load resistor (100W) to the DC2707B output turret or banana jack (V<sub>OUT</sub>).

- 5. Verify correct jumper setting for validation time ( $3.5\mu s$  default), HYS (R<sub>HYS</sub> default), EN (EXT + 3.3V) and SHDN (EXT + 3.3V).

- 6. Turn on power supplies and observe the transient of powering a load from V1 = 12V.

- 7. The prioritizing function is demonstrated by simply turning off the V1 supply. The output will be powered from the remaining supply V2. V1 can be adjusted up and down beyond  $\pm 20\%$  to invalidate the V1 input and observe the transient from V2 to V1 and vice versa.

Figure 1. Proper Measurement Equipment Setup

### **QUICK START PROCEDURE**

UG-1312 Rev A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions of stad ad agreed to the Agreement. Your use of the Evaluation Board with which case the Analog Devices Standard Terms and Conditions of state shall govern. Do not use the Evaluation Board shall signify your acceptance of the Agreement This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board for any other purpose. Furthermore, the license grant and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is provensly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board or termination of this Agreement, Customer any not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of reverse engineer chips on the Evaluation Board. Customer any not disclose or transfer any portion of the Evaluation Board at the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board at the tevaluation Board at the teval second at the teval access to the Evaluation Board at the Evaluation Board at the teval to any other activity that affects the

6 Downloaded from Arrow.com.

UG-1312 Rev A UG16893-0-6/18(A)