# Single-Chip USB HID Touch-Screen Bridge

#### **Programmable Touch-Screen Interface**

- Adds Windows-compatible USB HID touchscreen interface to touch-screen modules

- Supports multiple touch points and pen inputs

- Supports basic mouse functions

- Includes a programmable 8051-based controller that is pre-programmed with USB interface

- Supports most common touch-screen module interfaces: UART, SPI and I<sup>2</sup>C.

#### **UART Interface**

- Data Bits: 5, 6, 7, and 8

- Stop Bits: 1, 1.5, and 2

- Parity: Odd, Even, Mark, Space, and None

- Baud Rates: 9600 bps to 500 kbps

#### **SPI Master Interface**

- 4-wire SPI Master with Chip Select

- Configurable Clock Polarity and Phase

- Clock speeds up to 4 MHz

#### SMBus / I<sup>2</sup>C Master Interface

- Operates at configurable clock rates up to 400 kHz

- Supports configurable slave address

#### **GPIO Capability**

- CP2501 supports 16 GPIO pins

- Configurable as inputs, open-drain outputs or pushpull outputs

#### High-Speed 8051 µC Core

- 48 MHz or 24 MHz system clock

- Pipelined instruction architecture; executes 70% of instructions in 1 or 2 system clocks

#### User Memory Space

- 53 kB Flash

- 3.5 kB RAM

#### **USB Peripheral Function Controller**

- HID Touch Screen class device

- USB Specification 2.0 compliant (full-speed)

- Built-in oscillator

- Configurable USB parameters such as VID, PID, and strings

- Supports remote wakeup

#### **Programming Options**

- Obtain pre-programmed parts from the factory

- Program memory in-system

- Program over USB using bootloader

#### Supply Voltage 3.0 to 3.6 V

- Built-in voltage supply monitor

# - Built-in 3 V regulator

# Ordering Information

- CP2501-B01-GM (QFN-32, 5x5 mm)

### Temperature Range: -40 to +85 °C

# CP2501

# **Table of Contents**

| 1. System Overview                              |    |

|-------------------------------------------------|----|

| 2. Pin Definitions                              |    |

| 2.1. QFN-32 Package Specifications              |    |

| 3. Electrical Characteristics                   |    |

| 3.1. Absolute Maximum Specifications            |    |

| 3.2. Electrical Characteristics                 | 15 |

| 4. System Development                           |    |

| 4.1. System Development Process                 | 17 |

| 4.2. Firmware Development                       |    |

| 4.3. System Configurable Parameters             | 19 |

| 4.4. Programming Options                        | 20 |

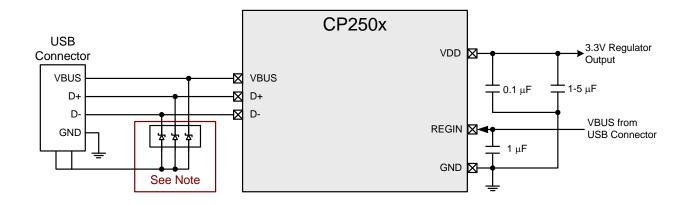

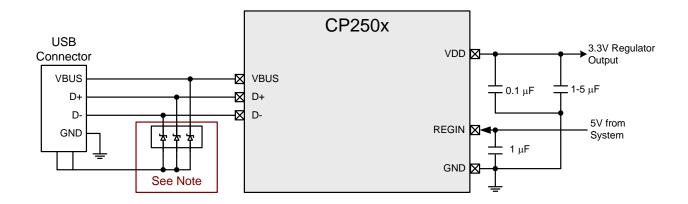

| 5. Typical Connection Diagrams                  |    |

| 5.1. USB Connections and System Power           |    |

| 5.2. Touch Screen Interface                     |    |

| 5.3. C2 Debug Interface                         |    |

| 6. CIP-51 Microcontroller                       |    |

| 6.1. Instruction Set                            | 26 |

| 6.2. CIP-51 Register Descriptions               | 31 |

| 7. Memory Organization                          |    |

| 7.1. Program Memory                             |    |

| 8. Voltage Regulator and Voltage Supply Monitor |    |

| 8.1. Voltage Regulator                          |    |

| 8.2. Power-Fail Reset / VDD Monitor             |    |

| 8.3. Power-On Reset                             |    |

| 8.4. External Reset                             |    |

| 9. USB Interface                                |    |

| 9.1. API Functionality                          | 40 |

| 9.2. Device Descriptors and Customization       | 41 |

| 9.3. Enumeration Process                        | 42 |

| 9.4. USB Bootloader                             |    |

| 10. UART Interface                              |    |

| 11. Serial Peripheral Interface (SPI)           | 46 |

| 11.1. Signal Descriptions                       |    |

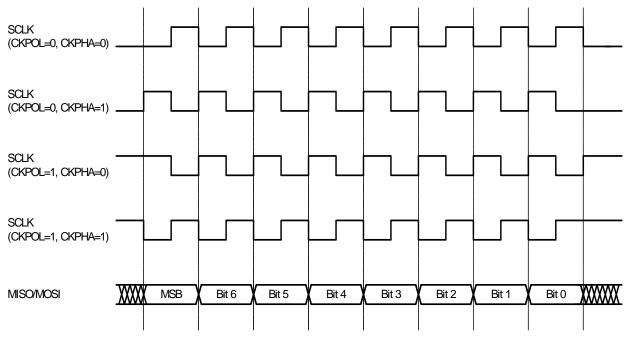

| 11.2. Serial Clock Phase and Polarity           |    |

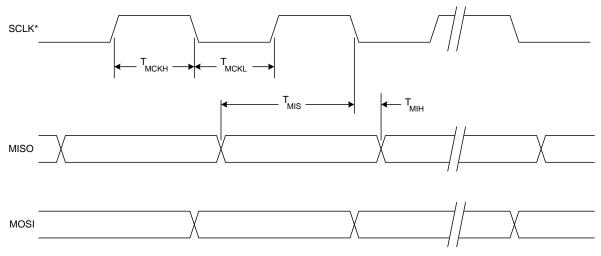

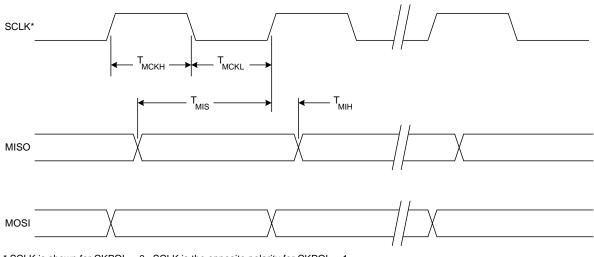

| 11.3. SPI Timing                                | 49 |

| 12. System-Management Bus (SMBus) Interface     |    |

| 12.1. SMBus Configuration                       |    |

| 12.2. SMBus Operation                           |    |

| 13. General Purpose Input / Output pins (GPIO)  |    |

| Contact Information                             | 56 |

# List of Figures

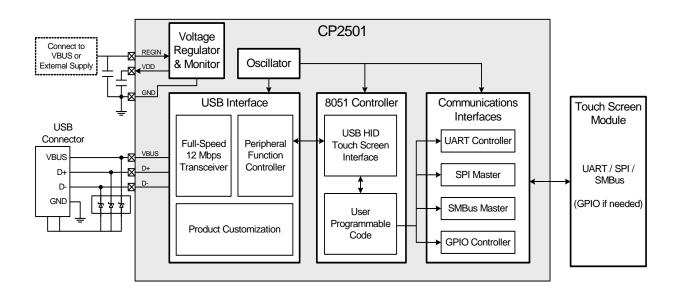

| Figure 1.1. CP2501 Block Diagram                     | 8  |

|------------------------------------------------------|----|

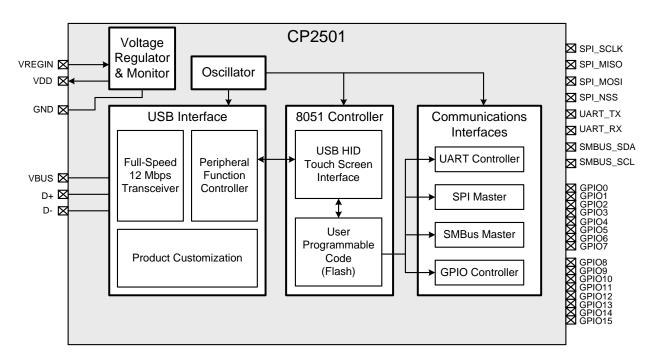

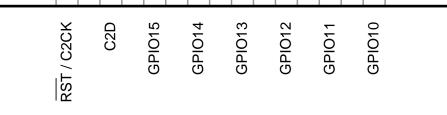

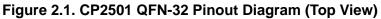

| Figure 2.1. CP2501 QFN-32 Pinout Diagram (Top View)  | 11 |

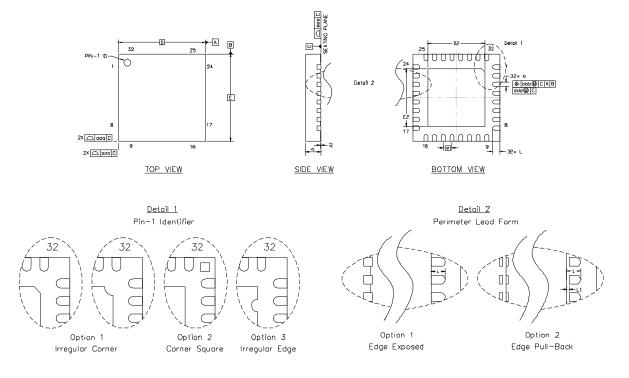

| Figure 2.2. QFN-32 Package Drawing                   | 12 |

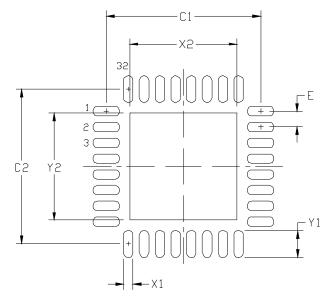

| Figure 2.3. QFN-32 Recommended PCB Land Pattern      | 13 |

| Figure 5.1. USB Bus-Powered                          | 21 |

| Figure 5.2. USB Self-Powered with Regulator Enabled  | 21 |

| Figure 5.3. USB Self-Powered with Regulator Disabled | 22 |

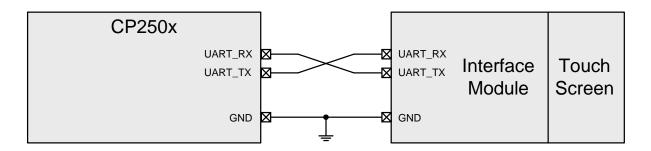

| Figure 5.4. UART Interface                           |    |

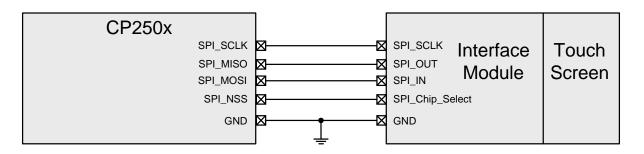

| Figure 5.5. SPI interface                            |    |

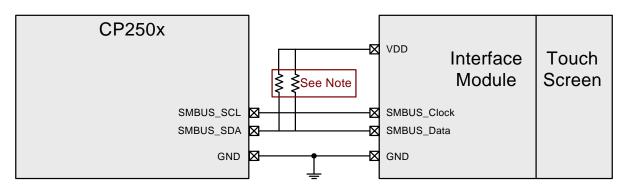

| Figure 5.6. SMBus Interface                          | 23 |

| Figure 5.7. GPIO Interface                           | 24 |

| Figure 5.8. C2 Program and Debug Interface           | 24 |

| Figure 6.1. CIP-51 Block Diagram                     |    |

| Figure 7.1. CP2501 Memory Map                        | 35 |

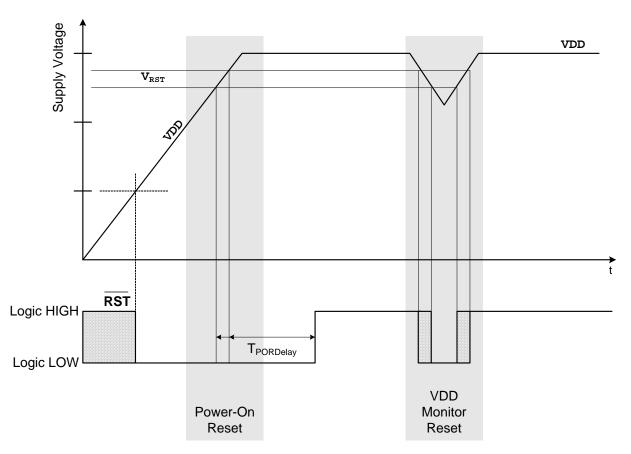

| Figure 8.1. Power-On and VDD Monitor Reset Timing    | 39 |

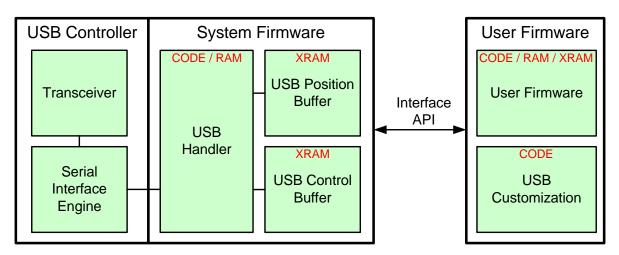

| Figure 9.1. USB Interface Block Diagram              | 40 |

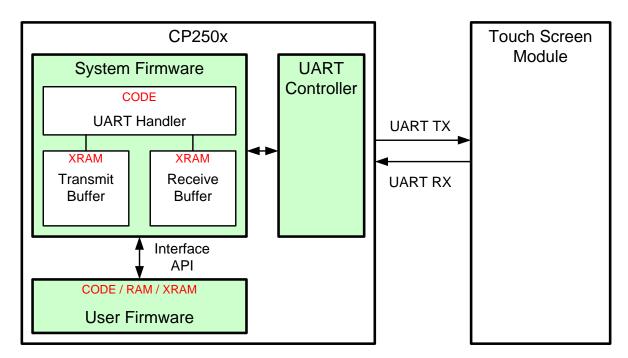

| Figure 10.1. UART System Block Diagram               | 44 |

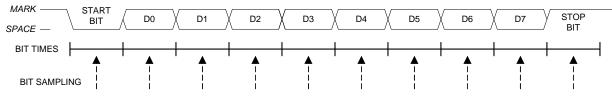

| Figure 10.2. 8-Bit UART Timing Diagram               | 45 |

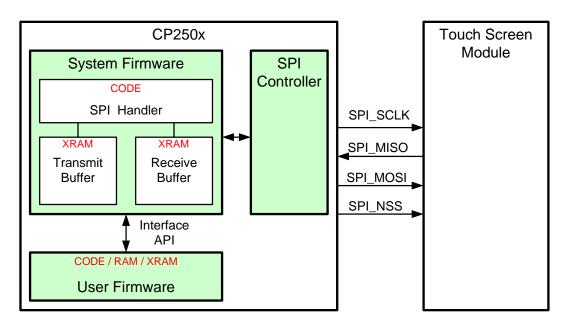

| Figure 11.1. SPI Block Diagram                       |    |

| Figure 11.2. Master Mode Data/Clock Timing           | 48 |

| Figure 11.3. SPI Master Timing (Clock Phase = 0)     | 49 |

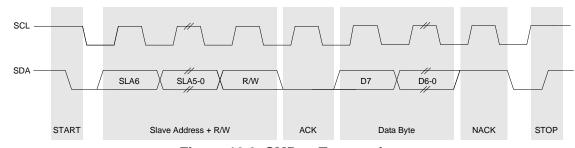

| Figure 11.4. SPI Master Timing (Clock Phase = 1)     | 49 |

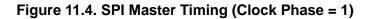

| Figure 12.1. SMBus Block Diagram                     |    |

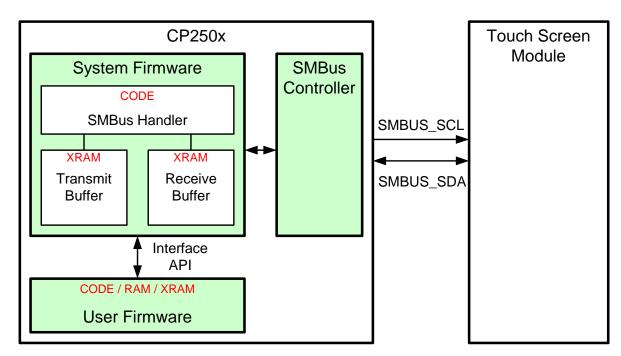

| Figure 12.2. Typical SMBus Configuration             | 52 |

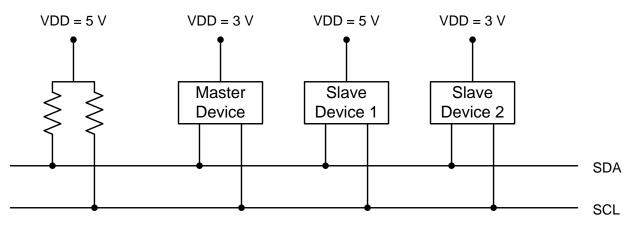

| Figure 12.3. SMBus Transaction                       | 53 |

# **List of Tables**

| Table 2.1. Pin Definitions for the CP2501                                | 9  |

|--------------------------------------------------------------------------|----|

| Table 2.2. QFN-32 Package Dimensions                                     | 12 |

| Table 2.3. QFN-32 PCB Land Pattern Dimensions                            | 13 |

| Table 3.1. Absolute Maximum Ratings                                      | 14 |

| Table 3.2. Global Electrical Characteristics                             | 15 |

| Table 3.3. GPIO and VBUS DC Electrical Characteristics                   | 15 |

| Table 3.4. Reset Electrical Characteristics                              | 16 |

| Table 3.5. Internal Voltage Regulator Electrical Characteristics         | 16 |

| Table 3.6. Internal High-Frequency Oscillator Electrical Characteristics |    |

| Table 6.1. CIP-51 Instruction Set Summary                                | 27 |

| Table 7.1. CP2501Memory Allocation                                       | 35 |

| Table 9.1. Configurable USB Descriptors                                  | 41 |

| Table 9.2. Default USB Bootloader Descriptors                            | 41 |

| Table 10.1. Data Formats and Baud Rates                                  | 44 |

| Table 11.1. PI Clock Speeds and Configurations                           |    |

| Table 11.2. Data centered on first or second edge of SCK period          | 46 |

| Table 11.3. SPI Master Timing Parameters                                 | 50 |

| Table 12.1. SMBus Clock Speed                                            | 51 |

# List of Registers

| SFR Definition 6.1. DPL: Data Pointer Low Byte  | 31 |

|-------------------------------------------------|----|

| SFR Definition 6.2. DPH: Data Pointer High Byte | 31 |

| SFR Definition 6.3. SP: Stack Pointer           | 32 |

| SFR Definition 6.4. ACC: Accumulator            | 32 |

| SFR Definition 6.5. B: B Register               | 33 |

| SFR Definition 6.6. PSW: Program Status Word    | 34 |

# 1. System Overview

The CP2501 is a programmable, 8051-based bridge device that adds a HID-compliant USB touch-screen interface to multi-touch devices such as digitizers, touch screens and pens. The CP2501 devices are preprogrammed with an easy-to-use firmware API, called the System Firmware, to perform USB communication and interface to touch modules using UART, SPI, or SMBus.

The development tools for the CP2501 include the CP2501 Configuration Wizard, which is a Windows tool that enables quick system development by creating a firmware project, including USB descriptors that match the capabilities of the multi-touch device. The tool also customizes the USB parameters such as the VID, PID and user strings.

The user programmable memory enables a custom interface to a wide range of multi-touch modules. Typical multi-touch modules use UART, SPI, or SMBus interfaces. The user firmware calls functions in the System Firmware to retrieve data from touch module and then sends the touch information to the USB host PC. The functions provided by the System Firmware make firmware development easy and remove the need to write low-level USB or interface firmware.

Highlighted features of the CP2501 are listed below.

- Support for up to 5 multi-touch points and 1 pen device

- High-speed pipelined 8051-compatible microcontroller core (up to 48 MIPS)

- In-system, full-speed, non-intrusive debug interface (on-chip)

- Precision calibrated 48 MHz or 24 MHz internal oscillator

- 64 kB of on-chip Flash memory

- 4 kB bytes of on-chip RAM

- SMBus/I<sup>2</sup>C, UART, and SPI serial interfaces

- On-chip VDD supply monitor

- 16 general purpose I/O

With on-chip power-on reset, V<sub>DD</sub> monitor, and clock oscillator, the CP2501 devices are truly stand-alone, system-on-a-chip solutions. The Flash memory devices are reprogrammable in-circuit, providing non-vola-tile data storage. The Flash memory devices also allow field upgrades of the 8051 firmware.

The CP2501 devices include Silicon Laboratories' 2-Wire C2 Debug and Programming interface, which allows for non-intrusive (uses no on-chip resources), full speed, in-circuit debugging using the production device installed in the final application. This debug logic supports inspection of memory, viewing and modification of special function registers, setting breakpoints, single stepping, and run and halt commands. All features are fully functional while debugging using C2.

Each device is specified for 3.0 to 3.6 V operation over the industrial temperature range (–45 to +85 °C). The Port I/O and RST pins are tolerant of input signals up to 5 V. Figure 1.1 is the block diagram for the CP2501.

Figure 1.1. CP2501 Block Diagram

# 2. Pin Definitions

| Name     Pin     Type     Description |              |                 |                                                                                                                                                             |  |  |  |

|---------------------------------------|--------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                       |              | Туре            | · · · · · · · · · · · · · · · · · · ·                                                                                                                       |  |  |  |

| GND                                   | 3            | Power           | Ground. This ground connection is required. The center pad may optionally be connected to ground as well.                                                   |  |  |  |

| V <sub>DD</sub>                       | 6            | Power           | Power Supply Voltage. The output of the on-chip voltage regulator is available on this pin.                                                                 |  |  |  |

| RST<br>/                              | 9            | Digital I/O     | Device Reset. Open-drain output of internal POR or V <sub>DD</sub> mon-<br>itor. An external source can initiate a system reset by driving<br>this pin low. |  |  |  |

| C2CK                                  |              | Digital I/O     | Clock signal for the C2 Debug Interface.                                                                                                                    |  |  |  |

| C2D                                   | 10           | D I/O           | Bi-directional data signal for the C2 Debug Interface.                                                                                                      |  |  |  |

| VREGIN                                | 7            | Power           | 5 V Regulator Input. This pin is the input to the on-chip voltage regulator.                                                                                |  |  |  |

| VBUS                                  | 8            | Power           | VBUS Sense Input. This pin should be connected to the VBUS signal of a USB network. A 5 V signal on this pin indicates a USB network connection.            |  |  |  |

| D+                                    | 4            | Digital I/O     | USB D+.                                                                                                                                                     |  |  |  |

| D-                                    | 5            | Digital I/O     | USB D                                                                                                                                                       |  |  |  |

| SPI_SCLK                              | 2*           | Digital I/O     | SPI Clock.                                                                                                                                                  |  |  |  |

| SPI_MISO                              | 1*           | Digital I/O     | SPI Master In / Slave Out.                                                                                                                                  |  |  |  |

| SPI_MOSI                              | 32*          | Digital I/O     | SPI Master Out / Slave In.                                                                                                                                  |  |  |  |

| SPI_NSS                               | 31*          | Digital I/O     | SPI Slave Select.                                                                                                                                           |  |  |  |

| UART_TX                               | 30*          | Digital I/O     | UART Transmit.                                                                                                                                              |  |  |  |

| UART_RX                               | 29*          | Digital I/O     | UART Receive.                                                                                                                                               |  |  |  |

| SMBUS_SDA                             | 28*          | Digital I/O     | SMBus Data.                                                                                                                                                 |  |  |  |

| SMBUS_SCL                             | 27*          | Digital I/O     | SMBus Clock.                                                                                                                                                |  |  |  |

| GPIO0                                 | 26*          | Digital I/O     | General Purpose I/O 0.                                                                                                                                      |  |  |  |

| GPIO1                                 | 25*          | Digital I/O     | General Purpose I/O 1.                                                                                                                                      |  |  |  |

| GPIO2                                 | 24*          | Digital I/O     | General Purpose I/O 2.                                                                                                                                      |  |  |  |

| GPIO3                                 | 23*          | Digital I/O     | General Purpose I/O 3.                                                                                                                                      |  |  |  |

| GPIO4                                 | 22*          | Digital I/O     | General Purpose I/O 4.                                                                                                                                      |  |  |  |

| Note: Pins can b                      | e left uncor | nnected when no | ot used.                                                                                                                                                    |  |  |  |

Table 2.1. Pin Definitions for the CP2501

| Pin       | Туре                                                               | Description                                                                                                                                  |

|-----------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 21*       | Digital I/O                                                        | General Purpose I/O 5.                                                                                                                       |

| 20*       | Digital I/O                                                        | General Purpose I/O 6.                                                                                                                       |

| 19*       | Digital I/O                                                        | General Purpose I/O 7.                                                                                                                       |

| 18*       | Digital I/O                                                        | General Purpose I/O 8.                                                                                                                       |

| 17*       | Digital I/O                                                        | General Purpose I/O 9.                                                                                                                       |

| 16*       | Digital I/O                                                        | General Purpose I/O 10.                                                                                                                      |

| 15*       | Digital I/O                                                        | General Purpose I/O 11.                                                                                                                      |

| 14*       | Digital I/O                                                        | General Purpose I/O 12.                                                                                                                      |

| 13*       | Digital I/O                                                        | General Purpose I/O 13.                                                                                                                      |

| 12*       | Digital I/O                                                        | General Purpose I/O 14.                                                                                                                      |

| 11*       | Digital I/O                                                        | General Purpose I/O 15.                                                                                                                      |

| · · · · · | 21*<br>20*<br>19*<br>18*<br>17*<br>16*<br>15*<br>14*<br>13*<br>12* | 21*Digital I/O20*Digital I/O19*Digital I/O18*Digital I/O17*Digital I/O16*Digital I/O15*Digital I/O14*Digital I/O13*Digital I/O12*Digital I/O |

Table 2.1. Pin Definitions for the CP2501 (Continued)

#### SMBUS\_SDA SMBUS\_SCL UART\_TX UART\_RX SPI\_MOSI SPI\_NSS GP100 GPI01 32 30 29 28 26 25 31 27 SPI\_MISO GPIO2 24 1 SPI\_SCLK GPIO3 2 23 GND 22 GPIO4 3 GPIO5 D+ 4 21 **CP2501-GM Top View** D-5 20 GPIO6 VDD GPIO7 6 19 VREGIN 7 GPIO8 18 GND (optional) VBUS 8 17 GPIO9 16 10 <u>\_</u> 2 3 4 51 တ

# 2.1. QFN-32 Package Specifications

Figure 2.2. QFN-32 Package Drawing

| Dimension | Min       | Тур       | Max  |  | Dimension | Min  | Тур  | Max  |  |      |  |  |

|-----------|-----------|-----------|------|--|-----------|------|------|------|--|------|--|--|

| А         | 0.80      | 0.90      | 1.00 |  | E2        | 3.20 | 3.30 | 3.40 |  |      |  |  |

| A1        | 0.00      | 0.02      | 0.05 |  | L         | 0.30 | 0.40 | 0.50 |  |      |  |  |

| b         | 0.18      | 0.25      | 0.30 |  | L1        | 0.00 |      | 0.15 |  |      |  |  |

| D         | 5.00 BSC. |           |      |  | aaa       |      | 0.15 | •    |  |      |  |  |

| D2        | 3.20      | 3.30      | 3.40 |  | bbb       | 0.10 |      |      |  | 0.10 |  |  |

| е         |           | 0.50 BSC. |      |  | ddd 0.05  |      |      |      |  |      |  |  |

| E         |           | 5.00 BSC. |      |  | eee       | 0.08 |      |      |  |      |  |  |

| Nataa     |           |           |      |  |           |      |      |      |  |      |  |  |

### Table 2.2. QFN-32 Package Dimensions

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- **3.** This drawing conforms to the JEDEC Solid State Outline MO-220, variation VHHD except for custom features D2, E2, and L which are toleranced per supplier designation.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

Figure 2.3. QFN-32 Recommended PCB Land Pattern

| Table 2.3. QF | N-32 PCB Land | Pattern Dimensions |

|---------------|---------------|--------------------|

|---------------|---------------|--------------------|

| Dimension | Min      | Max  |  |  |

|-----------|----------|------|--|--|

| C1        | 4.80     | 4.90 |  |  |

| C2        | 4.80     | 4.90 |  |  |

| E         | 0.50 BSC |      |  |  |

| X1        | 0.20     | 0.30 |  |  |

| Dimension | Min  | Max  |

|-----------|------|------|

| X2        | 3.20 | 3.40 |

| Y1        | 0.75 | 0.85 |

| Ý2        | 3.20 | 3.40 |

#### Notes:

General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This Land Pattern Design is based on the IPC-7351 guidelines.

Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be  $60 \ \mu m$  minimum, all the way around the pad.

Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- 6. The ratio of stencil aperture to land pad size should be 1:1 for all perimeter pins.

- **7.** A 3x3 array of 1.0 mm openings on a 1.2 mm pitch should be used for the center pad to assure the proper paste volume.

Card Assembly

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

# 3. Electrical Characteristics

# 3.1. Absolute Maximum Specifications

### Table 3.1. Absolute Maximum Ratings

| Parameter                                                                                                           | Conditions | Min  | Тур | Max | Units |  |  |

|---------------------------------------------------------------------------------------------------------------------|------------|------|-----|-----|-------|--|--|

| Ambient temperature under bias                                                                                      |            | -55  |     | 125 | °C    |  |  |

| Storage Temperature                                                                                                 |            | -65  | _   | 150 | °C    |  |  |

| Voltage on $\overline{\text{RST}}$ or any Port I/O Pin with respect to GND                                          |            | -0.3 | _   | 5.8 | V     |  |  |

| Voltage on V <sub>DD</sub> with respect to GND                                                                      |            | -0.3 |     | 4.2 | V     |  |  |

| Maximum Total current through V <sub>DD</sub><br>and GND                                                            |            |      | _   | 500 | mA    |  |  |

| Maximum output current sunk by $\overline{RST}$ or any Port pin                                                     |            | _    | _   | 100 | mA    |  |  |

| <b>Note:</b> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. |            |      |     |     |       |  |  |

This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 3.2. Electrical Characteristics

#### **Table 3.2. Global Electrical Characteristics** –40 to +85 °C

| Parameter                                    | Conditions              | Min | Тур | Max | Units |

|----------------------------------------------|-------------------------|-----|-----|-----|-------|

| Digital Supply Voltage (V <sub>DD</sub> )    |                         | 3.0 | 3.3 | 3.6 | V     |

| Supply Current <sup>1</sup>                  | Normal Operation—48 MHz | —   | 35  | 37  | mA    |

|                                              | Normal Operation—24 MHz | —   | 23  | 25  | mA    |

|                                              | Suspended               | —   | 43  | 54  | μA    |

| Supply Current - USB Pull-up <sup>2</sup>    |                         |     | 200 | 228 |       |

| Digital Supply RAM Data Retention<br>Voltage |                         | —   | 1.5 | —   | V     |

| Specified Operating Temperature<br>Range     |                         | -40 |     | +85 | °C    |

|                                              |                         |     |     |     |       |

Notes:

- 1. If the device is connected to the USB bus, the USB Pull-up Current should be added to the Supply Current to calculate the total required current.

- 2. The USB Pull-up supply current values are calculated based on the USB specifications.

### Table 3.3. GPIO and VBUS DC Electrical Characteristics

$V_{DD}$  = 3.0 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameters           | Conditions                                                      | Min                   | Тур                   | Мах | Units |

|----------------------|-----------------------------------------------------------------|-----------------------|-----------------------|-----|-------|

| Output High Voltage  | Output High Voltage $I_{OH} = -10 \ \mu A$ , Port I/O push-pull |                       |                       |     | V     |

|                      | I <sub>OH</sub> = –3 mA, Port I/O push-pull                     | V <sub>DD</sub> - 0.7 | —                     | —   | V     |

|                      | I <sub>OH</sub> = –10 mA, Port I/O push-pull                    | —                     | V <sub>DD</sub> - 0.8 | —   | V     |

| Output Low Voltage   | I <sub>OL</sub> = 10 μA                                         | —                     | _                     | 0.1 | V     |

|                      | l <sub>OL</sub> = 8.5 mA                                        | —                     | —                     | 0.6 | V     |

|                      | I <sub>OL</sub> = 25 mA                                         | —                     | 1.0                   | —   | V     |

| Input High Voltage   |                                                                 | 2.0                   |                       |     | V     |

| Input Low Voltage    |                                                                 | —                     | _                     | 0.8 | V     |

| Input Leakage        | Weak Pullup Off                                                 | -1                    | _                     | 1   | μA    |

| Current              | Weak Pullup On, V <sub>IN</sub> = 0 V                           | —                     | 25                    | 50  | μA    |

| VBUS Detection Input |                                                                 | 3.0                   | _                     |     | V     |

| High Voltage         |                                                                 |                       |                       |     |       |

| VBUS Detection Input |                                                                 | _                     | _                     | 1.0 | V     |

| Low Voltage          |                                                                 |                       |                       |     |       |

#### **Table 3.4. Reset Electrical Characteristics**

$V_{DD}$  = 1.8 to 3.6 V, –40 to +85 °C unless otherwise specified.

| Parameter                                       | Conditions                                                    | Min                   | Тур  | Max                   | Units |

|-------------------------------------------------|---------------------------------------------------------------|-----------------------|------|-----------------------|-------|

| RST Output Low Voltage                          | I <sub>OL</sub> = 8.5 mA,<br>V <sub>DD</sub> = 1.8 V to 3.6 V | _                     | _    | 0.6                   | V     |

| RST Input High Voltage                          |                                                               | 0.7 x V <sub>DD</sub> | —    | —                     | V     |

| RST Input Low Voltage                           |                                                               | —                     | —    | 0.3 x V <sub>DD</sub> | V     |

| $V_{DD}$ Monitor Threshold ( $V_{RST}$ )        |                                                               | 2.40                  | 2.55 | 2.70                  | V     |

| Minimum RST Low Time to Generate a System Reset |                                                               | 15                    |      |                       | μs    |

#### **Table 3.5. Internal Voltage Regulator Electrical Characteristics**

| Parameter                                       | Conditions                            | Min          | Тур      | Max         | Units |

|-------------------------------------------------|---------------------------------------|--------------|----------|-------------|-------|

| Input Voltage Range <sup>1</sup>                |                                       | 3.0          | —        | 5.25        | V     |

| Output Voltage Range                            |                                       | 3.0          | 3.3      | 3.6         | V     |

| Output Current <sup>2</sup>                     |                                       | _            |          | 100         | mA    |

| Dropout Voltage (V <sub>DO</sub> ) <sup>3</sup> |                                       | —            | 1        | —           | mV/mA |

| 1. Input range specified for regu               | lation. When an external regulator is | used, VREGIN | should b | e tied to V | DD.   |

ulation. When an external regulator is used, VREGIN should be tied to VDD.

2. Output current is total regulator output, including any current required by the CP2501.

3. The minimum input voltage is 3.0 V or VDD +  $V_{DO}$  (max load), whichever is greater.

## Table 3.6. Internal High-Frequency Oscillator Electrical Characteristics

V<sub>DD</sub> = 3.0 to 3.6 V; -40 to +85 °C unless otherwise specified.

| Parameter            | Conditions           | Min       | Тур | Мах       | Units |

|----------------------|----------------------|-----------|-----|-----------|-------|

| Oscillator Frequency | 48 MHz configuration | 48 – 0.5% | 48  | 48 + 0.5% | MHz   |

| Oscillator Frequency | 24 MHz configuration | 24 – 0.5% | 24  | 24 + 0.5% | MHz   |

# 4. System Development

The CP2501 family of products are programmable, 8051-based bridge devices that add a Windows-compatible, HID USB touch-screen interface to multi-touch screen devices such as digitizers, touch screens and pens. The CP2501 devices are pre-programmed with an easy-to-use firmware API, called the System Firmware, to perform USB communication and interface to touch modules using UART, SPI, or SMBus.

All multi-touch devices have unique capabilities and interface requirements. Custom user firmware is required to use the functions provided by the System Firmware to initialize the CP2501 and the touch screen. The user firmware also needs to process the data received from the touch screen before sending it to the USB host. Example firmware is available for each communications interface to show how use the API.

The following sections describe the user firmware development process, the development tools, the various configuration options for the CP2501 devices, and how to program the devices once firmware development is complete.

### 4.1. System Development Process

#### 4.1.1. Relevant Documents and Development Tools

The following documents and development tools are necessary for developing user firmware for CP2501 devices:

- Silicon Labs Integrated Development Environment (IDE)

- 8051 C Compiler

- CP2501 Configuration Wizard

- Application Note 464: CP2501 Programmer's Guide and API Specification.

The document and tools are available with the CP2501 development kit and also available online at www.silabs.com.

#### 4.1.2. Development Procedure Overview

The development process for the CP2501 includes these steps:

- 1. Determine the touch capabilities and interface specifications for the touch screen device.

- 2. Use the CP2501 Configuration Wizard to generate a firmware project based on those capabilities.

- 3. Develop user firmware on top of the base project using the Silicon Labs IDE and an 8051-toolset.

- 4. Test the project using the Silicon Labs CP2501 development kit hardware. The development kit hardware can interface directly to the touch screen module.

#### 4.1.3. Development Tool Overview

The source code generated for the base firmware project by the CP2501 Configuration Wizard is written in C. An 8051 C compiler is required to build this project. The base firmware is written to be compatible with the following 8051 compilers:

- Raisonance

- Keil

- SDCC

The Silicon Labs IDE and CP2501 Configuration Wizard require Microsoft Windows XP or newer operating system.

### 4.2. Firmware Development

The user firmware performs three primary tasks:

- 1. CP2501 device configuration and initialization, including USB initialization.

- 2. Initialization of the touch screen, using one of the three communications interfaces.

- 3. Touch screen data retrieval, processing, and communication with the USB host.

The first component, CP2501 device configuration and initialization, is primarily handled by the firmware generated by the CP2501 Configuration Wizard. The system configurable parameters are described in Section 4.3.

The second and third components of the user firmware are customized for each system. The follow sections describe important aspects of the user firmware.

#### 4.2.1. Interface API

All functions performed by the user firmware must use the Interface API, except for the functions that manage data returned from the touch screen. The CP2501 API Specification provides the full details regarding Interface API.

The capabilities of the communications interfaces and the GPIO are described in their respective sections:

Section "10. UART Interface" on page 44

Section "11. Serial Peripheral Interface (SPI)" on page 46

Section "12. System-Management Bus (SMBus) Interface" on page 51.

Section "13. General Purpose Input / Output pins (GPIO)" on page 54.

Example code that uses each of the three communications interfaces is available as part of the development kit. The example code is not targeted towards a specific touch screen interface, but it is intended to show how a typical system would use the communications interface.

#### 4.2.2. Memory Organization

The pre-programmed System Firmware block reserves small portions of the various memory segments (Flash, RAM, and XRAM) for operation. The remaining parts of the memory segments are available for user firmware. The memory organization is detailed in Section "7. Memory Organization" on page 35.

The firmware project generated by the Configuration Wizard includes compiler and linker command line options to prevent user firmware from using the System Firmware's reserved memory spaces. If these settings are overridden, user firmware must take care not to use any of the reserved memory spaces.

#### 4.2.3. USB Data Format

The user firmware sends the touch screen data to the PC using the Interface API. The System Firmware directly copies the data from the user memory space to the USB FIFO. For the USB host to properly interpret the touch screen data, the data must be sent to host PC in a format that matches the specification defined by the USB descriptors. The Configuration Wizard generates a header file which includes a C struct. The C struct defines the order and the size of the elements for each of the attributes (usage) of each touch point. A separate struct is generated for touch point, pen, and mouse support.

#### 4.2.4. Key Signature

When a CP2501 device is powered-on, code execution is initially handled by the System Firmware. The System Firmware transfers control to the user firmware if it determines that the key signature is present. Without a key signature, device control remains with the System Firmware. The base firmware project generated by the Configuration Wizard includes the key signature. The key signature is not intended as a data integrity signature, such as checksum or CRC, but is only used to indicate that user firmware has been programmed. The key signature should always be programmed after the user firmware.

### 4.3. System Configurable Parameters

The CP2501 devices include various configurable options. The configuration options for the USB, UART, SPI, SMBus and GPIO are detailed in their respective sections. All other options are detailed in the following sections.

#### 4.3.1. System Clock

The 8051 system clock is configurable using the Interface API to 48 MHz or 24 MHz. The default system clock is 24 MHz. The faster system clock allows for quicker firmware execution, but requires a higher supply current. The faster clock is useful if the touch screen returns data at a high rate or if the data requires a large amount of processing before it is sent to the host PC.

The slower system clock speed executes the firmware at half the speed, but requires less supply current. If the touch screen data can be processed using the slower clock speed, the slower clock speed is recommended. The supply current requirements for the two clock speeds are available in Table 3.2, "Global Electrical Characteristics," on page 15.

The system clock configuration should not be changed once the device has enumerated.

#### 4.3.2. Voltage Regulator

The CP2501 devices include an on-chip 5 V to 3 V regulator. The regulator is turned on by default. If the CP2501 is powered using the 5 V source from the USB host (VBUS), the voltage regulator should use the default setting. If a 3 V source is available in the system to power the CP2501, the regulator should be turned off using the Interface API in order to reduce supply current. The supply current requirements for the voltage regulator are available in Table 3.5, "Internal Voltage Regulator Electrical Characteristics," on page 16. The regulator is fully described in Section "8. Voltage Regulator and Voltage Supply Monitor" on page 38.

## 4.4. Programming Options

There are multiple options for programming CP2501 devices once user firmware development is complete.

- Silicon Labs factory programming

- Programming in-system over the C2 interface

- Programming in-system using the USB bootloader

#### Silicon Labs factory programming

Once firmware development is complete, the developer can submit the user firmware hex file to Silicon Labs. Silicon Labs will create a custom-part number which is available for order.

#### Programming in-system over the C2 Interface

If the final system includes external connections for the debug pins, the device is programmable in-system using the USB debug adapter that is provided with the development kit.

The final system can include the standard 10-pin debug header that is included on the development kits to directly interface with the USB debug adapter, or it can include a reduced size connection with only the debug pins and GND. A custom connection can be created between the USB debug adapter and the target system.

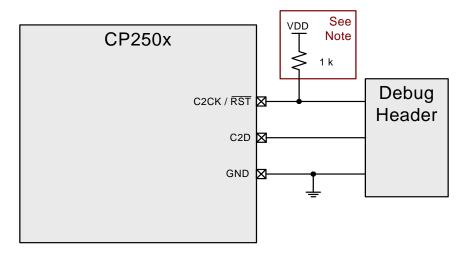

To program CP2501 devices in system, the C2CK/RST, C2D, and GND pins must be made available.

#### Programming in-system using the USB bootloader

The CP2501 user firmware is bootloadable over the USB interface using the Silicon Labs CP2501 Bootloader. The Silicon Labs CP2501 Bootloader is a Windows application that takes the hex file from the user generated firmware as an input.

# 5. Typical Connection Diagrams

The typical connection diagrams shown in this section partition the CP2501 device schematic into three components: USB & Power, touch screen interface, and debug connection.

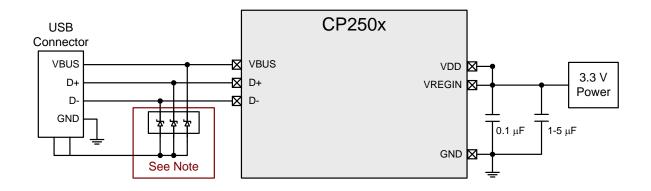

### 5.1. USB Connections and System Power

Figure 5.1. USB Bus-Powered

### Figure 5.2. USB Self-Powered with Regulator Enabled

**Note:** Avalanche transient voltage suppression diodes compatible with full-speed USB should be added at the connector for ESD protection. Use Littelfuse p/n SP0503BAHT or equivalent.

Figure 5.3. USB Self-Powered with Regulator Disabled

**Note:** Avalanche transient voltage suppression diodes compatible with full-speed USB should be added at the connector for ESD protection. Use Littelfuse p/n SP0503BAHT or equivalent.

# 5.2. Touch Screen Interface

The CP2501 devices support the use of only one of the three touch-screen interfaces at any time, and systems should only connect one of these interfaces.

**Note:** External pull-up resistors are required if they are not already present on the bus. The pull-up resistors should be chosen according to the I<sup>2</sup>C specification.

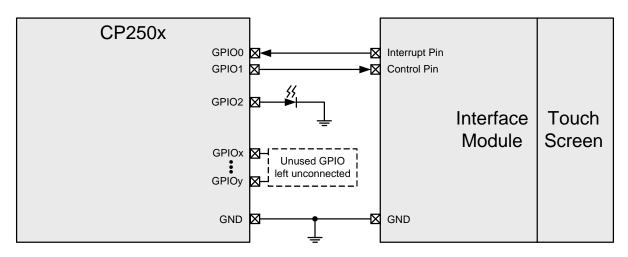

The GPIO pins are optional connections, that can be interfaced to the touch screen module or to other circuitry. Unused GPIO pins can be left unconnected. Figure 5.7 shows some example connections for the GPIO pins.

Figure 5.7. GPIO Interface

# 5.3. C2 Debug Interface

This debug connection is only necessary if the devices are programmed in-system. If the devices are programmed at the factory or elsewhere, external connections for a debug header are not necessary.

# Figure 5.8. C2 Program and Debug Interface

**Note:** An external pull-up is not required, but is recommended for noise immunity. This pull-up is recommended even if a debug connection is not required.

# 6. CIP-51 Microcontroller

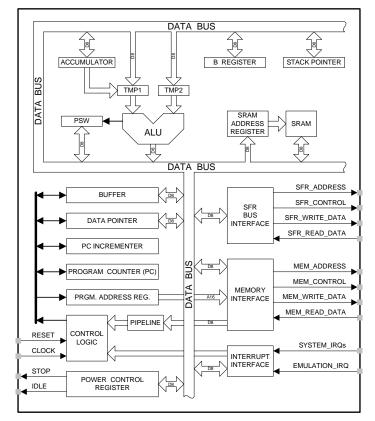

The system controller core is the CIP-51 microcontroller. The CIP-51 is fully compatible with the MCS-51<sup>™</sup> instruction set; standard 803x/805x assemblers and compilers can be used to develop software. The CIP-51 includes on-chip debug hardware, and interfaces directly with the analog and digital subsystems providing a complete data acquisition or control-system solution in a single integrated circuit.

The CIP-51 core implements the standard 8051 organization and peripherals as well as additional custom peripherals and functions to extend its capability (see Figure 6.1 for a block diagram). The CIP-51 includes the following features:

- Fully Compatible with MCS-51 Instruction Set

- 48 MIPS Peak Throughput with 48 MHz Clock

- Reset Input

- Power Management Modes

- On-chip Debug Logic

- Program and Data Memory Security

#### Performance

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute, and usually have a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with no instructions taking more than eight system clock cycles.

Figure 6.1. CIP-51 Block Diagram

CP2501

With the CIP-51's maximum system clock at 48 MHz, it has a peak throughput of 48 MIPS. The CIP-51 has a total of 109 instructions. The table below shows the total number of instructions that require each execution time.

| Clocks to Execute      | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

|------------------------|----|----|-----|----|-----|---|-----|---|---|

| Number of Instructions | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

### 6.1. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set. Standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 6.1.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 6.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

| Mnemonic              | Description                              | Bytes | Clock<br>Cycles |

|-----------------------|------------------------------------------|-------|-----------------|

| Arithmetic Operations | S                                        | I     |                 |

| ADD A, Rn             | Add register to A                        | 1     | 1               |

| ADD A, direct         | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri            | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data          | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn            | Add register to A with carry             | 1     | 1               |

| ADDC A, direct        | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri           | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data         | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn            | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct        | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri           | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data         | Subtract immediate from A with borrow    | 2     | 2               |

| INC A                 | Increment A                              | 1     | 1               |

| INC Rn                | Increment register                       | 1     | 1               |

| INC direct            | Increment direct byte                    | 2     | 2               |

| INC @Ri               | Increment indirect RAM                   | 1     | 2               |

| DEC A                 | Decrement A                              | 1     | 1               |

| DEC Rn                | Decrement register                       | 1     | 1               |

| DEC direct            | Decrement direct byte                    | 2     | 2               |

| DEC @Ri               | Decrement indirect RAM                   | 1     | 2               |

| INC DPTR              | Increment Data Pointer                   | 1     | 1               |

| MUL AB                | Multiply A and B                         | 1     | 4               |

| DIV AB                | Divide A by B                            | 1     | 8               |

| DA A                  | Decimal adjust A                         | 1     | 1               |

| Logical Operations    | ,                                        |       |                 |

| ANL A, Rn             | AND Register to A                        | 1     | 1               |

| ANL A, direct         | AND direct byte to A                     | 2     | 2               |

| ANL A, @Ri            | AND indirect RAM to A                    | 1     | 2               |

| ANL A, #data          | AND immediate to A                       | 2     | 2               |

| ANL direct, A         | AND A to direct byte                     | 2     | 2               |

| ANL direct, #data     | AND immediate to direct byte             | 3     | 3               |

| ORL A, Rn             | OR Register to A                         | 1     | 1               |

| ORL A, direct         | OR direct byte to A                      | 2     | 2               |

| ORL A, @Ri            | OR indirect RAM to A                     | 1     | 2               |

| ORL A, #data          | OR immediate to A                        | 2     | 2               |

| ORL direct, A         | OR A to direct byte                      | 2     | 2               |

| ORL direct, #data     | OR immediate to direct byte              | 3     | 3               |

| XRL A, Rn             | Exclusive-OR Register to A               | 1     | 1               |

| XRL A, direct         | Exclusive-OR direct byte to A            | 2     | 2               |

| XRL A, @Ri            | Exclusive-OR indirect RAM to A           | 1     | 2               |

| XRL A, #data          | Exclusive-OR immediate to A              | 2     | 2               |

| XRL direct, A         | Exclusive-OR A to direct byte            | 2     | 2               |

| Mnemonic                    | Description                                | Bytes | Clock<br>Cycles |

|-----------------------------|--------------------------------------------|-------|-----------------|

| XRL direct, #data           | Exclusive-OR immediate to direct byte      | 3     | 3               |

| CLR A                       | Clear A                                    | 1     | 1               |

| CPL A                       | Complement A                               | 1     | 2               |

| RL A                        | Rotate A left                              | 1     | 1               |

| RLC A                       | Rotate A left through Carry                | 1     | 1               |

| RR A                        | Rotate A right                             | 1     | 1               |

| RRC A                       | Rotate A right through Carry               | 1     | 1               |

| SWAP A                      | Swap nibbles of A                          | 1     | 1               |

| Data Transfer               |                                            |       |                 |

| MOV A, Rn                   | Move Register to A                         | 1     | 1               |

| MOV A, direct               | Move direct byte to A                      | 2     | 2               |

| MOV A, @Ri                  | Move indirect RAM to A                     | 1     | 2               |

| MOV A, #data                | Move immediate to A                        | 2     | 2               |

| MOV Rn, A                   | Move A to Register                         | 1     | 1               |

| MOV Rn, direct              | Move direct byte to Register               | 2     | 2               |

| MOV Rn, #data               | Move immediate to Register                 | 2     | 2               |

| MOV direct, A               | Move A to direct byte                      | 2     | 2               |

| MOV direct, Rn              | Move Register to direct byte               | 2     | 2               |

| MOV direct, direct          | Move direct byte to direct byte            | 3     | 3               |

| MOV direct, @Ri             | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct, #data           | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri, A                  | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri, direct             | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri, #data              | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR, #data16           | Load DPTR with 16-bit constant             | 3     | 3               |

| MOVC A, @A+DPTR             | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A, @A+PC               | Move code byte relative PC to A            | 1     | 3               |

| MOVX A, @Ri                 | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri, A                 | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A, @DPTR               | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR, A               | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct                 | Push direct byte onto stack                | 2     | 2               |

| POP direct                  | Pop direct byte from stack                 | 2     | 2               |

| XCH A, Rn                   | Exchange Register with A                   | 1     | 1               |

| XCH A, direct               | Exchange direct byte with A                | 2     | 2               |

| XCH A, @Ri                  | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A, @Ri                 | Exchange low nibble of indirect RAM with A | 1     | 2               |

| <b>Boolean Manipulation</b> |                                            |       |                 |

| CLR C                       | Clear Carry                                | 1     | 1               |

| CLR bit                     | Clear direct bit                           | 2     | 2               |

| SETB C                      | Set Carry                                  | 1     | 1               |

| SETB bit                    | Set direct bit                             | 2     | 2               |

| CPL C                       | Complement Carry                           | 1     | 1               |

| CPL bit                     | Complement direct bit                      | 2     | 2               |

Table 6.1. CIP-51 Instruction Set Summary (Continued)

| Inemonic Description |                                                     | Bytes | Clock<br>Cycles |

|----------------------|-----------------------------------------------------|-------|-----------------|

| ANL C, bit           | AND direct bit to Carry                             | 2     | 2               |

| ANL C, /bit          | AND complement of direct bit to Carry               | 2     | 2               |

| ORL C, bit           | OR direct bit to carry                              | 2     | 2               |

| ORL C, /bit          | OR complement of direct bit to Carry                | 2     | 2               |

| MOV C, bit           | Move direct bit to Carry                            | 2     | 2               |

| MOV bit, C           | Move Carry to direct bit                            | 2     | 2               |

| JC rel               | Jump if Carry is set                                | 2     | 2/4             |

| JNC rel              | Jump if Carry is not set                            | 2     | 2/4             |

| JB bit, rel          | Jump if direct bit is set                           | 3     | 3/5             |

| JNB bit, rel         | Jump if direct bit is not set                       | 3     | 3/5             |

| JBC bit, rel         | 3                                                   | 3/5   |                 |

| Program Branching    |                                                     |       |                 |

| ACALL addr11         | Absolute subroutine call                            | 2     | 4               |

| LCALL addr16         | Long subroutine call                                |       | 5               |

| RET                  | Return from subroutine                              | 1     | 6               |

| RETI                 | Return from interrupt                               | 1     | 6               |

| AJMP addr11          | Absolute jump                                       | 2     | 4               |

| LJMP addr16          | Long jump                                           | 3     | 5               |

| SJMP rel             | Short jump (relative address)                       | 2     | 4               |

| JMP @A+DPTR          | Jump indirect relative to DPTR                      | 1     | 4               |

| JZ rel               | Jump if A equals zero                               | 2     | 2/4             |

| JNZ rel              | Jump if A does not equal zero                       | 2     | 2/4             |

| CJNE A, direct, rel  | Compare direct byte to A and jump if not equal      | 3     | 3/5             |

| CJNE A, #data, rel   | Compare immediate to A and jump if not equal        | 3     | 3/5             |

| CJNE Rn, #data, rel  | Compare immediate to Register and jump if not equal | 3     | 3/5             |

| CJNE @Ri, #data, rel | Compare immediate to indirect and jump if not equal | 3     | 4/6             |

| DJNZ Rn, rel         | Decrement Register and jump if not zero             | 2     | 2/4             |

| DJNZ direct, rel     | Decrement direct byte and jump if not zero          | 3     | 3/5             |

| NOP                  | No operation                                        | 1     | 1               |

Table 6.1. CIP-51 Instruction Set Summary (Continued)

#### Notes on Registers, Operands and Addressing Modes:

**Rn**—Register R0–R7 of the currently selected register bank.

@Ri—Data RAM location addressed indirectly through R0 or R1.

**rel**—8-bit, signed (twos complement) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct**—8-bit internal data location's address. This could be a direct-access Data RAM location (0x00–0x7F) or an SFR (0x80–0xFF).

#data—8-bit constant

#data16—16-bit constant

bit—Direct-accessed bit in Data RAM or SFR

**addr11**—11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr16**—16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

### 6.2. CIP-51 Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should always be written to the value indicated in the SFR description. Future product versions may use these bits to implement new features in which case the reset value of the bit will be the indicated value, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

### SFR Definition 6.1. DPL: Data Pointer Low Byte

| Bit   | 7             | 6                 | 5               | 4             | 3           | 2   | 1 | 0 |  |  |

|-------|---------------|-------------------|-----------------|---------------|-------------|-----|---|---|--|--|

| Nam   | e             | DPL[7:0]          |                 |               |             |     |   |   |  |  |

| Туре  | •             | R/W               |                 |               |             |     |   |   |  |  |

| Rese  | et 0          | 0                 | 0               | 0             | 0           | 0   | 0 | 0 |  |  |

| SFR A | Address = 0x8 | 32                |                 |               |             |     |   |   |  |  |

| Bit   | Name          | Function          |                 |               |             |     |   |   |  |  |

| 7:0   | DPL[7:0]      | Data Pointer Low. |                 |               |             |     |   |   |  |  |

|       |               | The DPL reg       | gister is the l | ow byte of th | e 16-bit DP | ſR. |   |   |  |  |

## SFR Definition 6.2. DPH: Data Pointer High Byte

| Bit   | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|----------|---|---|---|---|---|---|---|--|

| Name  | DPH[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W      |   |   |   |   |   |   |   |  |

| Reset | 0        | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

SFR Address = 0x83

| Bit | Name     | Function                                              |

|-----|----------|-------------------------------------------------------|

| 7:0 | DPH[7:0] | Data Pointer High.                                    |

|     |          | The DPH register is the high byte of the 16-bit DPTR. |

# SFR Definition 6.3. SP: Stack Pointer

| Bit                | 7       | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|---------|----------|---|---|---|---|---|---|

| Name               | SP[7:0] |          |   |   |   |   |   |   |

| Туре               |         | R/W      |   |   |   |   |   |   |

| Reset              | 0       | 0        | 0 | 0 | 0 | 1 | 1 | 1 |

| SFR Address = 0x81 |         |          |   |   |   |   |   |   |

| Bit                | Name    | Function |   |   |   |   |   |   |

|                    |         |          |   |   |   |   |   |   |

| 7:0 | SP[7:0] | Stack Pointer.                                                                                                                                                                 |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         | The Stack Pointer holds the location of the top of the stack. The stack pointer is incre-<br>mented before every PUSH operation. The SP register defaults to 0x07 after reset. |

# SFR Definition 6.4. ACC: Accumulator

| Bit           | 7                                   | 6            | 5   | 4 | 3 | 2 | 1 | 0 |  |

|---------------|-------------------------------------|--------------|-----|---|---|---|---|---|--|

| Name ACC[7:0] |                                     |              |     |   |   |   |   |   |  |

| Туре          | Type R/W                            |              |     |   |   |   |   |   |  |

| Rese          | <b>t</b> 0                          | 0            | 0   | 0 | 0 | 0 | 0 | 0 |  |

| SFR A         | SFR Address = 0xE0; Bit-Addressable |              |     |   |   |   |   |   |  |

| Bit           | Name                                | ame Function |     |   |   |   |   |   |  |

| 7:0           | ACC[7:0]                            | Accumulato   | or. |   |   |   |   |   |  |

| This register is the accumulator for arithmetic operation |

|-----------------------------------------------------------|

|-----------------------------------------------------------|

# SFR Definition 6.5. B: B Register

| -                                   | -    |        |   |   |   |   |   |   |

|-------------------------------------|------|--------|---|---|---|---|---|---|

| Bit                                 | 7    | 6      | 5 | 4 | 3 | 2 | 1 | 0 |

| Name                                | )    | B[7:0] |   |   |   |   |   |   |

| Туре                                |      | R/W    |   |   |   |   |   |   |

| Reset                               | t 0  | 0      | 0 | 0 | 0 | 0 | 0 | 0 |

| SFR Address = 0xF0; Bit-Addressable |      |        |   |   |   |   |   |   |

| Bit                                 | Name |        |   |   |   |   |   |   |

| ы   | Name   | i unction                                                                       |

|-----|--------|---------------------------------------------------------------------------------|

| 7:0 | B[7:0] | B Register.                                                                     |

|     |        | This register serves as a second accumulator for certain arithmetic operations. |

# SFR Definition 6.6. PSW: Program Status Word

| <b>D</b> '( | 7           |                                                                                                                                                                           |                       |     |    | •      |     | • |  |

|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|----|--------|-----|---|--|

| Bit         | 1           | 6                                                                                                                                                                         | 5                     | 4   | 3  | 2      | 1   | 0 |  |

| Nam         | e CY        | CY AC F0 RS[1:0]                                                                                                                                                          |                       | OV  | F1 | PARITY |     |   |  |

| Туре        | e R/W       | R/W                                                                                                                                                                       | R/W                   | R/W |    | R/W    | R/W | R |  |

| Rese        | et 0        | 0                                                                                                                                                                         | 0                     | 0   | 0  | 0      | 0   | 0 |  |

| SFR A       | Address = 0 | xD0; Bit-Addre                                                                                                                                                            | ssable                |     |    |        |     |   |  |

| Bit         | Name        | ne Function                                                                                                                                                               |                       |     |    |        |     |   |  |

| 7           | CY          | Carry Flag.                                                                                                                                                               | Carry Flag.           |     |    |        |     |   |  |

|             |             | This bit is set when the last arithmetic operation resulted in a carry (addition) or a borrow (subtraction). It is cleared to logic 0 by all other arithmetic operations. |                       |     |    |        |     |   |  |

| 6           | AC          | Auxiliary Car                                                                                                                                                             | Auxiliary Carry Flag. |     |    |        |     |   |  |

| This bit is set when the last arithmetic operation resulted in a carry into (addition) or a   |

|-----------------------------------------------------------------------------------------------|

| borrow from (subtraction) the high order nibble. It is cleared to logic 0 by all other arith- |

| metic operations.                                                                             |

|                                                                                               |

|     |         | metic operations.                                                                                                 |

|-----|---------|-------------------------------------------------------------------------------------------------------------------|

| 5   | F0      | User Flag 0.                                                                                                      |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                   |

| 4:3 | RS[1:0] | Register Bank Select.                                                                                             |

|     |         | These bits select which register bank is used during register accesses.                                           |

|     |         | 00: Bank 0, Addresses 0x00-0x07                                                                                   |

|     |         | 01: Bank 1, Addresses 0x08-0x0F                                                                                   |

|     |         | 10: Bank 2, Addresses 0x10-0x17                                                                                   |

|     |         | 11: Bank 3, Addresses 0x18-0x1F                                                                                   |

| 2   | OV      | Overflow Flag.                                                                                                    |

|     |         | This bit is set to 1 under the following circumstances:                                                           |

|     |         | <ul> <li>An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> </ul>                              |

|     |         | <ul> <li>A MUL instruction results in an overflow (result is greater than 255).</li> </ul>                        |

|     |         | A DIV instruction causes a divide-by-zero condition.                                                              |

|     |         | The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.                  |

| 1   | F1      |                                                                                                                   |

| 1   | ГІ      | User Flag 1.                                                                                                      |

|     |         | This is a bit-addressable, general purpose flag for use under software control.                                   |

| 0   | PARITY  | Parity Flag.                                                                                                      |

|     |         | This bit is set to logic 1 if the sum of the eight bits in the accumulator is odd and cleared if the sum is even. |

# 7. Memory Organization

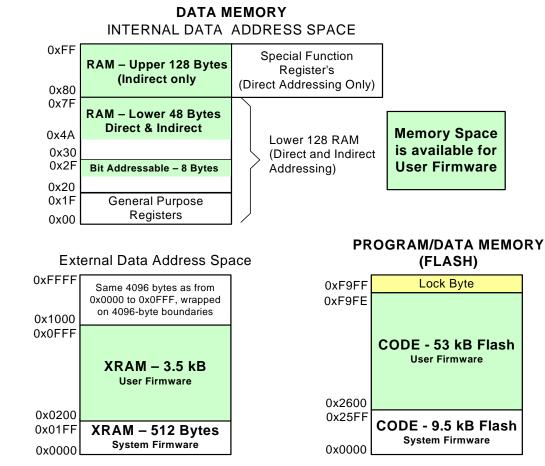

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. The memory organization of the CP2501 device family is shown in Figure 7.1

| Figure | 7.1. | CP2501 | Memory Map |

|--------|------|--------|------------|

|--------|------|--------|------------|

The System Firmware requires small portions of the Flash, RAM, and XRAM and the unused memory is available for user firmware. Table 7.1 indicates how much of each memory space is available for user firmware.

| Memory Space        | Full Address<br>Range | In Use By<br>System Firmware | User Available<br>Range | User Available<br>Size (Bytes) |

|---------------------|-----------------------|------------------------------|-------------------------|--------------------------------|

| Code                | 0x0000- 0xF9FF        | 0x0000-0x25FF                | 0x2600-0xF9FF           | 54272                          |

| Internal RAM        | 0x00–0xFF             | 0x00–0x27<br>0x30–0x49       | 0x28–0x2F<br>0x4A–0xFF  | 190                            |

| External RAM (XRAM) | 0x0000-0x0FFF         | 0x0000-0x01FF                | 0x0200-0x0FFF           | 3584                           |

### Table 7.1. CP2501Memory Allocation

# 7.1. Program Memory

The CIP-51 core has 64 kB program memory space and the CP2501 implements all 53 kB of this program memory space as in-system, re-programmable Flash memory. The address range of Flash available for user firmware is provided in Table 7.1. Addresses outside of this range

#### 7.1.1. MOVX Instruction and Program Memory

The MOVX instruction in an 8051 device is typically used to access external data memory. On the CP2501 devices, the MOVX instruction is normally used to read and write on-chip XRAM.

#### 7.1.2. Data Memory

The CP2501 devices family contain a total of 4352 bytes of RAM data memory. On the CP2501 devices, 256 bytes of this memory is mapped into the internal RAM space of the 8051. The other 4096 bytes memory is the on-chip "external" memory, or XRAM. The data memory map is shown in Figure 7.1 for reference.

#### 7.1.3. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 7.1 illustrates the data memory organization of the CP2501.

#### 7.1.3.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 6.6). This allows fast context switching when entering subroutines. Indirect addressing modes use registers R0 and R1 as index registers. The System Firmware uses all RAM locations from 0x08 through 0x1F and so the register banks are not available to user firmware.

#### 7.1.3.2. Bit Addressable Locations