# 27 GHz to 32 GHz, GaAs, pHEMT, MMIC Power Amplifier

#### **Data Sheet**

#### **FEATURES**

P<sub>SAT</sub>: 29.5 dBm High output IP3: 37 dBm High gain: 24 dB (typical) at 29 GHz to 32 GHz DC supply: 5 V at 650 mA 50 Ω matched input/output 32-lead, 5 mm × 5 mm LFCSP package: 25 mm<sup>2</sup>

#### **APPLICATIONS**

Point to point radios Point to multipoint radios Very small aperture terminals (VSATs) and satellite communication (SATCOM) Military and space

#### **GENERAL DESCRIPTION**

The HMC1132PM5E is a four-stage, gallium arsenide (GaAs) pseudomorphic high electron mobility transistor (pHEMT), monolithic microwave integrated circuit (MMIC) power amplifier. The device operates from 27 GHz to 32 GHz, providing 24 dB of gain and 29.5 dBm of saturated output power from a 5 V power supply.

The HMC1132PM5E exhibits excellent linearity with high output third-order intercept (IP3) of 37 dBm, and it is optimized for high capacity, point to point and point to

# HMC1132PM5E

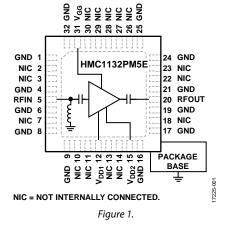

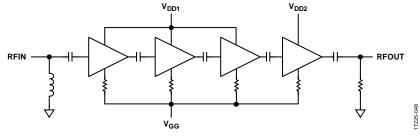

#### FUNCTIONAL BLOCK DIAGRAM

multipoint radio systems. The amplifier configuration and high gain make the HMC1132PM5E an ideal candidate for last stage signal amplification before the antenna.

The HMC1132PM5E amplifier input/outputs (I/Os) are internally matched to 50  $\Omega$ . The device is housed in a RoHS compliant, premolded cavity, 5 mm × 5 mm LFCSP package, making the device compatible with high volume surface-mount technology (SMT) assembly equipment.

Rev. 0

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 1 |

| Revision History                            | 2 |

| Specifications                              | 3 |

| Electrical Specifications                   | 3 |

| Absolute Maximum Ratings                    | 4 |

| Thermal Resistance                          | 4 |

| ESD Caution                                 | 4 |

| Pin Configuration and Function Descriptions | 5 |

| Interface Schematics                | 5  |

|-------------------------------------|----|

| Typical Performance Characteristics | 6  |

| Theory of Operation                 | 13 |

| Applications Information            | 14 |

| Application Circuit                 | 14 |

| Evaluation Board                    | 15 |

| Bill of Materials                   | 15 |

| Evaluation Board Schematic          | 16 |

| Outline Dimensions                  | 17 |

| Ordering Guide                      | 17 |

#### **REVISION HISTORY**

9/2018—Revision 0: Initial Version

### **SPECIFICATIONS**

#### **ELECTRICAL SPECIFICATIONS**

$T_A = 25^{\circ}C$ ,  $V_{DD1} = V_{DD2} = 5$  V, quiescent current ( $I_{DDQ}$ ) = 650 mA, and frequency range = 27 GHz to 29 GHz, unless otherwise noted.

| Parameter                         | Symbol           | Min  | Тур   | Max | Unit  | Test Conditions/Comments                                                                                           |

|-----------------------------------|------------------|------|-------|-----|-------|--------------------------------------------------------------------------------------------------------------------|

| FREQUENCY RANGE                   |                  | 27   |       | 29  | GHz   |                                                                                                                    |

| GAIN                              |                  | 19   | 22    |     | dB    |                                                                                                                    |

| Gain Variation over Temperature   |                  |      | 0.028 |     | dB/°C |                                                                                                                    |

| RETURN LOSS                       |                  |      |       |     |       |                                                                                                                    |

| Input                             |                  |      | 7     |     | dB    |                                                                                                                    |

| Output                            |                  |      | 9     |     | dB    |                                                                                                                    |

| POWER                             |                  |      |       |     |       |                                                                                                                    |

| Output Power for 1 dB Compression | P1dB             | 26.5 | 28.5  |     | dBm   |                                                                                                                    |

| Saturated Output Power            | Psat             |      | 29.5  |     | dBm   |                                                                                                                    |

| OUTPUT THIRD-ORDER INTERCEPT      | IP3              |      | 37    |     | dBm   | Measurement taken at 5 V, 650 mA, output power ( $P_{OUT}$ ) per tone = 20 dBm                                     |

| NOISE FIGURE                      | NF               |      | 7     |     | dB    |                                                                                                                    |

| SUPPLY VOLTAGE                    | V <sub>DD</sub>  | 4    |       | 6   | V     |                                                                                                                    |

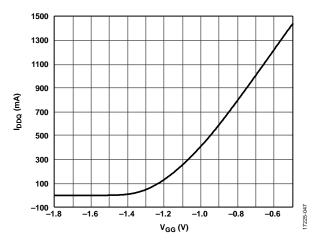

| QUIESCENT SUPPLY CURRENT          | I <sub>DDQ</sub> | 500  |       | 750 | mA    | Adjust the gate bias voltage ( $V_{GG}$ ) from $-2$ V up to 0 V to achieve desired quiescent current ( $I_{DDQ}$ ) |

$T_A = 25^{\circ}C$ ,  $V_{DD1} = V_{DD2} = 5$  V, quiescent current ( $I_{DDQ}$ ) = 650 mA, and frequency range = 29 GHz to 32 GHz, unless otherwise noted.

| Table 2.                          |                 |     |       |     |       |                                                                                                                      |

|-----------------------------------|-----------------|-----|-------|-----|-------|----------------------------------------------------------------------------------------------------------------------|

| Parameter                         | Symbol          | Min | Тур   | Max | Unit  | Test Conditions/Comments                                                                                             |

| FREQUENCY RANGE                   |                 | 29  |       | 32  | GHz   |                                                                                                                      |

| GAIN                              |                 | 21  | 24    |     | dB    |                                                                                                                      |

| Gain Variation over Temperature   |                 |     | 0.034 |     | dB/°C |                                                                                                                      |

| RETURN LOSS                       |                 |     |       |     |       |                                                                                                                      |

| Input                             |                 |     | 11    |     | dB    |                                                                                                                      |

| Output                            |                 |     | 14    |     | dB    |                                                                                                                      |

| POWER                             |                 |     |       |     |       |                                                                                                                      |

| Output Power for 1 dB Compression | P1dB            | 27  | 29    |     | dBm   |                                                                                                                      |

| Saturated Output Power            | Psat            |     | 29.5  |     | dBm   |                                                                                                                      |

| OUTPUT THIRD-ORDER INTERCEPT      | IP3             |     | 37    |     | dBm   | Measurement taken at 5 V, 650 mA, $P_{OUT}$ per tone = 20 dBm                                                        |

| NOISE FIGURE                      | NF              |     | 5.5   |     | dB    |                                                                                                                      |

| SUPPLY VOLTAGE                    | V <sub>DD</sub> | 4   |       | 6   | V     |                                                                                                                      |

| QUIESCENT SUPPLY CURRENT          | Iddq            | 500 |       | 750 | mA    | Adjust the gate bias voltage ( $V_{GG}$ ) from $-2 V$ up to $0 V$ to achieve desired quiescent current ( $I_{DDQ}$ ) |

\_ \_ \_ \_

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                                                                                                      | Rating                    |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Drain Bias Voltage (V <sub>DDx</sub> )                                                                                         | 6.5 V                     |

| Gate Voltage (V <sub>GG</sub> )                                                                                                | –2.5 V to +0.5 V          |

| Radio Frequency Input Power (RFIN) <sup>1</sup>                                                                                | 18 dBm                    |

| Continuous Power Dissipation (P <sub>DISS</sub> ),<br>T <sub>BASE</sub> <sup>2</sup> = 85°C (Derate 57.47 mW/°C<br>Above 85°C) | 5.17 W                    |

| Output Load Voltage Standing Wave<br>Ratio (VSWR)                                                                              | 7:1                       |

| Storage Temperature Range                                                                                                      | –65°C to +150°C           |

| Operating Temperature Range                                                                                                    | –55°C to +85°C            |

| Peak Reflow Temperature, Moisture<br>Sensitivity Level 3 (MSL3) <sup>3</sup>                                                   | 260°C                     |

| Electrostatic Discharge (ESD) Sensitivity                                                                                      |                           |

| Human Body Model (HBM)                                                                                                         | Class 0B, passed<br>150 V |

| Junction Temperature to Maintain<br>1 Million Hour Mean Time to Failure<br>(MTTF)                                              | 175°C                     |

| Nominal Junction Temperature<br>$(T_{BASE}^2 = 85^{\circ}C, V_{DDx} = 5 \text{ V})$                                            | 141.55°C                  |

<sup>1</sup> Maximum input power is limited to 18 dBm or thermal limits constrained by maximum power dissipation (see Figure 31), whichever is lower.

$^2\,T_{\text{BASE}}$  is the actual temperature on the package base.

<sup>3</sup> See the Ordering Guide for additional information.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{\text{JC}}$  is the junction to case thermal resistance.

#### Table 4. Thermal Resistance

| Package              | θις  | Unit |  |  |  |

|----------------------|------|------|--|--|--|

| CG-32-2 <sup>1</sup> | 17.4 | °C/W |  |  |  |

<sup>1</sup> Thermal resistance ( $\theta_{JC}$ ) was determined by simulation under the following conditions: the heat transfer is due solely to thermal conduction from the channel, through the ground paddle, to the PCB, and the ground paddle is held constant at the operating temperature of 85°C.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

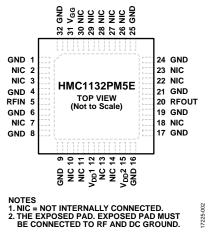

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### **Table 5. Pin Function Descriptions**

| Pin No.                                          | Mnemonic                            | Description                                                                                                                                                                                                              |

|--------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 4, 6, 8, 9, 16, 17, 19,<br>21, 24, 25, 32     | GND                                 | Ground. These pins and the exposed pad must be connected to RF and dc ground.                                                                                                                                            |

| 2, 3, 7, 10, 11, 13, 14,<br>18, 22, 23, 26 to 30 | NIC                                 | Not Internally Connected. These pins are not connected internally. However, all data was measured with these pins connected to RF and dc ground externally.                                                              |

| 5                                                | RFIN                                | RF Input. This pin is dc-coupled and matched to 50 $\Omega$ . See Figure 4 for the RFIN interface schematic.                                                                                                             |

| 12, 15                                           | V <sub>DD1</sub> , V <sub>DD2</sub> | Drain Bias Voltage. External 100 pF, 10 nF, and 4.7 $\mu$ F bypass capacitors are required. See Figure 5 for the V <sub>DD1</sub> and V <sub>DD2</sub> interface schematic.                                              |

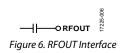

| 20                                               | RFOUT                               | RF Output. This pin is ac-coupled and matched to 50 $\Omega$ . See Figure 6 for the RFOUT interface schematic.                                                                                                           |

| 31                                               | $V_{GG}$                            | Gate Control for Amplifier. Adjust V <sub>GG</sub> to achieve the recommended bias current. External 100 pF, 10 nF, and 4.7 μF bypass capacitors are required. See Figure 7 for the V <sub>GG</sub> interface schematic. |

|                                                  | EPAD                                | Exposed Pad. The exposed pad must be connected to RF and dc ground.                                                                                                                                                      |

#### **INTERFACE SCHEMATICS**

Figure 4. RFIN Interface

Figure 5. V<sub>DD1</sub> and V<sub>DD2</sub> Interface

Figure 7. V<sub>GG</sub> Interface

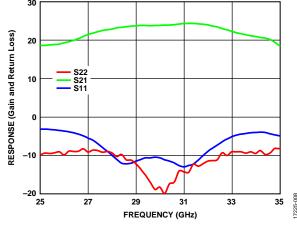

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 8. Response (Gain and Return Loss) vs. Frequency,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

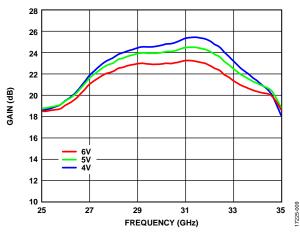

Figure 9. Gain vs. Frequency for Various Drain Bias Voltages ( $V_{DDx}$ ),  $I_{DDQ} = 650 \text{ mA}$

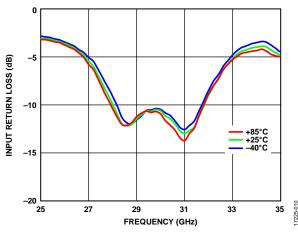

Figure 10. Input Return Loss vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

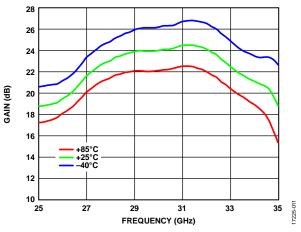

Figure 11. Gain vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $l_{DDQ} = 650 \text{ mA}$

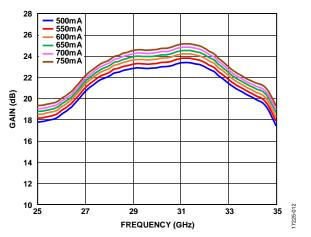

Figure 12. Gain vs. Frequency for Various Quiescent Currents ( $I_{DDQ}$ ),  $V_{DDx} = 5 V$

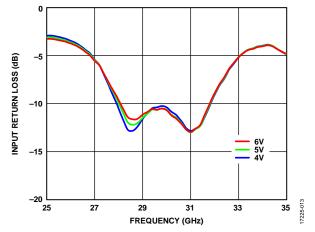

Figure 13. Input Return Loss vs. Frequency for Various Drain Bias Voltages (V<sub>DDx</sub>), I<sub>DDQ</sub> = 650 mA

### **Data Sheet**

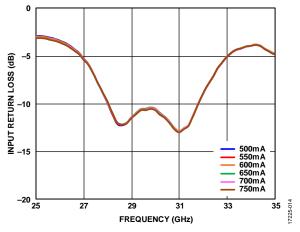

Figure 14. Input Return Loss vs. Frequency for Various Quiescent Currents  $(I_{DDQ}), V_{DDx} = 5 V$

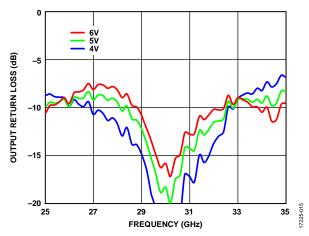

Figure 15. Output Return Loss vs. Frequency for Various Drain Bias Voltages  $(V_{DDx})$ ,  $I_{DDQ} = 650 \text{ mA}$

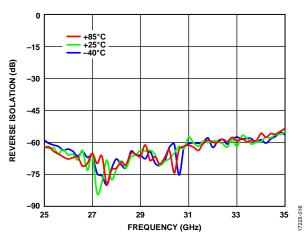

Figure 16. Reverse Isolation vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

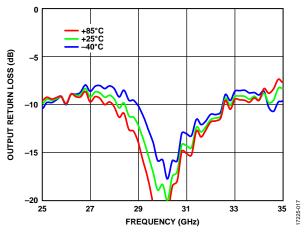

Figure 17. Output Return Loss vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

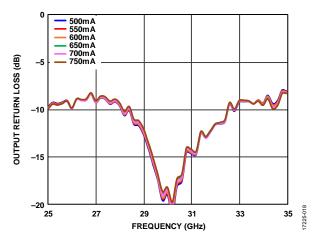

Figure 18. Output Return Loss vs. Frequency for Various Quiescent Currents ( $I_{DDQ}$ ),  $V_{DDx} = 5 V$

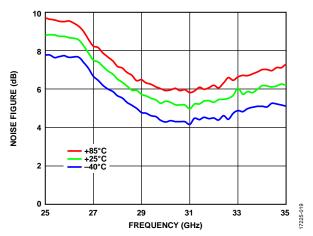

Figure 19. Noise Figure vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

Figure 20. P1dB vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

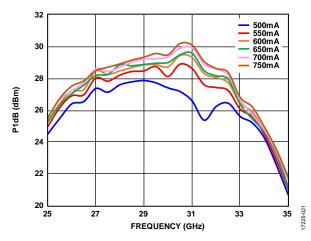

Figure 21. P1dB vs. Frequency for Various Quiescent Currents ( $I_{DDQ}$ ),  $V_{DDx} = 5 V$

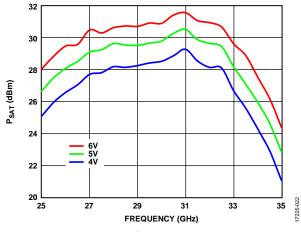

Figure 22.  $P_{SAT}$  vs. Frequency for Various Drain Bias Voltages (V<sub>DDx</sub>),  $I_{DDQ} = 650 \text{ mA}$

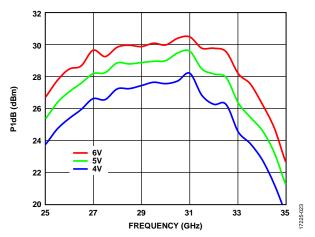

Figure 23. P1dB vs. Frequency for Various Drain Bias Voltages ( $V_{DDx}$ ),  $I_{DDQ} = 650 \text{ mA}$

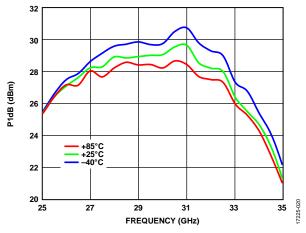

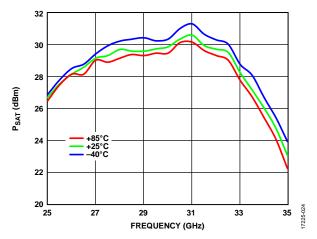

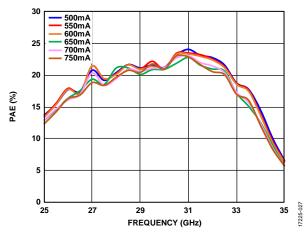

Figure 24.  $P_{SAT}$  vs. Frequency for Various Temperatures,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 \text{ mA}$

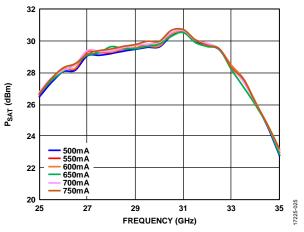

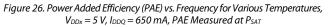

Figure 25.  $P_{SAT}$  vs. Frequency for Various Quiescent Currents ( $I_{DDQ}$ ),  $V_{DDx} = 5 V$

### **Data Sheet**

#### 30 25 20 PAE (%) 15 +85°C +25°C –40°C 10 5 0 7225-026 25 27 29 31 33 35 FREQUENCY (GHz)

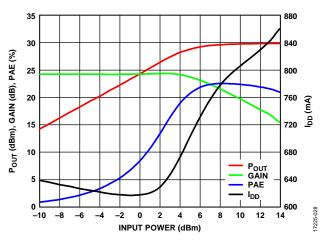

Figure 28. Output Power (Pour), Gain, Power Added Efficiency (PAE), and Drain Current (I<sub>DD</sub>) vs. Input Power, 29.5 GHz, V<sub>DDx</sub> = 5 V, I<sub>DDQ</sub> = 650 mA

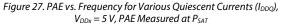

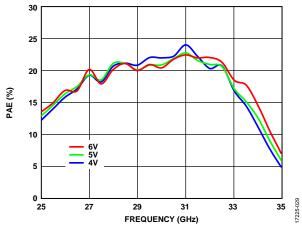

Figure 29. PAE vs. vs. Frequency for Various Drain Bias Voltages ( $V_{DDx}$ ),  $I_{DDQ} = 650$  mA, PAE Measured at  $P_{SAT}$

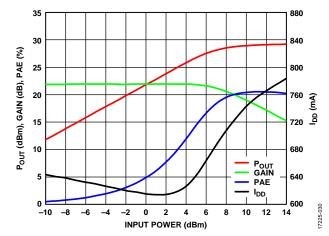

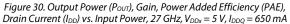

Figure 31. Output Power (P<sub>OUT</sub>), Gain, Power Added Efficiency (PAE), Drain Current (I<sub>DD</sub>) vs. Input Power, 32 GHz, V<sub>DDx</sub> = 5 V, I<sub>DDQ</sub> = 650 mA

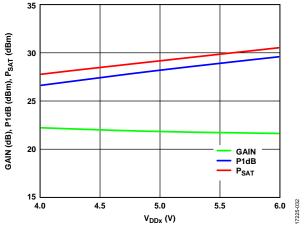

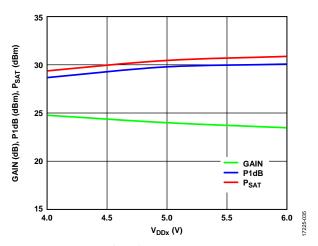

Figure 32. Gain, P1dB, and  $P_{SAT}$  vs.  $V_{DDx}$ , 27 GHz,  $I_{DDQ} = 650$  mA

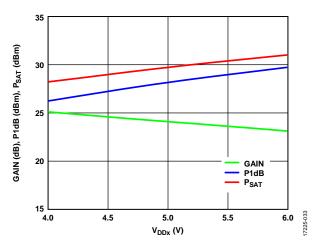

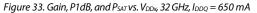

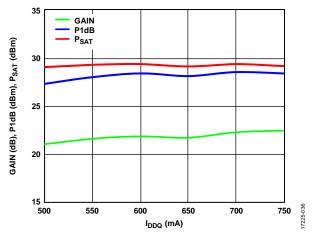

Figure 34. Gain, P1dB, and PSAT vs. IDDQ, 29.5 GHz, VDDx = 5 V

Figure 35. Gain, P1dB, and PSAT vs. VDDX, 29.5 GHz, IDDQ = 650 mA

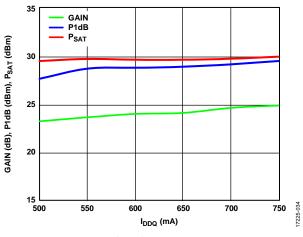

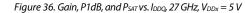

Figure 37. Gain, P1dB, and Psat vs. IDDQ, 32 GHz, VDDx = 5 V

### **Data Sheet**

#### 5.5 MAXIMUM PDISS 5.0 4.5 POWER DISSIPATION (W) 4.0 3.5 3.0 2.5 32GHz 31GHz 30GHz 29GHz 2.0 1.5 28GHz 27GHz 1.0 7225-038 -10 -6 -2 2 6 10 14 INPUT POWER (dBm)

Figure 38. Power Dissipation vs. Input Power at  $T_A = 85$  °C,  $V_{DDx} = 5$  V,  $I_{DDQ} = 650$  mA

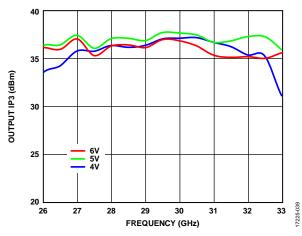

Figure 39. Output IP3 vs. Frequency for Various Supply Voltages ( $V_{DDx}$ ),  $I_{DDQ} = 650 \text{ mA}$

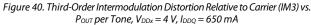

Figure 41. Output IP3 vs. Frequency for Various Temperatures,  $P_{OUT}$  per Tone = 20 dBm,  $V_{DDx}$  = 5 V,  $I_{DDQ}$  = 650 mA

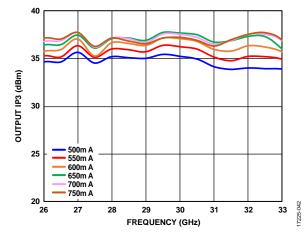

Figure 42. Output IP3 vs. Frequency for Various Quiescent Currents ( $I_{DDQ}$ ),  $V_{DDx} = 5 V$

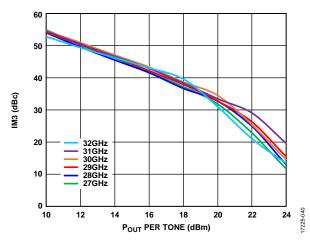

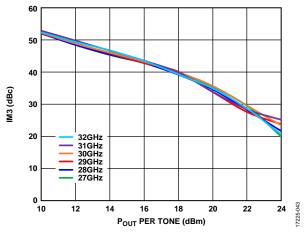

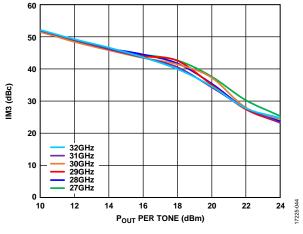

Figure 43. IM3 vs.  $P_{OUT}$  per Tone,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 mA$

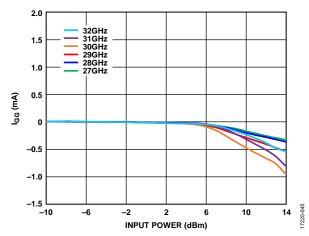

Figure 45. Gate Current ( $I_{GG}$ ) vs. Input Power for Various Frequencies,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 mA$

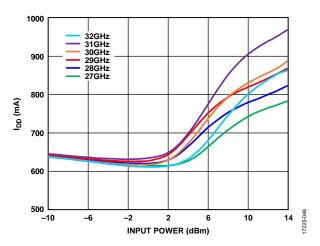

Figure 46. Drain Current ( $I_{DD}$ ) vs. Input Power for Various Frequencies,  $V_{DDx} = 5 V$ ,  $I_{DDQ} = 650 mA$

Figure 47. Quiescent Current ( $I_{DDQ}$ ) vs.  $V_{GG}$ ,  $V_{DDx} = 5$  V, Representative of a Typical Device

### **THEORY OF OPERATION**

The architecture of the HMC1132PM5E power amplifier is shown in Figure 48. The amplifier consists of a cascade of four, single-stage amplifiers. This approach provides a high P1dB as well as a high gain that is flat across the operating frequency range.  $V_{\rm DD1}$  provides drain bias to the first three gain stages,

whereas  $V_{DD2}$  provides drain bias to the fourth gain stage.  $V_{GG}$  provides gate bias to all four gain stages, allowing control of the quiescent current. RFIN and RFOUT provide dc paths to GND as a way of increasing the overall ESD robustness of the device.

Figure 48. Architecture and Simplified Block Diagram

### **APPLICATIONS INFORMATION**

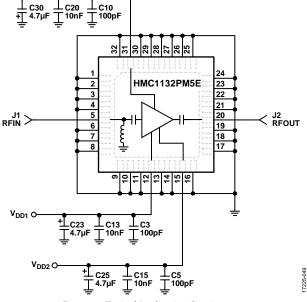

The HMC1132PM5E is a GaAs, pHEMT, MMIC power amplifier. Capacitive bypassing is required for  $V_{DD1}$ ,  $V_{DD2}$ , and  $V_{GG}$  (see Figure 49). The drain bias voltage must be applied to both  $V_{DD1}$  and  $V_{DD2}$ , and the gate bias voltage must be applied to  $V_{GG}$ . Although the RFIN and RFOUT ports ac couple the signal, dc paths to GND are provided to increase the ESD robustness of the device. External dc blocking of RFIN and/or RFOUT is desirable when appreciable levels of dc are present.

All measurements for this device were taken using the typical application circuit shown in Figure 49, configured as shown on the evaluation PCB (see Figure 50).

The following bias sequence is recommended during power-up:

- 1. Connect the evaluation board to ground.

- 2. Set the gate bias voltage to -2 V.

- 3. Set the drain bias voltages to 5 V.

- 4. Increase the gate bias voltage to achieve a quiescent  $I_{DDQ} = 650 \text{ mA}$ .

V<sub>GG</sub> C

5. Apply the RF signal.

The following bias sequence is recommended during power-down:

- 1. Turn off the RF signal.

- 2. Decrease the gate bias voltage to -2 V to achieve an  $I_{DDQ} = 0$  mA (approximately).

- 3. Decrease the drain bias voltages to 0 V.

- 4. Increase the gate bias voltage to 0 V.

The  $V_{DDx}$  = 5 V and  $I_{DDQ}$  = 650 mA bias conditions are the operating points recommended to optimize the overall performance of the device. Unless otherwise noted, the data shown was obtained using the recommended bias conditions. Operation of the HMC1132PM5E at different bias conditions may provide performance that differs from what is shown in the Typical Performance Characteristics section. Biasing the HMC1132PM5E for a higher drain current typically results in higher P1dB, P<sub>SAT</sub>, and gain, though at the expense of increased power consumption.

#### **APPLICATION CIRCUIT**

Figure 49 shows the typical application circuit.

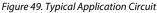

### **EVALUATION BOARD**

The HMC1132PM5E evaluation board is a 2-layer board fabricated using Rogers 4350 and best practices suited for high frequency RF design. The RF input and RF output traces have a 50  $\Omega$  characteristic impedance. The circuit board is attached to a heat sink. Components are mounted using SN63 solder, allowing rework of the surface-mount components without compromising attachment of the PCB to a heat sink.

The evaluation board and populated components are designed to operate over the ambient temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

During operation, to control the temperature of the HMC1132PM5E, attach the evaluation board to a temperature controlled plate. For the proper bias sequence, see the Applications Information section.

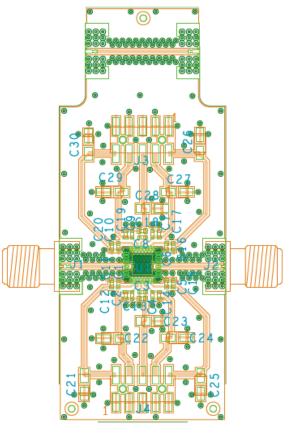

The evaluation board schematic is shown in Figure 51. A fully populated and tested evaluation board (see Figure 50) is available from Analog Devices, Inc., upon request.

7225-050

Figure 50. Evaluation PCB

#### **BILL OF MATERIALS**

| ltem          | Description                                                      |

|---------------|------------------------------------------------------------------|

| J1, J2        | Connector, SRI K connector. SRI Part Number 25-146-1000-92.      |

| J3, J4        | DC pins.                                                         |

| J5, J6        | Connector, SRI K connector. Not populated.                       |

| C3, C5, C10   | 100 pF capacitors, 0402 package.                                 |

| C13, C15, C20 | 10 nF capacitors, 0402 package.                                  |

| C23, C25, C30 | 4.7 μF capacitors, Case A package.                               |

| U1            | HMC1132PM5E amplifier.                                           |

| Heat Sink     | Used for thermal transfer from the HMC1132PM5E amplifier.        |

| РСВ           | 08_047754 evaluation board. Circuit board material: Rogers 4350. |

17225-051

#### **EVALUATION BOARD SCHEMATIC**

Figure 51. Evaluation Board Schematic

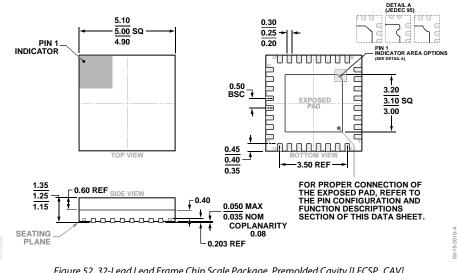

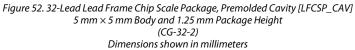

### **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Temperature    | MSL Rating <sup>3</sup> | <b>Description</b> <sup>4</sup>                                     | Package<br>Option |

|-----------------------|----------------|-------------------------|---------------------------------------------------------------------|-------------------|

| HMC1132PM5E           | -40°C to +85°C | MSL3                    | 32-Lead Lead Frame Chip Scale Package, Premolded Cavity [LFCSP_CAV] | CG-32-2           |

| HMC1132PM5ETR         | -40°C to +85°C | MSL3                    | 32-Lead Lead Frame Chip Scale Package, Premolded Cavity [LFCSP_CAV] | CG-32-2           |

| EV1HMC1132PM5         |                |                         | Evaluation Board                                                    |                   |

<sup>1</sup> All models are RoHS compliant parts.

<sup>2</sup> When ordering the evaluation board only, reference the model number, EV1HMC1132PM5.

<sup>3</sup> See the Absolute Maximum Ratings section for additional information.

<sup>4</sup> The lead finish of the HMC1132PM5E and the HMC1132PM5ETR is nickel palladium gold (NiPdAu).

©2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D17225-0-9/18(0)