The following document contains information on Cypress products. Although the document is marked with the name "Broadcom", the company that originally developed the specification, Cypress will continue to offer these products to new and existing customers.

#### **CONTINUITY OF SPECIFICATIONS**

There is no change to this document as a result of offering the device as a Cypress product. Any changes that have been made are the result of normal document improvements and are noted in the document history page, where supported. Future revisions will occur when appropriate, and changes will be noted in a document history page.

#### CONTINUITY OF ORDERING PART NUMBERS

Cypress continues to support existing part numbers. To order these products, please use only the Cypress Ordering Part Number listed in the table.

| Broadcom Ordering Part Number                                                                                                                                                             | Cypress Ordering Part Number                                                                                                                                           |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BCM20730A2KML2GT<br>BCM20730A1KML2G<br>BCM20730A1KMLG<br>BCM20730A1KFBGT<br>BCM20730A2KFBG<br>BCM20730A1KFBG<br>BCM20730A1KML2GT<br>BCM20730A2KML2G<br>BCM20730A1KML2G<br>BCM20730A1KMLGT | CYW20730A2KML2GT<br>CYW20730A1KML2G<br>CYW20730A1KMLG<br>CYW20730A1KFBGT<br>CYW20730A2KFBG<br>CYW20730A1KFBG<br>CYW20730A1KML2GT<br>CYW20730A2KML2G<br>CYW20730A1KMLGT |  |

| BCM20730A2KFBGT                                                                                                                                                                           | CYW20730A2KFBGT                                                                                                                                                        |  |

#### FOR MORE INFORMATION

Please visit our website at <a href="www.cypress.com">www.cypress.com</a> or contact your <a href="local sales office">local sales office</a> for additional information about Cypress products and services.

#### **OUR CUSTOMERS**

Cypress is for true innovators – in companies both large and small.

Our customers are smart, aggressive, out-of-the-box thinkers who design and develop game-changing products that revolutionize their industries or create new industries with products and solutions that nobody ever thought of before.

#### **ABOUT CYPRESS**

Founded in 1982, Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, home automation and appliances, consumer electronics and medical products. Cypress's programmable systems-on-chip, general-purpose microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first.

Cypress is committed to providing customers with the best support and engineering resources on the planet enabling innovators and out-of-the-box thinkers to disrupt markets and create new product categories in record time. To learn more, go to <a href="https://www.cypress.com">www.cypress.com</a>.

Cypress Semiconductor Corporation

Document Number: 002-14824 Rev. \*H

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised October 17, 2016

# Single-Chip Bluetooth Transceiver for Wireless Input Devices

#### **GENERAL DESCRIPTION**

The Broadcom® BCM20730 is a Bluetooth 3.0-compliant, stand-alone baseband processor with an integrated 2.4 GHz transceiver. It is ideal for wireless input device applications including game controllers, keyboards, 3D glasses, remote controls, gestural input devices, and sensor devices. Built-in firmware adheres to the Bluetooth Human Interface Device (HID) profile and Bluetooth Device ID profile specifications.

The BCM20730 radio has been designed to provide low power, low cost, and robust communications for applications operating in the globally available 2.4 GHz unlicensed ISM band. It is fully compliant with Bluetooth Radio Specification 3.0.

The single-chip Bluetooth transceiver is a monolithic component implemented in a standard digital CMOS process and requires minimal external components to make a fully compliant Bluetooth device. The BCM20730 is available in three package options: a 32-pin, 5 mm × 5 mm QFN, a 40-pin, 6 mm × 6 mm QFN, and a 64-pin, 7 mm × 7 mm BGA.

#### **APPLICATIONS**

- Wireless pointing devices: mice, trackballs, gestural controls

- Wireless keyboards

- 3D glasses

- Remote controls

- · Game controllers

- Point-of-sale (POS) input devices

- Remote sensors

- · Home automation

- · Personal health and fitness monitoring

#### **FEATURES**

- On-chip support for common keyboard and mouse interfaces eliminates external processor

- Programmable keyscan matrix interface, up to 8 × 20 key-scanning matrix

- 3-axis quadrature signal decoder

- Shutter control for 3D glasses

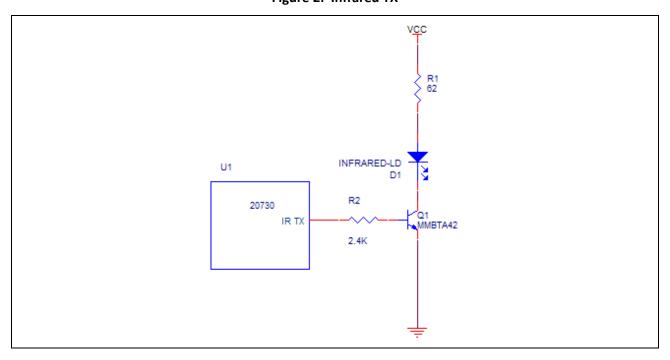

- Infrared modulator

- IR learning

- Triac control

- Triggered Broadcom Fast Connect

- Supports Adaptive Frequency Hopping

- · Excellent receiver sensitivity

- Bluetooth specification 3.0 compatible, including enhanced power control (Unicast Connectionless Data)

- Bluetooth HID profile version 1.0 compliant

- Bluetooth Device ID profile version 1.3 compliant

- Bluetooth AVRCP-CT profile version 1.3 compliant

- 10-bit auxiliary ADC with 28 analog channels

- On-chip support for serial peripheral interface (master and slave modes)

- Broadcom Serial Communications (BSC) interface (compatible with Philips® (now NXP) I<sup>2</sup>C slaves)

- Programmable output power control meets Class 2 or Class 3 requirements

- Class 1 operation supported with external PA and T/R switch

- Integrated ARM Cortex<sup>™</sup>-M3 based microprocessor core

- On-chip power-on reset (POR)

- Support for EEPROM and serial flash interfaces

- Integrated low-dropout regulator (LDO)

- On-chip software controlled power management unit

- Three package types are available:

- 32-pin QFN package (5 mm × 5 mm)

- 40-pin QFN package (6 mm × 6 mm)

- 64-pin BGA package (7 mm × 7 mm)

- RoHS compliant

BCM20730 Data Sheet Revision History

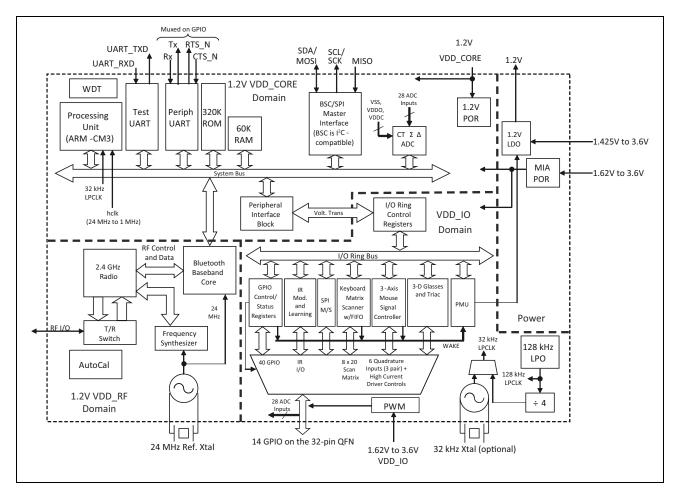

Figure 1: Functional Block Diagram

BCM20730 Data Sheet Revision History

# **Revision History**

| Revision      | Date       | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20730-DS108-R | 09/09/13   | Revised:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |            | <ul> <li>Section: "Shutter Control for 3D Glasses," on page 13</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |            | <ul> <li>Table 27: "Ordering Information," on page 58</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |            | Added:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |            | Table 15: "ESD Tolerance," on page 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20730-DS107-R | 10/10/12   | Revised:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |            | "SPI Timing" on page 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 20730-DS106-R | 09/20/11   | Changed from a Preliminary Data Sheet to a Data Sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 20730-DS105-R | 06/29/11   | Added:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |            | <ul> <li>Figure 9: "32-Pin QFN Ball Map," on page 39</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |            | <ul> <li>Figure 16: "32-Pin QFN Package," on page 52</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

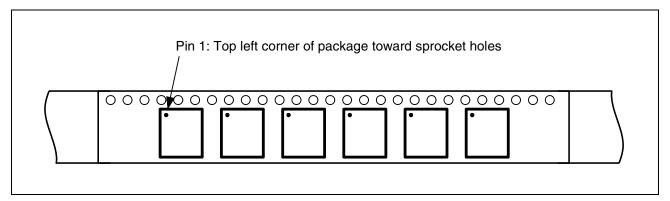

|               |            | <ul> <li>Table 20: "BCM20730 5 × 5 × 1 mm QFN, 32-Pin Tape Reel<br/>Specifications," on page 55</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |            | Revised:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |            | <ul> <li>General Description and Features on Cover</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               |            | <ul> <li>Figure 1: "Functional Block Diagram," on page 2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |            | <ul> <li>"ADC Port" on page 17</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |            | <ul> <li>Table 2: "BCM20730 First SPI Set (Master Mode)," on page 18</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |            | <ul> <li>Table 2: "BCM20730 First SPI Set (Master Mode)," on page 18</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |            | <ul> <li>Table 2: "BCM20730 First SPI Set (Master Mode)," on page 18</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

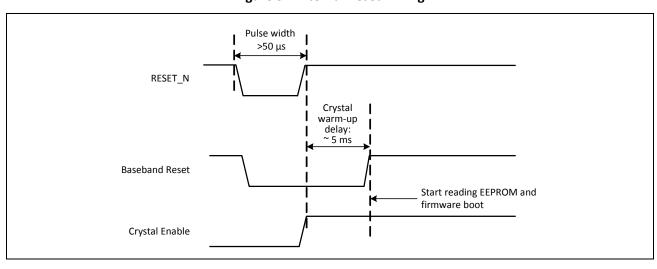

|               |            | <ul> <li>Figure 5: "External Reset Timing," on page 22</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |            | <ul> <li>"GPIO Port" on page 27</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |            | <ul> <li>"BBC Power Management" on page 29</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |            | <ul> <li>Table 7: "Pin Descriptions," on page 30</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |            | <ul> <li>Table 8: "GPIO Pin Descriptions," on page 32</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|               |            | Table 12: "ADC Specifications," on page 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20730-DS104-R | 05/09/2011 | Revised:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |            | Figure 1: "Functional Block Diagram," on page 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|               |            | "ADC Port" on page 17  The state of the |

|               |            | Table 10: "Power Supply," on page 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20730-DS103-R | 04/06/11   | Revised:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|               |            | Table 14: "Current Consumption," on page 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|               |            | <ul> <li>Table 23: "Ordering Information," on page 54</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

BCM20730 Data Sheet Revision History

| Revision      | Date     | Change Description                                                                                            |

|---------------|----------|---------------------------------------------------------------------------------------------------------------|

| 20730-DS102-R | 03/23/11 | Added:                                                                                                        |

|               |          | <ul> <li>Table 1: "ADC Modes," on page 18</li> </ul>                                                          |

|               |          | Revised:                                                                                                      |

|               |          | <ul> <li>Figure 1: "Functional Block Diagram," on page 2</li> </ul>                                           |

|               |          | "ADC Port" on page 17                                                                                         |

|               |          | <ul> <li>"Internal LDO Regulator" on page 22</li> </ul>                                                       |

|               |          | <ul> <li>"UART Interface" on page 23</li> </ul>                                                               |

|               |          | <ul> <li>Table 6: "XTAL Oscillator Characteristics," on page 25</li> </ul>                                    |

|               |          | <ul> <li>Table 8: "GPIO Pin Descriptions," on page 30</li> </ul>                                              |

|               |          | <ul> <li>Table 10: "Power Supply," on page 39</li> </ul>                                                      |

|               |          | <ul> <li>Table 11: "LDO Regulator Electrical Specifications," on page 40</li> </ul>                           |

|               |          | <ul> <li>Table 12: "ADC Specifications," on page 41</li> </ul>                                                |

|               |          | <ul> <li>Table 14: "Current Consumption," on page 42</li> </ul>                                               |

|               |          | <ul> <li>Table 15: "Receiver RF Specifications," on page 43</li> </ul>                                        |

|               |          | <ul> <li>Table 16: "Transmitter RF Specifications," on page 44</li> </ul>                                     |

|               |          | <ul> <li>Table 18: "SPI Interface Timing Specifications," on page 46</li> </ul>                               |

|               |          | <ul> <li>Table 21: "BCM20730 6 × 6 × 1 mm QFN, 40-Pin Tape Reel<br/>Specifications," on page 52</li> </ul>    |

|               |          | <ul> <li>Table 22: "BCM20730 7 × 7 × .8 mm WFBGA, 64-Pin Tape Reel<br/>Specifications," on page 52</li> </ul> |

|               |          | Deleted:                                                                                                      |

|               |          | Placeholder for Figure 4: Triac Control                                                                       |

|               |          | <ul> <li>Placeholder for Figure 18: BCM20730, 6 x 6 QFN Package Tray</li> </ul>                               |

|               |          | <ul> <li>Placeholder for Figure 19: BCM20730, 7 x 7 FBGA Package Tray</li> </ul>                              |

| Revision       | Date    | Change Description                                                                                                |

|----------------|---------|-------------------------------------------------------------------------------------------------------------------|

| 20730-DS101-R  | 6/25/10 | Added:                                                                                                            |

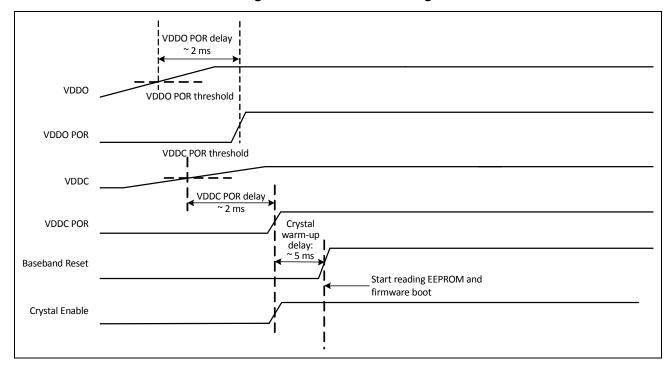

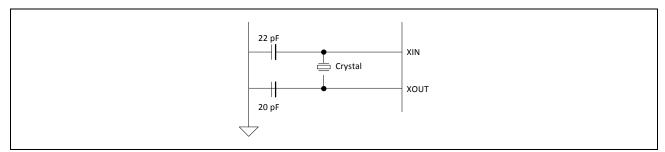

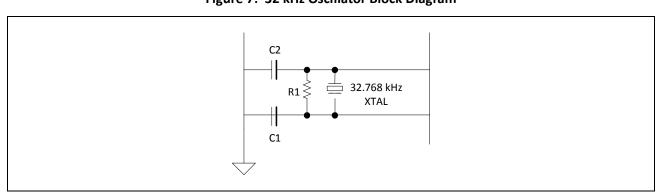

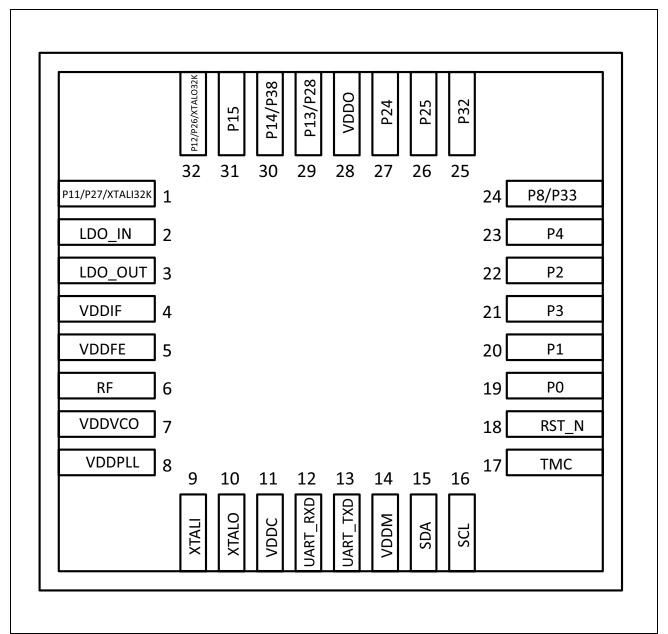

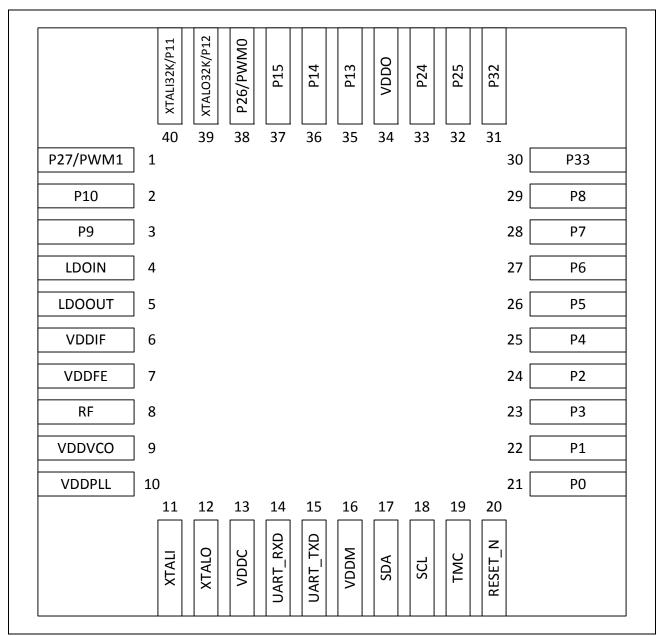

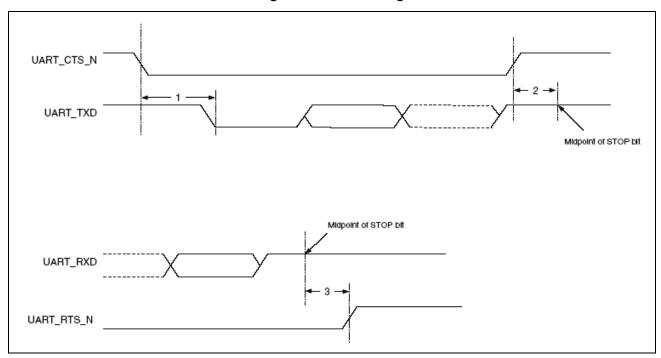

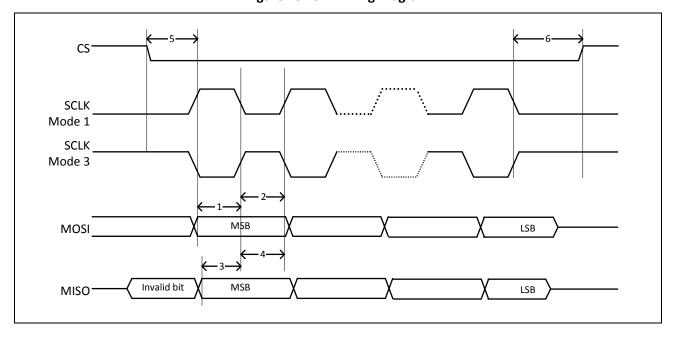

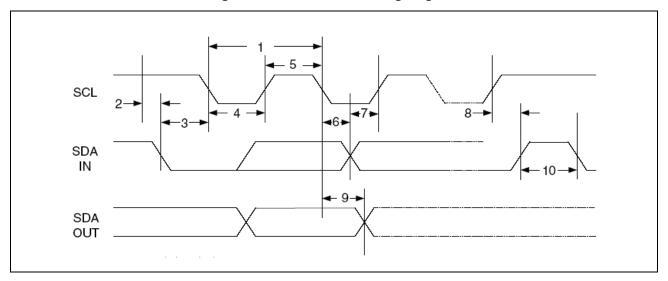

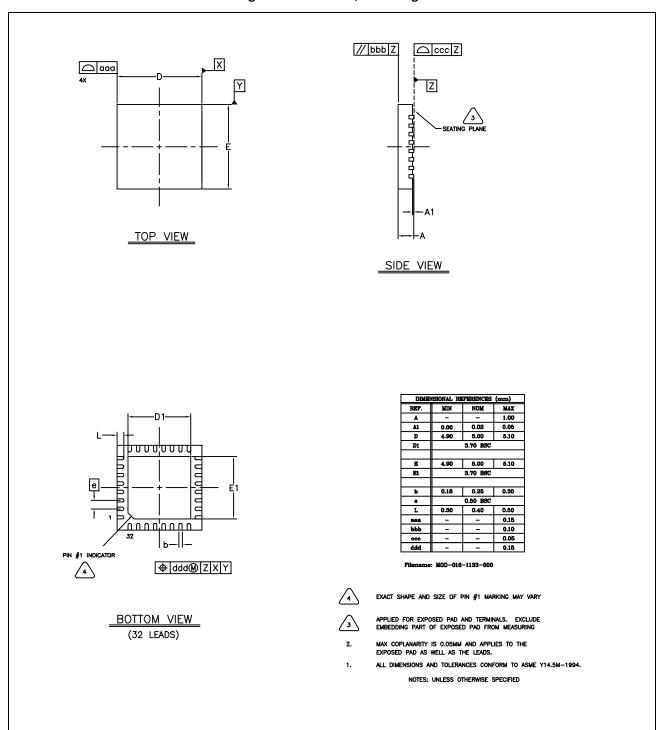

|                |         | <ul> <li>"Shutter Control for 3D Glasses" on page 10.</li> </ul>                                                  |