# Programmable Reference

### FEATURES

- Guaranteed 0.4% Initial Voltage Tolerance

- 0.1Ω Typical Dynamic Output Impedance

- Fast Turn On

- Sink Current Capability, 1mA to 100mA

- Low Reference Pin Current

- Available in N8, S8 or 3-Lead TO-92 Z Packages

# **APPLICATIONS**

- Linear Regulators

- Adjustable Power Supplies

- Switching Power Supplies

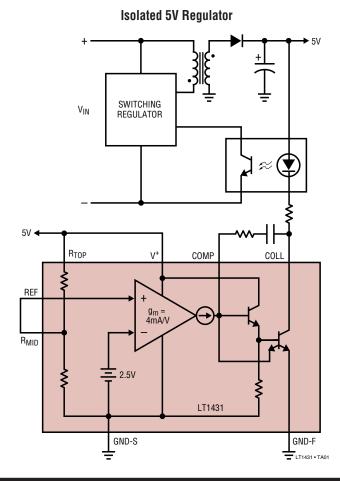

TYPICAL APPLICATION

### DESCRIPTION

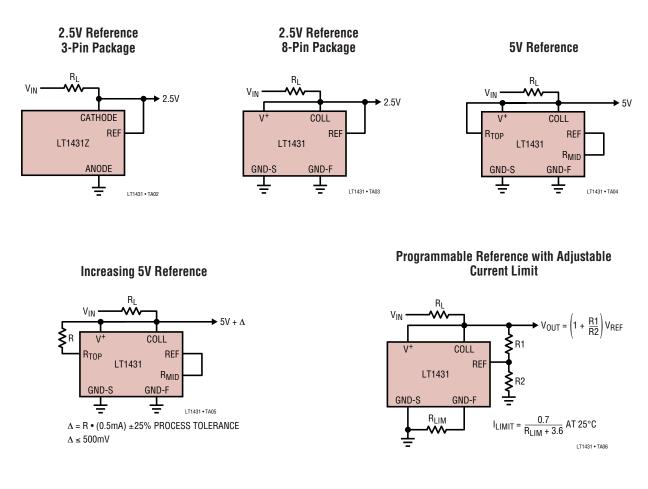

The LT<sup>®</sup>1431 is an adjustable shunt voltage regulator with 100mA sink capability, 0.4% initial reference voltage tolerance and 0.3% typical temperature stability. On-chip divider resistors allow the LT1431 to be configured as a 5V shunt regulator, with 1% initial voltage tolerance and requiring no additional external components. By adding two external resistors, the output voltage may be set to any value between 2.5V and 36V. The nominal internal current limit of 100mA may be decreased by including one external resistor.

A simplified 3-pin version, the LT1431CZ/LT1431IZ, is available for applications as an adjustable reference and is pin compatible with the TL431.

LTC and LT are registered trademarks of Linear Technology Corporation.

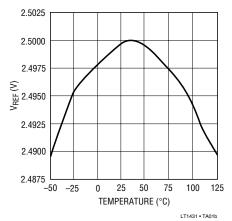

#### **V<sub>REF</sub> vs Temperature**

Downloaded from Arrow.com.

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| V <sup>+</sup> , V <sub>COLLECTOR</sub>                                    |               |

|----------------------------------------------------------------------------|---------------|

| V <sub>COMP</sub> , R <sub>TOP</sub> , R <sub>MID</sub> , V <sub>RFF</sub> |               |

| GND-F to GND-S                                                             | 0.7V          |

| Ambient Temperature Range                                                  |               |

| LT1431M (OBSOLETE)                                                         | 55°C to 125°C |

| LT1431I                                                                    | 40°C to 85°C  |

| LT1431C                                                                    | 0°C TO 70°C   |

JunctionTemperature Range

| LT1431M (OBSOLETE)                   | -55°C to 150°C |

|--------------------------------------|----------------|

| LT14311                              | -40°C to 100°C |

| LT1431C                              | 0°C to 100°C   |

| Storage Temperature Range            | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) | 300°C          |

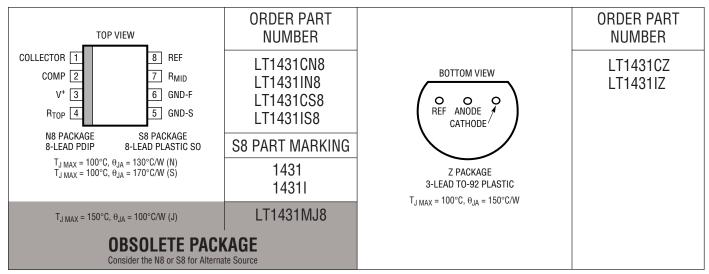

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. I<sub>K</sub> = 10mA unless otherwise specified (Note 2)

| SYMBOL                                         | PARAMETER                                               | CONDITIONS                                                            |   | LT1431<br>Min typ    | M/I<br>Max     | LT143<br>Min Typ     | 1C<br>Max      | UNITS    |

|------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|---|----------------------|----------------|----------------------|----------------|----------|

| V <sub>REF</sub>                               | Reference Voltage                                       | $V_{KA} = 5V, I_K = 2mA, (Note 3)$                                    | • | 2.490 2.500<br>2.465 | 2.510<br>2.535 | 2.490 2.500<br>2.480 | 2.510<br>2.520 | V<br>V   |

| $\Delta V_{\text{REF}} / \Delta T$             | Reference Drift                                         | V <sub>KA</sub> = 5V, I <sub>K</sub> = 2mA                            | ٠ | 50                   |                | 30                   |                | ppm/°C   |

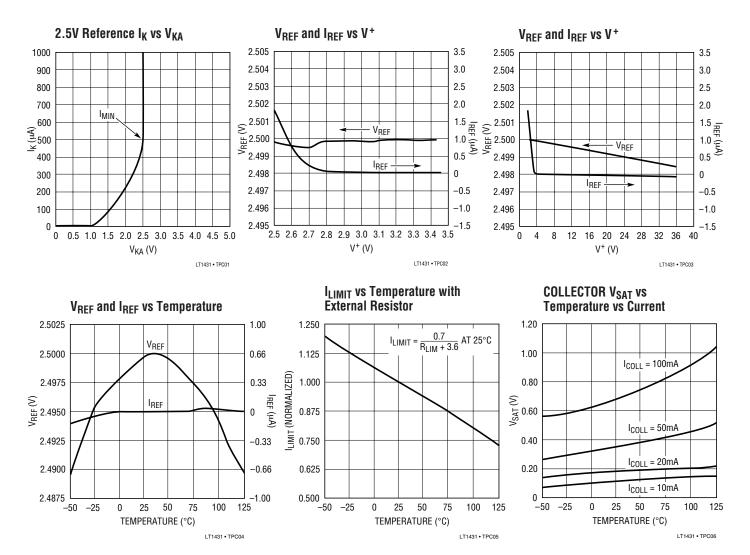

| $\Delta V_{\text{REF}} / \Delta V_{\text{KA}}$ | Voltage Ratio, Reference to<br>Cathode (Open-Loop Gain) | $I_{\rm K}$ = 2mA, $V_{\rm KA}$ = 3V to 36V                           | • | 0.2                  | 0.5            | 0.2                  | 0.5            | mV/V     |

| I <sub>REF</sub>                               | Reference Input Current                                 | V <sub>KA</sub> = 5V, T <sub>A</sub> = 25°C                           | • | 0.2                  | 1.0<br>1.5     | 0.2                  | 1.0<br>1.2     | μΑ<br>μΑ |

| I <sub>MIN</sub>                               | Minimum Operating Current                               | V <sub>KA</sub> = V <sub>REF</sub> to 36V                             |   | 0.6                  | 1.0            | 0.6                  | 1.0            | mA       |

| I <sub>OFF</sub>                               | Off-State Cathode Current                               | V <sub>KA</sub> = 36V, V <sub>REF</sub> = 0V                          | • |                      | 1<br>15        |                      | 1<br>2         | μΑ<br>μΑ |

| I <sub>LEAK</sub>                              | Off-State Collector Leakage Current                     | V <sub>COLL</sub> = 36V, V <sup>+</sup> = 5V, V <sub>REF</sub> = 2.4V | • |                      | 1<br>5         |                      | 1<br>2         | μΑ<br>μΑ |

| Z <sub>KA</sub>                                | Dynamic Impedance                                       | $V_{KA} = V_{REF}$ , $I_K = 1$ mA to 100mA, f $\leq$ 1kHz             |   |                      | 0.2            |                      | 0.2            | Ω        |

| I <sub>LIM</sub>                               | Collector Current Limit                                 | V <sub>KA</sub> = V <sub>REF</sub> + 50mV                             |   | 80                   | 360            | 100                  | 260            | mA       |

|                                                | 5V Reference Output                                     | Internal Divider Used, I <sub>K</sub> = 2mA                           |   | 4.950 5.000          | 5.050          | 4.950 5.000          | 5.050          | V        |

2 Downloaded from Arrow.com.

1413fc

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:**  $V_{KA}$  is the cathode voltage of the LT1431CZ/IZ and corresponds to V<sup>+</sup> of the LT1431CN8/IN8/CS8/IS8.  $I_K$  is the cathode current of the LT1431CZ/IZ and corresponds to I(V<sup>+</sup>) + I<sub>COLLECTOR</sub> of the LT1431CN8/IN8/CS8/IS8.

**Note 3:** The LT1431 has bias current cancellation which is effective only for  $V_{KA} \ge 3V$ . A slight ( $\approx 2mV$ ) shift in reference voltage occurs when  $V_{KA}$  drops below 3V. For this reason, these tests are not performed at  $V_{KA} = V_{REF}$ .

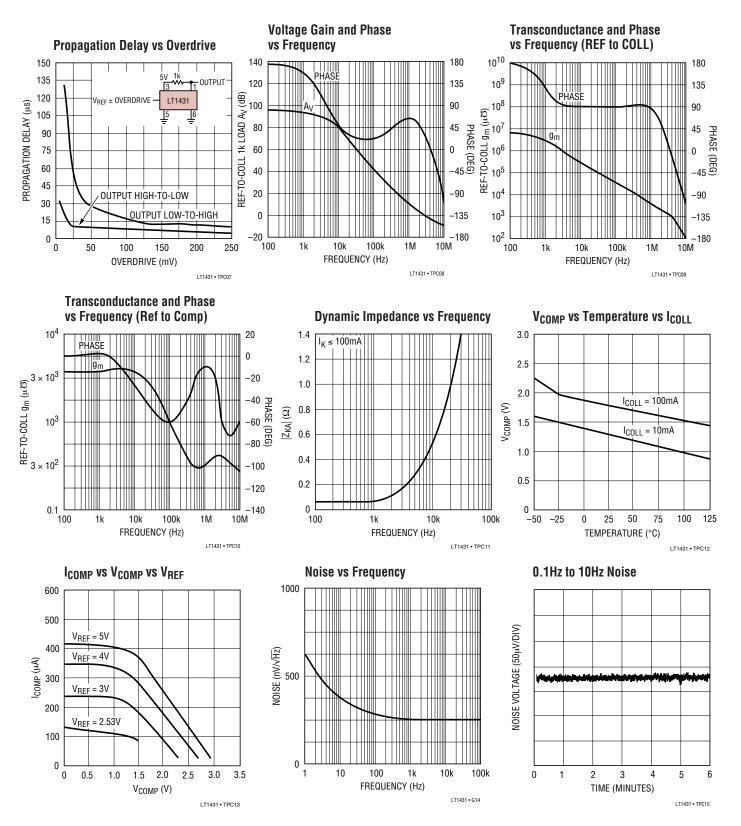

### TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS**

1413fc

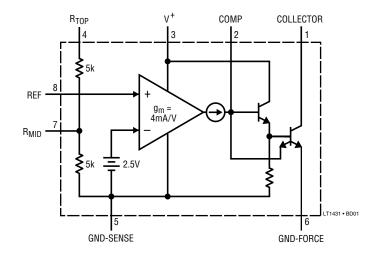

### PIN FUNCTIONS

**COLL (Pin 1):** Open collector of the output transistor. The maximum pin voltage is 36V. The saturation voltage at 100mA is approximately 1V.

**COMP (Pin 2):** Base of the driver for the output transistor. This pin allows additional compensation for complex feedback systems and shutdown of the regulator. It must be left open if unused.

**V<sup>+</sup> (Pin 3):** Bias voltage for the entire shunt regulator. The maximum input voltage is 36V and the minimum to operate is equal to  $V_{REF}$  (2.5V). The quiescent current is typically 0.6mA.

**R<sub>TOP</sub> (Pin 4):** Top of the on-chip 5k-5k resistive divider that guarantees 1% accuracy of operation as a 5V shunt regulator with no external trim. The pin is tied to COLL for self-contained 5V operation. It may be left open if unused. See note on parasitic diodes below.

**GND-S (Pin 5):** Ground reference for the on-chip resistive divider and shunt regulator circuitry except for the output transistor. This pin allows external current limit of the output transistor with one resistor between GND-F (force) and GND-S (sense).

**GND-F (Pin 6):** Emitter of the output transistor and substrate connection for the die.

$R_{MID}$  (Pin 7): Middle of the on-chip resistive divider string between  $R_{TOP}$  and GND-S. The pin is tied to REF for self-contained 5V operation. It may be left open if unused.

**REF (Pin 8):** Control pin of the shunt regulator with a 2.5V threshold. If  $V^+ > 3V$ , input bias current cancellation reduces  $I_B$  to 0.2µA typical.

COMP,  $R_{TOP}$ ,  $R_{MID}$ , and REF have static discharge protection circuits that must not be activated on a continuous basis. Therefore, the absolute maximum DC voltage on these pins is 6V, well beyond the normal operating conditions.

As with all bipolar ICs, the LT1431 contains parasitic diodes which must not be forward biased or else anomalous behavior will result. Pin conditions to be avoided are  $R_{TOP}$  below  $R_{MID}$  in voltage and any pin below GND-F in voltage (except for GND-S).

The following pin definitions apply to the Z package.

**CATHODE:** Corresponds to COLL and V<sup>+</sup> tied together.

**ANODE:** Corresponds to GND-S and GND-F tied together.

REF: Corresponds to REF.

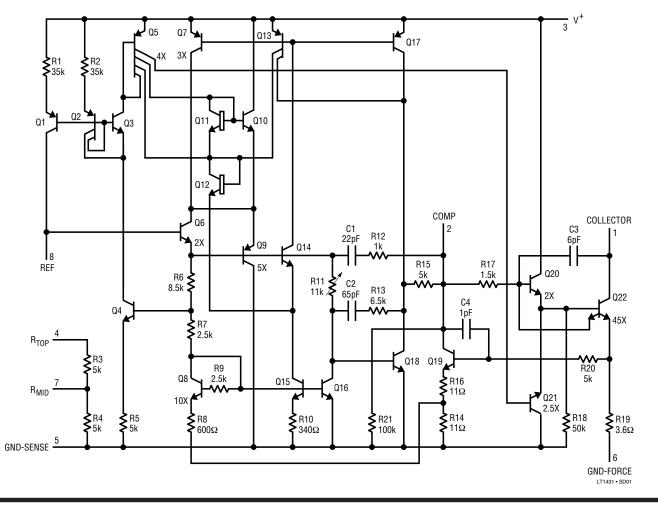

### **BLOCK DIAGRAM**

# **APPLICATIONS INFORMATION**

#### **Frequency Compensation**

As a shunt regulator, the LT1431 is stable for all capacitive loads on the COLL pin. Capacitive loading between  $0.01\mu$ F and  $18\mu$ F causes reduced phase margin with some ringing under transient conditions. Output capacitors should not be used arbitrarily because output noise is not necessarily reduced.

Excess capacitance on the REF pin can introduce enough phase shift to induce oscillation when configured as a reference >2.5V. This can be compensated with capacitance between COLL and REF (phase lead). More complicated feedback loops may require shaping of the frequency response of the LT1431 with dominant pole or pole-zero compensation. This can be accomplished with a capacitor or series resistor and capacitor between COLL and COMP.

The compensation schemes mentioned above use voltage feedback to stabilize the circuits. There must be voltage gain at the COLL pin for them to be effective, so the COLL pin must see a reasonable AC impedance. Capacitive loading of the COLL pin reduces the AC impedance, voltage gain, and frequency response, thereby decreasing the effectiveness of the compensation schemes, but also decreasing their necessity.

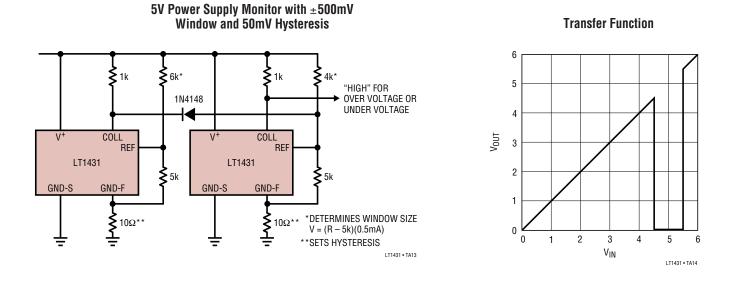

## TYPICAL APPLICATIONS

6 Downloaded from Arrow.com.

### **TYPICAL APPLICATIONS**

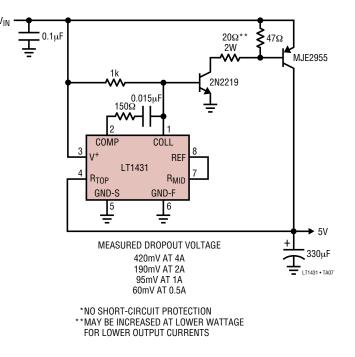

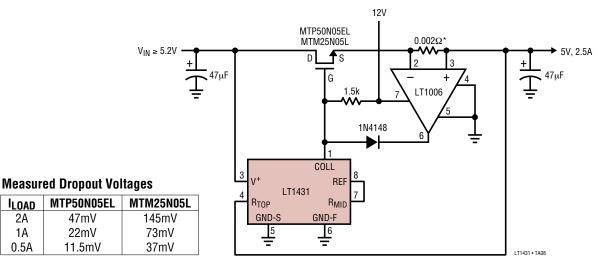

**PNP Low Dropout 5V Regulator\***

#### FET Low Dropout 5V Regulator with Current Limit

#### \*1.5" #23 SOLID COPPER WIRE

${\sim}0.002\Omega \rightarrow {\rm 3A~LIMIT}$

ILOAD

2A

1A

0.5A

47mV

22mV

11.5mV

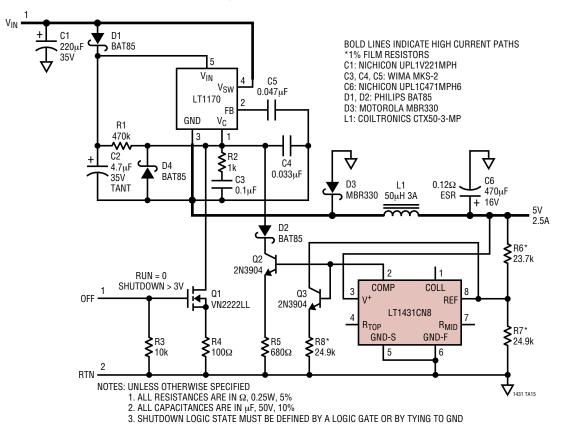

### TYPICAL APPLICATIONS

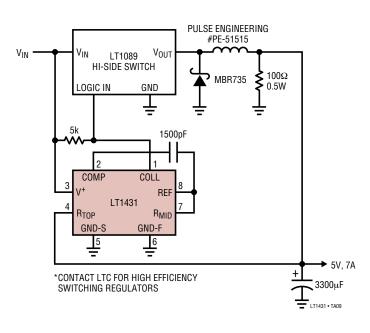

12V to 5V Buck Converter with Foldback Current Limit\*

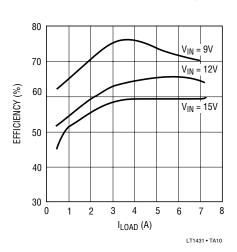

#### **Buck Converter Efficiency**

Fully Loaded Output Ripple vs Filtering

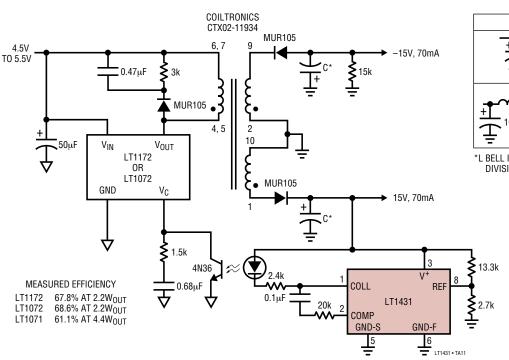

Isolated 5V to  $\pm$ 15V Flyback Converter

C\*

LT1172

LT1072

++

210μF

30mV<sub>P-P</sub>

40mV<sub>P-P</sub>

++

100μF

6mV<sub>P-P</sub>

8mV<sub>P-P</sub>

\*L BELL INDUSTRIES J.W. MILLER DIVISION 9310-36 10μH, 450mA

LT1431+TA12

B Downloaded from Arrow.com.

1413fc

### **TYPICAL APPLICATIONS**

High Efficiency Buck Converter E = 85% to 89%

### SCHEMATIC DIAGRAM

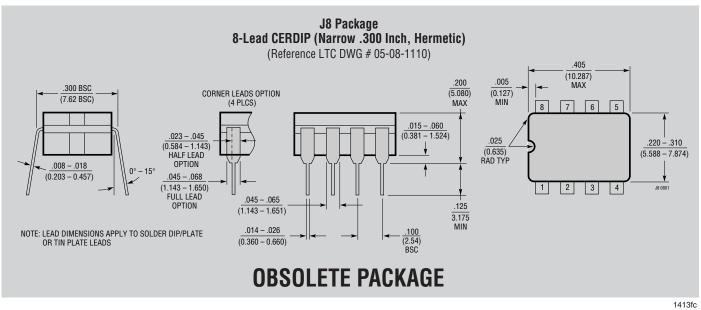

# PACKAGE DESCRIPTION

5

4

N8 1002

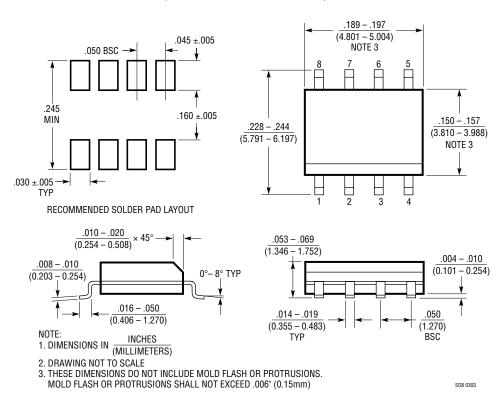

### PACKAGE DESCRIPTION

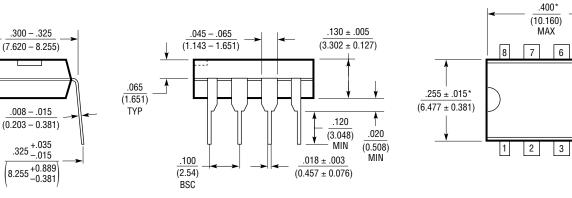

**N8 Package** 8-Lead PDIP (Narrow .300 Inch) (Reference LTC DWG # 05-08-1510)

NOTE:

NOTE: 1. DIMENSIONS ARE <u>INCHES</u> \*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of circuits as described herein will not infringe on existing patent rights.

### PACKAGE DESCRIPTION

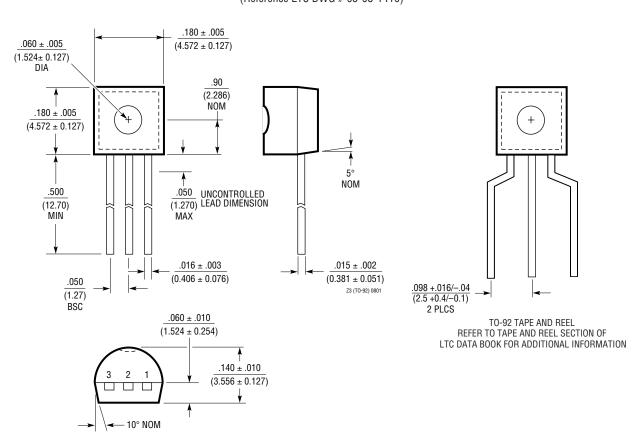

Z Package 3-Lead Plastic TO-92 (Similar to TO-226) (Reference LTC DWG # 05-08-1410)

# **RELATED PARTS**

| PART NUMBER           | DESCRIPTION                                                 | COMMENTS                                                              |

|-----------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|

| LTC <sup>®</sup> 3722 | Synchronous Full-Bridge Controller                          | Zero Voltage Switching, Adjustable 2V <sub>S</sub> Timing             |

| LTC3723               | Synchronous Push-Pull PWM Controller                        | 1.5A Sink, 1A Source Output Drivers, Adjustable Dead Time             |

| LTC3803               | SOT-23 Flyback Controller                                   | Adjustable Slope Compensation, 200kHz Operation                       |

| LTC3806               | Synchronous Flyback Controller                              | Excellent Cross Regulation, High Efficiency                           |

| LTC3900/LTC3901       | Synchronous Rectifiers for Forward and Push-Pull Converters | Programmable Time Out, Reverse Inductor Current Sense                 |

| LT4430                | Optocoupler Driver in SOT-23                                | Overshoot Control, 600mV Reference, High Bandwidth Error<br>Amplifier |