# 30 A Isolated SiC Gate Driver with Slew Rate Control and SPI

**Preliminary Technical Data**

**ADuM4177**

#### **FEATURES**

30 A peak short circuit (typ) drive output

20 A peak drive current (typ) in typical application

Output power device resistance < 0.4Ω

1500 V peak and dc working voltage to DIN V VDE 0884-11

Slew rate control via SPI interface

Low propagation delay (140 ns typ)

60 ns Minimum Pulse Width

Bi-polar and Uni-polar secondary side supply capability

VDD1: 4.4 V to 7 V VDD2-GND2: 12 V to 24 V GND2-VSS2: 0 V to -5.5 V Protection Features:

DESAT – SiC drain sense, 7 V (typ) threshold Programmable internal DESAT blanking time ASC pin, secondary side driver turn-on control, 8 V (typ) threshold External Miller Clamp Soft-shutdown, 1 µs capability, adjustable with external

resistor

#### **GENERAL DESCRIPTION**

The ADuM4177 is an advanced isolated gate driver that provides 5 kVrms isolation employing Analog Devices, Inc. *i*Couper\* technology. The ADuM4177 provides 8.3 mm creepage in a 28-pin wide body SOIC package. The devices are suitable for applications that require insulation against working voltages of 1060 V rms and 1500 V dc for the lifetime of the device. Combining high speed CMOS and monolithic transformer technology, these isolated gate drivers provide outstanding performance characteristics suitable for driving the demanding needs of high performance Silicon Carbide (SiC) switches. SPI communication allows for user programmable operating modes and fault read back.

The ADuM4177 operates with an input voltage range from 4.4 to 7 V. The output voltages can operate with bipolar gate drive of 12 to 24 V positive and -5.5 to -3.25 V for the negative rail. Multiple programmable undervoltage lockout (UVLO) levels can be obtained through SPI communication with the gate driver. In comparison to gate drivers employing high voltage level translation methodologies, the ADuM4177 offers the

GND2-VSS2 OVP and UVP

Isolated Fault differentiation through fault reporting pins

SiC Switch Isolated Temperature Sense

1 kHz PWM, and SPI register read

VDD2-VSS2 OVP and programmable VDD2-VSS2 UVP

Temperature sense diode stack

Compatible with NTC using external resistor network

SPI Interface

Non-volatile EEPROM registers for configurability Fault reporting information

Operating junction temperature range (-40 to 150°C)

#### **APPLICATIONS**

Switching power supplies SiC gate drivers Industrial inverters Power Factor Correctors

benefit of true, galvanic isolation between the input and the output.

The ADuM4177 includes many advanced protection features such as the drain monitoring desaturation detection, an active short circuit (ASC) operation, external temperature sensing, and both over voltage protection (OVP) and undervoltage protection (UVP).

Adjustable slew rate control is available to allow for faster edge transitions and higher efficiency when the system operating point can accommodate it. An external miller clamp allows for strong pull-down to prevent unintended Miller injection induced turn on. The ADuM4177 can operate in a wide range of junction temperatures, from -40 to 150°C.

As a result, the ADuM4177 provides reliable control over the switching characteristics of SiC switch configurations over a wide range of switching voltages.

Rev. PrA

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice.

No license is granted by implication or otherwise under any patent or patent rights of Analog

Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2020 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **Preliminary Technical Data**

# **TABLE OF CONTENTS**

| reatures                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| General Description                          | 1  |

| Functional Block Diagram                     | 3  |

| Specifications                               | 4  |

| Insulation and Safety-Related Specifications | 8  |

| Recommended Operating Conditions             | 8  |

| Absolute Maximum Ratings                     | 9  |

| Thermal Resistance                           | 9  |

| ESD Caution                                  | 9  |

| Pin Configuration and Function Descriptions  | 10 |

| Typical Performance Characteristics          | 11 |

| Theory of Operation                          | 12 |

| Applications                                 | 13 |

| PCD Layout                           | . 13           |

|--------------------------------------|----------------|

| Power Supplies                       | . 13           |

| Propagation Delay Related Parameters | . 13           |

| SPI Interface                        | . 14           |

| Temperature Sense                    | . 16           |

| Gate Drive                           | . 19           |

| Protection Features                  | . 19           |

| Faults                               | . 22           |

| BIST                                 | . 24           |

| Power Dissipation                    | . 25           |

| SPI Registers                        | . 26           |

| Typical Application Circuit          | . 31           |

| Outline Dimensions                   | . 32           |

|                                      | Power Supplies |

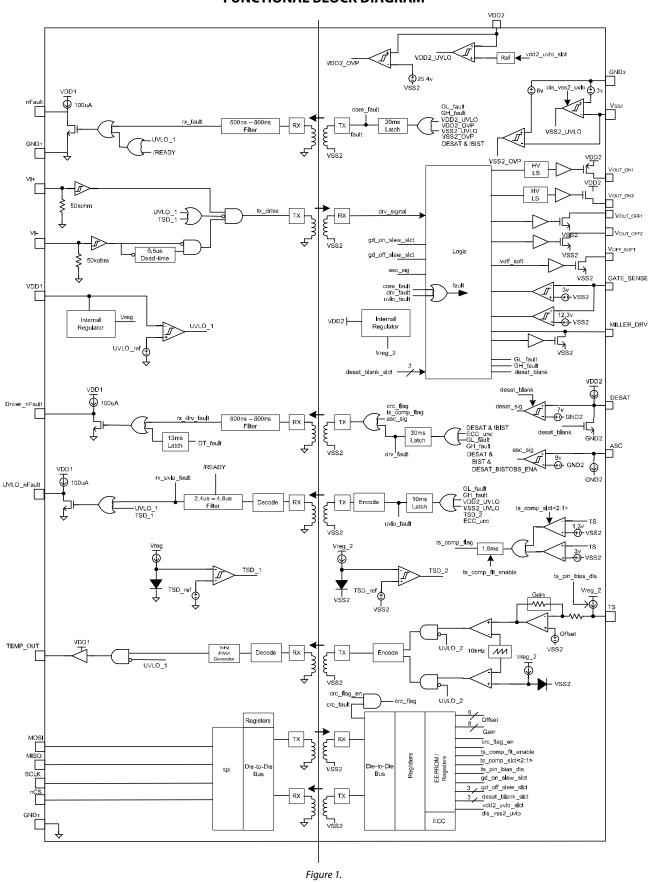

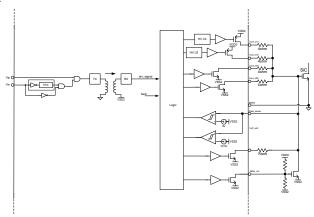

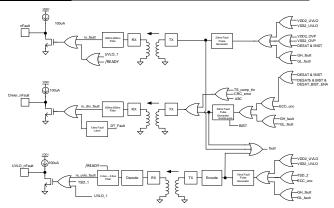

#### **FUNCTIONAL BLOCK DIAGRAM**

# **SPECIFICATIONS**

Low-side voltages referenced to GND<sub>1</sub> and high-side voltages referenced to GND<sub>2</sub> unless otherwise noted.  $V_{\rm DD1} = 4.4$  to 7 V,  $V_{\rm DD2} = 12$  to 24 V,  $V_{SS2} = -5.5$  to -3.25 V,  $T_{\rm J} = -40$ °C to +150°C, unless otherwise noted. All minimum and maximum specifications apply over the entire recommended operating junction temperature range, unless otherwise noted. All typical specifications are at  $T_{\rm J} = 25$ °C,  $V_{\rm DD1} = 5$  V, and  $V_{\rm DD2} = 18$  V, unless otherwise noted.

Table 1.

| Parameter                                     | Symbol                                       | Min        | Тур         | Max         | Unit | Test Conditions/Comments                                                                              |

|-----------------------------------------------|----------------------------------------------|------------|-------------|-------------|------|-------------------------------------------------------------------------------------------------------|

| DC Specifications                             |                                              |            |             |             |      |                                                                                                       |

| Primary Side Power Supply                     |                                              |            |             |             |      |                                                                                                       |

| V <sub>DD1</sub> Input Voltage                | $V_{DD1}$                                    | 4.4        |             | 7           | V    |                                                                                                       |

| V <sub>DD1</sub> Input Current, Quiescent     | I <sub>DD1(Q)</sub>                          | TBD        | TBD         | 10          | mA   | VDD1 = 5 V, VI+ = 0 V, VI+ = 5 V, CS<br>= 5 V                                                         |

| V <sub>DD1</sub> Input Current, SPI active    | I <sub>DD1</sub> (SPI)                       | TBD        | TBD         | 15          | mA   | VDD1 = 5 V, VI+ = 0 V, VI+ = 5 V, CS<br>= 0 V                                                         |

| Secondary Side Power Supply                   |                                              |            |             |             |      |                                                                                                       |

| V <sub>DD2</sub> Input Voltage                | $V_{DD2}$                                    | 12         |             | 24          | V    |                                                                                                       |

| Input Current, Quiescent for V <sub>DD2</sub> | I <sub>DD2(Q)</sub>                          | TBD        | 15          | TBD         | mA   | $V_{DD2} = 25 \text{ V}, V_{SS2} = -5 \text{ V}, VI+ = 0 \text{ V},$<br>$\overline{CS} = 5 \text{ V}$ |

| V <sub>SS2</sub> Input Voltage                | V <sub>SS2(Q)</sub>                          | -5.5       |             | -3.25       | V    | V <sub>DD2</sub> = 18 V                                                                               |

| UVLO Positive Going Threshold                 |                                              |            |             |             |      |                                                                                                       |

| _                                             | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \        | TDD        | 2.0         | TDD         | .,   |                                                                                                       |

| $V_{DD1}$ $V_{SS2}$                           | V <sub>VDD1UV+</sub><br>V <sub>VSS2UV+</sub> | TBD<br>TBD | 3.8<br>-3.0 | TBD<br>TBD  | V    |                                                                                                       |

|                                               | ***                                          |            |             |             |      | VDD2 11VLQ \$1.CT - '000'                                                                             |

| $V_{DD2}$ (referenced to $V_{SS2}$ )          | V <sub>VDD2UV+0</sub>                        | 13.76      | 13.96       | 14.16       | V    | VDD2_UVLO_SLCT = '000'                                                                                |

|                                               | V <sub>VDD2UV+1</sub>                        | TBD        | 15.95       | TBD         | V    | VDD2_UVLO_SLCT = '001'                                                                                |

|                                               | V <sub>VDD2UV+2</sub>                        | TBD        | 16.93       | TBD         | V    | VDD2_UVLO_SLCT = '010'                                                                                |

|                                               | V <sub>VDD2UV+3</sub>                        | TBD        | 17.92       | TBD         | V    | VDD2_UVLO_SLCT = '011'                                                                                |

| (1.6.1)                                       | V <sub>VDD2UV+4</sub>                        | 18.58      | 18.88       | 19.18       | V    | VDD2_UVLO_SLCT = '100'                                                                                |

| (default)                                     | V <sub>VDD2UV+5</sub>                        | TBD        | 20.87       | TBD         | V    | VDD2_UVLO_SLCT = '101'                                                                                |

|                                               | V <sub>VDD2UV+6</sub>                        | TBD        | 21.85       | TBD         | V    | VDD2_UVLO_SLCT = '110'                                                                                |

| N .: C : TI I II                              | V <sub>VDD2UV+7</sub>                        | 22.44      | 22.84       | 23.14       | V    | VDD2_UVLO_SLCT = '111'                                                                                |

| Negative Going Threshold                      |                                              | TDD        | 2.5         | <b>T</b> DD | .,   |                                                                                                       |

| V <sub>DD1</sub>                              | V <sub>VDD1UV</sub> -                        | TBD        | 3.5         | TBD         | V    |                                                                                                       |

| V <sub>SS2</sub>                              | V <sub>VSS2UV</sub> -                        | TBD        | -2.55       | TBD         | V    |                                                                                                       |

| $V_{DD2}$ (referenced to $V_{SS2}$ )          | V <sub>VDD2UV</sub> -0                       | 13.16      | 13.36       | 13.56       | V    | VDD2_UVLO_SLCT = '000'                                                                                |

|                                               | V <sub>VDD2UV-1</sub>                        | TBD        | TBD         | TBD         | V    | VDD2_UVLO_SLCT = '001'                                                                                |

|                                               | V <sub>VDD2UV-2</sub>                        | TBD        | TBD         | TBD         | V    | VDD2_UVLO_SLCT = '010'                                                                                |

|                                               | V <sub>VDD2UV-3</sub>                        | TBD        | TBD         | TBD         | V    | VDD2_UVLO_SLCT = '011'                                                                                |

|                                               | V <sub>VDD2UV-4</sub>                        | 17.76      | 18.06       | 18.36       | V    | VDD2_UVLO_SLCT = '100'                                                                                |

| (default)                                     | $V_{VDD2UV-5}$                               | TBD        | TBD         | TBD         | V    | VDD2_UVLO_SLCT = '101'                                                                                |

|                                               | $V_{VDD2UV-6}$                               | TBD        | TBD         | TBD         | V    | VDD2_UVLO_SLCT = '110'                                                                                |

|                                               | $V_{VDD2UV-7}$                               | 21.41      | 21.81       | 22.11       | V    | VDD2_UVLO_SLCT = '111'                                                                                |

| Hysteresis                                    |                                              |            |             |             |      |                                                                                                       |

| $V_{DD1}$                                     | V <sub>VDD1UVH</sub>                         |            | 0.3         |             | V    |                                                                                                       |

| $V_{SS2}$                                     | $V_{VSS2UVH}$                                |            | 0.45        |             | V    |                                                                                                       |

| $V_{DD2}$                                     | V <sub>VDD2UVH0</sub>                        |            | 0.6         |             | V    | VDD2_UVLO_SLCT = '000'                                                                                |

|                                               | $V_{VDD2UVH1}$                               |            | TBD         |             | V    | VDD2_UVLO_SLCT = '001'                                                                                |

|                                               | $V_{\text{VDD2UVH2}}$                        |            | TBD         |             | V    | VDD2_UVLO_SLCT = '010'                                                                                |

|                                               | $V_{VDD2UVH3}$                               |            | TBD         |             | V    | VDD2_UVLO_SLCT = '011'                                                                                |

|                                               | $V_{VDD2UVH4}$                               |            | 0.82        |             | V    | VDD2_UVLO_SLCT = '100'                                                                                |

| Parameter                                    | Symbol                  | Min  | Тур  | Max  | Unit | Test Conditions/Comments         |

|----------------------------------------------|-------------------------|------|------|------|------|----------------------------------|

| (default)                                    | V <sub>VDD2UVH5</sub>   |      | TBD  |      | V    | VDD2_UVLO_SLCT = '101'           |

|                                              | V <sub>VDD2UVH6</sub>   |      | TBD  |      | V    | VDD2_UVLO_SLCT = '110'           |

|                                              | V <sub>VDD2UVH7</sub>   |      | 1.03 |      | V    | VDD2_UVLO_SLCT = '111'           |

| OVP                                          |                         |      |      |      |      |                                  |

| Positive Going Threshold                     |                         |      |      |      |      |                                  |

| $V_{DD2}$                                    | $V_{VDD2OV+}$           | TBD  | 25.4 | TBD  | V    | Referenced to V <sub>SS2</sub> . |

| $V_{SS2}$                                    | V <sub>VSS2OV+</sub>    | TBD  | -6.0 | TBD  | V    | Referenced to GND <sub>2</sub> . |

| Negative Going Threshold                     |                         |      |      |      |      |                                  |

| $V_{DD2}$                                    | $V_{VDD2OV-}$           | TBD  | 24.4 | TBD  | V    | Referenced to V <sub>SS2</sub> . |

| $V_{SS2}$                                    | $V_{VSS2OV-}$           | TBD  | -5.6 | TBD  | V    | Referenced to GND <sub>2</sub> . |

| Hysteresis                                   |                         |      |      |      |      |                                  |

| $V_{DD2}$                                    | V <sub>VDD2OVH</sub>    |      | 1    |      | V    | Referenced to V <sub>SS2</sub> . |

| $V_{SS2}$                                    | V <sub>VSS2OVH</sub>    |      | 0.4  |      | V    | Referenced to GND <sub>2</sub> . |

| PWM Logic Inputs (VI+, VI-, SCLK, nCS, MOSI) |                         |      |      |      |      |                                  |

| VI+                                          |                         |      |      |      |      |                                  |

| Rising Threshold                             | $V_{VI+\_th\_R}$        | 2.7  | 2.5  |      | V    |                                  |

| Falling Threshold                            | V <sub>VI+_th_F</sub>   |      | 1.5  | 1.3  | V    |                                  |

| Hysteresis                                   | $V_{VI+\_th\_H}$        |      | 1.0  |      |      |                                  |

| Internal Pull-down Resistance                | R <sub>VI+</sub>        |      | 50   |      | kΩ   |                                  |

| VI-                                          |                         |      |      |      |      |                                  |

| Rising Threshold                             | $V_{\text{VI-\_th}\_R}$ | 2.7  | 2.5  |      | V    |                                  |

| Falling Threshold                            | $V_{VIth_F}$            |      | 1.5  | 1.3  | V    |                                  |

| Hysteresis                                   | V <sub>VIth_H</sub>     |      | 1.0  |      |      |                                  |

| Internal Pull-down Resistance                | R <sub>VI-</sub>        |      | 50   |      | kΩ   |                                  |

| SCLK                                         |                         |      |      |      |      |                                  |

| Rising Threshold                             | V <sub>SCLK th R</sub>  | 2.7  | 2.5  |      | V    |                                  |

| Falling Threshold                            | V <sub>SCLK_th_F</sub>  |      | 1.5  | 1.3  | V    |                                  |

| Hysteresis                                   | V <sub>SCLK_th_H</sub>  |      | 1.0  |      |      |                                  |

| nCS                                          |                         |      |      |      |      |                                  |

| Rising Threshold                             | V <sub>nCS_th_R</sub>   | 2.7  | 2.5  |      | V    |                                  |

| Falling Threshold                            | $V_{nCS\_th\_F}$        |      | 1.5  | 1.3  | V    |                                  |

| Hysteresis                                   | $V_{nCS\_th\_H}$        |      | 1.0  |      |      |                                  |

| MOSI                                         |                         |      |      |      |      |                                  |

| Rising Threshold                             | V <sub>MOSI_th_R</sub>  | 2.7  | 2.5  |      | V    |                                  |

| Falling Threshold                            | V <sub>MOSI th F</sub>  |      | 1.5  | 1.3  | V    |                                  |

| Hysteresis                                   | V <sub>MOSI_th_H</sub>  |      | 1.0  |      |      |                                  |

| Thermal Shutdown (TSD)                       |                         |      |      |      |      |                                  |

| Primary Side TSD                             |                         |      |      |      |      |                                  |

| Positive Edge                                | TSD <sub>POS1</sub>     | 155  |      |      | °C   |                                  |

| Negative Edge                                | TSD <sub>NEG1</sub>     | 135  |      |      | °C   |                                  |

| Secondary Side TSD                           |                         |      |      |      |      |                                  |

| Positive Edge                                | TSD <sub>POS2</sub>     | 155  |      |      | °C   |                                  |

| Negative Edge                                | TSD <sub>NEG2</sub>     | 135  |      |      | °C   |                                  |

| Isolated Temperature Sense                   | -                       |      |      |      |      |                                  |

| Temperature Sense                            |                         |      |      |      |      |                                  |

| TS Pin Bias Current                          | I <sub>TS</sub>         | TBD  | 0.2  | TBD  | mA   |                                  |

| Operating Frequency                          | TS <sub>PWM</sub>       | TBD  | 10   | TBD  | kHz  |                                  |

| Sense Filter Time                            | t <sub>FILT</sub>       |      | TBD  |      | ms   |                                  |

| Maximum TS Pin Voltage                       | TS <sub>MAX</sub>       |      |      | 5    | V    |                                  |

| TS Comparator Thresholds                     |                         |      |      | -    |      |                                  |

| Positive Going Threshold                     |                         |      |      |      |      |                                  |

| Comparator 1                                 | TS <sub>COMP_1_R</sub>  | 1.32 | 1.38 | 1.44 | V    | TS_COMP_SLCT<2:1> = '01'         |

| Comparator 2                                 | TS <sub>COMP_2_R</sub>  | 2.97 | 3.00 | 3.03 | V    | TS_COMP_SLCT<2:1> = '10'         |

| Parameter                                             | Symbol                                | Min  | Тур     | Max         | Unit    | Test Conditions/Comments       |

|-------------------------------------------------------|---------------------------------------|------|---------|-------------|---------|--------------------------------|

| Negative Going Threshold                              |                                       |      | •       |             |         |                                |

| Comparator 1                                          | TS <sub>COMP 1 F</sub>                | 1.26 | 1.32    | 1.38        | V       | TS_COMP_SLCT<2:1> = '01'       |

| Comparator 2                                          | TS <sub>COMP_2_F</sub>                | 2.91 | 2.94    | 2.97        | V       | TS_COMP_SLCT<2:1> = '10'       |

| Hysteresis                                            |                                       |      |         |             |         |                                |

| Comparator 1                                          | TS <sub>COMP_1_H</sub>                |      | 0.06    |             | V       | TS_COMP_SLCT<2:1> = '01'       |

| Comparator 2                                          | TS <sub>COMP_2_H</sub>                |      | 0.06    |             | V       | TS_COMP_SLCT<2:1> = '10'       |

| Filter Time                                           | TS <sub>COMP_FILT</sub>               |      | 1.64    |             | ms      | TS_COMP_FILT_EN = '10'         |

| TEMP_OUT                                              |                                       |      |         |             |         |                                |

| _<br>TEMP_OUT Duty Cycle                              | TOD                                   |      | 12      |             | %       | $TS - V_{SS2} = 3.7 \text{ V}$ |

|                                                       |                                       |      | 88      |             | %       | $TS - V_{SS2} = 1.3 \text{ V}$ |

| TEMP_OUT Maximum Duty Cycle                           | TO <sub>DUTY_MAX</sub>                |      | 98      |             | %       | 552                            |

| TEMP_OUT Minimum Duty Cycle                           | TO <sub>DUTY_MIN</sub>                |      | 2.5     |             | %       |                                |

| TEMP_OUT PMOS R <sub>DSON</sub>                       | R <sub>DSON</sub> TO P                |      | 60      | TBD         | Ω       |                                |

| TEMP_OUT NMOS RDSON                                   | R <sub>DSON</sub> TO N                |      | 10      | TBD         | Ω       |                                |

| PWM Output Frequency                                  | F <sub>PWM</sub>                      | TBD  | 1       | TBD         | kHz     |                                |

| Switching Specifications                              | 1 FVVIVI                              | 100  | '       | 100         | KIIZ    |                                |

| Turn on/Turn off R <sub>DSON</sub>                    |                                       |      |         |             |         |                                |

| Vout on Roson                                         | R <sub>DSON ON1</sub>                 |      | TBD     | 0.8         | Ω       | GD_ON_SLEW_SLCT = '0'          |

| VOUT_ONT ROSON  VOUT_ON2 ROSON                        | RDSON_ON2                             |      | TBD     | 0.8         | Ω       | GD_ON_SLEW_SLCT = '0'          |

| VOUT_ONZ ROSON  VOUT_OFF1 ROSON                       | R <sub>DSON_OFF1</sub>                |      | TBD     | 0.8         | Ω       | GD_ON_SLEW_SLCT = '0'          |

| VOUT_OFF2 RDSON                                       | RDSON_OFF1                            |      | TBD     | 0.8         | Ω       | GD_ON_SLEW_SLCT = '0'          |

| VOOT_OFF2 NDSON<br>VOFF_SOFT RDSON                    | _ · · · · · <del>-</del> ·            |      | TBD     | 0.6         | Ω       | db_on_setw_set = 0             |

| WOFF_SOFT INDSON Miller Clamp                         | R <sub>DSON_SOFT</sub>                |      | טטו     | 0.0         | 12      |                                |

|                                                       | D                                     |      | TBD     |             | Ω       | Tested at TBD mA               |

| MILLER_DRV Rdson                                      | R <sub>DSON_M1</sub>                  |      |         |             |         | rested at TBD IIIA             |

| MILLER_DRVPull-up Current Miller Gate Sense Threshold | I <sub>MC_PU</sub>                    | TBD  | 10<br>3 | TBD         | μA<br>V | Referenced to Vss2             |

|                                                       |                                       | עפו  |         | טסו         | V       | Referenced to VSS2             |

| Miller Gate Sense Hysteresis                          | V <sub>th_hyst</sub>                  |      | 0.5     | TDD         |         | <del></del>                    |

| Propagation Delay                                     | <b>t</b> PROP                         | TDD  | 140     | TBD         | ns      | No gate load                   |

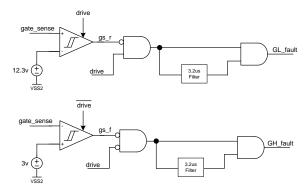

| Gate High Sense Threshold                             | GH <sub>th</sub>                      | TBD  | 12.3    | TBD         | V       | Referenced to V <sub>SS2</sub> |

| Gate High Sense Hysteresis                            | GH <sub>th_hyst</sub>                 | TDD  | TBD     | <b>T</b> DD | V       | Referenced to V <sub>SS2</sub> |

| Gate High Error Filter                                | T <sub>GH_FILT</sub>                  | TBD  | 3.2     | TBD         | μs      |                                |

| Gate Low Error Filter                                 | T <sub>GL_FILT</sub>                  | TBD  | 3.2     | TBD         | μs      |                                |

| Gate Low Sense Threshold                              | GH <sub>th</sub>                      | TBD  | TBD     | TBD         | V       | Referenced to V <sub>SS2</sub> |

| Gate Low Sense Hysteresis                             | GH <sub>th_hyst</sub>                 |      | TBD     |             | V       | Referenced to V <sub>SS2</sub> |

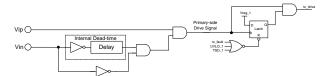

| Internal Deadtime                                     | T <sub>DT</sub>                       | TBD  | 0.5     | TBD         | μs      |                                |

| Common-Mode Transient Immunity                        | CM                                    |      |         |             | kV/μs   |                                |

| (CMTI) Static CMTI <sup>1</sup>                       |                                       | 150  |         |             |         | V 1500 V                       |

|                                                       |                                       | 150  |         |             |         | V <sub>CM</sub> = 1500 V       |

| Dynamic CMTI <sup>2</sup>                             |                                       | 150  |         |             |         | V <sub>CM</sub> = 1500 V       |

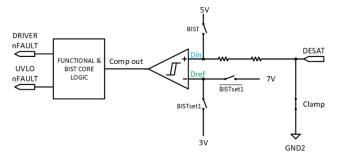

| Desaturation (DESAT) Detection                        | 1.                                    |      | 10      |             |         |                                |

| DESAT Pin Current                                     | I <sub>DESAT_PU</sub>                 |      | 10      |             | μΑ      |                                |

| Comparator Thresholds                                 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | C 4  | 7.0     | 7.0         | 1,,     |                                |

| Rising Threshold                                      | V <sub>DESAT_R</sub>                  | 6.4  | 7.0     | 7.6         | V       |                                |

| Falling Threshold                                     | V <sub>DESAT_F</sub>                  | 6.2  | 6.8     | 7.4         | V       |                                |

| Hysteresis                                            | V <sub>DESAT_H</sub>                  |      | 0.2     |             | V       |                                |

| Delay to Soft Turn Off                                | t <sub>DESAT_DLY</sub>                | 75   | 100     | 140         | ns      |                                |

| Blanking Switch R <sub>DSON</sub>                     | R <sub>DSON_BLANK</sub>               | 6    | 10.6    | 24          | Ω       |                                |

| DESAT Blanking Time                                   |                                       |      |         |             |         |                                |

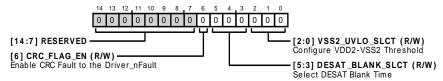

| Code 000                                              | T <sub>BLANK_000</sub>                | TBD  | 0       | TBD         | ns      | DESAT_BLANK_SLCT = '000'       |

| Code 001 (default)                                    | T <sub>BLANK_001</sub>                | TBD  | 100     | TBD         | ns      | DESAT_BLANK_SLCT = '001'       |

| Code 010                                              | T <sub>BLANK_010</sub>                | TBD  | 200     | TBD         | ns      | DESAT_BLANK_SLCT = '010'       |

| Code 011                                              | T <sub>BLANK_011</sub>                | TBD  | 300     | TBD         | ns      | DESAT_BLANK_SLCT = '011'       |

| Code 100                                              | T <sub>BLANK_100</sub>                | TBD  | 400     | TBD         | ns      | DESAT_BLANK_SLCT = '100'       |

| Parameter                                                               | Symbol                        | Min   | Тур  | Max | Unit | Test Conditions/Comments                                      |

|-------------------------------------------------------------------------|-------------------------------|-------|------|-----|------|---------------------------------------------------------------|

| Code 101                                                                | T <sub>BLANK_101</sub>        | TBD   | 500  | TBD | ns   | DESAT_BLANK_SLCT = '101'                                      |

| Code 110                                                                | T <sub>BLANK_110</sub>        | TBD   | 600  | TBD | ns   | DESAT_BLANK_SLCT = '110'                                      |

| Code 111                                                                | T <sub>BLANK_111</sub>        | TBD   | 700  | TBD | ns   | DESAT_BLANK_SLCT = '111'                                      |

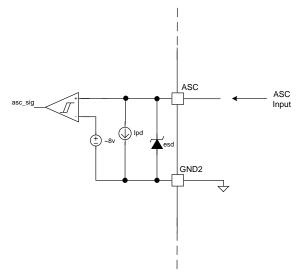

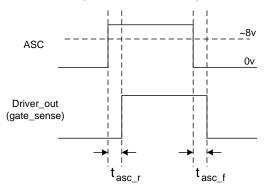

| Active Short Circuit (ASC)                                              |                               |       |      |     |      |                                                               |

| ASC Pin Current                                                         | I <sub>ASC</sub>              | 100   | 150  | 200 | μΑ   | $V_{ASC} = 8 V$                                               |

| Comparator Thresholds                                                   |                               |       |      |     | '    |                                                               |

| Rising Threshold                                                        | V <sub>ASC_R</sub>            | 7.4   | 8.0  | 8.6 | V    |                                                               |

| Falling Threshold                                                       | V <sub>ASC_F</sub>            | 7.2   | 7.8  | 8.4 | V    |                                                               |

| Hysteresis                                                              | V <sub>ASC_H</sub>            |       | 0.2  |     | V    |                                                               |

| ASC Propagation Delay                                                   |                               |       |      |     |      |                                                               |

| Propagation Delay Rising                                                | t <sub>PD_ASCr</sub>          | 70    | 100  | 130 | ns   |                                                               |

| Propagation Delay Falling                                               | t <sub>PD_ASCf</sub>          | 90    | 120  | 175 | ns   |                                                               |

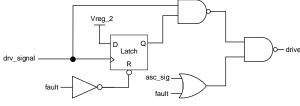

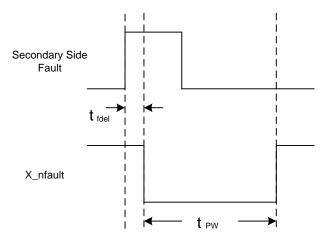

| Fault Specifications                                                    |                               |       |      |     |      |                                                               |

| Latch Time                                                              |                               | 1     |      |     |      |                                                               |

| UVLO_nFAULT                                                             | tlatch uvlo nfault            | TBD   | 10   | TBD | ms   |                                                               |

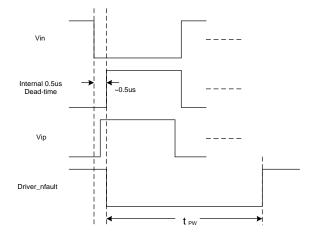

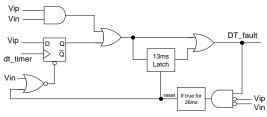

| <br>Deadtime                                                            | tlatch dt                     | TBD   | 13   | TBD | ms   |                                                               |

| FAULT                                                                   | tLATCH nFAULT                 | TBD   | 20   | TBD | ms   |                                                               |

| DRIVER_nFAULT                                                           | t <sub>LATCH_D_nFAULT</sub>   | TBD   | 30   | TBD | ms   |                                                               |

| Reporting Time                                                          | -Bitteri_b_titrioet           |       |      |     |      |                                                               |

| UVLO _nFAULT                                                            | t <sub>FDEL</sub> UVLO nFAULT |       | TBD  | 6.7 | μs   |                                                               |

| Deadtime                                                                | t <sub>FDEL</sub> DT          |       | TBD  |     | μs   |                                                               |

| FAULT                                                                   | t <sub>FDEL nFAULT</sub>      |       | TBD  | 1.1 | μs   |                                                               |

| DRIVER_nFAULT                                                           | tedel D neault                |       | TBD  | 1.1 | μs   |                                                               |

| DRIVER_nFAULT Pull-up Current                                           | ID_nFAULT_PU                  |       | 100  |     | μΑ   |                                                               |

| UVLO_nFAULT Pull-up Current                                             | I <sub>UVLO_nFAULT_PU</sub>   |       | 100  |     | μΑ   |                                                               |

| FAULT Pull-up Current                                                   | InFAULT_PU                    |       | 100  |     | μΑ   |                                                               |

| DRIVER_nFAULT NMOS R <sub>DSON</sub>                                    | RDSON D NFAULT                |       | 10   | TBD | Ω    |                                                               |

| UVLO_nFAULT NMOS R <sub>DSON</sub>                                      | R <sub>DSON_UVLO_nFAULT</sub> |       | 10   | TBD | Ω    |                                                               |

| FAULT NMOS R <sub>DSON</sub>                                            | RDSON_nFAULT                  |       | 10   | TBD | Ω    |                                                               |

| SPI Interface                                                           | TIDSON_HFAULT                 |       |      | 100 | 32   |                                                               |

| Minimum SCLK Period                                                     | t <sub>CLK</sub>              | 2.22  | 2.50 |     | lie. | 400 kHz (typ), 450 kHz (max)                                  |

| Minimum SCLK Feriou  Minimum SCLK High Time                             | t <sub>HI</sub>               | 0.45  | 2.30 |     | μs   | 400 kHz (typ), 430 kHz (IIIax)                                |

| Minimum SCLK High Time                                                  | t <sub>LO</sub>               | 0.775 |      |     | μs   |                                                               |

| Valid Data Before SCLK Falling Edge                                     | t <sub>DS</sub>               | 0.775 |      |     | μs   |                                                               |

| Valid Data Before SCLK Falling Edge  Valid Data After SCLK Falling Edge |                               | 0.125 |      |     | μs   |                                                               |

| Valid Data After SCEN Falling Edge                                      | <b>t</b> <sub>DH</sub>        | 0.123 |      |     | μs   |                                                               |

| nCS Falling to First SCLK Rising Edge                                   | to                            | 2.5   |      |     | μs   |                                                               |

| nCS Rising Edge to nCS falling Edge                                     | ts                            | 5.5   |      |     | μs   |                                                               |

| EEPROM Program Time                                                     | topes                         | ر.ر   | 1    |     | μs   | Single Programming Cycle                                      |

| LLF NOW Flogram Time                                                    | <b>t</b> PROG                 | 1     | ı    | 40  | ms   | 40 Programming Cycles                                         |

| Peak Current Per Output Pin <sup>3</sup>                                | l                             | -     | 10   | 40  | ms   | $V_{DD2} = 18 \text{ V}, 1.5 \Omega \text{ external}$         |

| reak Current rei Output Pili-                                           | ГРЕАКІР                       | 1     | 10   |     | A    | resistors                                                     |

| Short Circuit Peak Current Per Pin <sup>1</sup>                         | I <sub>PEAKIP_SC</sub>        | 1     | 15   |     | Α    | $V_{DD2} = 18 \text{ V}, 0 \Omega \text{ external resistors}$ |

<sup>&</sup>lt;sup>1</sup> Static common-mode transient immunity (CMTI) is defined as the largest dv/dt between V<sub>SS1</sub> and V<sub>SS2</sub>, with inputs held either high or low, such that the output voltage remains either above 0.8 × V<sub>DD2</sub> for output high or below 0.8 V for output low. Operation with transients above recommended levels may cause momentary data upsets. Tested in characterization and not production tested.

upsets. Tested in characterization and not production tested.

2 Dynamic common-mode transient immunity (CMTI) is defined as the largest dv/dt between V<sub>SS1</sub> and V<sub>SS2</sub> with the switching edge coincident with the transient test pulse. Operation with transients above recommended levels may cause momentary data upsets. Tested in characterization and not production tested.

<sup>&</sup>lt;sup>3</sup> Peak current ratings are tested in characterization and not production tested.

#### **INSULATION AND SAFETY-RELATED SPECIFICATIONS**

#### Table 2.

| Parameter                                                                   | Symbol  | Value | Unit  | Test Conditions/Comments                                                                                                   |

|-----------------------------------------------------------------------------|---------|-------|-------|----------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage                                         |         | 5000  | V rms | 1 minute duration                                                                                                          |

| Minimum External Air Gap (Clearance)                                        | L (I01) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance through air                                           |

| Minimum External Tracking (Creepage)                                        | L (I02) | 8.3   | mm    | Measured from input terminals to output terminals, shortest distance path along body                                       |

| Minimum Clearance in the Plane of the Printed Circuit Board (PCB Clearance) | L (PCB) | 8.7   | mm    | Measured from input terminals to output terminals, shortest distance through air, line of sight, in the PCB mounting plane |

| Minimum Internal Gap (Internal Clearance)                                   |         | 0.017 | mm    | Insulation distance through insulation                                                                                     |

| Tracking Resistance (Comparative Tracking Index)                            | CTI     | >600  | V     | DIN IEC 112/VDE 0303 Part 1                                                                                                |

| Material Group                                                              |         | 1     |       | Material group (DIN VDE 0110, 1/89, Table 1)                                                                               |

#### **RECOMMENDED OPERATING CONDITIONS**

#### Table 3.

| Parameter                                       | Value                                                                          |

|-------------------------------------------------|--------------------------------------------------------------------------------|

| Operating Junction Temperature Range            | −40°C to +150°C                                                                |

| Supply Voltages                                 |                                                                                |

| V <sub>DD1</sub> Referenced to GND <sub>1</sub> | 4.4 V to 7.0 V                                                                 |

| V <sub>DD2</sub> Referenced to GND <sub>2</sub> | 12 V to 24 V ( $V_{DD2} - V_{SS2} < 24 \text{ V}$ )                            |

| V <sub>SS2</sub> Referenced to GND <sub>2</sub> | $-5.5 \text{ V to } -3.25 \text{ V (V}_{DD2} - \text{V}_{SS2} < 24 \text{ V)}$ |

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                                                                     | Rating                             |

|-----------------------------------------------------------------------------------------------|------------------------------------|

| Supply Voltages                                                                               |                                    |

| V <sub>DD1</sub> <sup>1</sup>                                                                 | -0.2 V to 7.5 V                    |

| $V_{DD2}^2$                                                                                   | -0.2 V to 30 V                     |

| V <sub>SS2</sub> <sup>2</sup>                                                                 | -7 V to 0.2 V                      |

| Primary Side Pins                                                                             |                                    |

| VI+ <sup>1</sup> , VI- <sup>1</sup> , MOSI <sup>1</sup> , SCLK <sup>1</sup> , CS <sup>1</sup> | -0.2 V to 7.5 V when VDD1 > 4.4 V; |

|                                                                                               | -0.2 V to 6 V when VDD1 ≤ 4.4 V    |

| FAULT <sup>1</sup> , DRIVER_nFAULT <sup>1</sup> ,                                             | -0.2 V to V <sub>DD1</sub> + 0.2 V |

| UVLO_nFAULT <sup>1</sup> ,                                                                    |                                    |

| TEMP_OUT <sup>1</sup> , MISO <sup>1</sup>                                                     |                                    |

| Secondary Side Pins                                                                           |                                    |

| TS <sup>3</sup>                                                                               | -0.2 V to 5.2 V                    |

| ASC <sup>2</sup> , DESAT <sup>2</sup>                                                         | -0.2 V to V <sub>DD2</sub> V       |

| MILLER_DRV <sup>3</sup> ,                                                                     | -0.2 V to V <sub>DD2</sub> V       |

| Vout_off1 <sup>3</sup> , Vout_off2 <sup>3</sup> ,                                             |                                    |

| V <sub>OFF_SOFT</sub> <sup>3</sup> , GATE_SENSE <sup>3</sup>                                  |                                    |

| Vout_on1 <sup>3</sup> , Vout_on2 <sup>3</sup>                                                 | -0.2 V to V <sub>DD2</sub> + 0.2 V |

<sup>&</sup>lt;sup>1</sup> Referenced to GND<sub>1</sub>.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

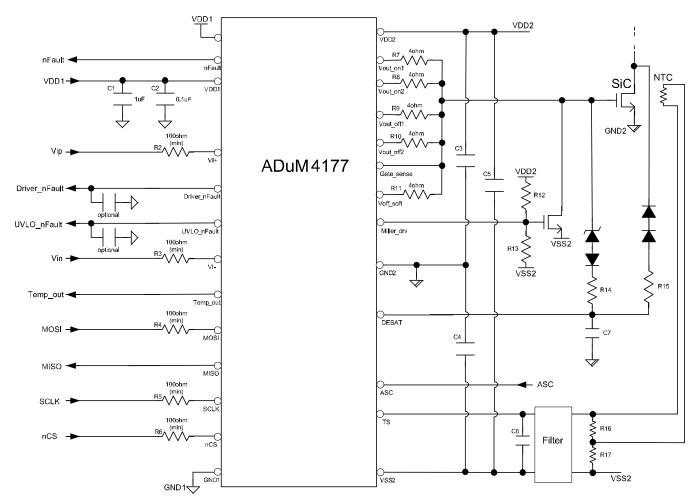

#### THERMAL RESISTANCE

Thermal performance is directly linked to PCB design and operating environment. Careful attention to PCB thermal design is required.  $\theta_{JA}$  is the junction to ambient thermal resistance, and  $\Psi_{JT}$  is the junction to top characterization parameter.

**Table 5. Thermal Resistance**

| Package Type | θ <sub>ЈА</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| RN-28-1      | TBD             | TBD | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Referenced to GND<sub>2</sub>.

<sup>&</sup>lt;sup>3</sup> Referenced to V<sub>SS2</sub>.

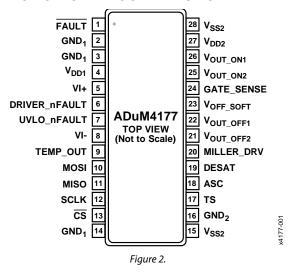

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic              | Description                                                                                                                 |

|---------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1       | FAULT                 | Negative logic fault output pin. Negative logic pin that communicates fault state of the gate driver.                       |

| 2       | GND <sub>1</sub>      | Primary side ground connection. Ground reference for primary side signals.                                                  |

| 3       | GND <sub>1</sub>      | Primary side ground connection. Ground reference for primary side signals.                                                  |

| 4       | V <sub>DD1</sub>      | Primary side power supply input. Provides current to operate the primary side of the gate driver.                           |

| 5       | VI+                   | Non-inverting input. Connect to non-inverting input of the control signal.                                                  |

| 6       | DRIVER_nFAULT         | Negative logic driver fault pin. Responds to driver related faults.                                                         |

| 7       | UVLO_nFAULT           | Negative logic UVLO fault pin. Responds to UVLO related faults.                                                             |

| 8       | VI-                   | Inverting input. Connect to inverted input of control signal.                                                               |

| 9       | TEMP_OUT              | Temperature sense PWM output pin. Returns the PWM encoded temperature sense signal from secondary side.                     |

| 10      | MOSI                  | SPI master out slave in pin. Data connection pin for SPI communication.                                                     |

| 11      | MISO                  | SPI master in slave out pin. Data connection pin for SPI communication.                                                     |

| 12      | SCLK                  | SPI reference clock. Clock pin for SPI communication.                                                                       |

| 13      | <u>cs</u>             | SPI chip select pin. Negative logic chip select pin for SPI communication.                                                  |

| 14      | GND <sub>1</sub>      | Primary side ground connection. Ground reference for primary side signals.                                                  |

| 15      | V <sub>SS2</sub>      | Secondary side negative supply connection. Lowest potential voltage on secondary side of gate driver.                       |

| 16      | GND <sub>2</sub>      | Secondary side ground connection. Ground reference for secondary side signals.                                              |

| 17      | TS                    | Temperature sense pin. Accepts an analog signal to convert into a PWM signal read out of TEMP_OUT pin.                      |

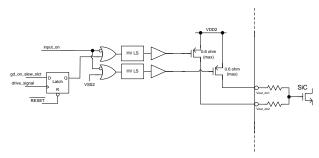

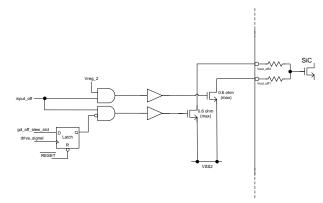

| 18      | ASC                   | Active Short Circuit pin. When ASC is brought high, the output of the gate driver goes high.                                |

| 19      | DESAT                 | Switch Drain protection sense input. Provides desaturation detection of the power device.                                   |

| 20      | MILLER_DRV            | Open drain miller drive pin. Connect to external Miller clamp to provide strong pull-down of power device.                  |

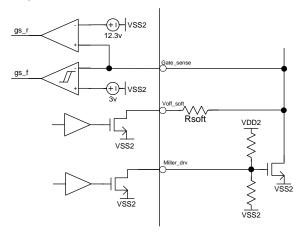

| 21      | Vout_off2             | Gate drive turn off pin 2. Provides strong turn off of power device. Can be toggled with slew rate control by SPI settings. |

| 22      | V <sub>OUT_OFF1</sub> | Gate drive turn off pin 1. Provides strong turn off of power device.                                                        |

| 23      | V <sub>OFF_SOFT</sub> | Soft shutdown pin. Provides shut off path for gate during fault conditions requiring a soft shutdown.                       |

| 24      | GATE_SENSE            | Switch gate sense pin. Connect directly to power device gate.                                                               |

| 25      | V <sub>OUT_ON2</sub>  | Gate drive turn on pin 2. Provides strong turn on of power device. Can be toggled with slew rate control by SPI settings.   |

| 26      | V <sub>OUT_ON1</sub>  | Gate drive turn on pin 1. Provides strong turn off of power device.                                                         |

| 27      | V <sub>DD2</sub>      | Secondary side positive power supply input pin. Provides positive voltage rail to gate driver.                              |

| 28      | V <sub>SS2</sub>      | Secondary side negative power supply input pin. Provides negative voltage rail to gate driver.                              |

# TYPICAL PERFORMANCE CHARACTERISTICS

**TBD**

Figure 3

**TBD**

Figure 4

**TBD**

Figure 5

**TBD**

Figure 6

**TBD**

Figure 7

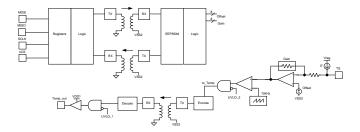

### THEORY OF OPERATION

Gate drivers are required in situations where fast rise times of switching device gates are required. The gate signals for enhancement power devices are referenced to a source or emitter node. The gate driver must follow this source or emitter node. As such, isolation is necessary between the controlling signal and the output of the gate driver in topologies where the source or emitter nodes swing, such as a half bridge. Gate switching times are a function of the drive strength of the gate driver. Buffer stages before a complementary metal-oxide semiconductor (CMOS) output reduce the total delay time and increase the final drive strength of the driver.

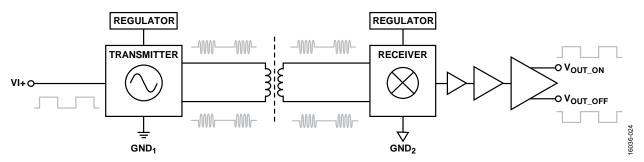

The ADuM4177 achieves isolation between the control side and the output side of the gate driver using a high frequency carrier that transmits data across the isolation barrier with *i*Coupler<sup>®</sup> chip scale transformer coils separated by layers of polyimide

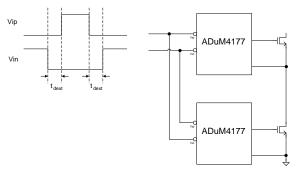

isolation. The ADuM4177 uses positive logic on/off keying (OOK) encoding, in which a high signal is transmitted by the presence of the carrier frequency across the *i*Coupler chip scale transformer coils. Positive logic encoding ensures that a low signal is seen on the output when the input side of the gate driver is unpowered. A low state is the most common safe state in enhancement mode power devices and can drive in situations where shoot through conditions are present. The architecture of the ADuM4177 is designed for high commonmode transient immunity and high immunity to electrical noise and magnetic interference. Radiated emissions are minimized with a spread spectrum OOK carrier and differential coil layout. Figure 8 shows the OOK encoding used by the ADuM4177.

Figure 8. Operational Block Diagram of OOK Encoding

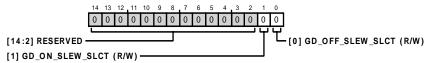

# APPLICATIONS PCB LAYOUT

The ADuM4177 SiC gate driver requires power supply bypassing at the  $V_{\rm DD1},\,V_{\rm DD2}$  and  $V_{\rm SS2}$  supply pins. Use a ceramic capacitor greater than  $10~\mu F$  on  $V_{\rm DD1}$  to  $GND_1.$  Add at least  $10~\mu F$  of capacitance on  $V_{\rm DD2}$  to  $V_{\rm SS2}$  to provide decoupling to the secondary side circuitry. Separate decoupling capacitors must be placed between  $V_{\rm DD2}$  to  $GND_2$  and from  $GND_2$  to  $V_{\rm SS2}.$  These capacitors supply the energy to drive the power device gate on and off, and should be at least  $10~\mu F$  each. Large gate charge power devices may need more capacitance. This capacitance can be provided by multiple parallel capacitors. Avoid using vias on the bypass capacitor or employ multiple vias to reduce the inductance in the bypassing because board vias can introduce parasitic inductance. The total lead length between both ends of the smaller capacitor and the input or output power supply pin should not exceed approximately 5 mm.

To improve robustness <u>against</u> bulk current injection, the input pins (VI+, VI–, MOSI,  $\overline{\text{CS}}$ , and SCLK) can have series 100  $\Omega$  resistors placed to limit current. The inclusion of 100  $\Omega$  resistors in series with input lines is highly recommended.

#### **POWER SUPPLIES**

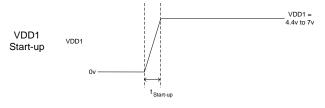

#### **V**<sub>DD1</sub> **Supply**

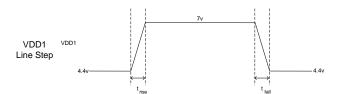

$V_{\rm DD1}$  can be operated between 4.4 V (min) to 7 V (max). The  $V_{\rm DD1}$  power supply powers the primary side circuitry. A UVLO is included to prevent underpowered operation. The ADuM4177 will begin to operate once the  $V_{\rm DD1}$  voltage exceeds the rising UVLO threshold, 3.8 V (typ), and will continue to operate until the  $V_{\rm DD1}$  voltage falls below the falling UVLO threshold, 3.5 V (typ). The ramp rate on the  $V_{\rm DD1}$  pin must be kept below 1 V/ms to avoid stress on the primary side silicon. Both startup and operation have this dv/dt rate limitation.

Figure 9. Start-up dv/dt.

Figure 10. Line-step dv/dt.

#### V<sub>DD2</sub>/V<sub>SS2</sub> Supplies

The ADuM4177 allows for native bipolar output to drive power devices both positively and negatively with respect to their source/emitter node. The secondary side of the ADuM4177 is powered through the  $V_{\rm DD2}$ , GND<sub>2</sub>, and  $V_{\rm SS2}$  pins. The operating range of  $V_{\rm DD2}$  to GND<sub>2</sub> is 12 V (min) to 24 V (max). The maximum voltage between  $V_{\rm DD2}$  and  $V_{\rm SS2}$  is 24 V (max), meaning that if a negative voltage drive is used, the  $V_{\rm DD2}$  to GND<sub>2</sub> voltage must be below 24 V. A negative drive can be obtained by supplying a -5.5 V (min) to -3.25 V (max) voltage between  $V_{\rm SS2}$  and GND<sub>2</sub>.

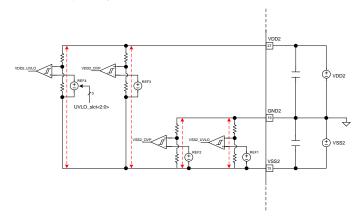

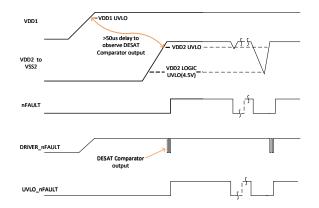

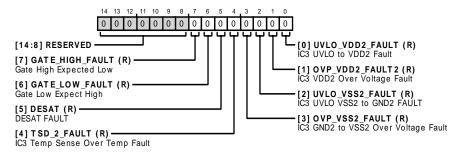

The ADuM4177 provides secondary side UVLO and OVP protections on both the  $V_{\rm DD2}$  and  $V_{\rm SS2}$  pins, ensuring that the gate drive is within tight tolerances. The  $V_{\rm DD2}$  UVLO and OVP is referenced to  $V_{\rm SS2}$ , ensuring a specific total gate voltage swing. The  $V_{\rm SS2}$  UVLO and OVP is referenced to GND<sub>2</sub>.

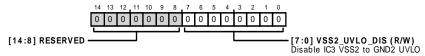

The UVLO is programmable through the SPI interface register 0x54 bits <2:0>, VDD2\_UVLO\_SLCT. The values in register 0x54 are EEPROM programmable, resulting in UVLO options that persist between power cycles.

If the registers of the ADuM4177 are programmed to work in bipolar mode, a negative voltage with the UVLO/OVP range of  $V_{SS2}$  is required. In order to operate in unipolar mode (GND<sub>2</sub> =  $V_{SS2}$ ), VSS2\_UVLO\_DIS, register 0x52 bits <7:0> must be programmed to '01101101'. This is the only bit configuration that will disable the  $V_{SS2}$  UVLO.

Voltage supply excursions outside of the VDD2 and VSS2 UVLO and OVP will issue a fault, shut off the driver output, and enter soft-shutdown. The faults will latch for the prescribed timings, allowing for fault differentiation at the pin reporting level on the primary side.

Figure 11. Functional VDD2/VSS2 supply UVLO and OVP

#### PROPAGATION DELAY RELATED PARAMETERS

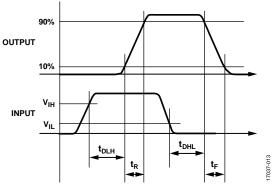

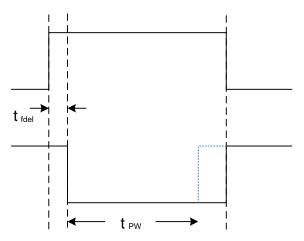

Propagation delay describes the time it takes a logic signal to propagate through a component. The propagation delay to a low

output can differ from the propagation delay to a high output. The ADuM4177 specifies the rising propagation delay,  $t_{\rm DLH}$  (see Figure 12), as the time between the rising input high logic threshold,  $V_{\rm IH}$ , to the output rising 10% threshold. Likewise, the falling propagation delay,  $t_{\rm DHL}$ , is defined as the time between the input falling logic low threshold,  $V_{\rm IL}$ , and the output falling 90% threshold. The rise and fall times are dependent on the loading conditions and are not included in the propagation delay, which is the industry standard for gate drivers.

Figure 12. Propagation Delay Parameters

Propagation delay skew refers to the maximum amount that the propagation delay differs between multiple ADuM4177 components operating under the same temperature, input voltage, and load conditions.

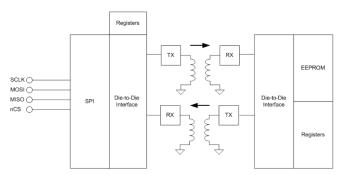

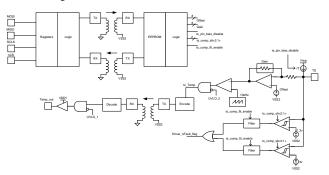

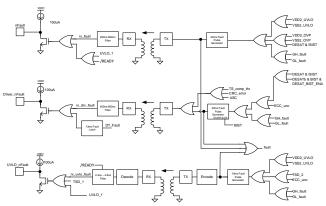

#### **SPI INTERFACE**

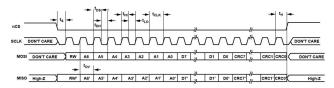

The SPI interface, consisting of the MOSI, MISO, SCLK and nCS pins, is an independent interface that is active when both the primary side UVLO1 and secondary side  $V_{\rm DD2}\text{-}V_{SS2}$  voltage is greater than 11.5 V (typ). See Figure 15 for a functional block diagram of the SPI interface. The format for an SPI bit sequence write/read is shown in Figure 13. 24 bits defines a full SPI bit sequence:

| Command Field      | Address Field | Data Field | CRC Field |

|--------------------|---------------|------------|-----------|

| <23>               | <22:16>       | <15:8>     | <7:0>     |

| READ(=0)/WRITE(=1) | ADDR<6:0>     | Data<7:0>  | CRC<7:0>  |

Figure 13. SPI Register Format (except PWM registers)

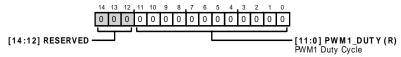

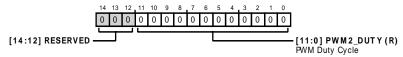

Registers 0x08 and 0x09 for the PWM duty cycle information follow a different format for the read back, see Figure 14:

| MISO Read  |            |           |

|------------|------------|-----------|

| Data Field | Data Field | CRC Field |

| <23:20>    | <19:8>     | <7:0>     |

| 0000       | Data<11:0> | CRC<7:0>  |

Figure 14. Register 0x08, 0x09 PWM Format

The PWM register format allows a larger data field to properly send the duty cycle information in a single read step.

Figure 15. SPI Functional Block Diagram

Figure 16. SPI Timing Diagram

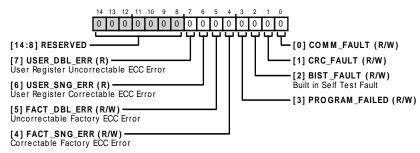

CRC is used to ensure proper integrity of a read/write operation. In addition to CRC, ECC is used on both primary side fuse trim and the secondary side EEPROM bits. An ECC\_CORR fault occurs if the ECC successfully corrected a single bit error in the secondary side EEPROM. If an ECC\_CORR fault occurs, the ADuM4177 will operate normally, but there is a defect present in the part. An uncorrected error will post and shut down operation of the device. On the primary side, an ECC error will only post to the IC Digital Status register, no action is taken to affect operation of the ADuM4177.

A Communication Fault occurs during an SPI write or read operation. A Communication Fault will be posted if either not enough bits were sent during an SPI transfer, or if too many bits were sent during an SPI transfer. In either case, in the event of Communication Fault, the SPI transfer is aborted. A communication fault is posted to the IC1 Digital Status register and the IC3 Digital Status register. A communication fault does not affect normal operation of the ADuM4177.

#### CRC

The ADuM4177 SPI word is constructed with a CRC field, see Figure 41. The 8 bit CRC word, CRC<7:0>, is set to a specific value which is associated with value of the remaining 16 bits; Data<7:0>, ADDR<6:0> and the READ/WRITE bit.

If the user is performing a write command, the correct CRC<7:0> value must be calculated for the corresponding remaining 16 bits. When performing the write, all data must be transferred to the ADuM4177 device. Internally, the ADuM4177 will take the CRC<7:0> value field and compare it to the remaining 16 bits. If the values correspond correctly, no error is reported. If the values do not correlate, then a CRC\_error fault will be issued.

The CRC value is based on the PMBus CRC-8 packet check, which utilizes the polynomial  $x^8 + x^2 + x + 1$ . Example Verilog code is as follows:

```

Example code in Verilog (data[15] = command, data[14:8] = address, data[7:0] = value):

// CRC-8

function [7:0] crc8;

input [15:0] data;

integer i;

begin

crc8 = 0;

for(i=15;i>=0;i=i-1)

if ( crc8[7] ^ data[i] )

crc8 = ( crc8 << 1 ) ^ 8'b00000111;

else

crc8 = ( crc8 << 1 );

end

endfunction

```

When writing data to the ADuM4177, the above algorithm should be used to calculate the CRC bit field. Similarly, when performing a read, the above algorithm should be used to confirm the 16 bits of data, address and command against the CRC field read.

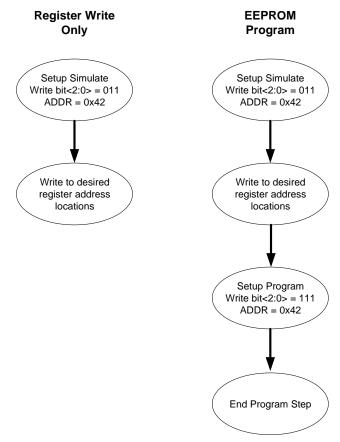

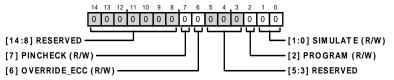

#### Simulating and Programming EEPROM

To simulate trim, or write to registers but not program the available EEPROM bits, both "simulate" bits, bit 0 and bit 1, must be set to '1', and the "program" bit, bit 2, must be set to '0' in the data field. To program trim, or program any EEPROM registers, both "simulate" bits, and the "program" bit, must be set to '1'. This helps prevent false writes by requiring a specific 3 bit sequence to both simulate and program the register space on the secondary side. To summarize:

Simulate register values  $\Rightarrow$  bits<2:0> = 011 Program eeprom/register values  $\Rightarrow$  bits<2:0> = 111

Figure 17 provides a flow diagram for both the simulate and program steps for the ADuM4177 secondary side register space. To determine when the programming step is complete, read the IC3 Control register, address 0x42. When bit<2> changes from a '1' to a '0', the programming cycle has completed. A programming step can take up to 40 ms (max) to complete.

During  $V_{\rm DD1}$  start-up, the SPI interface will be inactive until the first rising edge of the nCS pin. After the nCS pin goes high for the first time, the SPI interface will respond when the nCS pin if forced low, providing the  $V_{\rm DD1}$  UVLO is valid and the  $V_{\rm DD2}\text{-}V_{SS2}$  supply is greater than 11.5 V (typ).

If during start-up,  $V_{\rm DD1}$  is applied while  $V_{\rm DD2}$  is 0 V, or if  $V_{\rm DD2}$  is lost during normal operation, the SPI interface will continue to operate. The registers located on the primary side can be written to and read from. However, if any register on the secondary side it written to, no value will be accepted without power present on  $V_{\rm DD2}$ . If any registers are read on the secondary side, MISO will return all 0's if power is not present

on  $V_{DD2}$ . With power not present on  $V_{DD2}$ , the SPI return receiver will have no signal present, which will return only 0's.

Figure 17. Simulate and Program Flow Diagram

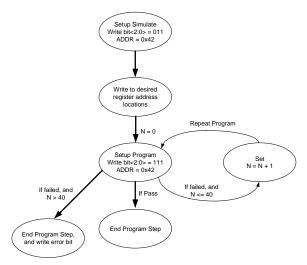

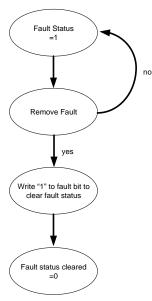

#### **Programming Error Fault**

Some faults are written to fault registers for readback. One fault accessible by register read is the "Programming Failed" fault. Figure 18 provides a state diagram for the EEPROM programming flow. After '111' is written to bits <2:0> IC3 Control register, address 0x42, the EEPROM program cycle will start. If at the end of the program cycle, the EEPROM write did not complete successfully, the ADuM4177 will repeat the step automatically. The ADuM4177 will continue this for a total of 40 attempts if any preceding attempt was not successful. After 40 programming attempts, if there continue to be errors, the ADuM4177 will abort the programming cycle and issue a '1' to the Programming Failed bit in the IC3 Digital Status Register.

Figure 18. Programming State Diagram

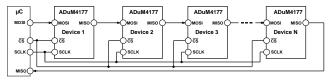

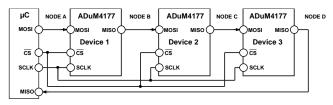

#### Daisy Chaining ADuM4177

A typical daisy chain configuration for the ADuM4177 is shown in Figure 19. Please note, resistor pull-ups (or pull-downs) should be used on each MOSI pin to avoid high impedance states when the nCS pin is set high, and the MISO pin goes into a Hi-Z output state.

Figure 19. Daisy Chain Diagram

The ADuM4177 is able to be daisy-chained in order to reduce MOSI, MISO, nCS, and SCLK lines interfacing the controller and multiple ADuM4177 units. Please refer to the configuration shown in Figure 20 for the following explanation.

Figure 20. Daisy Chain of Three ADuM4177 Devices

In the configuration shown in Figure 20, three units are shown connected. Each ADuM4177 expects to see some integer multiple of 24 clock cycles per cycle of the nCS pin. If a non-integer number of clock cycles occurs between the falling and rising edges of the nCS pin, the commands are ignored. This is important to note, as the ADuM4177 can be daisy chained with devices that are not ADuM4177 ONLY if the added devices also require an integer number of multiples of 24 cycles.

In this example, because there are three devices daisy chained, each falling and rising edge of nCS will have 24 x 3 cycles on SCLK. This is because three packets of 24 bits needs to be sent. The following is an example transfer, where commands are sent at Node A, and responses are received at Node D.

Figure 21. Example SPI transfer of three nCS edges

In Figure 21, there are three separate nCS rising edges. The commands sent are read into each individual ADuM4177 when the rising edge of nCS occurs. "C/" stands for "Command", "R/" stands for response, and "X" stands for unknown. Before the first rising edge, "Edge 1", there are three commands being sent to the devices. The devices repeat the bitstream given to their MOSI pin 24 cycles after. The repeated bitstream appears on the MISO pin. When the rising edge of nCS occurs, the last 24 bits seen on each of the ADuM4177 device's MOSI pin is taken into the device as a command. In this example, command "C" goes to ADuM4177 Device 1, command "B" goes to ADuM4177 Device 2, and command "A" goes to ADuM4177 device "A". During the next falling edge of nCS, the devices are now able to send the responses to the commands, as well as take in the next bitstream of commands. Since ADuM4177 Device 3 is the last in the daisy chain, it is the first to output its response to the controller. This means response "A" is seen on Node "D" first, followed by response "B", and finally response "C".

If a single command is desired to be sent to only one device, a read command can be given to the other devices on the chain. For example, if a "write xxx" command is to be given to ADuM4177 Device 2, then command "B" could be "write xxx", while command "A" and command "C" can be "read xxx". On the rising edge of nCS, the commands will be registered to the devices, and only ADuM4177 Device 2 will have a write command given to it.

There does not need to be an explicit wait time between 24 bit packets. The spaces between the 24 bit packets was drawn for clarity of bit count, and not to show actual timing. It is possible to have a single stream of 72 bits and SCLK periods in this example.

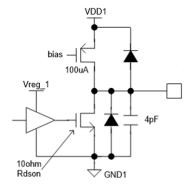

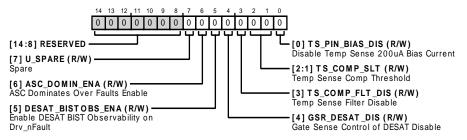

#### **TEMPERATURE SENSE**

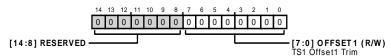

The ADuM4177 provides the ability to measure internal die temperature of the secondary side die, as well as a remote temperature sense that can be used in conjunction with a diode stack external to the ADuM4177 to measure temperatures outside of the ADuM4177. Remote temperature sensing is performed using the TS pin, and is referred to as TS1 in register names. Internal die temperature of the secondary side ADuM4177 die is reported as TS2 in register names.

#### **External Temperature Sense**

The ADuM4177 includes an analog input pin, TS, referenced to the V<sub>SS2</sub> pin on the secondary side that can report the value of the voltage on TS within a specified range operating at 10 kHz (typ). The reporting occurs on the primary side and is reported both with a 1 kHz (typ) PWM signal on the TEMP\_OUT pin, as well as in SPI register 0x08 bits <11:0> PWM\_TS1\_DUTY.

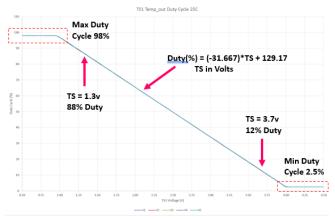

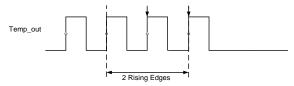

#### TEMP\_OUT Encoding

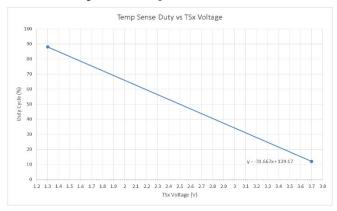

The target TEMP\_OUT duty cycle vs. TS voltage transfer function follows:

$$TEMP\_OUT(DUTY) = (-31.667) \times V_{TS1} + 129.17$$

Where

TEMP\_OUT(DUTY) is the duty cycle of the TEMP\_OUT pin.  $V_{TS1}$  is the voltage seen on TS pin.

Figure 22. Duty Cycle vs TS Voltage

Figure 23. Typical behavior of TS pin vs TEMP\_OUT Duty cycle

The target TEMP\_OUT duty cycle encoding for the ADuM4177 is  $-40^{\circ}$ C = 12% and 150 $^{\circ}$ C = 88%. The ADuM4177 Temp\_out Duty signal has a built in maximum duty cycle, 98% (typ), and minimum duty cycle, 2.5% (typ). If the TS voltage sense pins goes outside the normal range of operation, the Temp\_out duty ratio will be fixed by the ADuM4177.

Figure 24. Temperature Sense basic block diagram

The ADuM4177 temperature sense is designed to work with external diode sense stack. An internal 200  $\mu A$  (typ) bias current is used to bias the external diode stack. The ADuM4177 also contains trim capability to calibrate manufacturing variation in a temperature sense diode stack. The ADuM4177 allows for gain and offset trimming of the duty cycle response of the TS pi to allow for calibration due to variation in temperature sensing diode stacks.

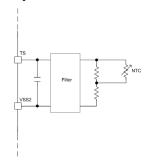

The ADuM4177 TS pin can also be used with an external NTC rather than a diode stack. A resistor network may be needed to ensure the range of operation is within 1.3 V and 3.7 V.

Figure 25. Example NTC Sense Element Configuration

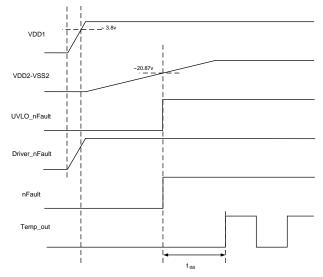

Figure 26. Temperature Sense Start-up Diagram

Figure 26 provides typical start-up diagram for the Temperature Sense output PWM duty cycle. After the  $V_{\text{DD2}}\text{-}V_{\text{SS2}}$

UVLO clears, the TEMP\_OUT duty cycle will be valid within time  $t_{\text{FILT}}$ , 3.15ms (max).

#### **Temperature Sense Duty Cycle Register**

In addition to having the Temp\_out pin to read the 1kHz (typ) temperature sense duty cycle, the ADuM4177 offers two addressable registers to read the TS pin and an internal secondary side diode via the SPI interface, registers 0x08 and 0x09.

Register 0x08 provides the duty cycle of the TS pin voltage sensed by the diode stack, or NTC.

Register 0x09 provides temperature information for the secondary driver die of the ADuM4177. The data present in register 0x09 is the duty cycle of the equivalent temperature seen on the secondary side die. The temperature is given by the following equation:

$$T = (-6.374) * D + 415.923$$

where D is given as a %, read from register 0x09,

T is given as temperature in C.

The temperature sense on the secondary side operates at 10 kHz (typ). Data is captured on the secondary side for both TS and the internal diode, and transferred to the primary side at the rising edge at the start of the next cycle 10 kHz (typ) clock. ADuM4177 utilizes a "boxcar" filtering technique with the following equation:

$$val = \frac{val_{-1}}{2} + \frac{x}{2}$$

where x is the new temperature sense value obtain,

val-1 is the previous calculated average value,

and val is the new average calculation which will be transferred to IC1.

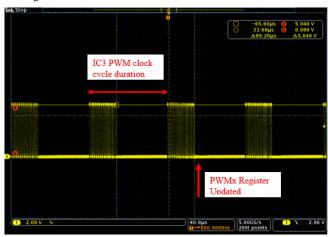

At the end of a data transfer, both TS and the internal diode PWM registers will be updated. Temperatures sense values are updated every 100  $\mu$ s (typ) and can be obtained by a read through the SPI interface.

Figure 27. Temperature sense data transfer

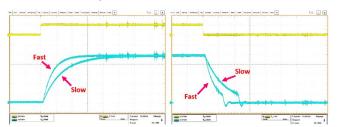

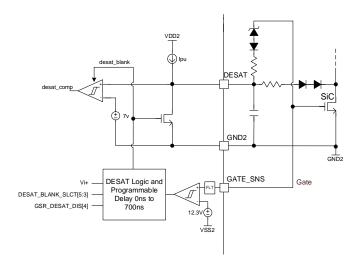

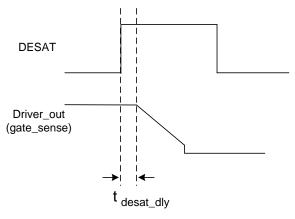

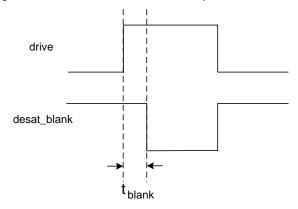

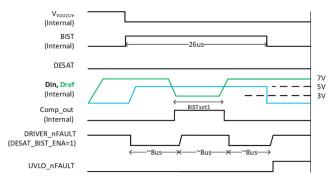

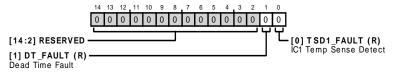

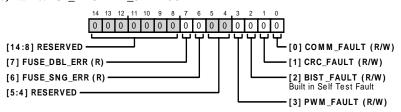

#### TS Analog Input