# 12-Bit ADC in 6-Lead SOT-23

AD7476-EP

### **FEATURES**

Specified for V<sub>DD</sub> of 2.35 V to 5.25 V

Low power

3.6 mW at 600 kSPS with 3 V supplies

15 mW at 600 kSPS with 5 V supplies

Wide input bandwidth

70 dB SNR at 100 kHz input frequency

High speed serial interface

SPI/QSPI™/MICROWIRE™/DSP compatible

Standby mode: 1 µA maximum

### **ENHANCED PRODUCT FEATURES**

Military temperature range (-55°C to +125°C) Controlled manufacturing baseline One assembly/test site One fabrication site Enhanced product change notification Qualification data available upon request

### **APPLICATIONS**

6-lead SOT-23 package

Battery-powered systems

Personal digital assistants

Medical instruments

Mobile communications

Instrumentation and control systems

Data acquisition systems

### **GENERAL DESCRIPTION**

The AD7476¹ is a 12-bit, high speed, low power, successive approximation ADC. The part operates from a single 2.35 V to 5.25 V power supply and features throughput rates up to 600 kSPS. The part contains a low noise, wide bandwidth, trackand-hold amplifier that can handle input frequencies in excess of 6 MHz.

The conversion process and data acquisition are controlled using  $\overline{CS}$  and the serial clock, allowing the device to interface with microprocessors or DSPs. The input signal is sampled on the falling edge of  $\overline{CS}$  and the conversion is initiated at this point. There are no pipeline delays associated with this part.

The AD7476 uses advanced design techniques to achieve very low power dissipation at high throughput rates.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

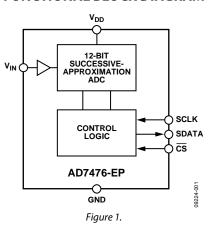

### **FUNCTIONAL BLOCK DIAGRAM**

The reference for the part is taken internally from  $V_{DD}$ . This allows the widest dynamic input range to the ADC. Thus, the analog input range for the part is 0 V to  $V_{DD}$ . The conversion rate is determined by the SCLK pin.

Additional application and technical information can be found in the AD7476 data sheet.

### **PRODUCT HIGHLIGHTS**

- 1. First 12-Bit ADC in a SOT-23 Package.

- 2. High Throughput with Low Power Consumption.

- 3. Flexible Power/Serial Clock Speed Management. The conversion rate is determined by the serial clock, allowing the conversion time to be reduced through the serial clock speed increase. This allows the average power consumption to be reduced while not converting. The part also features a shutdown mode to maximize power efficiency at lower throughput rates. Current consumption is 1 μA maximum when in shutdown mode.

- 4. Reference Derived from the Power Supply.

- 5. No Pipeline Delay. The part features a standard successive-approximation ADC with accurate control of the sampling instant via a  $\overline{\text{CS}}$  input and once-off conversion control.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2010 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patent No. 6,681,332.

# **TABLE OF CONTENTS**

| Features                  | ] |

|---------------------------|---|

|                           |   |

| Enhanced Product Features | 1 |

| Applications              | 1 |

| General Description       | 1 |

| Functional Block Diagram  | 1 |

| Product Highlights        | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Timing Specifications                       | .5 |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    | .6 |

| ESD Caution                                 | .6 |

| Pin Configuration and Function Descriptions | .7 |

| Typical Performance Characteristics         | .8 |

| Outline Dimensions                          | .9 |

| Ordering Guide                              | .9 |

### **REVISION HISTORY**

8/10—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD} = 2.35 \text{ V}$  to 5.25 V,  $f_{SCLK} = 12 \text{ MHz}$ ,  $f_{SAMPLE} = 600 \text{ kSPS}$ , unless otherwise noted;  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 1.

| Parameter                                          | S Version                 | Unit     | Test Conditions/Comments                                                         |

|----------------------------------------------------|---------------------------|----------|----------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                |                           |          | f <sub>IN</sub> = 100 kHz sine wave                                              |

| Signal-to-(Noise + Distortion) (SINAD)             | 69                        | dB min   |                                                                                  |

|                                                    | 70                        | dB min   | $T_A = 25$ °C                                                                    |

| Signal-to-Noise Ratio (SNR)                        | 70                        | dB min   |                                                                                  |

| Total Harmonic Distortion (THD)                    | <b>–78</b>                | dB typ   |                                                                                  |

| Peak Harmonic or Spurious Noise (SFDR)             | -80                       | dB typ   |                                                                                  |

| Intermodulation Distortion (IMD)                   |                           |          |                                                                                  |

| Second-Order Terms                                 | -78                       | dB typ   | fa = 103.5 kHz, fb = 113.5 kHz                                                   |

| Third-Order Terms                                  | <b>–78</b>                | dB typ   | fa = 103.5 kHz, fb = 113.5 kHz                                                   |

| Aperture Delay                                     | 10                        | ns typ   |                                                                                  |

| Aperture Jitter                                    | 30                        | ps typ   |                                                                                  |

| Full Power Bandwidth                               | 6.5                       | MHz typ  | At 3 dB                                                                          |

| DC ACCURACY                                        |                           |          | $V_{DD} = (2.35 \text{ V to } 3.6 \text{ V})^{1}$                                |

| Resolution                                         | 12                        | Bits     |                                                                                  |

| Integral Nonlinearity                              | ±1.5                      | LSB max  |                                                                                  |

| ,                                                  | ±0.6                      | LSB typ  |                                                                                  |

| Differential Nonlinearity                          | -0.9/+1.5                 | LSB max  | Guaranteed no missed codes to 12 bits                                            |

| ,                                                  | ±0.75                     | LSB typ  |                                                                                  |

| Offset Error                                       | ±2                        | LSB max  |                                                                                  |

|                                                    |                           | LSB typ  |                                                                                  |

| Gain Error                                         | ±2                        | LSB max  |                                                                                  |

|                                                    |                           | LSB typ  |                                                                                  |

| ANALOG INPUT                                       |                           |          |                                                                                  |

| Input Voltage Ranges                               | 0 to V <sub>DD</sub>      | V        |                                                                                  |

| DC Leakage Current                                 | ±1                        | μA max   |                                                                                  |

| Input Capacitance                                  | 30                        | pF typ   |                                                                                  |

| LOGIC INPUT                                        |                           |          |                                                                                  |

| Input High Voltage, V <sub>INH</sub>               | 2.4                       | V min    |                                                                                  |

|                                                    | 1.8                       | V min    | $V_{DD} = 2.35 \text{ V}$                                                        |

| Input Low Voltage, V <sub>INL</sub>                | 0.4                       | V max    | $V_{DD} = 3 V$                                                                   |

|                                                    | 0.8                       | V max    | $V_{DD} = 5 \text{ V}$                                                           |

| Input Current, I <sub>IN</sub> , SCLK Pin          | ±1                        | μA max   | Typically 10 nA, $V_{IN} = 0 \text{ V or } V_{DD}$                               |

| Input Current, I <sub>IN</sub> , <del>CS</del> Pin | ±1                        | μA typ   |                                                                                  |

| Input Capacitance, C <sub>IN</sub> <sup>2</sup>    | 10                        | pF max   |                                                                                  |

| LOGIC OUTPUT                                       |                           |          |                                                                                  |

| Output High Voltage, V <sub>OH</sub>               | V <sub>DD</sub> - 0.2     | V min    | $I_{SOURCE} = 200 \mu\text{A}; V_{DD} = 2.35 \text{V} \text{ to } 5.25 \text{V}$ |

| Output Low Voltage, Vol                            | 0.4                       | V max    | $I_{SINK} = 200 \mu\text{A}$                                                     |

| Floating-State Leakage Current                     | ±10                       | μA max   |                                                                                  |

| Floating-State Output Capacitance <sup>2</sup>     | 10                        | pF max   |                                                                                  |

| Output Coding                                      | Straight (natural) binary |          |                                                                                  |

| CONVERSION RATE                                    |                           |          |                                                                                  |

| Conversion Time                                    | 1.33                      | μs max   | 16 SCLK cycles                                                                   |

| Track-and-Hold Acquisition Time                    | 500                       | ns max   | Full-scale step input                                                            |

| ·                                                  | 400                       | ns max   | Sine wave input ≤ 100 kHz                                                        |

| Throughput Rate                                    | 600                       | kSPS max | ·                                                                                |

| Parameter                 | S Version | Unit      | Test Conditions/Comments                                                     |

|---------------------------|-----------|-----------|------------------------------------------------------------------------------|

| POWER REQUIREMENTS        |           |           |                                                                              |

| $V_{DD}$                  | 2.35/5.25 | V min/max |                                                                              |

| I <sub>DD</sub>           |           |           | Digital I/Ps = $0 \text{ V}$ or $V_{DD}$                                     |

| Normal Mode (Static)      | 2         | mA typ    | $V_{DD} = 4.75 \text{ V}$ to 5.25 V, SCLK on or off                          |

|                           | 1         | mA typ    | $V_{DD} = 2.35 \text{ V}$ to 3.6 V, SCLK on or off                           |

| Normal Mode (Operational) | 3         | mA max    | $V_{DD} = 4.75 \text{ V to } 5.25 \text{ V},$ $f_{SAMPLE} = f_{SAMPLE}MAX^3$ |

|                           | 1.4       | mA max    | $V_{DD} = 2.35 \text{ V to } 3.6 \text{ V},$ $f_{SAMPLE} = f_{SAMPLE}MAX^4$  |

| Full Power-Down Mode      | 1         | μA max    | SCLK off                                                                     |

|                           | 80        | μA max    | SCLK on                                                                      |

| Power Dissipation         |           |           |                                                                              |

| Normal Mode (Operational) | 15        | mW max    | $V_{DD} = 5 \text{ V}, f_{SAMPLE} = f_{SAMPLE}MAX^4$                         |

|                           | 4.2       | mW max    | $V_{DD} = 3 \text{ V, } f_{SAMPLE} = f_{SAMPLE} MAX^4$                       |

| Full Power-Down           | 5         | μW max    | $V_{DD} = 5 \text{ V, SCLK off}$                                             |

|                           | 3         | μW max    | $V_{DD} = 3 \text{ V, SCLK off}$                                             |

$<sup>^1</sup>$  S version specifications apply as typical figures when  $V_{DD}=5.25$  V.  $^2$  Guaranteed by characterization.  $^3$   $f_{SAMPLE}MAX=600$  kSPS.

### **TIMING SPECIFICATIONS**

$V_{\text{DD}}$  = 2.35 V to 5.25 V,  $T_{\text{A}}$  =  $T_{\text{MIN}}$  to  $T_{\text{MAX}},$  unless otherwise noted.

Table 2.

|                                | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> <sup>1</sup> |                        |         |                                                                                 |

|--------------------------------|-----------------------------------------------------------|------------------------|---------|---------------------------------------------------------------------------------|

| Parameter <sup>2</sup>         | 3 V                                                       | 5 V                    | Unit    | Description                                                                     |

| f <sub>SCLK</sub> <sup>3</sup> | 10                                                        | 10                     | kHz min |                                                                                 |

|                                | 12                                                        | 12                     | MHz max |                                                                                 |

| tconvert                       | $16 \times t_{SCLK}$                                      | 16 × t <sub>SCLK</sub> |         |                                                                                 |

| t <sub>QUIET</sub>             | 50                                                        | 50                     | ns min  | Minimum quiet time required between bus relinquish and start of next conversion |

| $t_1$                          | 10                                                        | 10                     | ns min  | Minimum CS pulse width                                                          |

| $t_2$                          | 10                                                        | 10                     | ns min  | CS to SCLK setup time                                                           |

| t <sub>3</sub> <sup>4</sup>    | 20                                                        | 20                     | ns max  | Delay from CS until SDATA three-state disabled                                  |

| t4 <sup>4</sup>                | 40                                                        | 20                     | ns max  | Data access time after SCLK falling edge, A version                             |

|                                | 70                                                        | 20                     | ns max  | Data access time after SCLK falling edge, B version                             |

| <b>t</b> <sub>5</sub>          | $0.4 \times t_{SCLK}$                                     | $0.4 \times t_{SCLK}$  | ns min  | SCLK low pulse width                                                            |

| t <sub>6</sub>                 | $0.4 \times t_{SCLK}$                                     | $0.4 \times t_{SCLK}$  | ns min  | SCLK high pulse width                                                           |

| <b>t</b> <sub>7</sub>          | 10                                                        | 10                     | ns min  | SCLK to data valid hold time                                                    |

| t <sub>8</sub> <sup>5</sup>    | 10                                                        | 10                     | ns min  | SCLK falling edge to SDATA high impedance                                       |

|                                | 25                                                        | 25                     | ns max  | SCLK falling edge to SDATA high impedance                                       |

| t <sub>POWER-UP</sub>          | 1                                                         | 1                      | μs typ  | Power-up time from full power-down                                              |

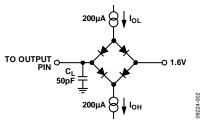

<sup>5</sup> t<sub>8</sub> is derived from the measured time taken by the data output to change 0.5 V when loaded with the circuit in Figure 2. The measured number is then extrapolated to remove the effects of charging or discharging the 50 pF capacitor. This means that the time, ts, is the true bus relinquish time of the part and is independent of the bus loading.

Figure 2. Load Circuit for Digital Output Timing Specifications

$<sup>^1</sup>$  3 V specifications apply from V<sub>DD</sub> = 2.35 V to 3.6 V; 5 V specifications apply from V<sub>DD</sub> = 4.75 V to 5.25 V.  $^2$  Guaranteed by characterization. All input signals are specified with tr = tf = 5 ns (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of 1.6 V.

$<sup>^{\</sup>rm 3}$  Mark/space ratio for the SCLK input is 40/60 to 60/40.

<sup>&</sup>lt;sup>4</sup> Measured with the load circuit of Figure 2 and defined as the time required for the output to cross 0.8 V or 2.0 V.

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                                             | Rating                                       |  |  |

|-------------------------------------------------------|----------------------------------------------|--|--|

| V <sub>DD</sub> to GND                                | −0.3 V to +7 V                               |  |  |

| Analog Input Voltage to GND                           | $-0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ |  |  |

| Digital Input Voltage to GND                          | -0.3  V to  +7  V                            |  |  |

| Digital Output Voltage to GND                         | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$   |  |  |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                       |  |  |

| Operating Temperature Range                           |                                              |  |  |

| Enhanced Plastic (EP Version)                         | −55°C to +125°C                              |  |  |

| Storage Temperature Range                             | −65°C to +150°C                              |  |  |

| Junction Temperature                                  | 150°C                                        |  |  |

| SOT-23 Package                                        |                                              |  |  |

| $\theta_{JA}$ Thermal Impedance                       | 230°C/W                                      |  |  |

| $\theta_{JC}$ Thermal Impedance                       | 92°C/W                                       |  |  |

| Lead Temperature, Soldering Reflow                    |                                              |  |  |

| (10 sec to 30 sec)                                    | 235 (0/+5)°C                                 |  |  |

| Pb-free Temperature Soldering Reflow                  | 255 (0/+5)°C                                 |  |  |

| ESD                                                   | 3.5 kV                                       |  |  |

$<sup>^{\</sup>rm 1}$  Transient currents of up to 100 mA do not cause SCR latch-up.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

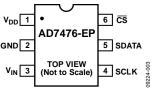

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

### **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                 |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | $V_{DD}$        | Power Supply Input. The V <sub>DD</sub> range for the AD7476-EP is from 2.35 V to 5.25 V.                                                                                                                                                                                                                   |

| 2       | GND             | Analog Ground. Ground reference point for all circuitry on the part. All analog input signals should be referred to this GND voltage.                                                                                                                                                                       |

| 3       | V <sub>IN</sub> | Analog Input. Single-ended analog input channel. The input range is 0 V to VDD.                                                                                                                                                                                                                             |

| 4       | SCLK            | Serial Clock. Logic input. SCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the AD7476-EP conversion process.                                                                                                                         |

| 5       | SDATA           | Data Out. Logic output. The conversion result is provided on this output as a serial data stream. The bits are clocked out on the falling edge of the SCLK input. The data stream from the AD7476-EP consists of four leading zeros followed by the 12 bits of conversion data; this is provided MSB first. |

| 6       | CS              | Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7476-EP and framing the serial data transfer.                                                                                                                                                 |

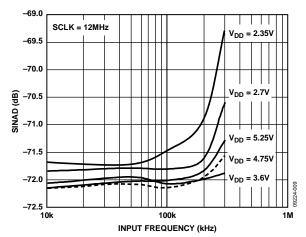

# TYPICAL PERFORMANCE CHARACTERISTICS

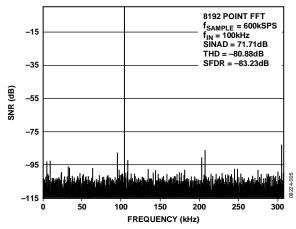

Figure 4. AD7476-EP Dynamic Performance at 600 kSPS

Figure 5. AD7476-EP SINAD vs. Input Frequency at 605 kSPS

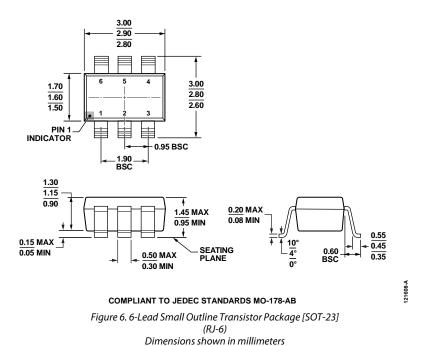

# **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Linearity Error (LSB) <sup>2</sup> | Package Description | Package Option | Branding |

|--------------------|-------------------|------------------------------------|---------------------|----------------|----------|

| AD7476SRTZ-EP-RL7  | −55°C to +125°C   | ±1.5 maximum                       | 6-Lead SOT-23       | RJ-6           | C73#     |

$<sup>^1</sup>$  Z = RoHS Compliant Part, # denotes RoHS compliant part maybe top or bottom marked.  $^2$  Linearity error refers to integral linearity error.

**NOTES**

**NOTES**

**NOTES**