# Please note that Cypress is an Infineon Technologies Company.

The document following this cover page is marked as "Cypress" document as this is the company that originally developed the product. Please note that Infineon will continue to offer the product to new and existing customers as part of the Infineon product portfolio.

# **Continuity of document content**

The fact that Infineon offers the following product as part of the Infineon product portfolio does not lead to any changes to this document. Future revisions will occur when appropriate, and any changes will be set out on the document history page.

# **Continuity of ordering part numbers**

Infineon continues to support existing part numbers. Please continue to use the ordering part numbers listed in the datasheet for ordering.

www.infineon.com

## CY7C2268KV18/CY7C2270KV18

# 36-Mbit DDR II+ SRAM Two-Word Burst Architecture (2.5 Cycle Read Latency) with ODT

### **Features**

- 36-Mbit density (2M × 18, 1M × 36)

- 550 MHz clock for high bandwidth

- Two-word burst for reducing address bus frequency

- Double data rate (DDR) interfaces (data transferred at 1100 MHz) at 550 MHz

- Available in 2.5 clock cycle latency

- Two input clocks (K and K) for precise DDR timing □ SRAM uses rising edges only

- Echo clocks (CQ and CQ) simplify data capture in high speed systems

- Data valid pin (QVLD) to indicate valid data on the output

- On-die termination (ODT) feature □ Supported for D<sub>[x:0]</sub>, BWS<sub>[x:0]</sub>, and K/K inputs

- Synchronous internally self-timed writes

- DDR II+ operates with 2.5 cycle read latency when DOFF is asserted HIGH

- Operates similar to DDR I device with 1 cycle read latency when DOFF is asserted LOW

- Core  $V_{DD}$  = 1.8 V ± 0.1 V; I/O  $V_{DDQ}$  = 1.4 V to  $V_{DD}$ <sup>[1]</sup> □ Supports both 1.5 V and 1.8 V I/O supply

- HSTL inputs and variable drive HSTL output buffers

- Available in 165-ball FBGA package (13 × 15 × 1.4 mm)

- Offered in both Pb-free and non Pb-free packages

- JTAG 1149.1 compatible test access port

- Phase-locked loop (PLL) for accurate data placement

## Configurations

With Read Cycle Latency of 2.5 Cycles:

CY7C2268KV18 - 2M × 18 CY7C2270KV18 - 1M × 36

## **Functional Description**

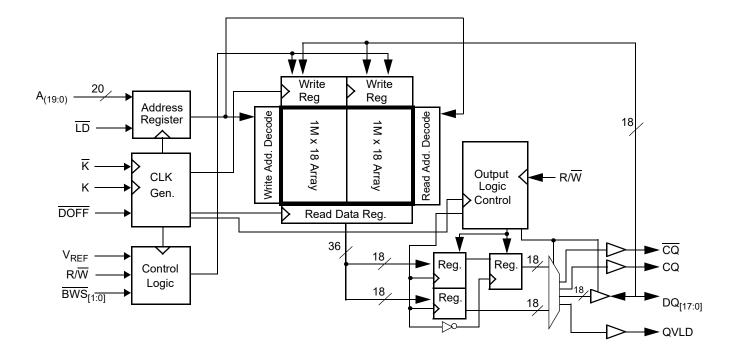

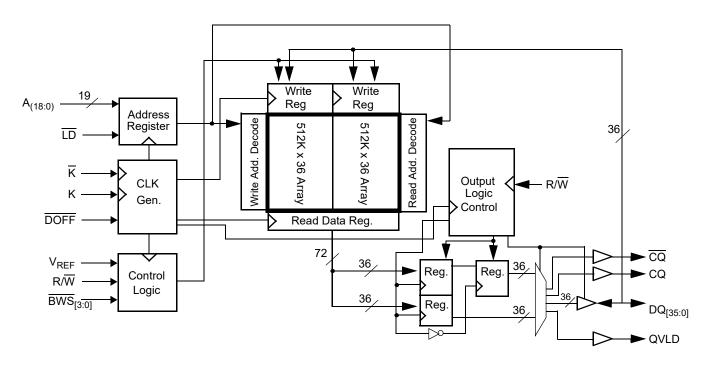

The CY7C2268KV18, and CY7C2270KV18 are 1.8 V synchronous pipelined SRAMs equipped with DDR II+ architecture. The DDR II+ consists of an SRAM core with advanced synchronous peripheral circuitry. Addresses for read and write are latched on alternate rising edges of the input (K) clock. Write data is registered on the rising edges of both K and K. Read data is driven on the rising edges of K and K. Each address location is associated with two 18-bit words (CY7C2268KV18), or 36-bit words (CY7C2270KV18) that burst sequentially into or out of the device.

These devices have an on-die termination feature supported for  $D_{[x:0]}$ , BWS<sub>[x:0]</sub>, and K/ $\overline{K}$  inputs, which helps eliminate external termination resistors, reduce cost, reduce board area, and simplify board routing.

Asynchronous inputs include an output impedance matching input (ZQ). Synchronous data outputs (Q, sharing the same physical pins as the data inputs D) are tightly matched to the two output echo clocks CQ/CQ, eliminating the need for separately capturing data from each individual DDR SRAM in the system

All synchronous inputs pass through input registers controlled by the K or K input clocks. All data outputs pass through output registers controlled by the K or  $\overline{K}$  input clocks. Writes are conducted with on-chip synchronous self-timed write circuitry.

For a complete list of related documentation, click here.

## **Selection Guide**

| Description                 |      | 550 MHz | 450 MHz     | 400 MHz     | Unit |

|-----------------------------|------|---------|-------------|-------------|------|

| Maximum operating frequency |      | 550     | 450         | 400         | MHz  |

| Maximum operating current   | × 18 | 700     | 600         | Not Offered | mA   |

|                             | × 36 | 890     | Not Offered | 690         |      |

**Cypress Semiconductor Corporation** Document Number: 001-57845 Rev. \*I

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

Revised January 4, 2018

Note

1. The Cypress QDR II+ devices surpass the QDR consortium specification and can support  $V_{DDQ} = 1.4 \text{ V to } V_{DD}$ .

# Logic Block Diagram - CY7C2268KV18

# Logic Block Diagram - CY7C2270KV18

## **Contents**

| Pin Configurations                            | 4                                    |

|-----------------------------------------------|--------------------------------------|

| Pin Definitions                               |                                      |

| Functional Overview                           | 6                                    |

| Read Operations                               | 6                                    |

| Write Operations                              |                                      |

| Byte Write Operations                         | 6                                    |

| DDR Operation                                 | . 7                                  |

| Depth Expansion                               | . 7                                  |

| Programmable Impedance                        |                                      |

| Echo Clocks                                   | . 7                                  |

| Valid Data Indicator (QVLD)                   | 7                                    |

| On-Die Termination (ODT)                      | 7                                    |

| PLL                                           |                                      |

| Application Example                           | 8                                    |

| Truth Table                                   |                                      |

| Write Cycle Descriptions                      | 9                                    |

| Write Cycle Descriptions1                     |                                      |

| IEEE 1149.1 Serial Boundary Scan (JTAG)1      | 11                                   |

|                                               | •                                    |

| Disabling the JTAG Feature1                   | 11                                   |

| Disabling the JTAG Feature1 Test Access Port1 | 11                                   |

|                                               | 1<br> 1                              |

| Test Access Port                              | 1<br> 1<br> 1                        |

| Test Access Port1 Performing a TAP Reset1     | 1<br> 1<br> 1                        |

| Test Access Port                              | 1<br> 1<br> 1<br> 1                  |

| Test Access Port                              | 1<br> 1<br> 1<br> 1                  |

| Test Access Port                              | 1<br> 1<br> 1<br> 1<br> 4            |

| Test Access Port                              | 1<br>  1<br>  1<br>  1<br>  1<br>  4 |

| Test Access Port                              | 1<br>  1<br>  1<br>  1<br>  1<br>  4 |

| Test Access Port                              | 1<br>  1<br>  1<br>  1<br>  4<br>  6 |

| Instruction Codes                       | 17 |

|-----------------------------------------|----|

| Boundary Scan Order                     | 18 |

| Power Up Sequence in DDR II+ SRAM       | 19 |

| Power Up Sequence                       | 19 |

| PLL Constraints                         | 19 |

| Maximum Ratings                         | 20 |

| Operating Range                         | 20 |

| Neutron Soft Error Immunity             | 20 |

| Electrical Characteristics              | 20 |

| DC Electrical Characteristics           | 20 |

| AC Electrical Characteristics           | 22 |

| Capacitance                             | 22 |

| Thermal Resistance                      | 22 |

| AC Test Loads and Waveforms             | 22 |

| Switching Characteristics               | 23 |

| Switching Waveforms                     | 25 |

| Read/Write/Deselect Sequence            | 25 |

| Ordering Information                    |    |

| Ordering Code Definitions               | 26 |

| Package Diagram                         | 27 |

| Acronyms                                | 28 |

| Document Conventions                    | 28 |

| Units of Measure                        | 28 |

| Document History Page                   | 29 |

| Sales, Solutions, and Legal Information | 31 |

| Worldwide Sales and Design Support      | 31 |

| Products                                | 31 |

| PSoC® Solutions                         | 31 |

| Cypress Developer Community             | 31 |

| Technical Support                       | 31 |

# **Pin Configurations**

The pin configuration for CY7C2268KV18, and CY7C2270KV18 follow. [2]

Figure 1. 165-ball FBGA (13 × 15 × 1.4 mm) pinout CY7C2268KV18 (2M × 18)

|   | 1    | 2         | 3         | 4                  | 5                | 6        | 7                | 8                  | 9         | 10        | 11  |

|---|------|-----------|-----------|--------------------|------------------|----------|------------------|--------------------|-----------|-----------|-----|

| Α | CQ   | NC/72M    | Α         | R/W                | BWS <sub>1</sub> | K        | NC/144M          | LD                 | Α         | Α         | CQ  |

| В | NC   | DQ9       | NC        | Α                  | NC/288M          | K        | BWS <sub>0</sub> | Α                  | NC        | NC        | DQ8 |

| С | NC   | NC        | NC        | $V_{SS}$           | Α                | NC       | Α                | V <sub>SS</sub>    | NC        | DQ7       | NC  |

| D | NC   | NC        | DQ10      | $V_{SS}$           | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | V <sub>SS</sub>    | NC        | NC        | NC  |

| E | NC   | NC        | DQ11      | $V_{\mathrm{DDQ}}$ | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | $V_{\mathrm{DDQ}}$ | NC        | NC        | DQ6 |

| F | NC   | DQ12      | NC        | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC        | DQ5 |

| G | NC   | NC        | DQ13      | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC        | NC  |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | $V_{DDQ}$ | $V_{REF}$ | ZQ  |

| J | NC   | NC        | NC        | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | DQ4       | NC  |

| K | NC   | NC        | DQ14      | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC        | DQ3 |

| L | NC   | DQ15      | NC        | $V_{\mathrm{DDQ}}$ | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | $V_{DDQ}$          | NC        | NC        | DQ2 |

| М | NC   | NC        | NC        | $V_{SS}$           | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | V <sub>SS</sub>    | NC        | DQ1       | NC  |

| N | NC   | NC        | DQ16      | $V_{SS}$           | Α                | Α        | Α                | V <sub>SS</sub>    | NC        | NC        | NC  |

| Р | NC   | NC        | DQ17      | Α                  | Α                | QVLD     | Α                | Α                  | NC        | NC        | DQ0 |

| R | TDO  | TCK       | Α         | Α                  | Α                | ODT      | А                | Α                  | Α         | TMS       | TDI |

## CY7C2270KV18 (1M × 36)

|   | 1    | 2         | 3         | 4                  | 5                | 6        | 7                | 8               | 9         | 10        | 11   |

|---|------|-----------|-----------|--------------------|------------------|----------|------------------|-----------------|-----------|-----------|------|

| Α | CQ   | NC/144M   | Α         | R/W                | BWS <sub>2</sub> | K        | BWS <sub>1</sub> | LD              | Α         | NC/72M    | CQ   |

| В | NC   | DQ27      | DQ18      | Α                  | BWS <sub>3</sub> | K        | BWS <sub>0</sub> | Α               | NC        | NC        | DQ8  |

| С | NC   | NC        | DQ28      | V <sub>SS</sub>    | Α                | NC       | Α                | V <sub>SS</sub> | NC        | DQ17      | DQ7  |

| D | NC   | DQ29      | DQ19      | $V_{SS}$           | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | V <sub>SS</sub> | NC        | NC        | DQ16 |

| E | NC   | NC        | DQ20      | $V_{DDQ}$          | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | $V_{DDQ}$       | NC        | DQ15      | DQ6  |

| F | NC   | DQ30      | DQ21      | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$       | NC        | NC        | DQ5  |

| G | NC   | DQ31      | DQ22      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$       | NC        | NC        | DQ14 |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$       | $V_{DDQ}$ | $V_{REF}$ | ZQ   |

| J | NC   | NC        | DQ32      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$       | NC        | DQ13      | DQ4  |

| K | NC   | NC        | DQ23      | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$       | NC        | DQ12      | DQ3  |

| L | NC   | DQ33      | DQ24      | $V_{DDQ}$          | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | $V_{DDQ}$       | NC        | NC        | DQ2  |

| М | NC   | NC        | DQ34      | $V_{SS}$           | V <sub>SS</sub>  | $V_{SS}$ | V <sub>SS</sub>  | V <sub>SS</sub> | NC        | DQ11      | DQ1  |

| N | NC   | DQ35      | DQ25      | V <sub>SS</sub>    | Α                | Α        | Α                | V <sub>SS</sub> | NC        | NC        | DQ10 |

| Р | NC   | NC        | DQ26      | Α                  | Α                | QVLD     | Α                | А               | NC        | DQ9       | DQ0  |

| R | TDO  | TCK       | Α         | Α                  | Α                | ODT      | Α                | Α               | Α         | TMS       | TDI  |

Document Number: 001-57845 Rev. \*I Page 4 of 31

Note

2. NC/72M, NC/144M, and NC/288M are not connected to the die and can be tied to any voltage level.

## **Pin Definitions**

| Pin Name                                                                           | I/O                                | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ <sub>[x:0]</sub>                                                                | Input output-<br>synchronous       | <b>Data input output signals</b> . Inputs are sampled on the rising edge of K and $\overline{K}$ clocks during valid write operations. These pins drive out the requested_data when the read operation is active. Valid data is driven out on the rising edge of both the K and $\overline{K}$ clocks during read operations. When read access is deselected, $Q_{[X:0]}$ are automatically tri-stated. CY7C2268KV18 – $DQ_{[17:0]}$ CY7C2270KV18 – $DQ_{[35:0]}$                                                                              |

| LD                                                                                 | Input-<br>synchronous              | <b>Synchronous load</b> . Sampled on the rising edge of the K clock. This input is brought LOW when a bus cycle sequence is defined. This definition includes address and read/write direction. All transactions operate on a burst of 2 data. LD must meet the setup and hold times around edge of K.                                                                                                                                                                                                                                         |

| BWS <sub>0</sub> ,<br>BWS <sub>1</sub> ,<br>BWS <sub>2</sub> ,<br>BWS <sub>3</sub> | Input-<br>synchronous              | Byte write select 0, 1, 2, and 3 – active LOW. Sampled on the rising edge of the K and $\overline{K}$ clocks during write operations. Used to select which byte is written into the device during the current portion of the write operations. Bytes not written remain unaltered.                                                                                                                                                                                                                                                             |

| A                                                                                  | Input-<br>synchronous              | <b>Address inputs</b> . Sampled on the rising edge of the K clock during active read and write operations. These address inputs are multiplexed for both read and write operations. Internally, the device is organized as 2 M $\times$ 18 (2 arrays each of 1 M $\times$ 18) for CY7C2268KV18, and 1 M $\times$ 36 (2 arrays each of 512 K $\times$ 36) for CY7C2270KV18.                                                                                                                                                                     |

| R/W                                                                                | Input-<br>synchronous              | Synchronous read or write input. When LD is LOW, this input designates the access type (read when R/W is HIGH, write when R/W is LOW) for loaded address. R/W must meet the setup and hold times around edge of K.                                                                                                                                                                                                                                                                                                                             |

| QVLD                                                                               | Valid output indicator             | Valid output indicator. The Q Valid indicates valid output data. QVLD is edge aligned with CQ and $\overline{CQ}$ .                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ODT <sup>[3]</sup>                                                                 | On-die<br>termination<br>input pin | <b>On-die termination input</b> . This pin is used for on-die termination of the input signals. ODT range selection is made during power up initialization. A LOW on this pin selects a low range that follows RQ/3.33 for 175 $\Omega \leq$ RQ $\leq$ 350 $\Omega$ (where RQ is the resistor tied to ZQ pin). A HIGH on this pin selects a high range that follows RQ/1.66 for 175 $\Omega \leq$ RQ $\leq$ 250 $\Omega$ (where RQ is the resistor tied to ZQ pin). When left floating, a high range termination value is selected by default. |

| K                                                                                  | Input clock                        | <b>Positive input clock input</b> . The rising edge of K is used to capture synchronous inputs to the device and to drive out data through $Q_{[x:0]}$ . All accesses are initiated on the rising edge of K.                                                                                                                                                                                                                                                                                                                                   |

| K                                                                                  | Input clock                        | <b>Negative input clock input.</b> $\overline{K}$ is used to capture synchronous data being presented to the device and to drive out data through $Q_{[x:0]}$ .                                                                                                                                                                                                                                                                                                                                                                                |

| CQ                                                                                 | Echo clock                         | <b>Synchronous echo clock outputs</b> . This is a free running clock and is synchronized to the input clock (K) of the DDR II+. The timing for the echo clocks is shown in the Switching Characteristics on page 23.                                                                                                                                                                                                                                                                                                                           |

| CQ                                                                                 | Echo clock                         | <b>Synchronous echo clock outputs</b> . This is a free running clock and is synchronized to the input clock (K) of the DDR II+. The timing for the echo clocks is shown in the Switching Characteristics on page 23.                                                                                                                                                                                                                                                                                                                           |

| ZQ                                                                                 | Input                              | <b>Output impedance</b> matching input. This input is used to tune the device outputs to the system data bus impedance. CQ, CQ, and $Q_{[x:0]}$ output impedance are set to $0.2 \times RQ$ , where RQ is a resistor connected between ZQ and ground. Alternatively, this pin can be connected directly to $V_{DDQ}$ , which enables the minimum impedance mode. This pin cannot be connected directly to GND or left unconnected.                                                                                                             |

Document Number: 001-57845 Rev. \*I Page 5 of 31

$<sup>\</sup>label{eq:optimize} \begin{tabular}{ll} \textbf{Note}\\ 3. & \mbox{On-die termination (ODT) feature is supported for $D_{[x:0]}$, $BWS_{[x:0]}$, and $K/\overline{K}$ inputs.} \end{tabular}$

## Pin Definitions (continued)

| Pin Name         | I/O                 | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DOFF             | Input               | <b>PLL turn off</b> – <b>active LOW</b> . Connecting this pin to ground turns off the PLL inside the device. The timing in the PLL turned off operation differs from those listed in this data sheet. For normal operation, this pin can be connected to a pull up through a 10 k $\Omega$ or less pull-up resistor. The device behaves in DDR I mode when the PLL is turned off. In this mode, the device can be operated at a frequency of up to 167 MHz with DDR I timing. |

| TDO              | Output              | TDO pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TCK              | Input               | TCK pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TDI              | Input               | TDI pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS              | Input               | TMS pin for JTAG.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NC               | N/A                 | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC/72M           | Input               | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC/144M          | Input               | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| NC/288M          | Input               | Not connected to the die. Can be tied to any voltage level.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>REF</sub> | Input-<br>reference | <b>Reference voltage input</b> . Static input used to set the reference level for HSTL inputs, outputs, and AC measurement points.                                                                                                                                                                                                                                                                                                                                            |

| $V_{DD}$         | Power supply        | Power supply inputs to the core of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V <sub>SS</sub>  | Ground              | Ground for the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{DDQ}$        | Power supply        | Power supply inputs for the outputs of the device.                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **Functional Overview**

The CY7C2268KV18, and CY7C2270KV18 are synchronous pipelined burst SRAMs equipped with a DDR interface, which operates with a read latency of two and half cycles when DOFF pin is tied HIGH. When DOFF pin is set LOW or connected to  $V_{SS}$  the device behaves in DDR I mode with a read latency of one clock cycle.

Accesses are initiated on the rising edge of the positive input clock (K). All synchronous input and output timing is referenced from the rising edge of the input clocks (K and  $\overline{K}$ ).

All synchronous data inputs  $(D_{[X:0]})$  pass through input registers controlled by the rising edge of the input clocks (K and K). All synchronous data outputs  $(Q_{[X:0]})$  pass through output registers controlled by the rising edge of the input clocks (K and K).

All synchronous control ( $R/\overline{W}$ ,  $\overline{LD}$ ,  $\overline{BWS}_{[X:0]}$ ) inputs pass through input registers controlled by the rising edge of the input clock (K).

CY7C2268KV18 is described in the following sections. The same basic descriptions apply to CY7C2270KV18.

#### Read Operations

The CY7C2268KV18 is organized internally as two arrays of 1M × 18. Accesses are completed in a burst of 2 sequential 18-bit data words. Read operations are initiated by asserting R/W HIGH and LD LOW at the rising edge of the positive input clock (K). The address presented to the address inputs is stored in the read address register. Following the next two  $\overline{K}$  clock rise, the corresponding 18-bit word of data from this address location is driven onto the  $Q_{[17:0]}$  using  $\overline{K}$  as the output timing reference. On the subsequent rising edge of K, the next 18-bit data word is driven onto the  $Q_{[17:0]}$ . The requested data  $\overline{K}$  valid 0.45 ns from the rising edge of the input clock (K and  $\overline{K}$ ). To maintain the

internal logic, each read access must be allowed to complete. Read accesses can be initiated on every rising edge of the positive input clock (K).

When read access is deselected, the CY7C2268KV18 first completes the pending read transactions. Synchronous internal circuitry automatically tri-states the output following the next rising edge of the negative input clock  $(\overline{K})$ . This enables for a transition between devices without the insertion of wait states in a depth expanded memory.

## Write Operations

Write operations are initiated by asserting R/W LOW and  $\overline{LD}$  LOW at the rising edge of the positive input clock (K). The address presented to address inputs is stored in the write address register. On the following K clock rise, the data presented to  $D_{[17:0]}$  is latched and stored into the 18-bit write data register, provided  $\overline{BWS}_{[1:0]}$  are both asserted active. On the subsequent rising edge of the negative input clock (K) the information presented to  $D_{[17:0]}$  is also stored into the write data register, provided  $\overline{BWS}_{[1:0]}$  are both asserted active. The 36 bits of data are then written into the memory array at the specified location. Write accesses can be initiated on every rising edge of the positive input clock (K). Doing so pipelines the data flow such that 18 bits of data can be transferred into the device on every rising edge of the input clocks (K and K).

When the write access is deselected, the device ignores all inputs after the pending write operations are completed.

#### **Byte Write Operations**

Byte write operations are supported by the CY7C2268KV18. A write operation is initiated as described in the section Write Operations on page 6. The bytes that are written are determined

Document Number: 001-57845 Rev. \*I Page 6 of 31

by  $\overline{BWS}_0$  and  $\overline{BWS}_1$ , which are sampled with each set of 18-bit data words. Asserting the appropriate byte write select input during the data portion of a write latches the data being presented and writes it into the device. Deasserting the byte write select input during the data portion of a write enables the data stored in the device for that byte to remain unaltered. This feature can be used to simplify read, modify, or write operations to a byte write operation.

## **DDR Operation**

The CY7C2268KV18 enables high performance operation through high clock frequencies (achieved through pipelining) and DDR mode of operation. The CY7C2268KV18 requires two No Operation (NOP) cycle during transition from a read to a write cycle. At higher frequencies, some applications require third NOP cycle to avoid contention.

If a read occurs after a write cycle, address and data for the write are stored in registers. The write information is stored because the SRAM cannot perform the last word write to the array without conflicting with the read. The data stays in this register until the next write cycle occurs. On the first write cycle after the read(s), the stored data from the earlier write is written into the SRAM array. This is called a posted write.

If a read is performed on the same address on which a write is performed in the previous cycle, the SRAM reads out the most current data. The SRAM does this by bypassing the memory array and reading the data from the registers.

## **Depth Expansion**

Depth expansion requires replicating the  $\overline{LD}$  control signal for each bank. All other control signals can be common between banks as appropriate.

### Programmable Impedance

An external resistor, RQ, must be connected between the ZQ pin on the SRAM and  $V_{SS}$  to allow the SRAM to adjust its output driver impedance. The value of RQ must be 5 × the value of the intended line impedance driven by the SRAM. The allowable range of RQ to guarantee impedance matching with a tolerance of ±15% is between 175  $\Omega$  and 350  $\Omega$ , with  $V_{DDQ}$  = 1.5 V. The output impedance is adjusted every 1024 cycles upon power-up to account for drifts in supply voltage and temperature.

## **Echo Clocks**

Echo clocks are provided on the DDR II+ to simplify data capture on high speed systems. Two echo clocks are generated  $\underline{by}$  the DDR II+. CQ is referenced with respect to K and  $\overline{CQ}$  is referenced with respect to K. These are free-running clocks and are synchronized to the input clock of the DDR II+. The timing for the echo clocks is shown in the Switching Characteristics on page 23.

#### Valid Data Indicator (QVLD)

QVLD is provided on the DDR II+ to simplify data capture on high speed systems. The QVLD is generated by the DDR II+ device along with data output. This signal is also edge aligned with the echo clock and follows the timing of any data pin. This signal is asserted half a cycle before valid data arrives.

#### On-Die Termination (ODT)

These devices have an on-die termination feature for data inp<u>uts</u>  $(D_{[X:0]})$ , byte write selects  $(BWS_{[X:0]})$ , and input clocks (K and K). The termination resistors are integrated within the chip. The ODT range selection is enabled through ball R6 (ODT pin). The ODT termination tracks value of RQ where RQ is the resistor tied to the ZQ pin. ODT range selection is made during power-up initialization. A LOW on this pin selects a low range that follows RQ/3.33 for  $175 \Omega \leq RQ \leq 350 \Omega$  (where RQ is the resistor tied to ZQ pin). A HIGH on this pin selects a high range that follows RQ/1.66 for  $175 \Omega \leq RQ \leq 250 \Omega$  (where RQ is the resistor tied to ZQ pin). When left floating, a high range termination value is selected by default. For a detailed description on the ODT implementation, refer to the application note, *On-Die Termination for QDRII+/DDRII+ SRAMs*.

#### **PLL**

These chips use a PLL that is designed to function between 120 MHz and the specified maximum clock frequency. During power up, when the  $\overline{\text{DOFF}}$  is tied HIGH, the PLL is locked after 20  $\mu s$  of stable clock. The PLL can also be reset by slowing or stopping the input clock K and K for a minimum of 30 ns. However, it is not necessary to reset the PLL to lock to the desired frequency. The PLL automatically locks 20  $\mu s$  after a stable clock is presented. The PLL may be disabled by applying ground to the  $\overline{\text{DOFF}}$  pin. When the PLL is turned off, the device behaves in DDR I mode (with one cycle latency and a longer access time). For information, refer to the application note, PLL Considerations in QDRII/DDRII/QDRII+/DDRII+.

# **Application Example**

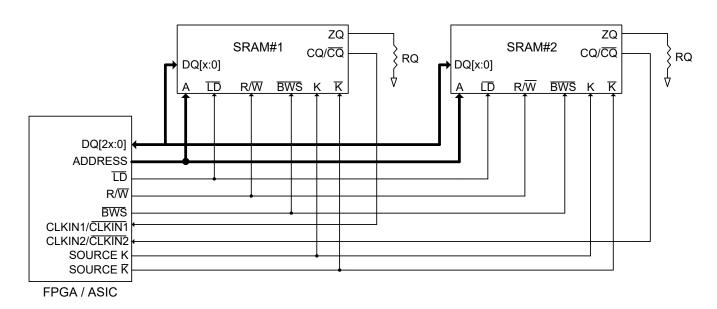

Figure 2 shows two DDR II+ used in an application.

Figure 2. Application Example (Width Expansion)

## **Truth Table**

The truth table for CY7C2268KV18 and CY7C2270KV18 follow. [4, 5, 6, 7, 8, 9]

| Operation                                                                                                              | K       | LD | R/W | DQ                                    | DQ                                          |

|------------------------------------------------------------------------------------------------------------------------|---------|----|-----|---------------------------------------|---------------------------------------------|

| Write cycle: Load address; wait one cycle; input write data on consecutive K and $\overline{K}$ rising edges.          | L–H     | L  | L   | D(A) at K(t + 1) ↑                    | D(A+1) at $\overline{K}$ (t + 1) $\uparrow$ |

| Read cycle: (2.5 cycle latency) Load address; wait two and half cycles; read data on consecutive K and K rising edges. | L–H     | L  | Н   | Q(A) at $\overline{K}(t + 2)\uparrow$ | Q(A+1) at K(t + 3) ↑                        |

| NOP: No operation                                                                                                      | L–H     | Н  | Х   | High Z                                | High Z                                      |

| Standby: Clock stopped                                                                                                 | Stopped | Х  | Х   | Previous state                        | Previous state                              |

## **Write Cycle Descriptions**

The write cycle description table for and CY7C2268KV18 follows. [4, 10]

| BWS <sub>0</sub> | BWS <sub>1</sub> | K   | K   | Comments                                                                                                                                                  |

|------------------|------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                | L                | L–H | 1   | During the data portion of a write sequence:<br>CY7C2268KV18 – both bytes (D <sub>[17:0]</sub> ) are written into the device.                             |

| L                | L                | I   | L–H | During the data portion of a write sequence:<br>CY7C2268KV18 – both bytes (D <sub>[17:0]</sub> ) are written into the device.                             |

| L                | Н                | L–H | ı   | During the data portion of a write sequence: CY7C2268KV18 – only the lower byte $(D_{[8:0]})$ is written into the device, $D_{[17:9]}$ remains unaltered. |

| L                | Н                | -   | L–H | During the data portion of a write sequence: CY7C2268KV18 – only the lower byte $(D_{[8:0]})$ is written into the device, $D_{[17:9]}$ remains unaltered. |

| Н                | L                | L–H | 1   | During the data portion of a write sequence: CY7C2268KV18 – only the upper byte $(D_{[17:9]})$ is written into the device, $D_{[8:0]}$ remains unaltered. |

| Н                | L                | -   | L–H | During the data portion of a write sequence: CY7C2268KV18 – only the upper byte $(D_{[17:9]})$ is written into the device, $D_{[8:0]}$ remains unaltered. |

| Н                | Н                | L–H | _   | No data is written into the devices during this portion of a write operation.                                                                             |

| Н                | Н                | _   | L–H | No data is written into the devices during this portion of a write operation.                                                                             |

## Notes

- X = "Don't Care," H = Logic HIGH, L = Logic LOW, ↑ represents rising edge.

Device powers up deselected with the outputs in a tri-state condition.

"A" represents address location latched by the devices when transaction was initiated. A + 1 represents the address sequence in the burst.

"t" represents the cycle at which a read/write operation is started. t + 1 and t + 2 are the first and second clock cycles succeeding the "t" clock cycle.

Data inputs are registered at K and K rising edges. Data outputs are delivered on K and K rising edges as well.

It is recommended that K = K = HIGH when clock is stopped. This is not essential, but permits most rapid restart by overcoming transmission line charging symmetrically.

Is based on a write cycle that was initiated in accordance with Truth Table. BWS<sub>0</sub>, BWS<sub>1</sub>, BWS<sub>2</sub>, and BWS<sub>3</sub> can be altered on different portions of a write cycle, as long as the setup and hold requirements are achieved.

# **Write Cycle Descriptions**

The write cycle description table for CY7C2270KV18 follows. [11, 12]

| BWS <sub>0</sub> | BWS <sub>1</sub> | BWS <sub>2</sub> | BWS <sub>3</sub> | K   | K   | Comments                                                                                                                                                 |

|------------------|------------------|------------------|------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                | L                | L                | L                | L–H | -   | During the data portion of a write sequence, all four bytes ( $D_{[35:0]}$ ) are written into the device.                                                |

| L                | L                | L                | L                | -   | L–H | During the data portion of a write sequence, all four bytes ( $D_{[35:0]}$ ) are written into the device.                                                |

| L                | Н                | Н                | Н                | L–H | -   | During the data portion of a write sequence, only the lower byte $(D_{[8:0]})$ is written into the device. $D_{[35:9]}$ remains unaltered.               |

| L                | Ι                | Η                | Η                | -   | L-H | During the data portion of a write sequence, only the lower byte $(D_{[8:0]})$ is written into the device. $D_{[35:9]}$ remains unaltered.               |

| Н                | L                | Н                | Н                | L–H | -   | During the data portion of a write sequence, only the byte $(D_{[17:9]})$ is written into the device. $D_{[8:0]}$ and $D_{[35:18]}$ remains unaltered.   |

| Н                | L                | Н                | Н                | -   | L–H | During the data portion of a write sequence, only the byte $(D_{[17:9]})$ is written into the device. $D_{[8:0]}$ and $D_{[35:18]}$ remains unaltered.   |

| Н                | Ι                | L                | Η                | L–H | 1   | During the data portion of a write sequence, only the byte $(D_{[26:18]})$ is written into the device. $D_{[17:0]}$ and $D_{[35:27]}$ remains unaltered. |

| Н                | Н                | L                | Н                | -   | L–H | During the data portion of a write sequence, only the byte $(D_{[26:18]})$ is written into the device. $D_{[17:0]}$ and $D_{[35:27]}$ remains unaltered. |

| Н                | Н                | Н                | L                | L–H | -   | During the data portion of a write sequence, only the byte $(D_{[35:27]})$ is written into the device. $D_{[26:0]}$ remains unaltered.                   |

| Н                | Н                | Н                | L                | _   | L–H | During the data portion of a write sequence, only the byte $(D_{[35:27]})$ is written into the device. $D_{[26:0]}$ remains unaltered.                   |

| Н                | Н                | Н                | Н                | L–H | _   | No data is written into the device during this portion of a write operation.                                                                             |

| Н                | Н                | Н                | Н                | -   | L–H | No data is written into the device during this portion of a write operation.                                                                             |

Document Number: 001-57845 Rev. \*I Page 10 of 31

<sup>11.</sup> X = "Don't Care," H = Logic HIGH, L = Logic LOW, ↑ represents rising edge.

12. Is based on a write cycle that was initiated in accordance with Truth Table on page 9. BWS<sub>0</sub>, BWS<sub>1</sub>, BWS<sub>2</sub>, and BWS<sub>3</sub> can be altered on different portions of a write cycle, as long as the set-up and hold requirements are achieved.

WKH ,'&2'( LQVWUXFWLRQ ,W LV DOVR OR LQVWUXFWLRQ LI WKH FRQWUROOMFWLEHSOOD

((( 6WDQGDUG

VWDQGDUG

, ( ( (

### PXVW EH OHIW XQFRQQHFWHG 8SRQ SRZHU XŠ, WKH GHYLFH FRPHV XS LQ D UHVHW VWDWHQWKHUFHUGHR ZLWWXKRWWKHI R YPU HWW FRHRZKHQ VHULDOO\ VKLILWLQJ G GHYLFH UHJLVWHU LV D VLQJOH ELW UHJLVW,HU WK DQG 7'2 SLQV 7KLV HQDEOHV VKLIWLQJ RI 7HVW \$FFHVV 3RUW ZLWK PLQLPDO SBIOVO\UFIKENVEV\HU6 FVZKHVQ /2: WKH % < 3\$66 LLRQQV WWW XHF WVF XWHG Test Clock 7KH WHVW FORFN LV XVHG RQO\ ZLWDKUHWHKHAZI\$ & FROWHIROOHU \$00 LQSXWV FDSWXUHG RQ WKH ULVLQJ HGJH RI 7&. \$00 RXWSXWV DUH GULYHQ IURP WKH IDOOLOJ HGJH RI 7&. 7KH ERXQGDU\ VFDQ UHJLVWHU LV FRQQHFY WKH IDOOLQJ HGJH RI 7&. RXWSXW SLQV RQ WKH 65\$0 6HYHUDO 1R &R LQFOXGHG LQ WKH VFDQ UHJLVWHU WR UH Test Mode Select (TMS) 7KH 706 LQSXW LV XVHG WR JLYH FRPPDGGY WKH 7\$3 FRQWUROOHU DQG LV VDPSOHG RQ WKH ULVLQJ HGJH 7RAH7 & RX70KOLDVUSLVQF PQ \ UEHHJLOMHWWYU LV ORDGHG XQFRQQHFWHG LIWKH 7\$3 LV QRW XV5HSQ L7QKSHXVSLQQGVRSXXVGSQXHVGUXSQJZKHQ WKH LQWHUQDOO\ UHVXOWLQJ LQ D ORJLF +&\*D+SØVAYVHO'5 VWDWH DQG LV WKHQ SODFHG \$LQV ZKHQ WKH FRQWUROOHU LV PRYHG W (;7(67 6\$03/(35(/2\$' DQG 6\$03/( = LQVWUXF Test Data-In (TDI) 7KH 7', SLQ LV XVHG WR VHULDOO\VLVQHSUXWHLXQYHOPVBWFPOSWAWHVWWKHLQHASWWHDOOWGVRXWS DQG FDQ EH FRQQHFWRHI © OWRRW WHK HL QUSHXVW 发发 10 0 U 7 16 17 DQ 2 U G M KL REZ CV SMCKJHH R U G H U L Q UHJLVWHU EHWZHHQF1K'ŖVDHQQGE7\'2WKWH LQVEYLUWXVFYDYUNRQFRVQKQDHWFWHG (DFK ELW FRUUHVSF LV ORDGHG LQWR WKH 7\$3 LQVWUXFWLRVQKHUHJ\$\$O & DIPNDRW FQHROPD WLRVQKRQHJLVW ORDGLQJ WKH LQVWUXF \$W3LR8QR CUMHUB YOW HOUQ G6WHRHA/H6% LV FRQQHFWHG WR 7'2 LDJUDP RQ SDJHLV LQWHUQDOO\ SXOOHG XS DQG FDQ EH XQFRQQHFWHG LIWKH 7\$3 LV XQXVHGldenoffication (ID)SRSegobleFDWLRQ FRQQHFWHG WR WOKOHWPERLYWW DOGG SKOULHRINDEVWHYLKH, UHJLVWHU LV ORDGHG ZLWK D YHQ GXULQJ WKH &DSWXUH '5 VWDWH ZKHQ WK Test Data-Out (TDO) ORDGHG LQ WKH LQVWUXFWLRQ UHJLRVWHU 7KH 7'2 RXWSXW SLQ LV XVHG WR VHULMDQQD\\65\$ARFDNQ&DFWDD RHWKLLRMPHVSKRHXW ZKHQ UHJLVWHUV 7KH R&WYSSK QVGLLVQ DFWYBLYQMWHKMVFFK LGUKHLQWY VFWDVDWWHH L7KKHDV, BURNQHLQ GROG RWK RIWKH 7\$3 VWDWH, OP NDWFklkkQFWLNZGH&RGHVLQQQRDDWLRQ GOHNZGWLEEHFGDNWQQRGII5GJUWWLNZQV 7KH RXWSXW FKDQJHV RQ WKH IDOOLQDJHGJH RI 7&. 7'2 LV FRQQHFWHG WR WQM/ OEHLDVVW6%LJRQILDLQF\DUHJLVWHU 7\$3,QVWUXFWLRQ 6HW 3HUIRUPLQJ D 7\$3 5HVHW (LJKW GLIIHUHQW HLQSVRWWWXEWHRQIWWKWWKH \$ UHVHW LV SHUIRUPHG E\√IRURUQULYP166ܱQ√VLMQU9XFWLRQ 191∃LIQ√DWWHLURQ\$ODDUCHFMR√DULXFWMIGR HGJHV RI 7&. 7KLV UHVHW GRHV QRW QRBFW WKHSB73KHUHDHWRRQVRHWHKHQVWUXFWL 65\$0 DQG FDQ EH SHUIRUPHG ZKLOH WK5H,66,5,5,0' LD/Q&SPHXU/DWWLQQRJW \$EWH XVHG 7KH RWK XS LQ D KLJK = VWDWH QVWUXFWLRQV DUH ORDGHG LQWRWW K5H 7\$3 VWDWH ZKHQ WKH LQVWUXFWLRQ UHJLVWH 7\$3 5HJLVWHUV 7 3 3 3 3 1 2 V W H O V 7 2 'X U L Q J W K L V V W D W H L Q V W U X F W L R Q V 5 H J L V W H U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R U V F W R WKH GDWD LQ DQG RIXVWW RFLUWFXXHLW65U\$.0H2W0QQQ\kRHQHQUVHVVUXPWVLRQ DIWHU LW LV VKELHIWHG

FDQ EH VHOHFWHG DWWKB WQ PUNHUWKKWWRWKDXPRD LQWR WKH 8SGDWH ,5 VWDWH LV VHULDOO\ ORDGHG LQWR WKH 7'D WDQ RQ WKH ULVLQJ HGJH RI 7&.

W LV SRVVLEOH WR RSHUDWH WKH 65.50 ZLWKRZYW3 XYLQWUW60HJ5.\*V LQ WWW &DSIHDWXUH 7R GLVDŒWHRWONHUT\$ 37 &F.RPXVWYEJO WJEJO WJEJO W ELWV DUH ORDGHG ZLWRWD EL 96 WR SUHYHQW FORFNLQJ RI WKH GJBYJJW LVROD WYERROW WHU LEDROD UWCHVW SDWK LQWHUQDOO\ SXOOHG XS DQG PD\ EH XQFRQQHFWHG YKHV PD\

7KH 7\$3 RSHUDWHV XXVI QH 86K Q SRZHU XS WKH LQVWUXFWLRQ

LQ WKHRXSVUHYHLEWLRQ

6 HULDO % RXQGDU\ 6 FistDuQjon Regrister

, 2 ORJLF OHYHOV

DOWHUQDWLYHO\ EHWRRUOROXHK WOHSSX VOID 9X SByblats y RegistleR U 7'2

'LVDEOLQJ WKH -7\$\* )HDWXUH

LV RXWSXW RQ RWQK HW K7 HH2 HHSDEQODE LRQI 7 &.

:KHQ WKH %<3\$66 LQVWUXFWLRQ LV @RDGHG

7KH (;7(67 LQVWUXFWLRQ GULYHV WKH SUH

WKH VVWHP RXWSXW SLQV 7KLV LQVWUX

#### **IDCODE**

35(/2\$' SODFHV DQ LEQWWHDDQQ GDDWWVKSH ODWF EHWZHHQ WKH 7', DQG 7'2 SLQV DQG VKL7IKWHV WKKLHW,L&Q2J'(RRXGVDVRDWRKUH WKH 6\$03/(DQG GHYLFH ZKHQ WKH 7\$3 FRQWUROOHU HORWFFIXUV WFIKEJF6XKULLIWYQ'WYOVW ZIMWHQ 7UKHHTXLU'HG '&2'(LQVWUXFWLRQLVORDGHGLQWRF1DVSXWHXLUDeN/GWRLDXXWFWLVLMFMDHSDUHHFNDDFDDFDDFBHGDDKDALDNWNDHGL SRZHU XS RU ZKHQHYHU WKH 7\$3 FRQWUROOHU LV VXSSOLHG D **BYPASS** 7HVW /RJLF 5HVHW VWDWH

#### SAMPLE 7

DQGWKH7\$3LVSO'BFVHWGDLWQHSDDWKKHLWEHLJVLVWHI 7KH 6\$03/( = LQVWUXFWLRQ FRQQHFWV WS/OB/BFEHFCXOE/GIDVUZ/HWHQD/OV/KUHHJ/L,VWS/GIG 7'2 SLQV EHWZHHQ WKH 7', DQG 7'2 SLQV ZKHQ W%K  $\pm$ 13\$66 EQQWURDW  $\pm$ 1RUQLLV  $\pm$ 10V  $\pm$ 10DW LW VKRUW 6KLIW '5 VWDWH 7KH 6\$03/( = FRPPDQGZ KSHXQV  $\pm$ 2 XVXXV  $\pm$ 3 XVX  $\pm$ 3 XVX  $\pm$ 4 XVX LQWR D KLJK = VWDWH XQWLO WKH &H[W FRPPDQG LV VXSSOLHG GXULQJ W EXTEST 8SGDWH .5 VWDWH

#### SAMPLE/PRELOAD

6\$03/(35(/2\$'LVDPDQGDWRU\LQVWUXETRWXQRGODU\KVHFQDQUHJLVWHUIRUVHULDODF WKH 6\$03/(35(/2\$' LQQWUDXEW ORDGHG'2LQQVRWKWHK6HKLIW'5 FRQWUROOHU VWDWH LQVWUXFWLRQ`UHJE1R10Q1HWW1PD0Q0GHWKLHV5L\$C8WKH &DSWXUH' VWDWH DVQDSVKRWRIGDWDRQWKHHGLE数15是70P14511045F87W1FSLQVLVFDSWX LQ WKH ERXQGDU\ VFDQ UHJLVWHU , ((( 6 W D Q G D U G D Q G D VP H V W KFDRVQ WWUKRHO7O\$H3U E H 7KH XVHU PXVW EH DZDUH WKDW WKH 7\$V3FFRXQVWWK6OMRADPSYMLFKYMADYGOMRADOGH RSHUDWH DW D IUHTXHQF\ XS WR 0+7KAKELPOXHQYOMOHOU KOODFDOQFOQHRUFILMODOOHOU KOOD OO ROFD WHO RSHUDWHV PRUH WKODIQ LOVQX BE LIGHOV WRHEP % KHFQ XWKLW KHLWKHLOHO FOOOHG WKLW 3 H [WILV DODUJH GLIIHUHQFH LQ WKH FQWKFDWO ID WK HV SSIRYOKL IEO WHILL WHU C GXULQJ WKH &DSWXUH '5 VWDWH DQ LQWXXAW7\$R3UFRXQWW8VXXVOXAQGHUWRELVUAHFWOW FRQ WUDQVLWLRQ 7KH 7\$3 PD\ WKHQ WU\ WA EFXOS WSYLUHY DZYKIHO DOOK AKLOHO LO HQWHU WKHUH LV QR JXDUBIQWDHOHXHDVWKWDRWWLKYRXFWDSSXWXVLEHXG :KHQW/28.ODMFKHLWWELKHRXWSXW 5HSHDWDEOH UHVXOWV PD\ QRW EH SRVWLJEOHFRQGLWLRQ 7R JXDUDQWHH WKDWFWCAHUERKYQVGBUU FÐAŞLWXLEHW YHKÐ EHULLON VEKHHOSNO3/(35(/2\$'FRUUHFW YDOXH RID VLJQDO WKH 65\$(97)/β-μΦΡΡΟΧΟΚΗ ΕΦΟΚΗΡΕΦΟΥΝΙΡΗΘΟΣΟΝΚΗ Θ

ORQJ HQRXJK WR PHHW WKH 7\$3 FRQOVUROXXQDHQJVWFQ-FVXLUHWVHWXXDQXQJXVXKURQQJ 8SGD WLPHYDONG, W7KH 65\$0 FORPELNIKLWQ SOXRW EH FOR W XWKHOW VKLIW UHJLVWHU FHOOKOIDWFKHFRUÜHFWO\LI WKHUH LV QR ZD\ LOFODROFNWH Q WR W WO SWO W WKHO WHO HO W GXULQJ D 6\$03/(35(/2\$RQQVWWKEW LV DQXLWS)XW 4LEWX VSLQV 1RWH WKDW WWKEM ELW VWLOO SRVVLEOH WR FDSWXUH DOOKHRWHXHWSXWVQRAD WQRAHMSHRSPHDQJQRBMDWHWZKHQ YDOXH RIWKH R&DSDVQXGUBIG LQUWKHDEQRIXHQAEDQWWJUROOHUWLVRLIQ FW54HVFHW VWDWH

\$IWHU WKH GDWD LV FDSWXUHG LOWELV SRVYLEOH WR VKLIW RXW WKH GDW SXWWLQJ WKH 7\$3 LQWR WKH 6KLIW U5\ V W 95 WP 1 7KLV SODFHV WKH ERXQGD VFDQ UHJLVWKH EHWDZQHGHQ'2WSLQV 7KHVH LQVWUXFWLORHQPVHQWHHQQEWWLPDSJH UH IXWXUH XVH WRKOHRWY KOZHWUXFWLRQV

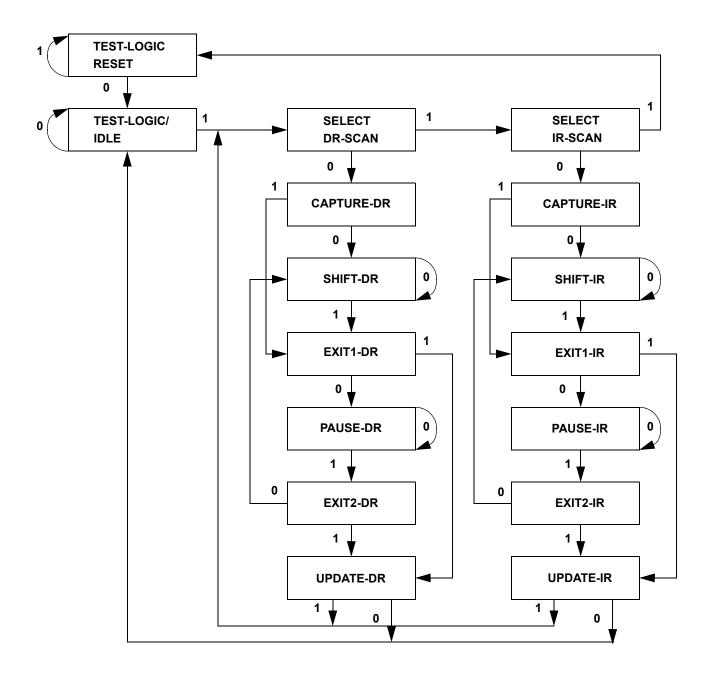

# **TAP Controller State Diagram**

The state diagram for the TAP controller follows. [13]

#### Note

13. The 0/1 next to each state represents the value at TMS at the rising edge of TCK.

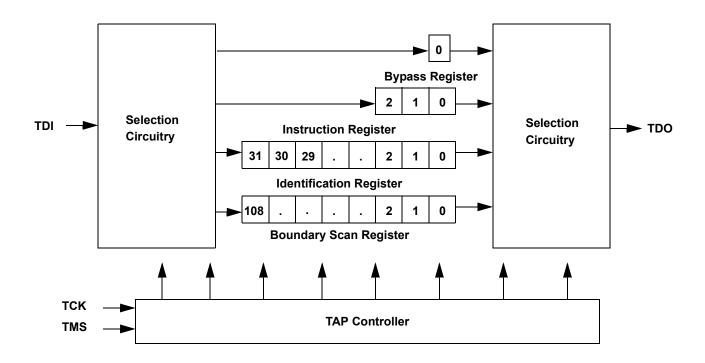

# **TAP Controller Block Diagram**

## **TAP Electrical Characteristics**

Over the Operating Range

| Parameter [14, 15, 16] | Description                   | Test Conditions            | Min                  | Max                   | Unit |

|------------------------|-------------------------------|----------------------------|----------------------|-----------------------|------|

| V <sub>OH1</sub>       | Output HIGH voltage           | $I_{OH} = -2.0 \text{ mA}$ | 1.4                  | -                     | V    |

| V <sub>OH2</sub>       | Output HIGH voltage           | I <sub>OH</sub> = -100 μA  | 1.6                  | -                     | V    |

| V <sub>OL1</sub>       | Output LOW voltage            | I <sub>OL</sub> = 2.0 mA   | -                    | 0.4                   | V    |

| $V_{OL2}$              | Output LOW voltage            | I <sub>OL</sub> = 100 μA   | -                    | 0.2                   | V    |

| V <sub>IH</sub>        | Input HIGH voltage            |                            | $0.65 \times V_{DD}$ | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>        | Input LOW voltage             |                            | -0.3                 | $0.35 \times V_{DD}$  | V    |

| I <sub>X</sub>         | Input and output load current | $GND \le V_I \le V_{DD}$   | <b>–</b> 5           | 5                     | μΑ   |

<sup>14.</sup> These characteristics pertain to the TAP inputs (TMS, TCK, TDI and TDO). Parallel load levels are specified in the Electrical Characteristics on page 20.

<sup>15.</sup> Overshoot:  $V_{IH(AC)} < V_{DDQ} + 0.3 \text{ V}$  (Pulse width less than  $t_{CYC}/2$ ), Undershoot:  $V_{IL(AC)} > -0.3 \text{ V}$  (Pulse width less than  $t_{CYC}/2$ ). 16. All voltage referenced to ground.

# **TAP AC Switching Characteristics**

Over the Operating Range

| Parameter [17, 18 | Description                   | Min | Max | Unit |

|-------------------|-------------------------------|-----|-----|------|

| t <sub>TCYC</sub> | TCK clock cycle time          | 50  | -   | ns   |

| t <sub>TF</sub>   | TCK clock frequency           | _   | 20  | MHz  |

| t <sub>TH</sub>   | TCK clock HIGH                | 20  | -   | ns   |

| t <sub>TL</sub>   | TCK clock LOW                 | 20  | -   | ns   |

| Setup Times       |                               | •   |     |      |

| t <sub>TMSS</sub> | TMS set-up to TCK clock rise  | 5   | _   | ns   |

| t <sub>TDIS</sub> | TDI set-up to TCK clock rise  | 5   | _   | ns   |

| t <sub>CS</sub>   | Capture set-up to TCK rise    | 5   | -   | ns   |

| Hold Times        |                               | •   |     |      |

| t <sub>TMSH</sub> | TMS hold after TCK clock rise | 5   | _   | ns   |

| t <sub>TDIH</sub> | TDI hold after clock rise     | 5   | _   | ns   |

| t <sub>CH</sub>   | Capture hold after clock rise | 5   | _   | ns   |

| Output Times      |                               | •   |     |      |

| t <sub>TDOV</sub> | TCK clock LOW to TDO valid    | _   | 10  | ns   |

| t <sub>TDOX</sub> | TCK clock LOW to TDO invalid  | 0   | _   | ns   |

**Notes**17.  $t_{CS}$  and  $t_{CH}$  refer to the setup and hold time requirements of latching data from the boundary scan register.

18. Test conditions are specified using the load in TAP AC Test Conditions.  $t_R/t_F = 1$  ns.

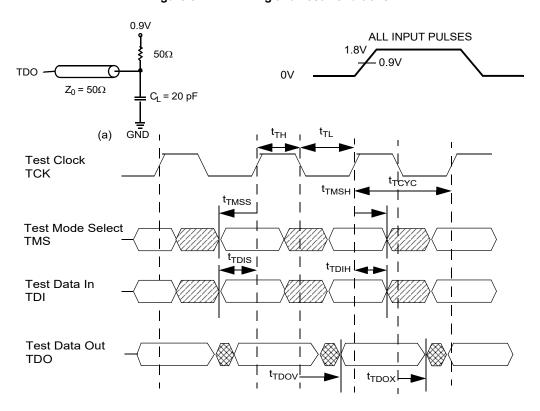

# **TAP Timing and Test Conditions**

Figure 3 shows the TAP timing and test conditions. [19]

Figure 3. TAP Timing and Test Conditions

#### Notes

<sup>19.</sup> Test conditions are specified using the load in TAP AC Test Conditions.  $t_{\mbox{\scriptsize R}}/t_{\mbox{\scriptsize F}}$  = 1 ns.

# **Identification Register Definitions**

| Instruction Field         | Value             |                   | Description                                  |

|---------------------------|-------------------|-------------------|----------------------------------------------|

|                           | CY7C2268KV18      | CY7C2270KV18      | Description                                  |

| Revision number (31:29)   | 000               | 000               | Version number.                              |

| Cypress device ID (28:12) | 11010111000010111 | 11010111000100111 | Defines the type of SRAM.                    |

| Cypress JEDEC ID (11:1)   | 00000110100       | 00000110100       | Allows unique identification of SRAM vendor. |

| ID register presence (0)  | 1                 | 1                 | Indicates the presence of an ID register.    |

# **Scan Register Sizes**

| Register Name | Bit Size |

|---------------|----------|

| Instruction   | 3        |

| Bypass        | 1        |

| ID            | 32       |

| Boundary scan | 109      |

# **Instruction Codes**

| Instruction    | Code | Description                                                                                                                                      |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTEST         | 000  | Captures the input and output ring contents.                                                                                                     |

| IDCODE         | 001  | Loads the ID register with the vendor ID code and places the register between TDI and TDO. This operation does not affect SRAM operation.        |

| SAMPLE Z       | 010  | Captures the input and output contents. Places the boundary scan register between TDI and TDO. Forces all SRAM output drivers to a high Z state. |

| RESERVED       | 011  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| SAMPLE/PRELOAD | 100  | Captures the input and output ring contents. Places the boundary scan register between TDI and TDO. Does not affect the SRAM operation.          |

| RESERVED       | 101  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| RESERVED       | 110  | Do Not Use: This instruction is reserved for future use.                                                                                         |

| BYPASS         | 111  | Places the bypass register between TDI and TDO. This operation does not affect SRAM operation.                                                   |

Document Number: 001-57845 Rev. \*I Page 17 of 31

# **Boundary Scan Order**

| Bit # | Bump ID |

|-------|---------|

| 0     | 6R      |

| 1     | 6P      |

| 2     | 6N      |

| 3     | 7P      |

| 4     | 7N      |

| 5     | 7R      |

| 6     | 8R      |

| 7     | 8P      |

| 8     | 9R      |

| 9     | 11P     |

| 10    | 10P     |

| 11    | 10N     |

| 12    | 9P      |

| 13    | 10M     |

| 14    | 11N     |

| 15    | 9M      |

| 16    | 9N      |

| 17    | 11L     |

| 18    | 11M     |

| 19    | 9L      |

| 20    | 10L     |

| 21    | 11K     |

| 22    | 10K     |

| 23    | 9J      |

| 24    | 9K      |

| 25    | 10J     |

| 26    | 11J     |

| 27    | 11H     |

| D:4 # | Duman ID |

|-------|----------|

| Bit # | Bump ID  |

| 28    | 10G      |

| 29    | 9G       |

| 30    | 11F      |

| 31    | 11G      |

| 32    | 9F       |

| 33    | 10F      |

| 34    | 11E      |

| 35    | 10E      |

| 36    | 10D      |

| 37    | 9E       |

| 38    | 10C      |

| 39    | 11D      |

| 40    | 9C       |

| 41    | 9D       |

| 42    | 11B      |

| 43    | 11C      |

| 44    | 9B       |

| 45    | 10B      |

| 46    | 11A      |

| 47    | 10A      |

| 48    | 9A       |

| 49    | 8B       |

| 50    | 7C       |

| 51    | 6C       |

| 52    | 8A       |

| 53    | 7A       |

| 54    | 7B       |

| 55    | 6B       |

| Bit # | Bump ID |  |

|-------|---------|--|

| 56    | 6A      |  |

| 57    | 5B      |  |

| 58    | 5A      |  |

| 59    | 4A      |  |

| 60    | 5C      |  |

| 61    | 4B      |  |

| 62    | 3A      |  |

| 63    | 2A      |  |

| 64    | 1A      |  |

| 65    | 2B      |  |

| 66    | 3B      |  |

| 67    | 1C      |  |

| 68    | 1B      |  |

| 69    | 3D      |  |

| 70    | 3C      |  |

| 71    | 1D      |  |

| 72    | 2C      |  |

| 73    | 3E      |  |

| 74    | 2D      |  |

| 75    | 2E      |  |

| 76    | 1E      |  |

| 77    | 2F      |  |

| 78    | 3F      |  |

| 79    | 1G      |  |

| 80    | 1F      |  |

| 81    | 3G      |  |

| 82    | 2G      |  |

| 83    | 1H      |  |

| ·     |         |  |

| Bit # | Bump ID  |

|-------|----------|

| 84    | 1J       |

| 85    | 2J       |

| 86    | 3K       |

| 87    | 3J       |

| 88    | 2K       |

| 89    | 1K       |

| 90    | 2L       |

| 91    | 3L       |

| 92    | 1M       |

| 93    | 1L       |

| 94    | 3N       |

| 95    | 3M       |

| 96    | 1N       |

| 97    | 2M       |

| 98    | 3P       |

| 99    | 2N       |

| 100   | 2P       |

| 101   | 1P       |

| 102   | 3R       |

| 103   | 4R       |

| 104   | 4P       |

| 105   | 5P       |

| 106   | 5N       |

| 107   | 5R       |

| 108   | Internal |

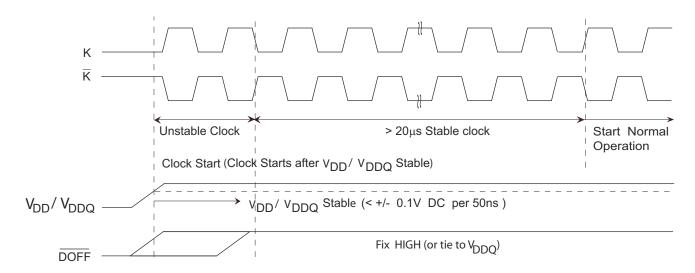

## Power Up Sequence in DDR II+ SRAM

DDR II+ SRAMs must be powered up and initialized in a predefined manner to prevent undefined operations.

## **Power Up Sequence**

- Apply power and drive DOFF either HIGH or LOW (all other inputs can be HIGH or LOW).

- □ Apply  $V_{DD}$  before  $V_{DDQ}$ .

□ Apply  $\underline{V_{DDQ}}$  before  $V_{REF}$  or at the same time as  $V_{REF}$ .

□ Drive DOFF HIGH.

- Provide stable DOFF (HIGH), power and clock (K, K) for 20 µs to lock the PLL

## **PLL Constraints**

- PLL uses K clock as its synchronizing input. The input must have low phase jitter, which is specified as  $t_{\mbox{\scriptsize KC Var}}$

- The PLL functions at frequencies down to 120 MHz.

- If the input clock is unstable and the PLL is enabled, then the PLL may lock onto an incorrect frequency, causing unstable SRAM behavior. To avoid this, provide 20 µs of stable clock to relock to the desired clock frequency.

Figure 4. Power Up Waveforms