## +2.5V Low-Power Precision Voltage Reference

REF43

### 1.0 SCOPE

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein.

The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. http://www.analog.com/aerospace

This data sheet specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at <a href="https://www.analog.com/REF43">www.analog.com/REF43</a>

### **2.0 Part Number**. The complete part number(s) of this specification follow:

| Part Number | <u>Description</u>                                            |

|-------------|---------------------------------------------------------------|

| REF43-803J  | +2.5V Low-Power Precision Voltage Reference                   |

| REF43-803L  | +2.5V Low-Power Precision Voltage Reference                   |

| REF43-803RC | +2.5V Low-Power Precision Voltage Reference                   |

| REF43-803Z  | +2.5V Low-Power Precision Voltage Reference                   |

| REF43R803J  | Radiation Tested, +2.5V Low-Power Precision Voltage Reference |

| REF43R803L  | Radiation Tested, +2.5V Low-Power Precision Voltage Reference |

| REF43R803RC | Radiation Tested, +2.5V Low-Power Precision Voltage Reference |

| REF43R803Z  | Radiation Tested, +2.5V Low-Power Precision Voltage Reference |

#### 2.1 Case Outline

| <u>Letter</u> | Descriptive designator <sup>1</sup> | Case Outline (Lead Finish per MIL-PRF-38535) |

|---------------|-------------------------------------|----------------------------------------------|

| J             | MACY1-X8                            | 8-Lead Can                                   |

| L             | GDFP1-F10                           | 10-lead cerpac                               |

| RC            | CQCC1-N20                           | 20-Terminal leadless chip carrier            |

| Z             | GDIP1-T8                            | 8-Lead ceramic dual-in-line package (CERDIP) |

|               | <sup>1</sup> See MIL-STD-1835       |                                              |

#### 3.0 Absolute Maximum Ratings. (T<sub>A</sub> = 25°C, unless otherwise noted)

| Supply voltage                         | 40V           |

|----------------------------------------|---------------|

| Power dissipation                      | 500mW         |

| Output short circuit duration          | Indefinite    |

| Storage Temperature range              |               |

| Operating temperature range            | 55° to +125°C |

| Lead temperature (soldering, 60 sec)   | +300°C        |

| Junction Temperature (T <sub>J</sub> ) | +175°C        |

ASD0011149 Rev. M Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2016 Analog Devices, Inc. All rights reserved.

## REF43

## 3.1 Thermal Characteristics:

| Package Type       | Junction-to-Case $(\Theta_{JC})$ | Junction-to-Ambient $(\Theta_{JA})$ | Units    |

|--------------------|----------------------------------|-------------------------------------|----------|

| таскаде турс       | ( 3.c)                           | ( C JA)                             | Offics   |

| J (TO-99 Package)  | 45                               | 150                                 | °C/W Max |

| L (CERPAC Package) | 22                               | 141                                 | °C/W Max |

| RC (LCC Package)   | 35                               | 110                                 | °C/W Max |

| Z (CERDIP Package) | 26                               | 120                                 | °C/W Max |

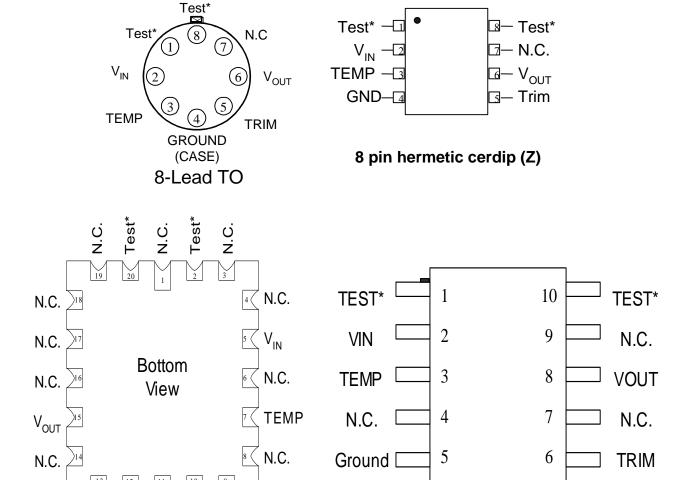

Figure 1 - <u>Terminal connections</u>.

\* Reserved for factory testing. Make no electrical connection to these pins.

10 lead CERPAC

GND

Trim

20-Terminal LCC

#### **4.0 Electrical Table**: See notes at end of table

|                                                    |                   | Table I                       |          |               |              |              |        |

|----------------------------------------------------|-------------------|-------------------------------|----------|---------------|--------------|--------------|--------|

| Parameter                                          | Symbol            | Conditions <u>1</u> /         | Package  | Sub-<br>group | Limit<br>Min | Limit<br>Max | Units  |

| Output voltage                                     | Vo                |                               |          | 1             | 2.4975       | 2.5025       | V      |

|                                                    |                   |                               | ALL      | 2, 3          | 2.4950       | 2.5050       |        |

|                                                    |                   | M, D, L ,R                    | ALL      | 1             | 2.4900       | 2.5025       |        |

| Output voltage temperature co-efficient <u>3</u> / | TC <sub>vo</sub>  |                               | ALL      | 8             |              | 15           | ppm/°C |

| Temperature voltage output                         | V <sub>T</sub>    |                               |          | 1             | 0.54         | 0.58         | V      |

| <u>4</u> /                                         |                   |                               | ALL      | 2             | 0.72         | 0.78         |        |

|                                                    |                   |                               |          | 3             | 0.38         | 0.43         |        |

| Load regulation                                    | LD <sub>REG</sub> | I <sub>L</sub> = 0mA to 10mA  | J, Z     | 1             |              | 20           | ppm/mA |

|                                                    |                   |                               | J, Z, RC | 2, 3          |              | 40           |        |

|                                                    |                   |                               | L, RC    | 1             |              | 28           |        |

|                                                    |                   |                               | L        | 2, 3          |              | 50           |        |

|                                                    |                   | M, D, L, R                    | J, Z, RC | 1             |              | 60           |        |

|                                                    |                   |                               | L        | 1             |              | 70           |        |

| Line regulation                                    | LN <sub>REG</sub> | V <sub>IN</sub> = 4.5V to 40V | ALL      | 1             |              | 2            | ppm/V  |

|                                                    |                   |                               |          | 2, 3          |              | 3            |        |

|                                                    |                   | M, D, L, R                    | ALL      | 1             |              | 100          |        |

| Short circuit current 4/                           | I <sub>SC</sub>   | $V_{\text{O}} = 0V$           | ALL      | 1             |              | 100          | mA     |

|                                                    |                   |                               |          | 2, 3          |              | 120          |        |

| Supply current                                     | I <sub>SY</sub>   |                               | ALL      | 1             |              | 450          | μΑ     |

|                                                    |                   |                               |          | 2, 3          |              | 600          |        |

|                                                    |                   | M, D, L, R                    | ALL      | 1             |              | 450          |        |

| Output adjustment range 4/                         | $\Delta V_{TRIM}$ |                               | ALL      | 1             | ±3           |              | %      |

| Load current <u>2</u> /                            | $I_{\rm L}$       |                               | ALL      | 1, 2, 3       | 10           |              | mA     |

| Wideband output noise                              | enRMS             |                               | ALL      | 7             |              | 10           | μVRMS  |

#### TABLE I NOTES:

- 1 V<sub>IN</sub> = 5V, unless otherwise specified. NOTE: Output decoupling is not generally required or recommended on the REF43. In applications that require output decoupling, care will need to be taken when choosing the capacitor due to the ESR of the capacitor. If capacitors with very low ESR are chosen it may be necessary to add some additional resistance in series with the capacitor to limit the initial charge current when power is applied to the REF43. Adding series resistance when low ESR capacitors are used will help with the stability of the REF43 when power is applied over the entire temperature range. Contact ADI Aerospace applications for more detailed application information.

- 2 Guaranteed by Load regulation test.

- 3 Output voltage temperature coefficient is measured by the box method. The tempco is defined as the slope of the diagonal of a box drawn around the output voltage plotted against temperature. Vout is measured at Tmin and Tmax. The lowest of these readings is subtracted from the highest reading and the resulting difference is divided by (Tmax Tmin).

- 4 Not tested post-irradiation.

#### 4.1 **Electrical Test Requirements**:

| Table II                                |                                                         |  |  |  |

|-----------------------------------------|---------------------------------------------------------|--|--|--|

| Test Requirements                       | Subgroups (in accordance with MIL-PRF-38535, Table III) |  |  |  |

| Interim Electrical Parameters           | 1                                                       |  |  |  |

| Final Electrical Parameters             | 1, 2, 3, 8 <u>1</u> / <u>2</u> /                        |  |  |  |

| Group A Test Requirements               | 1, 2, 3, 7, 8                                           |  |  |  |

| Group C end-point electrical parameters | 1 <u>2</u> /                                            |  |  |  |

| Group D end-point electrical parameters | 1                                                       |  |  |  |

| Group E end-point electrical parameters | 1                                                       |  |  |  |

#### 4.2 Table III. Lifetest / Burn-in delta limits.

| Table III |              |             |         |       |

|-----------|--------------|-------------|---------|-------|

| TEST      | BURN-IN      | LIFETEST    | DELTA   |       |

| TITLE     | ENDPOINT     | ENDPOINT    | LIMIT   | UNITS |

| VO        | 2.50 ±0.0025 | 2.50 ±0.005 | ±0.0025 | V     |

| ISY       | 450          | 495         | ±45     | μΑ    |

#### 5.0 **Life Test/Burn-In Circuit:**

- HTRB is not applicable for this drawing.

- Burn-in is per MIL-STD-883 Method 1015 test condition B. 5.2

- 5.3 Steady state life test is per MIL-STD-883 Method 1005.

<sup>1/</sup> PDA applies to subgroup 1. Delta's excluded from PDA.2/ See table III for delta measurement parameters. See Table I for test conditions.

# REF43

| Rev | Description of Change                                                                                                              | Date           |

|-----|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Α   | Initiate                                                                                                                           | 26-May-00      |

| В   | Add subgroup 8 to table II, Add L package, update table III                                                                        | Mar. 27, 2001  |

| С   | Update web address. Table II – delete subgroup 7 from final electrical parameters and add subgroup 7 to Group A Test Requirements. | Feb. 14, 2002  |

| D   | Update web address. Delete burn-in circuit.                                                                                        | May 29, 2003   |

| E   | Changed CERPAC Load Regulation limit from 20ppm/mA to 28ppm/mA. Add package column on electrical table                             | Feb. 03, 2005  |

| F   | Update Table I Load Regulation specs                                                                                               | April 27,2006  |

| G   | Update Table I Load Regulation specs.                                                                                              | Feb. 13, 2007  |

| Н   | Update header/footer and add to 1.0 Scope description.                                                                             | Feb. 21, 2008  |

| I   | Add temperature junction (T <sub>J</sub> )+175°C to 3.0 Absolute Max. Ratings.                                                     | April 4, 2008  |

| J   | Correct typo in Section 2 part numbers to be "R803" parts.                                                                         | Sep. 5, 2008   |

| К   | Add application note on output capacitive load sensitivity when using low ESR capacitors.                                          | Oct. 5, 2012   |

| L   | Correct typo on Theta JC/JA symbol                                                                                                 | Oct. 15, 2012  |

| М   | Change Load Regulation limit for RC package for Sub Group 1                                                                        | March 30, 2016 |

www.analog.com