# **ON Semiconductor**

# Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and Onsemi. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# <u>LDO Voltage Regulator</u> - Adjustable CMOS

# 1 A

The CAT6243 is a low dropout CMOS voltage regulator providing up to 1000 mA of output current with fast response to load current and line voltage changes. CAT6243 offers a user adjustable output voltage from 0.8 V to 5.0 V and its low quiescent current make CAT6243 ideal for energy conscious designs. CAT6243 is available in a DPAK-5 5-lead packages and in a space saving 3 mm x 3 mm WDFN-6 package with a power pad for heat sinking to the PCB.

### **Features**

- Guaranteed 1000 mA Continuous Output Current

- V<sub>OUT</sub>: 0.8 V to 5.0 V

- Dropout Voltage of 350 mV Typical at 1000 mA

- ±2.0% Output Voltage Accuracy at Room Temperature

- No-load Ground Current of 70 μA Typical

- Full-load Ground Current of 140 μA Typical

- "Zero" Current Shutdown Mode

- Under Voltage Lockout

- Stable with Ceramic Output Capacitors

- Current Limit and Thermal Protection

- 4 and 5 Lead DPAK-5 and 3 mm x 3 mm WDFN-6 Power Packages

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- DSP Core and I/O Voltages

- FPGAs, ASICs

- PDAs, Mobile Phones, GPS

- Camcorders and Cameras

- Hard Disk Drives

# ON Semiconductor®

### www.onsemi.com

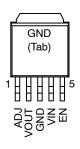

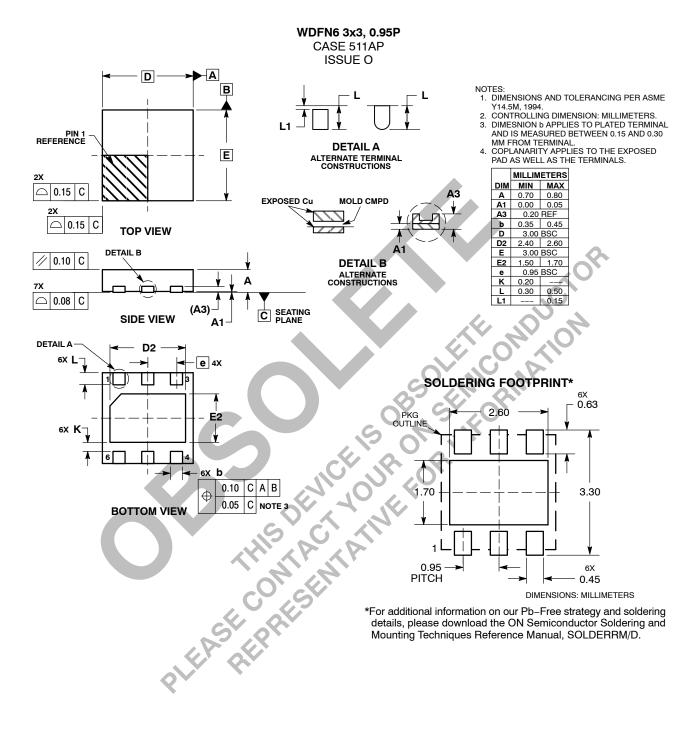

WDFN-6 3 x 3 mm CASE 511AP

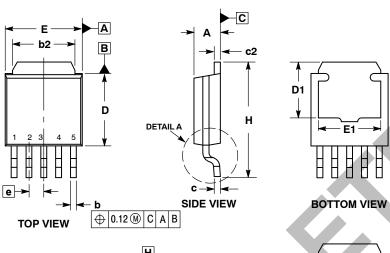

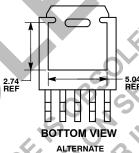

DPAK-5 TO-252 CASE 369AE

# PIN CONNECTIONS

(Top Views)

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 16 of this data sheet.

### **MARKING DIAGRAMS**

6243 = Specific Device Code

A = Assembly Location

XXX = Last Three Digits of

Assembly Lot Number

Y = Production Year

WW = Production Week (Two Digits)

■ = Pb-Free Package

\*Pb-Free indicator, "G" or microdot "■", may or may not be present.

= P (CAT) 6243 = Device Code = Output Voltage У W = Adjustable G = Pb-Free Package = Assembly Location Α L = Wafer Lot Υ = Year WW = Work Week

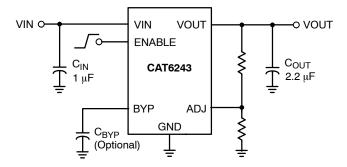

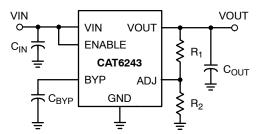

Figure 1. Application Schematic

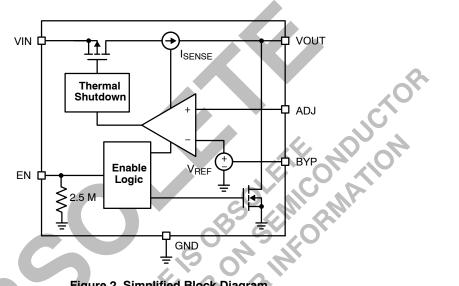

Figure 2. Simplified Block Diagram

**Table 1. PIN FUNCTION DESCRIPTION**

| Pin#   | Pin #    |                  | S C (1)                                                                                                                                                                                                                                                                           |

|--------|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDFN-6 | DPAK-5-5 | Pin Name         | Description                                                                                                                                                                                                                                                                       |

| 1      | 5        | EN               | The Enable Input. An active HIGH input, turning ON the LDO. This input should be tied to $V_{IN}$ if the LDO is not intended to be shut off during normal operation. A pull–down 2.5 M $\Omega$ resistor maintains the circuit in the OFF state if the pin is left open.          |

| 2, PAD | 3, TAB   | GND              | Power Supply Ground; Device Substrate. The center pad is internally connected to Ground and as such can cause short circuits to signal traces running beneath the IC. This pad is intended for heat sinking the IC to the PCB and is typically connected to the PCB ground plane. |

| 3      | NC       | BYP              | Bypass input. Placing a capacitor of 100 pF to 470 pF between BYP and ground reduces noise on V <sub>OUT</sub> . This capacitor is optional and it increases the turn-on time.                                                                                                    |

| 4      | 2        | V <sub>OUT</sub> | Regulated Output Voltage. A protection block eliminates any current flow from output to input if $V_{OUT} > V_{IN}$ .                                                                                                                                                             |

| 5      | 1        | ADJ              | Output Voltage Adjust Input. This input ties to the common point of a resistor divider which determines the regulator's output voltage. See Applications section for details on selecting resistor values.                                                                        |

| 6      | 4        | V <sub>IN</sub>  | Positive Power Supply Input. Supplies power for $V_{OUT}$ as well as the regulator's internal circuitry.                                                                                                                                                                          |

**Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                         | Symbol              | Value                                                           | Unit |

|--------------------------------------------------------------------------------|---------------------|-----------------------------------------------------------------|------|

| Input Voltage Range (Note 1)                                                   | V <sub>IN</sub>     | -0.3 to 6.0                                                     | V    |

| Output Voltage Range                                                           | V <sub>OUT</sub>    | -0.3 to 6.0                                                     | V    |

| Enable Input Range                                                             | EN                  | -0.3 to 5.5 V or (V <sub>IN</sub> + 0.3),<br>whichever is lower | V    |

| Adjust Input Range                                                             | ADJ                 | -0.3 to 5.5 V                                                   | V    |

| Bypass Input Range                                                             | BYP                 | -0.3 to 5.5 V or (V <sub>IN</sub> + 0.3),<br>whichever is lower | V    |

| Power Dissipation                                                              | PD                  | Internally Limited                                              | mW   |

| Maximum Junction Temperature                                                   | T <sub>J(max)</sub> | 150                                                             | °C   |

| Storage Temperature Range                                                      | T <sub>STG</sub>    | -65 to 150                                                      | °C   |

| ESD Capability, Human Body Model (Note 2)                                      | ESD <sub>HBM</sub>  | 2                                                               | kV   |

| ESD Capability, Machine Model (Note 2)                                         | ESD <sub>MM</sub>   | 200                                                             | V    |

| Lead Temperature Soldering Reflow (SMD Styles Only), Pb-Free Versions (Note 3) | T <sub>SLD</sub>    | 260                                                             | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACŤERISTIS and APPLICATION INFORMATION for Safe Operating range.

- 2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114) ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

Table 3. THERMAL CHARACTERISTICS

| Rating                                                                            | Value | Unit |

|-----------------------------------------------------------------------------------|-------|------|

| Thermal Characteristics, WDFN6, 3x3 mm                                            |       | °C/W |

| Thermal Resistance, Junction-to-Air: 1 in²/1 oz. copper (Note 4)                  | 55    |      |

| Thermal Reference, Junction-to-Case (Note 4)                                      | 10    |      |

| Thermal Characteristics, DPAK-5                                                   |       | °C/W |

| Thermal Resistance, Junction-to-Air: 1 in²/1 oz. copper (Note 4) R <sub>θJA</sub> | 60    |      |

| Thermal Reference, Junction-to-Tab (Note 4) $$R_{\psi JT}$$                       | 4.3   |      |

<sup>4.</sup> Values based on copper area of 650 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

# Table 4. OPERATING RANGES (Note 5)

|                        | Rating                   | Symbol           | Min        | Max        | Unit |

|------------------------|--------------------------|------------------|------------|------------|------|

| Input Voltage (Note 6) | CAT6243-ADJ<br>CAT6243DC | $V_{IN}$         | 1.8<br>1.8 | 5.0<br>5.5 | ٧    |

| Output Current         |                          | I <sub>OUT</sub> | 0.1        | 1000       | mA   |

| Output Voltage         |                          | V <sub>OUT</sub> | 0.8        | 5.0        | V    |

| Ambient Temperature    | <b>X</b> .               | T <sub>A</sub>   | -40        | 85         | °C   |

<sup>5.</sup> Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating range.

<sup>6.</sup> Minimum  $V_{IN\ MIN}$  = 1.8 V or  $(V_{OUT} + V_{DO})$ , whichever is higher.

**Table 5. ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = ( $V_{OUT}$  + 1 V) or  $V_{IN\_MIN}$ , whichever is higher,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 2.2  $\mu$ F, for typical values  $T_A$  = 25°C, for **Bold** values  $T_A$  = -40°C to 85°C; unless otherwise noted.)

| Symbol                | Parameter                                                    | Conditions                                                                                                                  | Min                            | Тур      | Max                | Unit   |

|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|--------------------|--------|

| INPUT / OU            | TPUT                                                         |                                                                                                                             |                                |          | <u>I</u>           |        |

| V <sub>OUT</sub>      | Output Voltage Range CAT6243-ADJ CAT6243DC                   |                                                                                                                             | 0.8<br>0.8                     |          | 4.5<br>5.0         | V      |

| V <sub>OUT-ACC</sub>  | Output Voltage Accuracy CAT6243-ADJ CAT6243DC CAT6243DC      | Initial accuracy, I <sub>OUT</sub> = 1 mA                                                                                   | - <b>2</b><br>-2<br>- <b>3</b> |          | +2<br>+2<br>+3     | %      |

| $V_{ADJ}$             | Voltage at ADJ input                                         |                                                                                                                             | 0.784                          | 0.8      | 0.816              | V      |

| TC <sub>OUT</sub>     | Output Voltage Temp. Coefficient<br>CAT6243-ADJ<br>CAT6243DC |                                                                                                                             |                                | 25<br>50 |                    | ppm/°C |

| I <sub>OUT</sub>      | Output Current                                               |                                                                                                                             | 0.0001                         | 1        |                    | Α      |

| V <sub>R-LINE</sub>   | Line Regulation                                              | $V_{IN} = V_{OUT} + 1.0 \text{ V to}$<br>$V_{IN(max)}$ , $I_{OUT} = 10 \text{ mA}$<br>$V_{IN} = V_{OUT} + 1.0 \text{ V to}$ | -0.2<br>-0.35                  | ±0.05    | 0.2<br><b>0.35</b> | %/V    |

|                       |                                                              | $V_{IN(max)}$ , $I_{OUT} = 10 \text{ mA}$                                                                                   | -0.00                          | ć        | 0,00               |        |

| $V_{R-LOAD}$          | Load Regulation                                              | I <sub>OUT</sub> = 100 μA to 1000 mA<br>I <sub>OUT</sub> = 100 μA to 1000 mA                                                | de.                            | 1.5      | 2                  | %      |

| V <sub>DO</sub>       | V <sub>OUT</sub> = 1.2 V                                     | I <sub>OUT</sub> = 300 mA                                                                                                   |                                | 6        | 600                | mV     |

| 20                    | V <sub>OUT</sub> = 2.5 V CAT6243–ADJ<br>CAT6243DC            | $T_A = 25$ °C                                                                                                               | 110                            | IDI      | 110<br>130         |        |

|                       | V <sub>OUT</sub> = 3.3 V                                     | 000                                                                                                                         |                                |          | 85                 |        |

|                       | V <sub>OUT</sub> = 1.2 V CAT6243–ADJ<br>CAT6243DC            | I <sub>OUT</sub> = 1 A<br>T <sub>A</sub> = 25°C                                                                             | . (O)                          |          | 625<br>650         |        |

|                       | V <sub>OUT</sub> = 2.5 V CAT6243-ADJ<br>CAT6243DC            | ck a a                                                                                                                      |                                |          | 350<br>400         |        |

|                       | V <sub>OUT</sub> = 3.3 V                                     | 110 M. 50.                                                                                                                  |                                |          | 275                |        |

| $I_{ADJ}$             | ADJ Input Current                                            | 67 10 61                                                                                                                    |                                |          | 100                | nA     |

| $I_{GND}$             | Ground Current                                               | I <sub>OUT</sub> = 0 μA                                                                                                     |                                | 70       |                    | μΑ     |

|                       |                                                              | $I_{OUT} = 0 \mu A$                                                                                                         |                                |          | 100                |        |

|                       |                                                              | I <sub>OUT</sub> = 1000 mA                                                                                                  |                                | 140      | 200                |        |

|                       |                                                              | I <sub>OUT</sub> = 1000 mA                                                                                                  |                                |          | 250                |        |

| I <sub>GND-SD</sub>   | Shutdown Ground Current CAT6243-ADJ CAT6243DC                | V <sub>EN</sub> < 0.4 V                                                                                                     |                                |          | 2<br>5             | μΑ     |

| ISC                   | Output short circuit current limit                           | V <sub>OUT</sub> = 0 V                                                                                                      |                                | 900      |                    | mA     |

| PSRR AND              | NOISE                                                        |                                                                                                                             |                                |          |                    |        |

| PSRR                  | Power Supply Rejection Ratio<br>CAT6243                      | f = 1 kHz, BYP = 470 pF,<br>I <sub>OUT</sub> = 10 mA                                                                        |                                | 54       |                    | dB     |

|                       |                                                              | f = 20 kHz, BYP = 470 pF,<br>I <sub>OUT</sub> = 10 mA                                                                       |                                | 42       |                    |        |

| e <sub>N</sub>        | Output Noise Voltage for 1.8 V output                        | BW = 10 Hz to 100 kHz<br>BYP = 470 pF, I <sub>OUT</sub> = 10 mA                                                             |                                | 45       |                    | μVrms  |

| UVLO, R <sub>OU</sub> | T AND ESR                                                    |                                                                                                                             |                                |          |                    |        |

| V <sub>UVLO</sub>     | Under voltage lockout threshold                              |                                                                                                                             |                                | 1.65     | 1.75               | V      |

| R <sub>OUT-SH</sub>   | ON resistance of Discharge Transistor                        |                                                                                                                             |                                | 150      |                    | Ω      |

| ESR                   | C <sub>OUT</sub> equivalent series resistance                |                                                                                                                             | 5                              |          | 500                | mΩ     |

<sup>7.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}C$ . Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

**Table 5. ELECTRICAL CHARACTERISTICS** ( $V_{IN}$  = ( $V_{OUT}$  + 1 V) or  $V_{IN\_MIN}$ , whichever is higher,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 2.2  $\mu$ F, for typical values  $T_A$  = 25°C, for **Bold** values  $T_A$  = -40°C to 85°C; unless otherwise noted.)

| Symbol           | Parameter                 | Conditions                                | Min | Тур  | Max | Unit |

|------------------|---------------------------|-------------------------------------------|-----|------|-----|------|

| ENABLE IN        | PUT                       |                                           |     |      |     |      |

| $V_{HI}$         | Logic High Level          | V <sub>IN</sub> = 1.8 to 5.5 V            | 1.6 |      |     | V    |

| V <sub>LO</sub>  | Logic Low Level           | V <sub>IN</sub> = 1.8 to 5.5 V            |     |      | 0.4 | V    |

| I <sub>EN</sub>  | Enable Input Current      | V <sub>EN</sub> = 0.4 V                   |     | 0.15 | 1   | μΑ   |

|                  |                           | V <sub>EN</sub> = V <sub>IN</sub> = 2.5 V |     | 1    | 3   |      |

| R <sub>EN</sub>  | Enable pull-down resistor |                                           |     | 2.5  |     | ΜΩ   |

| TIMING           |                           |                                           |     |      |     |      |

| T <sub>ON</sub>  | Turn-On Time              | C <sub>BYP</sub> = 0 pF                   |     | 230  |     | μs   |

|                  |                           | C <sub>BYP</sub> = 470 pF                 |     | 1600 |     |      |

| THERMAL          | PROTECTION                |                                           |     |      |     | •    |

| T <sub>SD</sub>  | Thermal Shutdown          |                                           |     | 145  | 0   | °C   |

| T <sub>HYS</sub> | Thermal Hysteresis        |                                           |     | 10   |     | °C   |

<sup>7.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization tested at  $T_J = T_A = 25^{\circ}$ C. Low duty cycle pulse techniques are used during testing to maintain the junction temperature as close to ambient as possible.

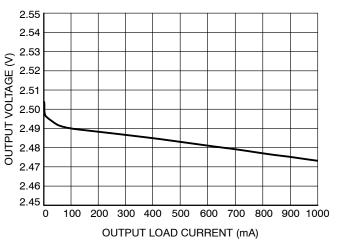

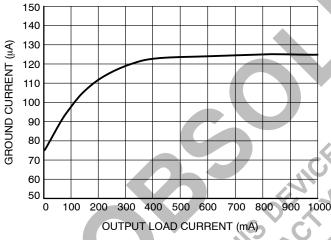

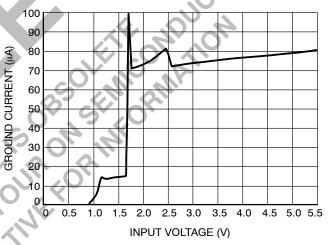

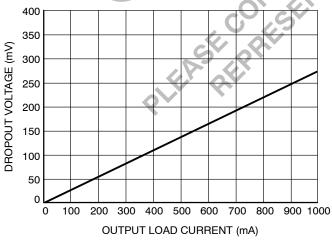

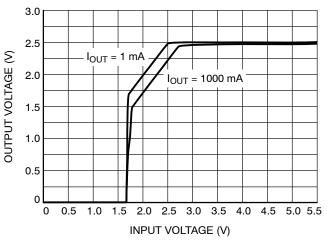

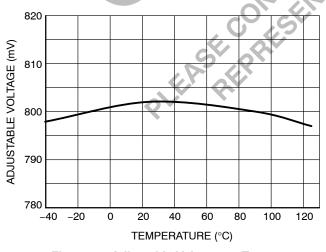

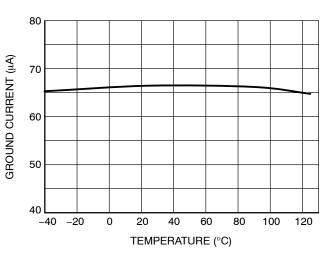

# **TYPICAL CHARACTERISTICS**

$(shown for \ V_{OUT} = 2.5 \ V, \ V_{IN} = 3.5 \ V, \ I_{OUT} = 1 \ mA, \ C_{IN} = 1 \ \mu F, \ C_{OUT} = 4.7 \ \mu F, \ C_{BYP} = 0, \ and \ T_A = 25 ^{\circ}C \ unless \ otherwise \ specified.)$

2.52

2.50 2.49 2.48 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5

Figure 3. Output Voltage vs. Load Current

Figure 4. Output Voltage vs. Input Voltage

INPUT VOLTAGE (V)

Figure 5. Ground Current vs. Load Current

Figure 6. Ground Current vs. Input Voltage

Figure 7. Dropout Voltage vs. Load Current

Figure 8. Dropout Characteristics

# **TYPICAL CHARACTERISTICS**

(shown for  $V_{OUT}$  = 2.5 V,  $V_{IN}$  = 3.5 V,  $I_{OUT}$  = 1 mA,  $C_{IN}$  = 1  $\mu$ F,  $C_{OUT}$  = 4.7  $\mu$ F,  $C_{BYP}$  = 0, and  $T_A$  = 25°C unless otherwise specified.)

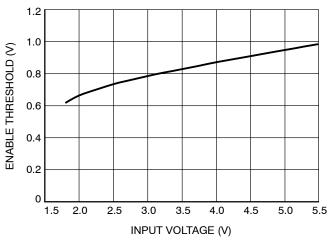

Figure 9. Rising Enable Threshold vs. Supply Voltage

Voltage

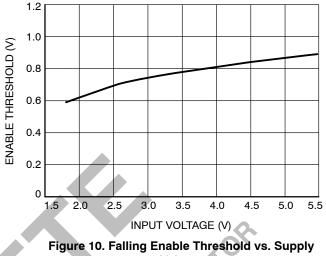

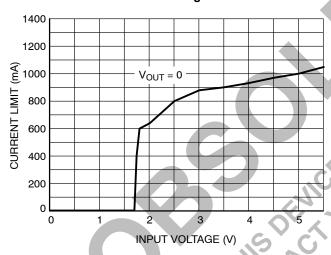

Figure 11. Current Limit on Output vs. Supply Voltage

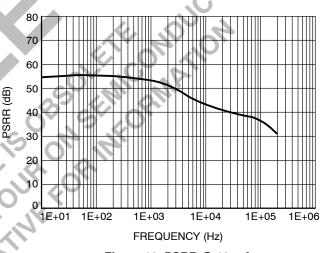

Figure 12. PSRR @ 10 mA

Figure 13. Adjustable Voltage vs. Temperature

Figure 14. Ground Current vs. Temperature

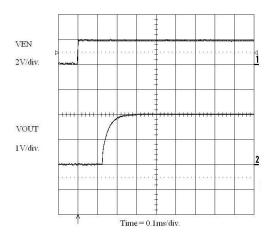

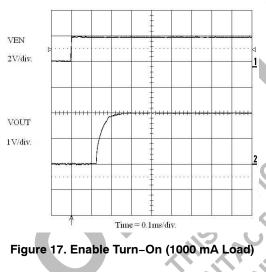

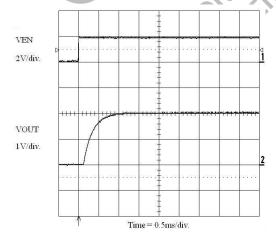

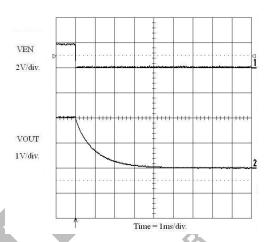

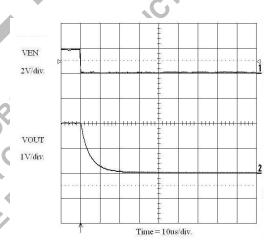

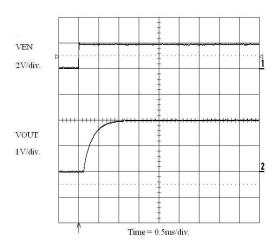

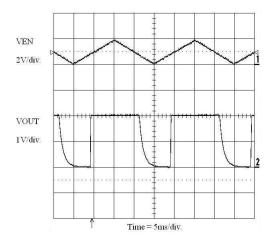

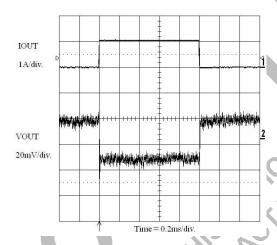

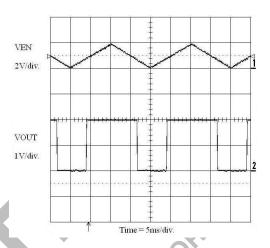

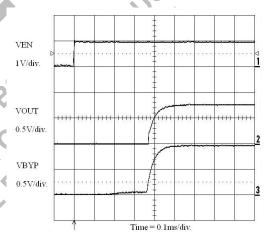

# TRANSIENT CHARACTERISTICS

$(shown for \ V_{OUT}=2.0 \ V, \ V_{IN}=3.0 \ V, \ I_{OUT}=1 \ mA, \ C_{IN}=1 \ \mu F, \ C_{OUT}=4.7 \ \mu F, \ C_{BYP}=0, \ and \ T_A=25 ^{\circ}C \ unless \ otherwise \ specified.)$

Figure 15. Enable Turn-On (1 mA Load)

Figure 19. Enable Turn-On (1 mA Load) **CBYP** = 470 pF

Figure 16. Enable Turn-Off (1 mA Load)

Figure 18. Enable Turn-Off (1000 mA Load)

Figure 20. Enable Turn-On (1000 mA Load) **CBYP** = 470 pF

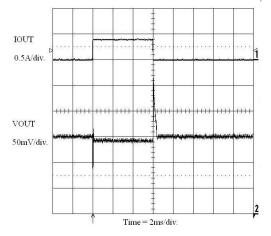

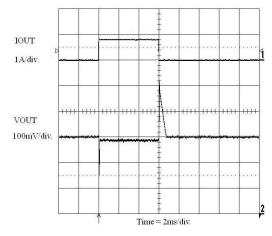

# TRANSIENT CHARACTERISTICS

$(shown for \ V_{OUT}=2.0 \ V, \ V_{IN}=3.0 \ V, \ I_{OUT}=1 \ mA, \ C_{IN}=1 \ \mu F, \ C_{OUT}=4.7 \ \mu F, \ C_{BYP}=0, \ and \ T_{A}=25^{\circ}C \ unless \ otherwise \ specified.)$

Figure 21. Slow Enable Operation (1 mA Load)

Figure 23. Load Transient Response (1 mA to 1000 mA)

Figure 25. Load Transient Response (1 mA to 400 mA) ( $V_{OUT}$  = 0.8 V and  $V_{IN}$  = 1.8 V)

Figure 22. Slow Enable Operation (1000 mA Load)

Figure 24. Enable Turn-On (1 mA Load) (V<sub>OUT</sub> = 0.8 V and V<sub>IN</sub> = 1.8 V)

Figure 26. Load Transient Response (1 mA to 800 mA) ( $V_{OUT}$  = 0.8 V and  $V_{IN}$  = 1.8 V)

# **PIN FUNCTIONS**

### $V_{IN}$

Positive Power Input. Power is supplied to the device through the  $V_{IN}$  pin. A bypass capacitor is required on this pin if the device is more than six inches away from the main input filter capacitor. In general it is advisable to include a small bypass capacitor adjacent to the regulator. In battery–powered circuits this is particularly important because the output impedance of a battery rises with frequency, so a bypass capacitor in the range of  $1~\mu F$  to  $10~\mu F$  is recommended.

### **GND**

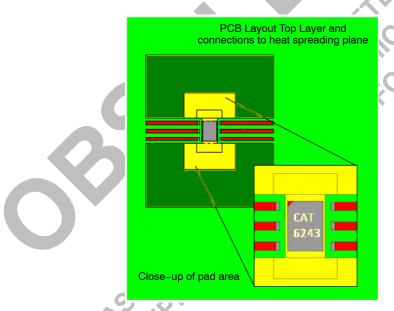

Ground. The negative voltage of the input power source. The center pad on the back of the package is also electrically ground. This pad is used for cooling the device by making connection to the buried ground plane through solder filled vias or by contact with a topside copper surface exposed to free flowing air.

### **ENABLE**

ENABLE is an active high logic input which controls the regulator's the output state. If ENABLE < 0.4~V the regulator is shutdown and  $V_{OUT} = 0~V$ . If ENABLE > 1.6~V the regulator is active and supplying power to the load.

If the regulator is intended to operate continuously and won't be shut down from time to time ENABLE should be tied to  $V_{\rm IN}$ .

### BYP

The Bypass Capacitor input is used to decrease output voltage noise by placing a capacitor between BYP and ground. The recommended range of capacitance is from tra

100 pF to 470 pF. Values larger than this will provide no additional improvement and will further extend CAT6243's startup time.

A bypass capacitor is not required for operation and BYP may be left open or floating if no capacitor is used but DO NOT ground BYP as this will interfere with the error amplifier's functioning.

# **ADJ**

ADJ = Adjust and is the voltage control input. ADJ connects to the center point of a resistor divider which determines the CAT6243's output voltage. See Applications Section for resistor selection guidelines.

# V<sub>OUT</sub>

$V_{OUT}$  is the regulator's output and supplies power to the load.  $V_{OUT}$  can be shut off via the ENABLE input. All CAT6243 members are designed to block reverse current, meaning anytime  $V_{OUT}$  becomes greater than  $V_{IN}$  the pass FET will be shut off so there is no reverse current flow from output to input. CAT6243 is also equipped with an output discharge transistor that is turned ON anytime ENABLE is at a logic Low. This transistor ensures  $V_{OUT}$  discharges to 0 V when the regulator is shutdown. This is especially important when powering digital circuitry because if  $V_{OUT}$  fails to reach 0 V their POR (power–ON reset) circuitry may not trigger and scrambled data or unpredictable operations may result.

A minimum output capacitor of 2.2  $\mu$ F should be placed between  $V_{OUT}$  and GND to insure stable operation. Increasing the size of  $C_{OUT}$ , up to 22  $\mu$ F, will improve transient response to large changes in load current.

### APPLICATIONS INFORMATION

# Input Decoupling (C<sub>IN</sub>)

A ceramic or tantalum 1 µF capacitor is recommended and should be connected close to the CAT6243's package. Higher capacitance and lower ESR will improve the overall line and load transient response.

# Output Decoupling (COUT)

The minimum output decoupling value is 2.2  $\mu F$  and can be augmented to fulfill stringent load transient requirements. The regulator works with ceramic chip capacitors. Larger values, up to 22 µF, improve noise rejection and load regulation transient response. The CAT6243 is a highly stable regulator and performs well over a wide range capacitor Equivalent Series Resistances (ESR).

# No-Load Regulation Considerations

The CAT6243 adjustable regulator will operate properly under conditions where the only load current is through the resistor divider that sets the output voltage. However, in the case where the CAT6243 is configured to provide a 0.8 V output, there is no resistor divider and the ADJ pin is connected to V<sub>OUT</sub>. If the part is enabled under no-load conditions, leakage current through the pass transistor at junction temperatures above 85°C can approach several microamperes, especially as junction temperature approaches 150°C. If this leakage current is not directed into a load, the output voltage will rise above nominal until a load is applied. For this reason it is recommended that a minimum load of 100 µA be present at all times. Normally the voltage setting resistor divider will serve this function but if no divider is used ( $V_{OUT} = 0.8 \text{ V}$ ) then an external load of 8 K $\Omega$ should be provided.

# **Output Voltage Adjust**

The output voltage can be adjusted from 0.8 V to 5.0 V using resistors between the output and the ADJ input. The output voltage and resistors are chosen using Equation 1 and Equation 2.

$$V_{OUT} = 0.8 \left( 1 + \frac{R_1}{R_2} \right) + \left( I_{ADJ} \times R_1 \right)$$

(eq. 1)

$$R_2 \cong \frac{0.8 \text{ V}}{I_{DIV}} \tag{eq. 2}$$

$$V_{OUT} = 0.8 \left( 1 + \frac{R_1}{R_2} \right) + \left( I_{ADJ} \times R_1 \right)$$

(eq. 1)

$$R_2 \cong \frac{0.8 \text{ V}}{I_{DIV}}$$

(eq. 2)

$$R_1 \cong R_2 \left( \frac{V_{OUT}}{0.8 \text{ V}} - 1 \right)$$

(eq. 3)

Figure 27. Adjustable Output Resistor Divider

Input bias current, IADJ, for all practical designs can be ignored  $(I_{ADJ} = 0)$ . Considering that the lowest recommended I<sub>OUT</sub> value is 100 μA, then, when there is no load on V<sub>OUT</sub>, I<sub>DIV</sub> must be 100 µA to keep CAT6243 in regulation. This then sets R2's value using Equation 2 to  $8 \text{ K}\Omega$ , which minimizes output noise. Use Equation 3 to find the required value for R1. If needed, lower values for I<sub>DIV</sub> can be considered, but not lower than 10 µA. The price will be worse values for both load regulation and TC<sub>OUT</sub>.

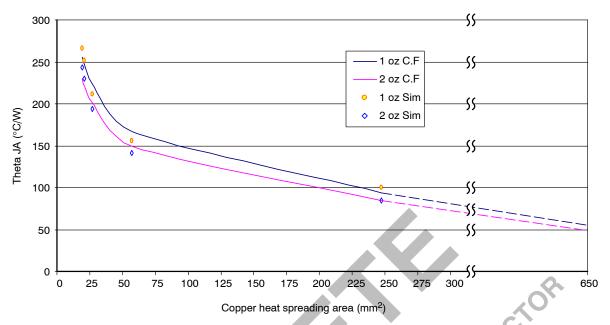

# **Thermal Considerations**

As power in the CAT6243 increases, it may become necessary to provide thermal relief. The maximum power dissipation supported by this device is dependent upon board design and layout. Mounting pad configuration on the PCB, the board material, and the ambient temperature affect the rate of junction temperature rise for the part. When the CAT6243 has good thermal conductivity through the PCB, the junction temperature will be relatively low even with high power applications. The maximum dissipation the CAT6243 can handle is given by:

$$P_{D(MAX)} = \frac{\left[T_{J(MAX)} - T_{A}\right]}{R_{\theta JA}}$$

(eq. 4)

Since T<sub>J</sub> is not recommended to exceed 125°C, then with CAT6243 soldered to 645 mm<sup>2</sup> (1 sq inch), 1 oz copper area, FR4 PCB material can dissipate in excess of 1 W when the ambient temperature (T<sub>A</sub>) is 25°C. Note that this assumes the pad in the center of the package is soldered to the dissipating copper foil. See Figure below for R<sub>HIA</sub> versus PCB area for heat dissipating areas smaller than 645 mm<sup>2</sup>. Power dissipation can be calculated from the following equations:

$$P_D \approx V_{IN}(I_{GND} + I_{OUT}) + I_{OUT}(V_{IN} - V_{OUT})$$

(eq. 5)

$$V_{IN(MAX)} \approx \frac{P_{D(MAX)} + (V_{OUT} \times I_{OUT})}{I_{OUT} + I_{GND}}$$

(eq. 6)

Figure 28. Thermal Resistance vs. PCB Copper Area for 3 mm x 3 mm WDFN Package

Figure 29. Topside Copper Foil Pattern for Heat Dissipation

# **Design Hints**

$V_{\rm IN}$  and GND printed circuit board traces should be as wide as possible. When the impedance of these traces is high due to narrow trace width or long length, there is a chance to pick up noise or cause the regulator to malfunction. Place

external components, especially the input and output capacitors, as close as possible to the CAT6243, and keep traces between power source and load as short as possible.

### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### PACKAGE DIMENSIONS

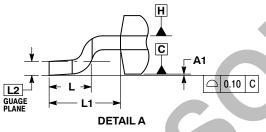

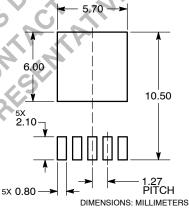

# DPAK-5 (TO-252, 5 LEAD) CASE 369AE **ISSUE A**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. THERMAL PAD CONTOUR OPTIONAL, WITHIN DIMENSIONS SHOWN.

4. DIMENSIONS O AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS OR BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEPD 0.15mm PER SIDE.

- NOT EXCEED 0.15mm PER SIDE.

DIMENSIONS D AND E ARE DETERMINED AT THE OUTERMOST EXTREMES OF THE PLASTIC BODY.

DATUMS A AND B ARE DETERMINED AT DATUM

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.10        | 2.50  |  |  |

| A1  | 0.00        | 0.13  |  |  |

| b   | 0.40        | 0.60  |  |  |

| b2  | 5.14        | 5.54  |  |  |

| С   | 0.40        | 0.60  |  |  |

| c2  | 0.40        | 0.60  |  |  |

| D   | 5.40        | 6.30  |  |  |

| D1  | 4.80        | 5.10  |  |  |

| E   | 6.35        | 6.80  |  |  |

| E1  | 4.75        | 5.05  |  |  |

| е   | 1.27        | BSC   |  |  |

| H   | 9.50        | 10.20 |  |  |

| L   | 1.39        | 1.78  |  |  |

| L1  | 2.50 2.90   |       |  |  |

| L2  | 0.51 BSC    |       |  |  |

# RECOMMENDED SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Table 6. ORDERING INFORMATION (Notes 8 - 11)

| Device Output Voltag |            | Package                       | Shipping            |  |

|----------------------|------------|-------------------------------|---------------------|--|

| CAT6243-ADJMT5T3     | Adjustable | WDFN-6, 3 mm x 3 mm (Pb-Free) | 3,000 / Tape & Reel |  |

| CAT6243DCADJ-RKG     | Adjustable | DPAK 5 5-Lead (Pb-Free)       | 2,500 / Tape & Reel |  |

- 8. The standard lead finish is Matte-Tin.

- 9. For additional package and temperature options, contact your nearest ON Semiconductor Sales office.

- 10. For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

- 11. For detailed information and a breakdown of device nomenclature and numbering systems, please see the ON Semiconductor Device Nomenclature document, TND310/D, available at www.onsemi.com

ON Semiconductor and the little are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent rega

# **PUBLICATION ORDERING INFORMATION**

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative