### **Freescale Semiconductor**

Data Sheet: Technical Data

Document Number: MCIMX31 Rev. 4.1, 11/2008

# MCIMX31 and MCIMX31L

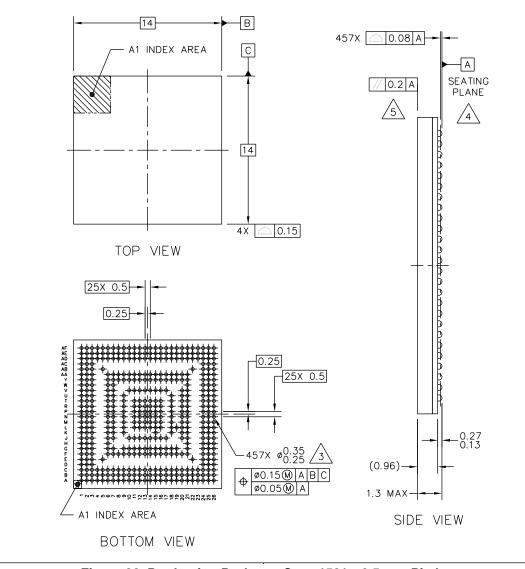

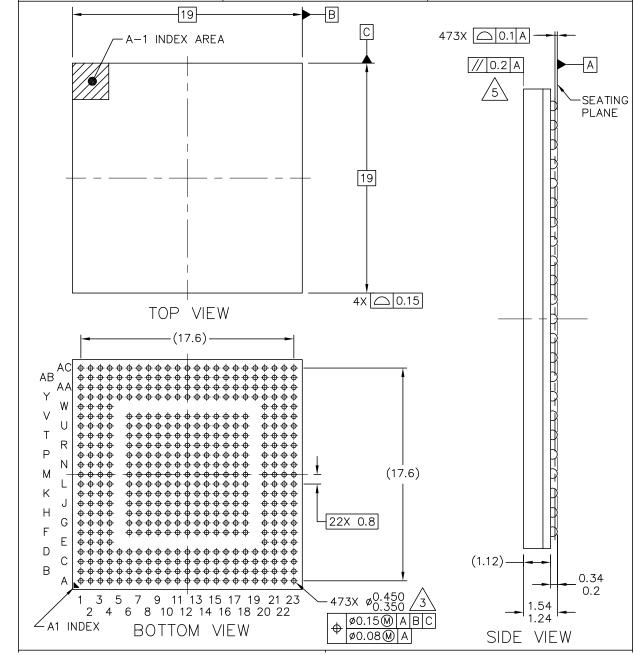

Package Information Plastic Package Case 1581 14 x 14 mm, 0.5 mm Pitch Case 1931 19 x 19 mm, 0.8 mm Pitch

Ordering Information See Table 1 on page 3 for ordering information.

# MCIMX31 and MCIMX31L

Multimedia Applications Processors

# 1 Introduction

The MCIMX31 and MCIMX31L multimedia applications processors represent the next step in low-power, high-performance application processors. Unless otherwise specified, the material in this data sheet is applicable to both the MCIMX31 and MCIMX31L processors and referred to singularly throughout this document as MCIMX31. The MCIMX31L does not include a graphics processing unit (GPU).

Based on an ARM11<sup>TM</sup> microprocessor core, the MCIMX31 provides the performance with low power consumption required by modern digital devices such as:

- Feature-rich cellular phones

- Portable media players and mobile gaming machines

- Personal digital assistants (PDAs) and Wireless PDAs

- Portable DVD players

- Digital cameras

The MCIMX31 takes advantage of the ARM1136JF-S<sup>™</sup> core running at up to 532 MHz, and is optimized for

#### Contents

| Introduction                              |

|-------------------------------------------|

| Ordering Information                      |

| Block Diagram 4                           |

| Functional Description and Application    |

| Information 4                             |

| ARM11 Microprocessor Core 4               |

| Module Inventory 6                        |

| Signal Descriptions 9                     |

| Electrical Characteristics 10             |

| Chip-Level Conditions 10                  |

| Supply Power-Up/Power-Down Requirements   |

| and Restrictions 18                       |

| Module-Level Electrical Specifications 21 |

| Package Information and Pinout 104        |

| MAPBGA Production Package—                |

| 457 14 x 14 mm, 0.5 mm Pitch 104          |

| MAPBGA Production Package—                |

| 473 19 x 19 mm, 0.8 mm Pitch 110          |

| Ball Maps 116                             |

| Product Differences 118                   |

| Product Documentation 119                 |

| Revision History 120                      |

|                                           |

freesc

This document contains information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2005–2008. All rights reserved.

#### Introduction

minimal power consumption using the most advanced techniques for power saving (DPTC, DVFS, power gating, clock gating). With 90 nm technology and dual-Vt transistors (two threshold voltages), the MCIMX31 provides the optimal performance versus leakage current balance.

The performance of the MCIMX31 is boosted by a multi-level cache system, and features peripheral devices such as an MPEG-4 Hardware Encoder (VGA, 30 fps), an Autonomous Image Processing Unit, a Vector Floating Point (VFP11) co-processor, and a RISC-based SDMA controller.

The MCIMX31 supports connections to various types of external memories, such as DDR, NAND Flash, NOR Flash, SDRAM, and SRAM. The MCIMX31 can be connected to a variety of external devices using technology, such as high-speed USB2.0 OTG, ATA, MMC/SDIO, and compact flash.

### 1.1 Features

The MCIMX31 is designed for the high-tier, mid-tier smartphone markets, and portable media players. They provide low-power solutions for high-performance demanding multimedia and graphics applications.

The MCIMX31 is built around the ARM11 MCU core and implemented in the 90 nm technology.

The systems include the following features:

- Multimedia and floating-point hardware acceleration supporting:

- MPEG-4 real-time encode of up to VGA at 30 fps

- MPEG-4 real-time video post-processing of up to VGA at 30 fps

- Video conference call of up to QCIF-30 fps (decoder in software), 128 kbps

- Video streaming (playback) of up to VGA-30 fps, 384 kbps

- 3D graphics and other applications acceleration with the ARM<sup>®</sup> tightly-coupled Vector Floating Point co-processor

- On-the-fly video processing that reduces system memory load (for example, the power-efficient viewfinder application with no involvement of either the memory system or the ARM CPU)

- Advanced power management

- Dynamic voltage and frequency scaling

- Multiple clock and power domains

- Independent gating of power domains

- Multiple communication and expansion ports including a fast parallel interface to an external graphic accelerator (supporting major graphic accelerator vendors)

- Security

### 1.2 Ordering Information

Table 1 provides the ordering information for the MCIMX31.

| Part Number    | Silicon Revision <sup>1, 2, 3,4</sup> | Device Mask     | Operating Temperature<br>Range (°C) | Package <sup>5</sup>         |  |

|----------------|---------------------------------------|-----------------|-------------------------------------|------------------------------|--|

| MCIMX31VKN5    | 1.15                                  | 2L38W and 3L38W | 0 to 70                             |                              |  |

| MCIMX31LVKN5   | 1.15                                  | 2L38W and 3L38W | 0 to 70                             | 14 x 14 mm,<br>0.5 mm pitch, |  |

| MCIMX31VKN5B   | 1.2                                   | M45G            | 0 to 70                             | MAPBGA-457,<br>Case 1581     |  |

| MCIMX31LVKN5B  | 1.2                                   | M45G            | 0 to 70                             | 0436 1301                    |  |

| MCIMX31VKN5C   | 2.0                                   | M91E            | 0 to 70                             |                              |  |

| MCIMX31LVKN5C  | 2.0                                   | M91E            | 0 to 70                             | 14 x 14 mm,<br>0.5 mm pitch, |  |

| MCIMX31CVKN5C  | 2.0                                   | M91E            | -40 to 85                           | MAPBGA-457,<br>Case 1581     |  |

| MCIMX31LCVKN5C | 2.0                                   | M91E            | -40 to 85                           |                              |  |

| MCIMX31VMN5C   | 2.0                                   | M91E            | 0 to 70                             | 19 x 19 mm,                  |  |

| MCIMX31LVMN5C  | 2.0                                   | M91E            | 0 to 70                             | 0.8 mm pitch,<br>Case 1931   |  |

| Table | 1.  | Orderina | Information |

|-------|-----|----------|-------------|

| IUNIO | ••• | oraoring | mornation   |

Information on reading the silicon revision register can be found in the IC Identification (IIM) chapter of the Reference Manual, see Section 7, "Product Documentation."

<sup>2</sup> Errata and fix information of the various mask sets can be found in the standard MCIMX31 Chip Errata, see Section 7, "Product Documentation."

<sup>3</sup> Changes in output buffer characteristics can be found in the I/O Setting Exceptions and Special Pad Descriptions table in the Reference Manual, see Section 7, "Product Documentation."

<sup>4</sup> JTAG functionality is not tested nor guaranteed at -40°C.

<sup>5</sup> Case 1581 and 1931 are RoHS compliant, lead-free, MSL = 3, and solders at  $260^{\circ}$ C.

### 1.2.1 Feature Differences Between Mask Sets

The following is a summary of differences between silicon Revision 2.0, mask set M91E, and previous revisions of silicon. A complete list of these differences is given in Table 72.

- Extended operating temperature range is available: -40°C to 85°C

- Supply current information changes, as shown in Table 13 and Table 14

- FUSE\_VDD supply voltage is floated or grounded during read operation

- No restriction on PLL versus core supply voltage

- Operating frequency as shown in Table 8.

MCIMX31/MCIMX31L Technical Data, Rev. 4.1

1

**Functional Description and Application Information**

### 1.3 Block Diagram

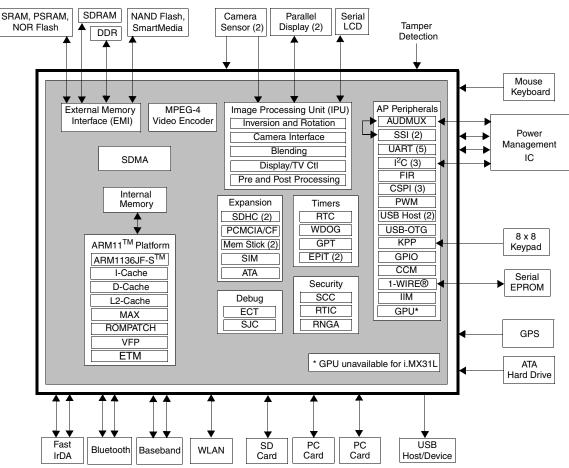

Figure 1 shows the MCIMX31 simplified interface block diagram.

Figure 1. MCIMX31 Simplified Interface Block Diagram

# 2 Functional Description and Application Information

### 2.1 ARM11 Microprocessor Core

The CPU of the MCIMX31 is the ARM1136JF-S core based on the ARM v6 architecture. It supports the ARM Thumb<sup>®</sup> instruction sets, features Jazelle<sup>®</sup> technology (which enables direct execution of Java byte codes), and a range of SIMD DSP instructions that operate on 16-bit or 8-bit data values in 32-bit registers.

The ARM1136JF-S processor core features:

- Integer unit with integral  $EmbeddedICE^{TM}$  logic

- Eight-stage pipeline

- Branch prediction with return stack

- Low-interrupt latency

4

#### **Functional Description and Application Information**

- Instruction and data memory management units (MMUs), managed using micro TLB structures backed by a unified main TLB

- Instruction and data L1 caches, including a non-blocking data cache with Hit-Under-Miss

- Virtually indexed/physically addressed L1 caches

- 64-bit interface to both L1 caches

- Write buffer (bypassable)

- High-speed Advanced Micro Bus Architecture (AMBA)<sup>TM</sup> L2 interface

- Vector Floating Point co-processor (VFP) for 3D graphics and other floating-point applications hardware acceleration

- $ETM^{TM}$  and JTAG-based debug support

### 2.1.1 Memory System

The ARM1136JF-S complex includes 16 KB Instruction and 16 KB Data L1 caches. It connects to the MCIMX31 L2 unified cache through 64-bit instruction (read-only), 64-bit data read/write (bi-directional), and 64-bit data write interfaces.

The embedded 16K SRAM can be used for audio streaming data to avoid external memory accesses for the low-power audio playback, for security, or for other applications. There is also a 32-KB ROM for bootstrap code and other frequently-used code and data.

A ROM patch module provides the ability to patch the internal ROM. It can also initiate an external boot by overriding the boot reset sequence by a jump to a configurable address.

Table 2 shows information about the MCIMX31 core in tabular form.

#### Table 2. MCIMX31 Core

| Core                | Core                | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Integrated Memory                                                                                                                                           |

|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acronym             | Name                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Includes                                                                                                                                                    |

| ARM11 or<br>ARM1136 | ARM1136<br>Platform | The ARM1136 <sup>™</sup> Platform consists of the ARM1136JF-S core, the ETM real-time debug modules, a 6 x 5 multi-layer AHB crossbar switch (MAX), and a Vector Floating Processor (VFP).<br>The MCIMX31 provides a high-performance ARM11 microprocessor core and highly integrated system functions. The ARM Application Processor (AP) and other subsystems address the needs of the personal, wireless, and portable product market with integrated peripherals, advanced processor core, and power management capabilities. | <ul> <li>16 Kbyte Instruction<br/>Cache</li> <li>16 Kbyte Data<br/>Cache</li> <li>128 Kbyte L2 Cache</li> <li>32 Kbyte ROM</li> <li>16 Kbyte RAM</li> </ul> |

**Functional Description and Application Information**

### 2.2 Module Inventory

Table 3 shows an alphabetical listing of the modules in the multimedia applications processor. For extended descriptions of the modules, see the reference manual. A cross-reference is provided to the electrical specifications and timing information for each module with external signal connections.

| Block<br>Mnemonic | Block Name                                           | Functional<br>Grouping       | Brief Description                                                                                                                                                                                                                                                                                |          |

|-------------------|------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1-Wire®           | 1-Wire Interface                                     | Connectivity<br>Peripheral   | The 1-Wire module provides bi-directional communication between the ARM11 core and external 1-Wire devices.                                                                                                                                                                                      | 4.3.4/26 |

| ATA               | Advanced<br>Technology (AT)<br>Attachment            | Connectivity<br>Peripheral   | The ATA block is an AT attachment host interface. It is designed to interface with IDE hard disc drives and ATAPI optical disc drives.                                                                                                                                                           | 4.3.5/27 |

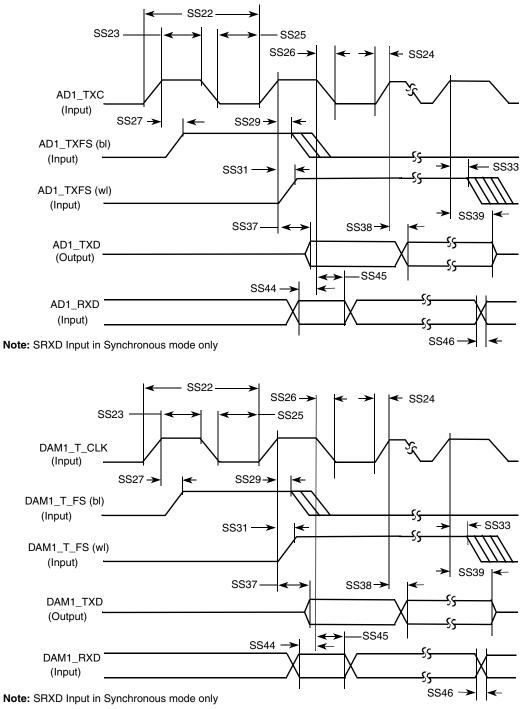

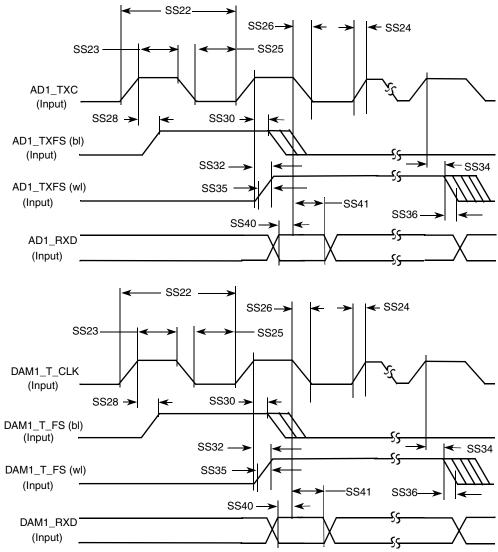

| AUDMUX            | Digital Audio<br>Multiplexer                         | Multimedia<br>Peripheral     | The AUDMUX interconnections allow multiple, simultaneous audio/voice/data flows between the ports in point-to-point or point-to-multipoint configurations.                                                                                                                                       | 4.3.6/36 |

| CAMP              | Clock Amplifier<br>Module                            | Clock                        | The CAMP converts a square wave/sinusoidal input into a rail-to-rail square wave. The output of CAMP feeds the predivider.                                                                                                                                                                       | 4.3.3/25 |

| CCM               | Clock Control<br>Module                              | Clock                        | The CCM provides clock, reset, and power management control for the MCIMX31.                                                                                                                                                                                                                     | —        |

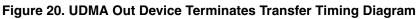

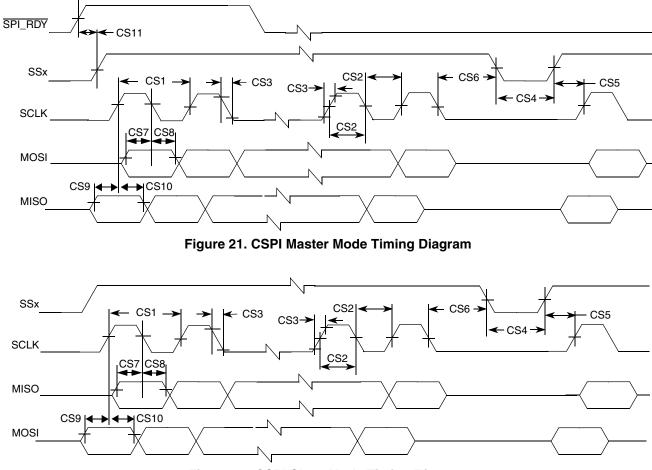

| CSPI              | Configurable<br>Serial Peripheral<br>Interface (x 3) | Connectivity<br>Peripheral   | The CSPI is equipped with data FIFOs and is a master/slave configurable serial peripheral interface module, capable of interfacing to both SPI master and slave devices.                                                                                                                         | 4.3.7/36 |

| DPLL              | Digital Phase<br>Lock Loop                           | Clock                        | The DPLLs produce high-frequency on-chip clocks with low frequency and phase jitters.<br>Note: External clock sources provide the reference frequencies.                                                                                                                                         | 4.3.8/37 |

| ECT               | Embedded<br>Cross Trigger                            | Debug                        | The ECT is composed of three CTIs (Cross Trigger Interface) and one CTM (Cross Trigger Matrix—key in the multi-core and multi-peripheral debug strategy.                                                                                                                                         |          |

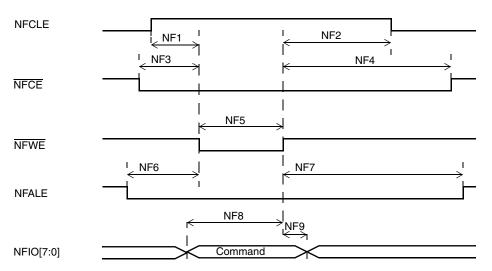

| EMI               | External<br>Memory<br>Interface                      | Memory<br>Interface<br>(EMI) | The EMI includes<br>• Multi-Master Memory Interface (M3IF)<br>• Enhanced SDRAM Controller (ESDCTL)<br>• NAND Flash Controller (NFC)<br>• Wireless External Interface Module (WEIM)                                                                                                               |          |

| EPIT              | Enhanced<br>Periodic<br>Interrupt Timer              | Timer<br>Peripheral          | The EPIT is a 32-bit "set and forget" timer which starts counting after<br>the EPIT is enabled by software. It is capable of providing precise<br>interrupts at regular intervals with minimal processor intervention.                                                                           |          |

| ETM               | Embedded<br>Trace Macrocell                          | Debug/Trace                  | The ETM (from ARM, Ltd.) supports real-time instruction and data tracing by way of ETM auxiliary I/O port.                                                                                                                                                                                       |          |

| FIR               | Fast InfraRed<br>Interface                           | Connectivity<br>Peripheral   | This FIR is capable of establishing a 0.576 Mbit/s, 1.152 Mbit/s or 4 Mbit/s half duplex link via a LED and IR detector. It supports 0.576 Mbit/s, 1.152 Mbit/s medium infrared (MIR) physical layer protocol and 4Mbit/s fast infrared (FIR) physical layer protocol defined by IrDA, Rev. 1.4. |          |

| Table 3. Digital and | Analog Modules |

|----------------------|----------------|

|----------------------|----------------|

| Block BLOCK Functional |                                              |                            |                                                                                                                                                                                                      |                                   |

|------------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Mnemonic               | Block Name                                   | Grouping                   | Brief Description                                                                                                                                                                                    | Section/<br>Page                  |

| Fusebox                | Fusebox                                      | ROM                        | The Fusebox is a ROM that is factory configured by Freescale.                                                                                                                                        | 4.3.12/55<br>See also<br>Table 11 |

| GPIO                   | General<br>Purpose I/O<br>Module             | Pins                       | The GPIO provides several groups of 32-bit bidirectional, general purpose I/O. This peripheral provides dedicated general-purpose signals that can be configured as either inputs or outputs.        | _                                 |

| GPT                    | General<br>Purpose Timer                     | Timer<br>Peripheral        | The GPT is a multipurpose module used to measure intervals or generate periodic output.                                                                                                              |                                   |

| GPU                    | Graphics<br>Processing Unit                  | Multimedia<br>Peripheral   | The GPU provides hardware acceleration for 2D and 3D graphics algorithms.                                                                                                                            | _                                 |

| l <sup>2</sup> C       | Inter IC<br>Communication                    | Connectivity<br>Peripheral | The I <sup>2</sup> C provides serial interface for controlling the Sensor Interface and other external devices. Data rates of up to 100 Kbits/s are supported.                                       | 4.3.13/56                         |

| IIM                    | IC Identification<br>Module                  | ID                         | The IIM provides an interface for reading device identification.                                                                                                                                     | _                                 |

| IPU                    | Image<br>Processing Unit                     | Multimedia<br>Peripheral   | The IPU processes video and graphics functions in the MCIMX31 and interfaces to video, still image sensors, and displays.                                                                            | 4.3.14/57,<br>4.3.15/59           |

| KPP                    | Keypad Port                                  | Connectivity<br>Peripheral | The KPP is used for keypad matrix scanning or as a general purpose I/O. This peripheral simplifies the software task of scanning a keypad matrix.                                                    | _                                 |

| MPEG-4                 | MPEG-4 Video<br>Encoder                      | Multimedia<br>Peripherals  | The MPEG-4 encoder accelerates video compression, following the MPEG-4 standard                                                                                                                      | _                                 |

| MSHC                   | Memory Stick<br>Host Controller              | Connectivity<br>Peripheral | The MSHC is placed in between the AIPS and the customer memory stick to support data transfer from the MCIMX31 to the customer memory stick.                                                         | 4.3.16/84                         |

| PADIO                  | Pads I/O                                     | Buffers and Drivers        | The PADIO serves as the interface between the internal modules and the device's external connections.                                                                                                | 4.3.1/22                          |

| PCMCIA                 | РСМ                                          | Connectivity<br>Peripheral | The PCMCIA Host Adapter provides the control logic for PCMCIA socket interfaces.                                                                                                                     | 4.3.17/86                         |

| PWM                    | Pulse-Width<br>Modulator                     | Timer<br>Peripheral        | The PWM has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones.                                                                         | 4.3.18/88                         |

| RNGA                   | Random<br>Number<br>Generator<br>Accelerator | Security                   | The RNGA module is a digital integrated circuit capable of generating 32-bit random numbers. It is designed to comply with FIPS-140 standards for randomness and non-determinism.                    |                                   |

| RTC                    | Real Time Clock                              | Timer<br>Peripheral        | The RTC module provides a current stamp of seconds, minutes,<br>hours, and days. Alarm and timer functions are also available for<br>programming. The RTC supports dates from the year 1980 to 2050. | _                                 |

| RTIC                   | Run-Time<br>Integrity<br>Checkers            | Security                   | The RTIC ensures the integrity of the peripheral memory contents and assists with boot authentication.                                                                                               | _                                 |

| Block<br>Mnemonic | Block Name                                                                    | Functional<br>Grouping          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Section/<br>Page |  |

|-------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| SCC               | Security<br>Controller<br>Module                                              | Security                        | The SCC is a hardware component composed of two blocks—the Secure RAM module, and the Security Monitor. The Secure RAM provides a way of securely storing sensitive information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |  |

| SDHC              | Secured Digital<br>Host Controller                                            | Connectivity<br>Peripheral      | The SDHC controls the MMC (MultiMediaCard), SD (Secure Digital) memory, and I/O cards by sending commands to cards and performing data accesses to and from the cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.19/89        |  |

| SDMA              | Smart Direct<br>Memory Access                                                 | System<br>Control<br>Peripheral | The SDMA controller maximizes the system's performance by relieving the ARM core of the task of bulk data transfer from memory to memory or between memory and on-chip peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                |  |

| SIM               | Subscriber<br>Identification<br>Module                                        | Connectivity<br>Peripheral      | The SIM interfaces to an external Subscriber Identification Card. It is<br>an asynchronous serial interface adapted for Smart Card<br>communication for e-commerce applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.3.20/90        |  |

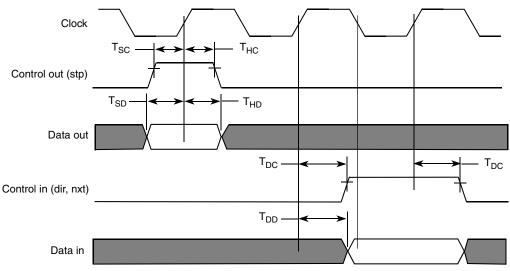

| SJC               | Secure JTAG<br>Controller                                                     | Debug                           | The SJC provides debug and test control with maximum security and provides a flexible architecture for future derivatives or future multi-cores architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.21/94        |  |

| SSI               | Synchronous<br>Serial Interface                                               | Multimedia<br>Peripheral        | The SSI is a full-duplex, serial port that allows the device to<br>communicate with a variety of serial devices, such as standard<br>codecs, Digital Signal Processors (DSPs), microprocessors,<br>peripherals, and popular industry audio codecs that implement the<br>inter-IC sound bus standard (I2S) and Intel AC97 standard.                                                                                                                                                                                                                                                                                                                                    | 4.3.22/96        |  |

| UART              | Universal<br>Asynchronous<br>Receiver/Trans<br>mitter                         | Connectivity<br>Peripheral      | The UART provides serial communication capability with external devices through an RS-232 cable or through use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed IrDA compatibility.                                                                                                                                                                                                                                                                                                                          | _                |  |

| USB               | Universal Serial<br>Bus—<br>2 Host<br>Controllers and<br>1 OTG<br>(On-The-Go) | Connectivity<br>Peripherals     | <ul> <li>USB Host 1 is designed to support transceiverless connection to the on-board peripherals in Low Speed and Full Speed mode, and connection to the ULPI (UTMI+ Low-Pin Count) and Legacy Full Speed transceivers.</li> <li>USB Host 2 is designed to support transceiverless connection to the Cellular Modem Baseband Processor.</li> <li>The USB-OTG controller offers HS/FS/LS capabilities in Host mode and HS/FS in device mode. In Host mode, the controller supports direct connection of a FS/LS device (without external hub). In device (bypass) mode, the OTG port functions as gateway between the Host 1 Port and the OTG transceiver.</li> </ul> | 4.3.23/104       |  |

| WDOG              | Watchdog Timer<br>Module                                                      | Timer<br>Peripheral             | The WDOG module protects against system failures by providing a method for the system to recover from unexpected events or programming errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —                |  |

Table 3. Digital and Analog Modules (continued)

9

Because of an order from the United States International Trade Commission, BGA-packaged product lines and part numbers indicated here currently are not available from Freescale for import or sale in the United States prior to September 2010: i.MX31 Product Family

# **3 Signal Descriptions**

Signal descriptions are in the reference manual. Special signal considerations are listed following this paragraph. The BGA ball assignment is in Section 5, "Package Information and Pinout."

Special Signal Considerations:

### • Tamper detect (GPIO1\_6)

Tamper detect logic is used to issue a security violation. This logic is activated if the tamper detect input is asserted.

The tamper detect logic is disabled after reset. After enabling the logic, it is impossible to disable it until the next reset. The GPR[16] bit functions as the tamper detect enable bit.

GPIO1\_6 functions similarly to other I/O with GPIO capabilities regardless of the status of the tamper detect enable bit. (For example, the GPIO1\_6 can function as an input with GPIO capabilities, such as sampling through PSR or generating interrupts.)

### • Power ready (GPIO1\_5)

The power ready input, GPIO1\_5, should be connected to an external power management IC power ready output signal. If not used, GPIO1\_5 must either be (a) externally pulled-up to NVCC1 or (b) a no connect, internally pulled-up by enabling the on-chip pull-up resistor. GPIO1\_5 is a dedicated input and cannot be used as a general-purpose input/output.

### • SJC\_MOD

SJC\_MOD must be externally connected to GND for normal operation. Termination to GND through an external pull-down resistor (such as 1 k $\Omega$ ) is allowed, but the value should be much smaller than the on-chip 100 k $\Omega$  pull-up.

### • CE\_CONTROL

CE\_CONTROL is a reserved input and must be externally tied to GND through a 1 k $\Omega$  resistor.

### • TTM\_PAD

TTM\_PAD is for Freescale factory use only. Control bits indicate pull-up/down disabled. However, TTM\_PAD is actually connected to an on-chip pull-down device. Users must either float this signal or tie it to GND.

### • M\_REQUEST and M\_GRANT

These two signals are not utilized internally. The user should make no connection to these signals.

• Clock Source Select (CLKSS)

The CLKSS is the input that selects the default reference clock source providing input to the DPLL. To select CKIH, tie CLKSS to NVCC1. To select CKIL, tie CLKSS to ground. After initialization, the reference clock source can be changed (initial setting is overwritten) by programming the PRCS bits in the CCMR.

This section provides the device-level and module-level electrical characteristics for the MCIMX31.

### 4.1 Chip-Level Conditions

This section provides the device-level electrical characteristics for the IC. See Table 4 for a quick reference to the individual tables and sections.

| For these characteristics,                                              | Topic appears |

|-------------------------------------------------------------------------|---------------|

| Table 5, "Absolute Maximum Ratings"                                     | on page 10    |

| Table 7, "Thermal Resistance Data—19 $\times$ 19 mm Package"            | on page 11    |

| Table 8, "Operating Ranges"                                             | on page 13    |

| Table 9, "Specific Operating Ranges for Silicon Revision 2.0"           | on page 14    |

| Table 10, "Interface Frequency"                                         | on page 14    |

| Section 4.1.1, "Supply Current Specifications"                          | on page 16    |

| Section 4.2, "Supply Power-Up/Power-Down Requirements and Restrictions" | on page 19    |

Table 4. MCIMX31 Chip-Level Conditions

### CAUTION

Stresses beyond those listed under Table 5 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Table 8, "Operating Ranges," on page 13 is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

| Parameter                                                 | Symbol                                | Min  | Max       | Units |

|-----------------------------------------------------------|---------------------------------------|------|-----------|-------|

| Supply Voltage (Core)                                     | QVCC <sub>max</sub>                   | -0.5 | 1.65      | V     |

| Supply Voltage (I/O)                                      | NVCC <sub>max</sub>                   | -0.5 | 3.3       | V     |

| Input Voltage Range                                       | V <sub>Imax</sub>                     | -0.5 | NVCC +0.3 | V     |

| Storage Temperature                                       | T <sub>storage</sub>                  | -40  | 125       | °C    |

| ESD Damage Immunity:                                      |                                       |      |           |       |

| Human Body Model (HBM)                                    |                                       | —    | 1500      | v     |

| Machine Model (MM)                                        | V <sub>esd</sub>                      | —    | 200       | v     |

| Charge Device Model (CDM)                                 |                                       | —    | 500       |       |

| Offset voltage allowed in run mode between core supplies. | V <sub>core_offset</sub> <sup>1</sup> |      | 15        | mV    |

<sup>1</sup> The offset is the difference between all core voltage pair combinations of QVCC, QVCC1, and QVCC4.

Table 6 provides the thermal resistance data for the  $14 \times 14$  mm, 0.5 mm pitch package.

| Rating                                       | Board                   | Symbol              | Value | Unit | Notes   |

|----------------------------------------------|-------------------------|---------------------|-------|------|---------|

| Junction to Ambient (natural convection)     | Single layer board (1s) | $R_{\thetaJA}$      | 56    | °C/W | 1, 2, 3 |

| Junction to Ambient (natural convection)     | Four layer board (2s2p) | $R_{\thetaJA}$      | 30    | °C/W | 1, 3    |

| Junction to Ambient (@200 ft/min)            | Single layer board (1s) | $R_{\thetaJMA}$     | 46    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Four layer board (2s2p) | $R_{\thetaJMA}$     | 26    | °C/W | 1, 3    |

| Junction to Board                            | —                       | $R_{\thetaJB}$      | 17    | °C/W | 1, 4    |

| Junction to Case                             | —                       | $R_{	ext{	heta}JC}$ | 10    | °C/W | 1, 5    |

| Junction to Package Top (natural convection) | —                       | $\Psi_{JT}$         | 2     | °C/W | 1, 6    |

#### Table 6. Thermal Resistance Data— $14 \times 14$ mm Package

### NOTES

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 7 provides the thermal resistance data for the  $19 \times 19$  mm, 0.8 mm pitch package.

| Rating                                       | Board                   | Symbol               | Value | Unit | Notes   |

|----------------------------------------------|-------------------------|----------------------|-------|------|---------|

| Junction to Ambient (natural convection)     | Single layer board (1s) | $R_{	ext{	heta}JA}$  | 46    | °C/W | 1, 2, 3 |

| Junction to Ambient (natural convection)     | Four layer board (2s2p) | $R_{	ext{	heta}JA}$  | 29    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Single layer board (1s) | $R_{	ext{	heta}JMA}$ | 38    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)            | Four layer board (2s2p) | $R_{	ext{	heta}JMA}$ | 25    | °C/W | 1, 2, 3 |

| Junction to Board                            | —                       | $R_{	hetaJB}$        | 19    | °C/W | 1, 3    |

| Junction to Case (Top)                       | _                       | $R_{\theta JCtop}$   | 10    | °C/W | 1, 4    |

| Junction to Package Top (natural convection) | _                       | $\Psi_{JT}$          | 2     | °C/W | 1, 5    |

#### Table 7. Thermal Resistance Data—19 × 19 mm Package

#### MCIMX31/MCIMX31L Technical Data, Rev. 4.1

#### NOTES

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

- 3. Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

- 4. Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- 5. Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 8 provides the operating ranges.

#### NOTE

The term NVCC in this section refers to the associated supply rail of an input or output. The association is shown in the Signal Multiplexing chapter of the reference manual.

#### CAUTION

NVCC6 and NVCC9 must be at the same voltage potential. These supplies are connected together on-chip to optimize ESD damage immunity.

| Symbol                      | Parameter                                                                                                                                                                                                                               | Min                   | Max                  | Units |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-------|

| QVCC,                       | Core Operating Voltage <sup>1,2,3</sup>                                                                                                                                                                                                 |                       |                      |       |

| QVCC1,<br>QVCC4             | $ \begin{array}{ll} \mbox{Silicon rev 1.15, 1.2, and 2.0} & 0 \leq f_{ARM} \leq 400 \mbox{ MHz, non-overdrive} \\ 0 \leq f_{ARM} \leq 400 \mbox{ MHz, overdrive}^4 \\ 0 \leq f_{ARM} \leq 532 \mbox{ MHz, overdrive}^4 \\ \end{array} $ | 1.22<br>>1.47<br>1.55 | 1.47<br>1.65<br>1.65 | V     |

|                             | State Retention Voltage <sup>5</sup>                                                                                                                                                                                                    | 0.95                  |                      |       |

| NVCC1,<br>NVCC3–10          | I/O Supply Voltage, except DDR <sup>6</sup> non-overdrive<br>overdrive <sup>7</sup>                                                                                                                                                     | 1.75<br>>3.1          | 3.1<br>3.3           | V     |

| NVCC2,<br>NVCC21,<br>NVCC22 | I/O Supply Voltage, DDR only                                                                                                                                                                                                            | 1.75                  | 1.95                 | V     |

| FVCC, MVCC,                 | PLL (Phase-Locked Loop) and FPM (Frequency Pre-multiplier) Supply Voltage <sup>8</sup>                                                                                                                                                  |                       |                      | V     |

| SVCC, UVCC                  | non-overdrive<br>overdrive <sup>4</sup>                                                                                                                                                                                                 | 1.3<br>>1.47          | 1.47<br>1.6          |       |

| IOQVDD                      | On-device Level Shifter Supply Voltage                                                                                                                                                                                                  | 1.6                   | 1.9                  | V     |

| FUSE VDD                    | Fusebox read Supply Voltage <sup>9, 10</sup>                                                                                                                                                                                            | 1.65                  | 1.95                 | V     |

| FUSE_VDD                    | Fusebox write (program) Supply Voltage <sup>11</sup>                                                                                                                                                                                    | 3.0                   | 3.3                  | V     |

| T <sub>A</sub>              | Operating Ambient Temperature Range <sup>12</sup>                                                                                                                                                                                       | 0                     | 70                   | °C    |

#### Table 8. Operating Ranges

<sup>1</sup> Measured at package balls, including peripherals, ARM, and L2 cache supplies (QVCC, QVCC1, QVCC4, respectively).

<sup>2</sup> The core voltage must be higher than 1.38V to avoid corrupted data during transfers from the USB HS. Please refer to Errata file ENGcm02610 ID.

<sup>3</sup> If the Core voltage is supplied by the MC13738, it will be 1.6 ± 0.05 V during the power-up sequence. This is allowed. After power-up the voltage should be reduced to avoid operation in overdrive mode.

<sup>4</sup> Supply voltage is considered "overdrive" for voltages above 1.47 V. Operation time in overdrive—whether switching or not—must be limited to a cumulative duration of 1.25 years (10,950 hours) or less to sustain the maximum operating voltage without significant device degradation—for example, 25% (average 6 hours out of 24 yours per day) duty cycle for 5-year rated equipment. To tolerate the maximum operating overdrive voltage for 10 years, the device must have a duty cycle of 12.5% or less in overdrive (for example 3 out of 24 hours per day). Below 1.47V, duty cycle restrictions may apply for equipment rated above 5 years.

<sup>5</sup> The SR voltage is applied to QVCC, QVCC1, and QVCC4 after the device is placed in SR mode. The Real-Time Clock (RTC) is operational in State Retention (SR) mode.

<sup>6</sup> Overshoot and undershoot conditions (transitions above NVCC and below GND) on I/O must be held below 0.6 V, and the duration of the overshoot/undershoot must not exceed 10% of the system clock cycle. Overshoot/undershoot must be controlled through printed circuit board layout, transmission line impedance matching, signal line termination, or other methods. Non-compliance to this specification may affect device reliability or cause permanent damage to the device.

- <sup>7</sup> Supply voltage is considered "overdrive" for voltages above 3.1 V. Operation time in overdrive—whether switching or not—must be limited to a cumulative duration of 1 year (8,760 hours) or less to sustain the maximum operating voltage without significant device degradation—for example, 20% (average 4.8 hours out of 24 hours per day) duty cycle for 5-year rated equipment. Operation at 3.3 V that exceeds a cumulative 3,504 hours may cause non-operation whenever supply voltage is reduced to 1.8 V; degradation may render the device too slow or inoperable. Below 3.1 V, duty cycle restrictions may apply for equipment rated above 5 years.

- <sup>8</sup> For normal operating conditions, PLLs' and core supplies must maintain the following relation: PLL ≥ Core 100 mV. In other words, for a 1.6 V core supply, PLL supplies must be set to 1.5 V or higher. This restriction is no longer necessary on mask set M91E. PLL supplies may be set independently of core supply. PLL voltage must not be altered after power up, otherwise the PLL will be unstable and lose lock. To minimize inducing noise on the PLL supply line, source the voltage from a low-noise, dedicated supply. PLL parameters in Table 31, "DPLL Specifications," on page 37, are guaranteed over the entire specified voltage range.

- <sup>9</sup> Fusebox read supply voltage applies to silicon Revisions 1.2 and previous.

- <sup>10</sup> In read mode, FUSE\_VDD can be floated or grounded for mask set M91E (silicon Revision 2.0).

- <sup>11</sup> Fuses might be inadvertently blown if written to while the voltage is below this minimum.

- <sup>12</sup> The temperature range given is for the consumer version. Please refer to Table 1 for extended temperature range offerings and the associated part numbers.

#### Table 9. Specific Operating Ranges for Silicon Revision 2.0

| Symbol   | Parameter                                           | Min | Max | Units |

|----------|-----------------------------------------------------|-----|-----|-------|

| FUSE_VDD | Fusebox read Supply Voltage <sup>1</sup>            | _   | —   | V     |

| 1032_000 | Fusebox write (program) Supply Voltage <sup>2</sup> | 3.0 | 3.3 | V     |

<sup>1</sup> In read mode, FUSE\_VDD should be floated or grounded.

<sup>2</sup> Fuses might be inadvertently blown if written to while the voltage is below the minimum.

Table 10 provides information for interface frequency limits. For more details about clocks characteristics, see Section 4.3.8, "DPLL Electrical Specifications," and Section 4.3.3, "Clock Amplifier Module (CAMP) Electrical Characteristics."

#### Table 10. Interface Frequency

| ID | Parameter                   | Symbol            | Min | Тур    | Max  | Units |

|----|-----------------------------|-------------------|-----|--------|------|-------|

| 1  | JTAG TCK Frequency          | f <sub>JTAG</sub> | DC  | 5      | 10   | MHz   |

| 2  | CKIL Frequency <sup>1</sup> | f <sub>CKIL</sub> | 32  | 32.768 | 38.4 | kHz   |

| 3  | CKIH Frequency <sup>2</sup> | f <sub>CKIH</sub> | 15  | 26     | 75   | MHz   |

<sup>1</sup> CKIL must be driven by an external clock source to ensure proper start-up and operation of the device. CKIL is needed to clock the internal reset synchronizer, the watchdog, and the real-time clock.

<sup>2</sup> DPTC functionality, specifically the voltage/frequency relation table, is dependent on CKIH frequency. At the time of publication, standard tables used by Freescale OSs provided for a CKIH frequency of 26 MHz only. Any deviation from this frequency requires an update to the OS. For more details, refer to the particular OS user's guide documentation.

Table 11 shows the fusebox supply current parameters.

| Ref. Num | Description                                                                                     | Symbol               | Minimum | Typical | Maximum | Units |

|----------|-------------------------------------------------------------------------------------------------|----------------------|---------|---------|---------|-------|

| 1        | eFuse Program Current. <sup>1</sup><br>Current to program one eFuse bit: efuse_pgm = 3.0 V      | I <sub>program</sub> | _       | 35      | 60      | mA    |

| 2        | eFuse Read Current <sup>2</sup><br>Current to read an 8-bit eFuse word<br>vdd_fusebox = 1.875 V | I <sub>read</sub>    | _       | 5       | 8       | mA    |

$^{1}~$  The current  $I_{program}$  is during program time (t\_{program}).

<sup>2</sup> The current I<sub>read</sub> is present for approximately 50 ns of the read access to the 8-bit word, and only applies to Silicon Rev. 1.2 and previous.

### 4.1.1 Supply Current Specifications

Table 12 shows the core current consumption for 0°C to 70°C for Silicon Revision 1.2 and previous for the MCIMX31.

| Mode               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | /CC<br>oheral) | QVCC1<br>(ARM) |     | QVCC4<br>(L2) |     | FVCC + MVCC<br>+ SVCC + UVCC<br>(PLL) |     | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|----------------|-----|---------------|-----|---------------------------------------|-----|------|

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур  | Мах            | Тур            | Max | Тур           | Max | Тур                                   | Max |      |

| State<br>Retention | <ul> <li>QVCC and QVCC1 = 0.95 V</li> <li>L2 caches are power gated (QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                                         | 0.80 | _              | 0.50           | _   | _             | _   | 0.04                                  | _   | mA   |

| Wait               | <ul> <li>QVCC, QVCC1, and QVCC4 = 1.22 V</li> <li>ARM is in wait for interrupt mode</li> <li>MAX is active</li> <li>L2 cache is stopped but powered</li> <li>MCU PLL is on (532 MHz), VCC = 1.4 V</li> <li>USB PLL and SPLL are off, VCC = 1.4 V</li> <li>FPM is on</li> <li>CKIH input is on</li> <li>CAMP is on</li> <li>32 kHz input is on</li> <li>All clocks are gated off</li> <li>All modules are off<br/>(by programming CGR[2:0] registers)</li> <li>RNGA oscillator is off</li> <li>No external resistive loads</li> </ul> | 6.00 |                | 3.00           |     | 0.04          |     | 3.50                                  |     | mA   |

Table 12. Current Consumption for 0°C to 70°C<sup>1, 2</sup> for Silicon Revision 1.2 and Previous

<sup>1</sup> Typical column: TA = 25°C

<sup>2</sup> Maximum column:  $TA = 70^{\circ}C$

Table 13 shows the core current consumption for -40°C to 85°C for Silicon Revision 2.0 for the MCIMX31.

| Mode               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | QVCC<br>(Peripheral) |      | QVCC1<br>(ARM) |      | QVCC4<br>(L2) |      | FVCC + MVCC<br>+ SVCC + UVCC<br>(PLL) |    |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|----------------|------|---------------|------|---------------------------------------|----|

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур  | Max                  | Тур  | Max            | Тур  | Max           | Тур  | Max                                   |    |

| Deep<br>Sleep      | <ul> <li>QVCC = 0.95 V</li> <li>ARM and L2 caches are power gated<br/>(QVCC1 = QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                               | 0.16 | 5.50                 |      |                |      | _             | 0.02 | 0.10                                  | mA |

| State<br>Retention | <ul> <li>QVCC and QVCC1 = 0.95 V</li> <li>L2 caches are power gated (QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                                         | 0.16 | 5.50                 | 0.07 | 2.20           | _    |               | 0.02 | 0.10                                  | mA |

| Wait               | <ul> <li>QVCC, QVCC1, and QVCC4 = 1.22 V</li> <li>ARM is in wait for interrupt mode</li> <li>MAX is active</li> <li>L2 cache is stopped but powered</li> <li>MCU PLL is on (532 MHz), VCC = 1.4 V</li> <li>USB PLL and SPLL are off, VCC = 1.4 V</li> <li>FPM is on</li> <li>CKIH input is on</li> <li>CAMP is on</li> <li>32 kHz input is on</li> <li>All clocks are gated off</li> <li>All modules are off<br/>(by programming CGR[2:0] registers)</li> <li>RNGA oscillator is off</li> <li>No external resistive loads</li> </ul> | 6.00 | 15.00                | 2.20 | 25.00          | 0.03 | 0.29          | 3.60 | 4.40                                  | mA |

| Table 13. Current Consumption for –40°C to 85°C <sup>1, 2</sup> for Silicon Revision 2.0 |

|------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------|

<sup>1</sup> Typical column:  $TA = 25^{\circ}C$

<sup>2</sup> Maximum column:  $TA = 85^{\circ}C$

17

Because of an order from the United States International Trade Commission, BGA-packaged product lines and part numbers indicated here currently are not available from Freescale for import or sale in the United States prior to September 2010: i.MX31 Product Family

#### Table 14 shows the core current consumption for 0°C to 70°C for Silicon Revision 2.0 for the MCIMX31.

| Mode               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | QVCC<br>(Peripheral) |      | QVCC1<br>(ARM) |      | CC4<br>.2) | FVCC, +MVCC,<br>+SVCC, +UVCC<br>(PLL) |      | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|----------------|------|------------|---------------------------------------|------|------|

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур  | Max                  | Тур  | Max            | Тур  | Max        | Тур                                   | Max  |      |

| Deep<br>Sleep      | <ul> <li>QVCC = 0.95 V</li> <li>ARM and L2 caches are power gated<br/>(QVCC1 2= QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                              | 0.16 | 2.50                 | _    |                | _    |            | 0.02                                  | 0.10 | mA   |

| State<br>Retention | <ul> <li>QVCC and QVCC1 = 0.95 V</li> <li>L2 caches are power gated (QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                                         | 0.16 | 2.50                 | 0.07 | 1.60           | _    | _          | 0.02                                  | 0.10 | mA   |

| Wait               | <ul> <li>QVCC, QVCC1, and QVCC4 = 1.22 V</li> <li>ARM is in wait for interrupt mode</li> <li>MAX is active</li> <li>L2 cache is stopped but powered</li> <li>MCU PLL is on (532 MHz), VCC = 1.4 V</li> <li>USB PLL and SPLL are off, VCC = 1.4 V</li> <li>FPM is on</li> <li>CKIH input is on</li> <li>CAMP is on</li> <li>32 kHz input is on</li> <li>All clocks are gated off</li> <li>All modules are off<br/>(by programming CGR[2:0] registers)</li> <li>RNGA oscillator is off</li> <li>No external resistive loads</li> </ul> | 6.00 | 13.00                | 2.20 | 16.00          | 0.03 | 0.17       | 3.60                                  | 4.40 | mA   |

#### Table 14. Current Consumption for 0°C to 70°C<sup>1, 2</sup> for Silicon Revision 2.0

<sup>1</sup> Typical column:  $TA = 25^{\circ}C$

<sup>2</sup> Maximum column:  $TA = 70^{\circ}C$

#### MCIMX31/MCIMX31L Technical Data, Rev. 4.1

Downloaded from Arrow.com.

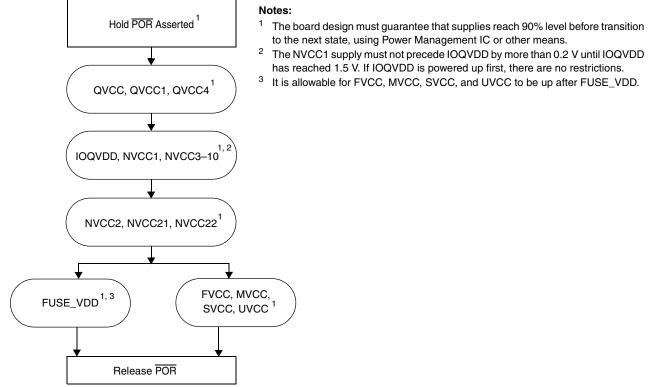

### 4.2 Supply Power-Up/Power-Down Requirements and Restrictions

Any MCIMX31 board design must comply with the power-up and power-down sequence guidelines as described in this section to guarantee reliable operation of the device. Any deviation from these sequences may result in any or all of the following situations:

- Cause excessive current during power up phase

- Prevent the device from booting

- Cause irreversible damage to the MCIMX31 (worst-case scenario)

### 4.2.1 Powering Up

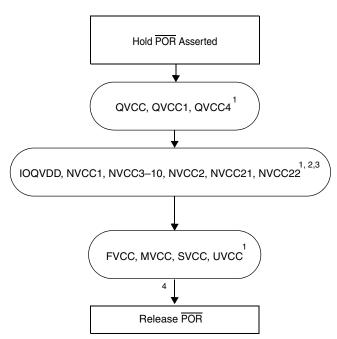

The Power On Reset ( $\overline{POR}$ ) pin must be kept asserted (low) throughout the power up sequence. Power up logic must guarantee that all power sources reach their target values prior to the release (de-assertion) of  $\overline{POR}$ . Figure 2 shows the power-up sequence for silicon Revisions 1.2 and previous. Figure 3 and Figure 4 show the power-up sequence for silicon Revision 2.0.

#### NOTE

Stages need to be performed in the order shown; however, *within* each stage, supplies can be powered up in any order. For example, supplies IOQVDD, NVCC1, and NVCC3 through NVCC10 do not need to be powered up in the order shown.

### CAUTION

NVCC6 and NVCC9 must be at the same voltage potential. These supplies are connected together on-chip to optimize ESD damage immunity.

Figure 2. Power-Up Sequence for Silicon Revisions 1.2 and Previous

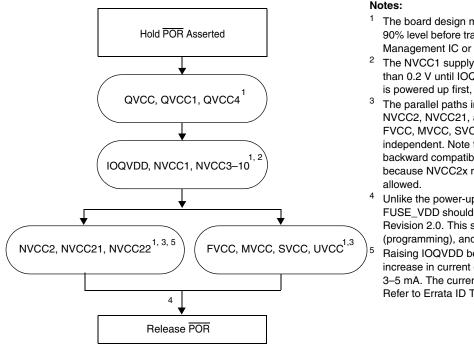

### 4.2.1.1 Power-Up Sequence for Silicon Revision 2

Silicon revision 2.0 offers two options for power-up sequencing. Option 1 is backwards compatible with silicon revision 1.2 and earlier versions of the IC. It should be noted that using option 1 on silicon Rev. 2.0 introduces a slight increase in current drain on IOQVDD when IOQVDD is raised before NVCC21. The expected resulting increase is in the range of 3 mA to 5 mA, which does not pose a risk to the IC.

Option 2 is an alternative power-up sequence that allows the powering up of NVCC2, NVCC21, NVCC22 with IOQVDD, NVCC1, and NVCC3-10 without producing a current drain increase on IOQVDD.

These two power-up options on the 2.0 silicon allow the user to select the optimum power-up sequence for their application.

#### Notes:

- The board design must guarantee that supplies reach 90% level before transition to the next state, using Power Management IC or other means.

- The NVCC1 supply must not precede IOQVDD by more than 0.2 V until IOQVDD has reached 1.5 V. If IOQVDD is powered up first, there are no restrictions.

- The parallel paths in the flow indicate that supply group NVCC2, NVCC21, and NVCC22, and supply group FVCC, MVCC, SVCC, and UVCC ramp-ups are independent. Note that this power-up sequence is backward compatible to Silicon Revs. 1.15 and 1.2, because NVCC2x ramp-up proceeding PLL supplies is

- Unlike the power-up sequence for Silicon Revision 1.2, FUSE\_VDD should not be driven on power-up for Silicon Revision 2.0. This supply is dedicated for fuse burning (programming), and should not be driven upon boot-up. Raising IOQVDD before NVCC21 produces a slight increase in current drain on IOQVDD of approximately 3-5 mA. The current increase will not damage the IC. Refer to Errata ID TLSbo91750 for details.

#### Figure 3. Option 1 Power-Up Sequence (Silicon Revision 2.0)

#### Notes:

- <sup>1</sup> The board design must guarantee that supplies reach 90% level before transition to the next state, using Power Management IC or other means.

- <sup>2</sup> The NVCC1 supply must not precede IOQVDD by more than 0.2 V until IOQVDD has reached 1.5 V. If IOQVDD is powered up first, there are no restrictions.

- 3 Raising NVCC2, NVCC21, and NVCC22 at the same time as IOQVDD does not produce the slight increase in current drain on IOQVDD (as described in Figure 3, Note 5).

- 4 Unlike the power-up sequence for Silicon Revision 1.2, FUSE\_VDD should not be driven on power-up for Silicon Revision 2.0. This supply is dedicated for fuse burning (programming), and should not be driven upon boot-up.

#### MCIMX31/MCIMX31L Technical Data, Rev. 4.1

#### 4.2.2 Powering Down

The power-down sequence prior to silicon Revision 2.0 should be completed as follows:

- 1. Lower the FUSE\_VDD supply (when in write mode).

- 2. Lower the remaining supplies.

For silicon revisions beginning with Revision 2.0 there is no special requirements for power down sequence.

### 4.3 Module-Level Electrical Specifications

This section contains the MCIMX31 electrical information including timing specifications, arranged in alphabetical order by module name.

### 4.3.1 I/O Pad (PADIO) Electrical Specifications

This section specifies the AC/DC characterization of functional I/O of the MCIMX31. There are two main types of I/O: regular and DDR. In this document, the "Regular" type is referred to as GPIO.

#### 4.3.1.1 DC Electrical Characteristics

The MCIMX31 I/O parameters appear in Table 15 for GPIO. See Table 8 for temperature and supply voltage ranges.

#### NOTE

The term NVCC in this section refers to the associated supply rail of an input or output. The association is shown in the Signal Multiplexing chapter of the reference manual. NVCC for Table 15 refers to NVCC1 and NVCC3–10; QVCC refers to QVCC, QVCC1, and QVCC4.

| Parameter                                 | Symbol            | Test Conditions                                                   | Min            | Тур | Max      | Units |

|-------------------------------------------|-------------------|-------------------------------------------------------------------|----------------|-----|----------|-------|

| High-level output voltage                 | V <sub>OH</sub>   | I <sub>OH</sub> = -1 mA                                           | NVCC -0.15     | _   | —        | V     |

|                                           |                   | I <sub>OH</sub> = specified Drive                                 | 0.8*NVCC       | _   | —        | V     |

| Low-level output voltage                  | V <sub>OL</sub>   | I <sub>OL</sub> = 1 mA                                            | —              | _   | 0.15     | V     |

|                                           |                   | I <sub>OL</sub> = specified Drive                                 | —              |     | 0.2*NVCC | V     |

| High-level output current, slow slew rate | I <sub>OH_S</sub> | V <sub>OH</sub> =0.8*NVCC<br>Std Drive<br>High Drive<br>Max Drive | -2<br>-4<br>-8 |     |          | mA    |

| High-level output current, fast slew rate | I <sub>OH_F</sub> | V <sub>OH</sub> =0.8*NVCC<br>Std Drive<br>High Drive<br>Max Drive | -4<br>-6<br>-8 |     | _        | mA    |

#### **Table 15. GPIO DC Electrical Parameters**

| Parameter                                | Symbol            | Test Conditions                                                   | Min         | Тур | Max        | Units                    |

|------------------------------------------|-------------------|-------------------------------------------------------------------|-------------|-----|------------|--------------------------|

| Low-level output current, slow slew rate | I <sub>OL_S</sub> | V <sub>OL</sub> =0.2*NVCC<br>Std Drive<br>High Drive<br>Max Drive | 2<br>4<br>8 |     | _          | mA                       |

| Low-level output current, fast slew rate | I <sub>OL_F</sub> | V <sub>OL</sub> =0.2*NVCC<br>Std Drive<br>High Drive<br>Max Drive | 4<br>6<br>8 | _   | _          | mA                       |

| High-Level DC input voltage              | V <sub>IH</sub>   | —                                                                 | 0.7*NVCC    | —   | NVCC       | V                        |

| Low-Level DC input voltage               | V <sub>IL</sub>   | —                                                                 | 0           | —   | 0.3*QVCC   | V                        |

| Input Hysteresis                         | V <sub>HYS</sub>  | Hysteresis enabled                                                | 0.25        | —   | —          | V                        |

| Schmitt trigger VT+                      | V <sub>T</sub> +  | Hysteresis enabled                                                | 0.5*QVCC    | —   | —          | V                        |

| Schmitt trigger VT-                      | V <sub>T</sub> –  | Hysteresis enabled                                                | —           |     | 0.5*QVCC   | V                        |

| Pull-up resistor (100 k $\Omega$ PU)     | R <sub>PU</sub>   | —                                                                 | —           | 100 | —          | kΩ                       |

| Pull-down resistor (100 k $\Omega$ PD)   | R <sub>PD</sub>   | —                                                                 | —           | 100 | —          | K52                      |

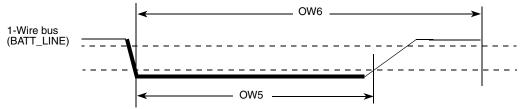

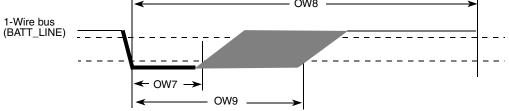

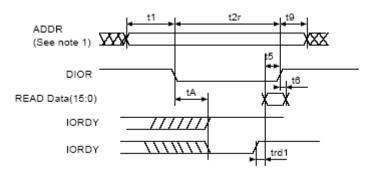

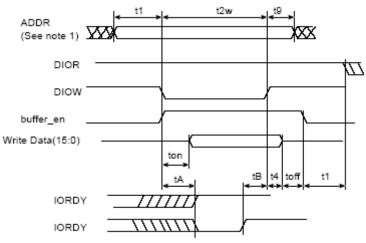

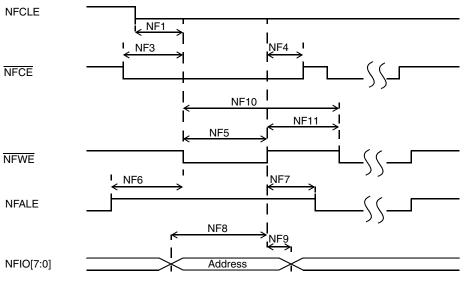

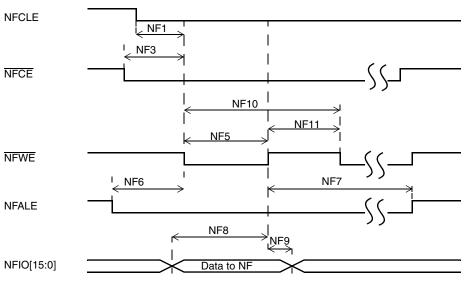

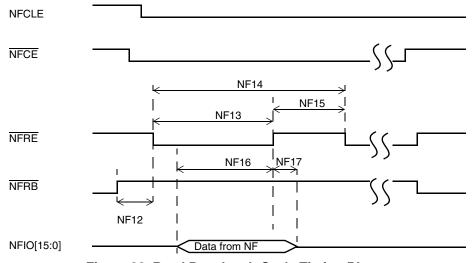

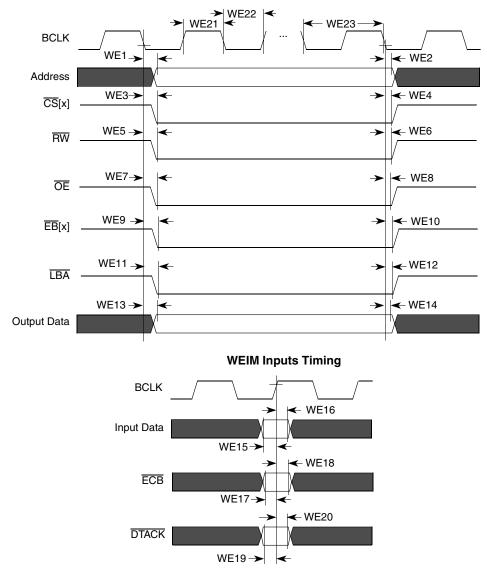

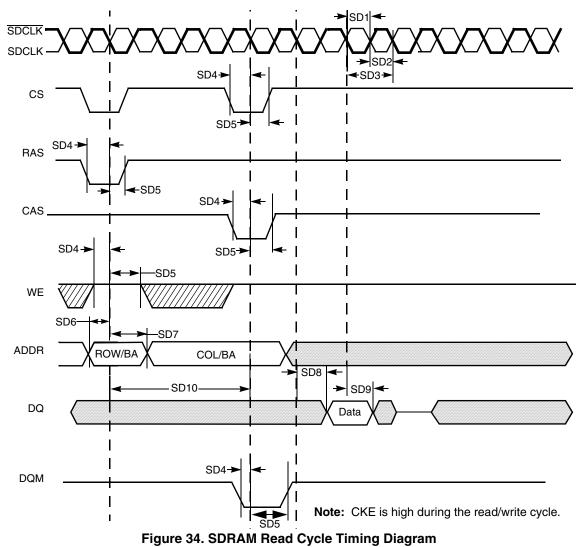

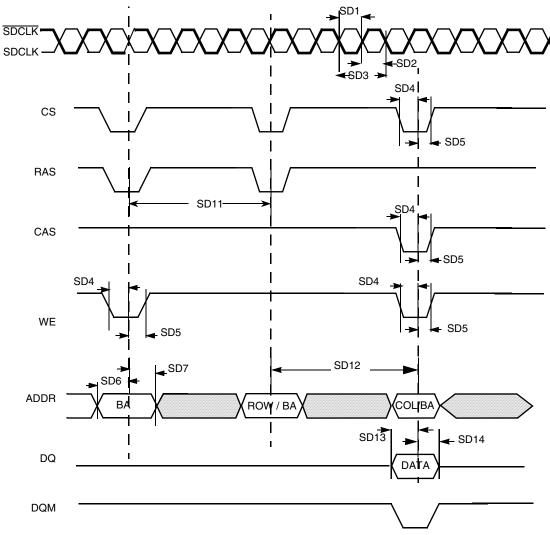

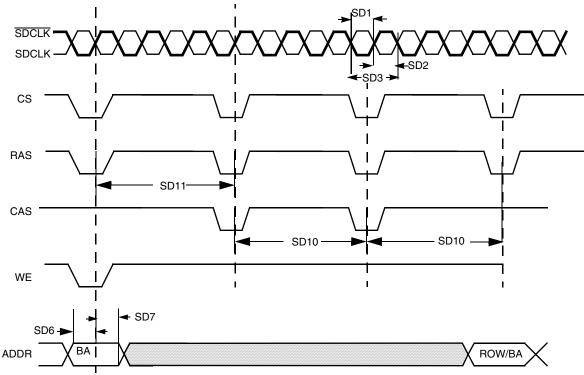

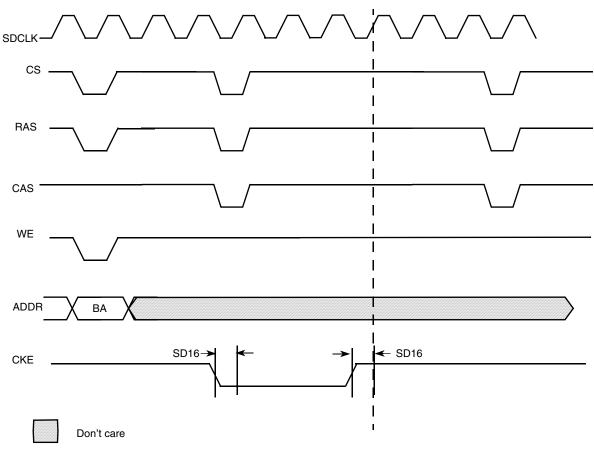

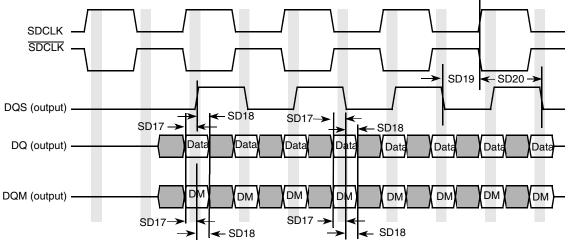

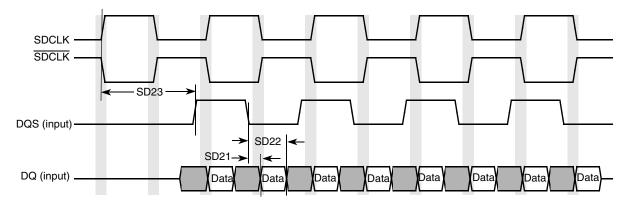

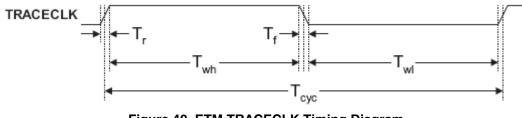

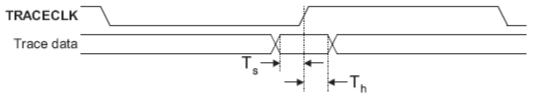

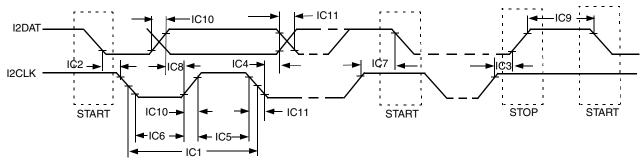

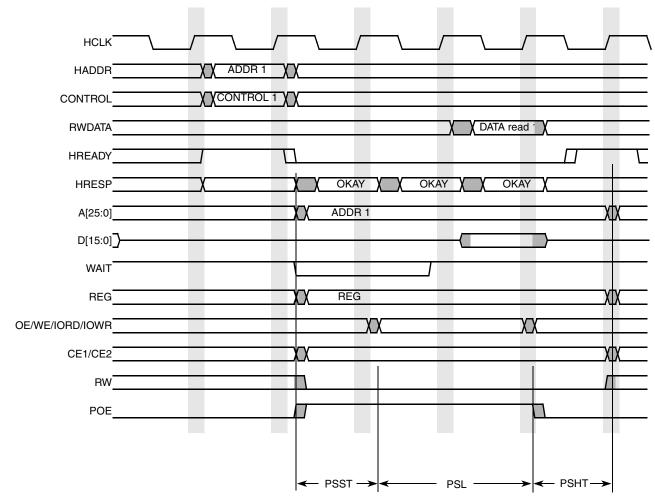

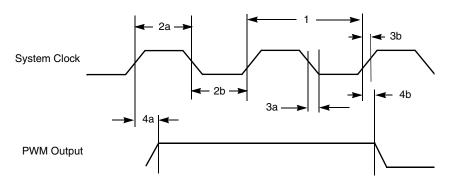

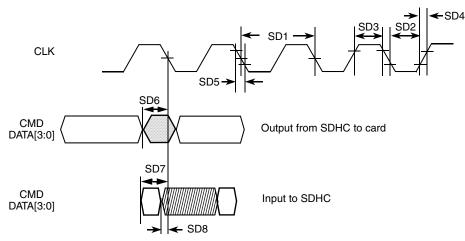

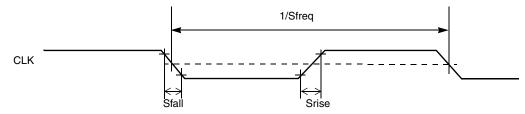

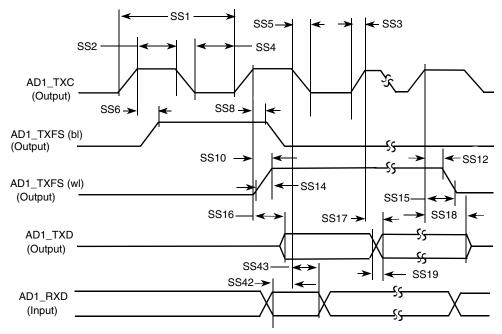

| Input current (no PU/PD)                 | I <sub>IN</sub>   | V <sub>I</sub> = NVCC or GND                                      | —           |     | ±1         | μA                       |