## DDR2 SDRAM Mini-RDIMM

## **MT9HTF6472PKZ – 512MB** MT9HTF12872PKZ - 1GB

### **Features**

- 244-pin, mini registered dual in-line memory module

- Fast data transfer rates: PC2-6400, PC2-5300, PC2-4200, or PC2-3200

- 512MB (64 Meg x 72), 1GB (128 Meg x 72)

- Supports ECC error detection and correction

- $V_{DD} = V_{DDO} = 1.8V$

- $V_{DDSPD} = 1.7-3.6V$

- JEDEC-standard 1.8V I/O (SSTL\_18-compatible)

- Differential data strobe (DQS, DQS#) option

- 4*n*-bit prefetch architecture

- · Multiple internal device banks for concurrent operation

- Programmable CAS latency (CL)

- · Posted CAS additive latency (AL)

- WRITE latency = READ latency 1 <sup>t</sup>CK

- Programmable burst lengths: 4 or 8

- Adjustable data-output drive strength

- 64ms, 8192-cycle refresh

- On-die termination (ODT)

- · Serial presence-detect (SPD) with EEPROM

- · Gold edge contacts

- Single rank

- · Halogen-free

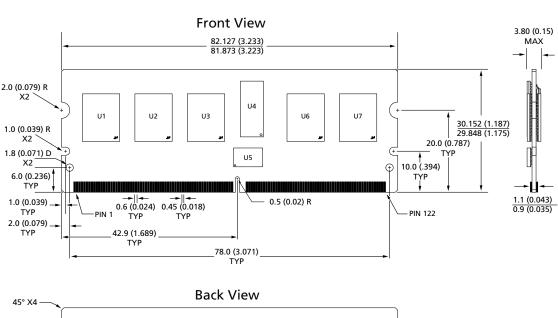

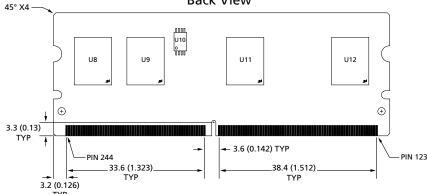

Figure 1: 244-Pin Mini-RDIMM (MO-244, R/C A)

Module Height: 30mm (1.181 in.)

| Options • Parity                                                                                                           | <b>Marking</b><br>P |

|----------------------------------------------------------------------------------------------------------------------------|---------------------|

| • Operating temperature                                                                                                    | None                |

| <ul> <li>Commercial (0°C ≤ T<sub>A</sub> ≤ 70°C)</li> <li>Industrial (-40°C ≤ T<sub>A</sub> ≤ 85°C)<sup>1</sup></li> </ul> | None                |

| • Package                                                                                                                  | 1                   |

| <ul> <li>244-pin DIMM (halogen-free)</li> <li>Frequency/CL<sup>2</sup></li> </ul>                                          | Z                   |

| - 2.5ns @ CL = 5 (DDR2-800)                                                                                                | -80E                |

| - 2.5ns @ CL = 6 (DDR2-800)                                                                                                | -800                |

| - 3.0ns @ CL = 5 (DDR2-667)                                                                                                | -667                |

- Notes: 1. Contact Micron for industrial temperature module offerings.

- 2. CL = CAS (READ) latency; registered mode will add one clock cycle to CL.

### **Table 1: Key Timing Parameters**

| Speed | Industry     | Data Rate (MT/s) t <sub>RCD</sub> t <sub>RP</sub> |        |        |        | <sup>t</sup> RP | <sup>t</sup> RC |      |

|-------|--------------|---------------------------------------------------|--------|--------|--------|-----------------|-----------------|------|

| Grade | Nomenclature | CL = 6                                            | CL = 5 | CL = 4 | CL = 3 | (ns)            | (ns)            | (ns) |

| -80E  | PC2-6400     | 800                                               | 800    | 533    | 400    | 12.5            | 12.5            | 55   |

| -800  | PC2-6400     | 800                                               | 667    | 533    | 400    | 15              | 15              | 55   |

| -667  | PC2-5300     | _                                                 | 667    | 553    | 400    | 15              | 15              | 55   |

| -53E  | PC2-4200     | _                                                 | _      | 553    | 400    | 15              | 15              | 55   |

| -40E  | PC2-3200     | _                                                 | _      | 400    | 400    | 15              | 15              | 55   |

## 512MB, 1GB (x72, ECC, SR) 244-Pin DDR2 SDRAM Mini-RDIMM

### **Table 2: Addressing**

|                      | 512MB             | 1GB               |

|----------------------|-------------------|-------------------|

| Refresh count        | 8K                | 8K                |

| Row address          | 16K A[13:0]       | 16K A[13:0]       |

| Device bank address  | 4 BA[1:0]         | 8 BA[2:0]         |

| Device configuration | 512Mb (64 Meg x8) | 1Gb (128 Meg x 8) |

| Column address       | 1K A[9:0]         | 1K A[9:0]         |

| Module rank address  | 1 SO#             | 1 SO#             |

### Table 3: Part Numbers and Timing Parameters - 512MB

Base device: MT47H64M8, 1 512Mb DDR2 SDRAM

| Part Number <sup>2</sup> | Module<br>Density | Configuration | Module<br>Bandwidth | Memory Clock/<br>Data Rate | Clock Cycles<br>(CL - <sup>t</sup> RCD - <sup>t</sup> RP) |

|--------------------------|-------------------|---------------|---------------------|----------------------------|-----------------------------------------------------------|

| MT9HTF6472PK(I)Z-80E     | 512MB             | 64 Meg x 72   | 6.4 GB/s            | 2.5ns/800 MT/s             | 5-5-5                                                     |

| MT9HTF6472PK(I)Z-800     | 512MB             | 64 Meg x 72   | 6.4 GB/s            | 2.5ns/800 MT/s             | 6-6-6                                                     |

| MT9HTF6472PK(I)Z-667     | 512MB             | 64 Meg x 72   | 5.3 GB/s            | 3.0ns/667 MT/s             | 5-5-5                                                     |

### Table 4: Part Numbers and Timing Parameters - 1GB

Base device: MT47H128M8, 1 1Gb DDR2 SDRAM

| Part Number <sup>2</sup> | Module<br>Density | Configuration | Module<br>Bandwidth | Memory Clock/<br>Data Rate | Clock Cycles<br>(CL- <sup>t</sup> RCD- <sup>t</sup> RP) |

|--------------------------|-------------------|---------------|---------------------|----------------------------|---------------------------------------------------------|

| MT9HTF12872PK(I)Z-80E    | 1GB               | 128 Meg x 72  | 6.4 GB/s            | 2.5ns/800 MT/s             | 5-5-5                                                   |

| MT9HTF12872PK(I)Z-800    | 1GB               | 128 Meg x 72  | 6.4 GB/s            | 2.5ns/800 MT/s             | 6-6-6                                                   |

| MT9HTF12872PK(I)Z-667    | 1GB               | 128 Meg x 72  | 5.3 GB/s            | 3.0ns/667 MT/s             | 5-5-5                                                   |

Notes: 1. Data sheets for the base devices can be found on Micron's Web site.

2. All part numbers end with a two-place code (not shown), designating component and PCB revisions. Consult factory for current revision codes. Example: MT9HTF12872PKZ-80EH1.

## **Pin Assignments**

**Table 5: Pin Assignments**

|     | 2               | 244-Pin VLP Mini-RDIMM Front |                     |     |                 |     |                 | 244-Pin VLP Mini-RDIMM Back                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     |                 | k   |                 |     |                    |

|-----|-----------------|------------------------------|---------------------|-----|-----------------|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|-----|-----------------|-----|--------------------|

| Pin | Symbol          | Pin                          | Symbol              | Pin | Symbol          | Pin | Symbol          | Pin Symbol |                 |     |                 |     | Symbol          |     |                    |

| 1   | $V_{REF}$       | 32                           | V <sub>SS</sub>     | 63  | $V_{DDQ}$       | 94  | DQS5#           | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 154 | DQ28            | 185 | А3              | 216 | NC                 |

| 2   | V <sub>SS</sub> | 33                           | DQ24                | 64  | A2              | 95  | DQS5            | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ4             | 155 | DQ29            | 186 | A1              | 217 | V <sub>SS</sub>    |

| 3   | DQ0             | 34                           | DQ25                | 65  | $V_{DD}$        | 96  | V <sub>SS</sub> | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ5             | 156 | V <sub>SS</sub> | 187 | $V_{DD}$        | 218 | DQ46               |

| 4   | DQ1             | 35                           | V <sub>SS</sub>     | 66  | V <sub>SS</sub> | 97  | DQ42            | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 157 | DM3             | 188 | CK0             | 219 | DQ47               |

| 5   | V <sub>SS</sub> | 36                           | DQS3#               | 67  | V <sub>SS</sub> | 98  | DQ43            | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DM0             | 158 | NC              | 189 | CK0#            | 220 | V <sub>SS</sub>    |

| 6   | DQS0#           | 37                           | DQS3                | 68  | Par_In          | 99  | $V_{SS}$        | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC              | 159 | $V_{SS}$        | 190 | $V_{DD}$        | 221 | DQ52               |

| 7   | DQS0            | 38                           | V <sub>SS</sub>     | 69  | $V_{DD}$        | 100 | DQ48            | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 160 | DQ30            | 191 | A0              | 222 | DQ53               |

| 8   | V <sub>SS</sub> | 39                           | DQ26                | 70  | A10             | 101 | DQ49            | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ6             | 161 | DQ31            | 192 | BA1             | 223 | $V_{SS}$           |

| 9   | DQ2             | 40                           | DQ27                | 71  | BA0             | 102 | V <sub>SS</sub> | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ7             | 162 | $V_{SS}$        | 193 | $V_{DD}$        | 224 | NC                 |

| 10  | DQ3             | 41                           | V <sub>SS</sub>     | 72  | $V_{DD}$        | 103 | SA2             | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 163 | CB4             | 194 | RAS#            | 225 | NC                 |

| 11  | V <sub>SS</sub> | 42                           | CB0                 | 73  | WE#             | 104 | NC              | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ12            | 164 | CB5             | 195 | $V_{DDQ}$       | 226 | V <sub>SS</sub>    |

| 12  | DQ8             | 43                           | CB1                 | 74  | $V_{DDQ}$       | 105 | V <sub>SS</sub> | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ13            | 165 | $V_{SS}$        | 196 | S0#             | 227 | DM6                |

| 13  | DQ9             | 44                           | V <sub>SS</sub>     | 75  | CAS#            | 106 | DQS6#           | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 166 | DM8             | 197 | $V_{DDQ}$       | 228 | NC                 |

| 14  | $V_{SS}$        | 45                           | DQS8#               | 76  | $V_{DDQ}$       | 107 | DQS6            | 136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DM1             | 167 | NC              | 198 | ODT0            | 229 | $V_{SS}$           |

| 15  | DQS1#           | 46                           | DQS8                | 77  | NC              | 108 | V <sub>SS</sub> | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC              | 168 | $V_{SS}$        | 199 | A13             | 230 | DQ54               |

| 16  | DQS1            | 47                           | V <sub>SS</sub>     | 78  | NC              | 109 | DQ50            | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 169 | CB6             | 200 | $V_{DD}$        | 231 | DQ55               |

| 17  | $V_{SS}$        | 48                           | CB2                 | 79  | $V_{DDQ}$       | 110 | DQ51            | 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC              | 170 | CB7             | 201 | NC              | 232 | $V_{SS}$           |

| 18  | RESET#          | 49                           | CB3                 | 80  | NC              | 111 | $V_{SS}$        | 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC              | 171 | $V_{SS}$        | 202 | $V_{SS}$        | 233 | DQ60               |

| 19  | NC              | 50                           | V <sub>SS</sub>     | 81  | V <sub>SS</sub> | 112 | DQ56            | 141                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 172 | NC              | 203 | DQ36            | 234 | DQ61               |

| 20  | $V_{SS}$        | 51                           | NC                  | 82  | DQ32            | 113 | DQ57            | 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ14            | 173 | $V_{DDQ}$       | 204 | DQ37            | 235 | $V_{SS}$           |

| 21  | DQ10            | 52                           | $V_{DDQ}$           | 83  | DQ33            | 114 | $V_{SS}$        | 143                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ15            | 174 | NC              | 205 | $V_{SS}$        | 236 | DM7                |

| 22  | DQ11            | 53                           | CKE0                | 84  | $V_{SS}$        | 115 | DQS7#           | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 175 | $V_{DD}$        | 206 | DM4             | 237 | NC                 |

| 23  | V <sub>SS</sub> | 54                           | V <sub>DD</sub>     | 85  | DQS4#           | 116 | DQS7            | 145                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ20            | 176 | A15             | 207 | NC              | 238 | $V_{SS}$           |

| 24  | DQ16            | 55                           | NC/BA2 <sup>1</sup> | 86  | DQS4            | 117 | V <sub>SS</sub> | 146                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ21            | 177 | A14             | 208 | $V_{SS}$        | 239 | DQ62               |

| 25  | DQ17            | 56                           | Err_Out#            | 87  | V <sub>SS</sub> | 118 | DQ58            | 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 178 | $V_{DDQ}$       | 209 | DQ38            | 240 | DQ63               |

| 26  | V <sub>SS</sub> | 57                           | $V_{DDQ}$           | 88  | DQ34            | 119 | DQ59            | 148                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DM2             | 179 | A12             | 210 | DQ39            | 241 | V <sub>SS</sub>    |

| 27  | DQS2#           | 58                           | A11                 | 89  | DQ35            | 120 | V <sub>SS</sub> | 149                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NC              | 180 | A9              | 211 | $V_{SS}$        | 242 | SDA                |

| 28  | DQS2            | 59                           | A7                  | 90  | $V_{SS}$        | 121 | SA0             | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>SS</sub> | 181 | $V_{DD}$        | 212 | DQ44            | 243 | SCL                |

| 29  | V <sub>SS</sub> | 60                           | $V_{DD}$            | 91  | DQ40            | 122 | SA1             | 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ22            | 182 | A8              | 213 | DQ45            | 244 | V <sub>DDSPD</sub> |

| 30  | DQ18            | 61                           | A5                  | 92  | DQ41            |     |                 | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DQ23            | 183 | A6              | 214 | V <sub>SS</sub> |     |                    |