## 8-Bit Serial-Input/Parallel-Output Shift Register

## High–Performance Silicon–Gate CMOS

The MC74HC164B is identical in pinout to the LS164. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs.

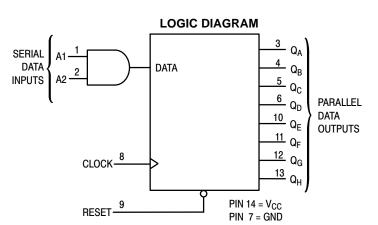

The MC74HC164B is an 8-bit, serial-input to parallel-output shift register. Two serial data inputs, A1 and A2, are provided so that one input may be used as a data enable. Data is entered on each rising edge of the clock. The active-low asynchronous Reset overrides the Clock and Serial Data inputs. Schmitt-trigger action at the Clock input enhances the device's tolerance to slower rise and fall times and immunity to noise of the input clock signal.

#### Features

- Output Drive Capability: 10 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 V to 6.0 V

- Low Input Current: 1 μA

- High Noise Immunity Characteristic of CMOS Devices

- In Compliance with the JEDEC Standard No. 7 A Requirements

- Chip Complexity: 244 FETs or 61 Equivalent Gates

- NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

MARKING DIAGRAMS <sup>14</sup> A A A A A A A A SOIC-14 HC164BG **D SUFFIX** AWLYWW CASE 751A 88888 14 AAAAAAA HC TSSOP-14 164B DT SUFFIX AI YW CASE 948G нннннн = Assembly Location A L, WL = Wafer Lot = Year Υ W, WW = Work Week G or -= Pb-Free Package (Note: Microdot may be in either location)

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

#### **PIN ASSIGNMENT**

| A1 [             | 1• | 14 | ∃ v <sub>cc</sub> |

|------------------|----|----|-------------------|

| A2 [             | 2  | 13 | ] Q <sub>H</sub>  |

| Q <sub>A</sub> [ | 3  | 12 | ] Q <sub>G</sub>  |

| Q <sub>B</sub> [ | 4  | 11 | ] Q <sub>F</sub>  |

| Q <sub>C</sub> [ | 5  | 10 | ] Q <sub>E</sub>  |

| Q <sub>D</sub> [ | 6  | 9  | ] RESET           |

| gnd [            | 7  | 8  | CLOCK             |

|                  |    |    |                   |

#### **FUNCTION TABLE**

| Inputs |       |    |    |                           | Outp            | outs |                 |

|--------|-------|----|----|---------------------------|-----------------|------|-----------------|

| Reset  | Clock | A1 | A2 | $\mathbf{Q}_{\mathbf{A}}$ | $Q_B$           |      | Q <sub>H</sub>  |

| L      | Х     | Х  | Х  | L                         | L               |      | L               |

| н      | ~     | Х  | Х  | No Change                 |                 |      | Э               |

| н      |       | н  | D  | D                         | Q <sub>An</sub> |      | Q <sub>Gn</sub> |

| н      | 7     | D  | Н  | D                         | $Q_{An}$        |      | Q <sub>Gn</sub> |

D = data input

$Q_{An} - Q_{Gn}$  = data shifted from the preceding stage on a rising edge at the clock input.

#### **ORDERING INFORMATION**

| Device            | Package              | Shipping <sup>†</sup> |

|-------------------|----------------------|-----------------------|

| MC74HC164BDG      |                      | 55 Units / Rail       |

| MC74HC164BDR2G    | SOIC-14<br>(Pb-Free) | 2500 / Tape & Reel    |

| NLV74HC164BDR2G*  | (******)             | 2500 / Tape & Reel    |

| MC74HC164BDTR2G   | TSSOP-14             | 2500 / Tape & Reel    |

| NLV74HC164BDTR2G* | (Pb-Free)            | 2500 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. \*NLV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP

Capable

#### MAXIMUM RATINGS

| Symbol           | Parameter                                                                  | Value                         | Unit |

|------------------|----------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>  | DC Supply Voltage (Referenced to GND)                                      | - 0.5 to + 7.0                | V    |

| V <sub>in</sub>  | DC Input Voltage (Referenced to GND)                                       | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Vout             | DC Output Voltage (Referenced to GND)                                      | $-0.5$ to V_CC + 0.5          | V    |

| l <sub>in</sub>  | DC Input Current, per Pin                                                  | ± 20                          | mA   |

| I <sub>out</sub> | DC Output Current, per Pin                                                 | ± 25                          | mA   |

| I <sub>CC</sub>  | DC Supply Current, V <sub>CC</sub> and GND Pins                            | ± 50                          | mA   |

| P <sub>D</sub>   | Power Dissipation in Still Air, SOIC Package†<br>TSSOP Package†            | 500<br>450                    | mW   |

| T <sub>stg</sub> | Storage Temperature                                                        | – 65 to + 150                 | °C   |

| TL               | Lead Temperature, 1 mm from Case for 10 Seconds<br>(SOIC or TSSOP Package) | 260                           | °C   |

This device contains protection circuitry to guard against damage due to high static voltages or electric fields. However, precautions must be taken to avoid applications of any voltage higher than maximum rated voltages to this high–impedance circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range GND  $\leq (V_{in} \text{ or } V_{out}) \leq V_{CC}$ .

Unused inputs must always be tied to an appropriate logic voltage level (e.g., either GND or  $V_{CC}$ ). Unused outputs must be left open.

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

+Derating — SOIC Package: – 7 mW/°C from 65° to 125°C TSSOP Package: – 6.1 mW/°C from 65° to 125°C

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol                             | Parameter                                                                  | Min                                      | Max             | Unit                             |    |

|------------------------------------|----------------------------------------------------------------------------|------------------------------------------|-----------------|----------------------------------|----|

| V <sub>CC</sub>                    | DC Supply Voltage (Referenced to GND)                                      |                                          |                 | 6.0                              | V  |

| V <sub>in</sub> , V <sub>out</sub> | DC Input Voltage, Output Voltage (Referenced GND)                          | 0                                        | V <sub>CC</sub> | V                                |    |

| T <sub>A</sub>                     | Operating Temperature, All Package Types                                   | Operating Temperature, All Package Types |                 |                                  | °C |

| t <sub>r</sub> , t <sub>f</sub>    | Input Rise and Fall Time $V_{CC} =$<br>(Figure 1) $V_{CC} =$<br>$V_{CC} =$ | 2.0 V<br>4.5 V<br>6.0 V                  | 0<br>0<br>0     | No Limit<br>No Limit<br>No Limit | ns |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)

|                                |                                                                 |                                                                                                                                                                            |                          | Guaranteed Limit             |                              |                              |      |

|--------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|------------------------------|------------------------------|------|

| Symbol                         | Parameter                                                       | Test Conditions                                                                                                                                                            | v <sub>cc</sub><br>v     | –55°C to<br>25°C             | ≤ 85°C                       | ≤ 125°C                      | Unit |

| V <sub>T+</sub><br>max         | Maximum Positive–Going Input<br>Threshold Voltage<br>(Figure 3) | V <sub>out</sub> = 0.1V<br> I <sub>out</sub>   ≤ 20µA                                                                                                                      | 2.0<br>3.0<br>4.5<br>6.0 | 1.50<br>2.15<br>3.15<br>4.20 | 1.50<br>2.15<br>3.15<br>4.20 | 1.50<br>2.15<br>3.15<br>4.20 | V    |

| V <sub>T+</sub> min            | Minimum Positive–Going Input<br>Threshold Voltage<br>(Figure 3) | V <sub>out</sub> = 0.1V<br> I <sub>out</sub>   ≤ 20µA                                                                                                                      | 2.0<br>3.0<br>4.5<br>6.0 | 1.0<br>1.5<br>2.3<br>3.0     | 0.95<br>1.45<br>2.25<br>2.95 | 0.95<br>1.45<br>2.25<br>2.95 | V    |

| V <sub>T-</sub><br>max         | Maximum Negative–Going Input<br>Threshold Voltage<br>(Figure 3) | $V_{out} = V_{CC} - 0.1V$<br>$ I_{out}  \le 20\mu A$                                                                                                                       | 2.0<br>3.0<br>4.5<br>6.0 | 0.9<br>1.4<br>2.0<br>2.6     | 0.95<br>1.45<br>2.05<br>2.65 | 0.95<br>1.45<br>2.05<br>2.65 | V    |

| V <sub>T-</sub> min            | Minimum Negative–Going Input<br>Threshold Voltage<br>(Figure 3) | $V_{out} = V_{CC} - 0.1V$<br>$ I_{out}  \le 20\mu A$                                                                                                                       | 2.0<br>3.0<br>4.5<br>6.0 | 0.3<br>0.5<br>0.9<br>1.2     | 0.3<br>0.5<br>0.9<br>1.2     | 0.3<br>0.5<br>0.9<br>1.2     | V    |

| V <sub>H</sub> max<br>(Note 1) | Maximum Hysteresis Voltage<br>(Figure 3)                        | $V_{out} = 0.1V \text{ or } V_{CC} - 0.1V$<br>$ I_{out}  \le 20 \mu A$                                                                                                     | 2.0<br>3.0<br>4.5<br>6.0 | 1.20<br>1.65<br>2.25<br>3.00 | 1.20<br>1.65<br>2.25<br>3.00 | 1.20<br>1.65<br>2.25<br>3.00 | V    |

| V <sub>H</sub> min<br>(Note 1) | Minimum Hysteresis Voltage<br>(Figure 3)                        | $V_{out} = 0.1V \text{ or } V_{CC} - 0.1V$<br>$ I_{out}  \le 20 \mu A$                                                                                                     | 2.0<br>3.0<br>4.5<br>6.0 | 0.20<br>0.25<br>0.40<br>0.50 | 0.20<br>0.25<br>0.40<br>0.50 | 0.20<br>0.25<br>0.40<br>0.50 | V    |

| V <sub>OH</sub>                | Minimum High-Level Output<br>Voltage                            | $ V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20 \ \mu \text{A}$                                                                                                 | 2.0<br>4.5<br>6.0        | 1.9<br>4.4<br>5.9            | 1.9<br>4.4<br>5.9            | 1.9<br>4.4<br>5.9            | V    |

|                                |                                                                 | $ \begin{array}{ll} V_{in} = V_{IH} \text{ or } V_{IL} &  I_{out}  \leq 2.4 \text{ mA} \\ &  I_{out}  \leq 4.0 \text{ mA} \\ &  I_{out}  \leq 5.2 \text{ mA} \end{array} $ | 3.0<br>4.5<br>6.0        | 2.48<br>3.98<br>5.48         | 2.34<br>3.84<br>5.34         | 2.20<br>3.70<br>5.20         |      |

| V <sub>OL</sub>                | Maximum Low–Level Output<br>Voltage                             | $V_{in} = V_{IH} \text{ or } V_{IL}$<br>$ I_{out}  \le 20 \ \mu\text{A}$                                                                                                   | 2.0<br>4.5<br>6.0        | 0.1<br>0.1<br>0.1            | 0.1<br>0.1<br>0.1            | 0.1<br>0.1<br>0.1            | V    |

|                                |                                                                 | $ \begin{array}{ll} V_{in} = V_{IH} \text{ or } V_{IL} &  I_{out}  \leq 2.4 \text{ mA} \\  I_{out}  \leq 4.0 \text{ mA} \\  I_{out}  \leq 5.2 \text{ mA} \end{array} $     | 3.0<br>4.5<br>6.0        | 0.26<br>0.26<br>0.26         | 0.33<br>0.33<br>0.33         | 0.40<br>0.40<br>0.40         |      |

| l <sub>in</sub>                | Maximum Input Leakage Current                                   | V <sub>in</sub> = V <sub>CC</sub> or GND                                                                                                                                   | 6.0                      | ±0.1                         | ± 1.0                        | ± 1.0                        | μΑ   |

| I <sub>CC</sub>                | Maximum Quiescent Supply<br>Current (per Package)               | $V_{in} = V_{CC} \text{ or } GND$<br>$I_{out} = 0 \ \mu A$                                                                                                                 | 6.0                      | 4                            | 40                           | 160                          | μΑ   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions. 1.  $V_H min > (V_{T+} min) - (V_{T-} max); V_H max = (V_{T+} max) - (V_{T-} min).$

|                                        |                                                                 |                                         | Gu                     | Guaranteed Limit       |                        |      |

|----------------------------------------|-----------------------------------------------------------------|-----------------------------------------|------------------------|------------------------|------------------------|------|

| Symbol                                 | Parameter                                                       | V <sub>CC</sub><br>V                    | -55°C to<br>25°C       | ≤ 85°C                 | ≤ 125°C                | Unit |

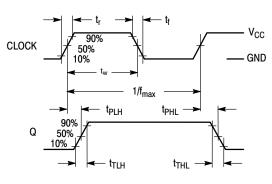

| f <sub>max</sub>                       | Maximum Clock Frequency (50% Duty Cycle)<br>(Figures 1 and 4)   | 2.0<br>3.0<br>4.5<br>6.0                | 10<br>20<br>40<br>50   | 10<br>20<br>35<br>45   | 10<br>20<br>30<br>40   | MHz  |

| t <sub>PLH</sub> ,<br>t <sub>PHL</sub> | Maximum Propagation Delay, Clock to Q<br>(Figures 1 and 4)      | 2.0<br>3.0<br>4.5<br>6.0                | 160<br>100<br>32<br>27 | 200<br>150<br>40<br>34 | 250<br>200<br>48<br>42 | ns   |

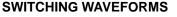

| t <sub>PHL</sub>                       | Maximum Propagation Delay, Reset to Q<br>(Figures 2 and 4)      | 2.0<br>3.0<br>4.5<br>6.0                | 175<br>100<br>35<br>30 | 220<br>150<br>44<br>37 | 260<br>200<br>53<br>45 | ns   |

| t <sub>TLH</sub> ,<br>t <sub>THL</sub> | Maximum Output Transition Time, Any Output<br>(Figures 1 and 4) | 2.0<br>3.0<br>4.5<br>6.0                | 75<br>27<br>15<br>13   | 95<br>32<br>19<br>16   | 110<br>36<br>22<br>19  | ns   |

| C <sub>in</sub>                        | Maximum Input Capacitance                                       | _                                       | 10                     | 10                     | 10                     | pF   |

|                                        |                                                                 | Typical @ 25°C, V <sub>CC</sub> = 5.0 V |                        | <sub>C</sub> = 5.0 V   |                        |      |

| C <sub>PD</sub>                        | Power Dissipation Capacitance (Per Package)*                    |                                         |                        | 180                    |                        | pF   |

#### **AC ELECTRICAL CHARACTERISTICS** ( $C_L = 50 \text{ pF}$ , Input $t_r = t_f = 6 \text{ ns}$ )

#### TIMING REQUIREMENTS (Input t<sub>r</sub> = t<sub>f</sub> = 6 ns)

|                  |                                                              |                          | Guaranteed Limit     |                      |                      |      |

|------------------|--------------------------------------------------------------|--------------------------|----------------------|----------------------|----------------------|------|

| Symbol           | Parameter                                                    | V <sub>CC</sub><br>V     | -55°C to<br>25°C     | ≤ 85°C               | ≤ 125°C              | Unit |

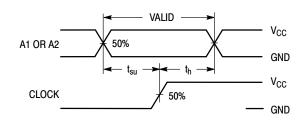

| t <sub>su</sub>  | Minimum Setup Time, A1 or A2 to Clock<br>(Figure 3)          | 2.0<br>3.0<br>4.5<br>6.0 | 25<br>15<br>7<br>5   | 35<br>20<br>8<br>6   | 40<br>25<br>9<br>6   | ns   |

| t <sub>h</sub>   | Minimum Hold Time, Clock to A1 or A2<br>(Figure 3)           | 2.0<br>3.0<br>4.5<br>6.0 | 3333                 | 3<br>3<br>3<br>3     | 3<br>3<br>3<br>3     | ns   |

| t <sub>rec</sub> | Minimum Recovery Time, Reset Inactive to Clock<br>(Figure 2) | 2.0<br>3.0<br>4.5<br>6.0 | 3<br>3<br>3<br>3     | 3<br>3<br>3<br>3     | 3<br>3<br>3<br>3     | ns   |

| t <sub>w</sub>   | Minimum Pulse Width, Clock<br>(Figure 1)                     | 2.0<br>3.0<br>4.5<br>6.0 | 50<br>26<br>12<br>10 | 60<br>35<br>15<br>12 | 75<br>45<br>20<br>15 | ns   |

| t <sub>w</sub>   | Minimum Pulse Width, Reset<br>(Figure 2)                     | 2.0<br>3.0<br>4.5<br>6.0 | 50<br>26<br>12<br>10 | 60<br>35<br>15<br>12 | 75<br>45<br>20<br>15 | ns   |

#### **PIN DESCRIPTIONS**

#### INPUTS

#### A1, A2 (Pins 1, 2)

Serial Data Inputs. Data at these inputs determine the data to be entered into the first stage of the shift register. For a high level to be entered into the shift register, both A1 and A2 inputs must be high, thereby allowing one input to be used as a data–enable input. When only one serial input is used, the other must be connected to  $V_{CC}$ .

#### Clock (Pin 8)

Shift Register Clock. A positive–going transition on this pin shifts the data at each stage to the next stage. The shift

register is completely static, allowing clock rates down to DC in a continuous or intermittent mode.

#### OUTPUTS

#### Q<sub>A</sub> – Q<sub>H</sub> (Pins 3, 4, 5, 6, 10, 11, 12, 13)

Parallel Shift Register Outputs. The shifted data is presented at these outputs in true, or noninverted, form.

#### **CONTROL INPUT**

#### Reset (Pin 9)

Active–Low, Asynchronous Reset Input. A low voltage applied to this input resets all internal flip–flops and sets Outputs  $Q_A - Q_H$  to the low level state.

Figure 1.

Figure 2.

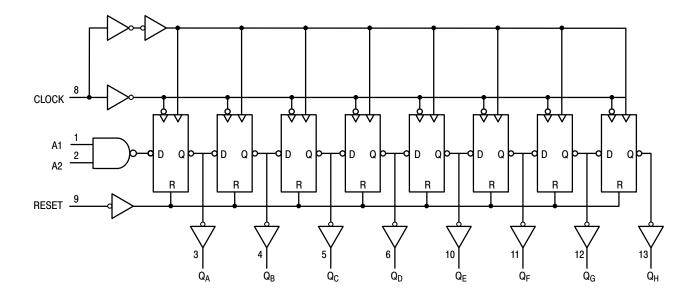

Figure 3.

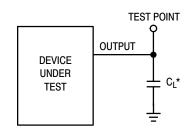

\*Includes all probe and jig capacitance

Figure 4. Test Circuit

#### EXPANDED LOGIC DIAGRAM

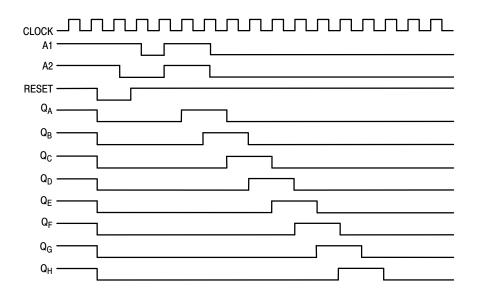

#### **TIMING DIAGRAM**

# DUSEM

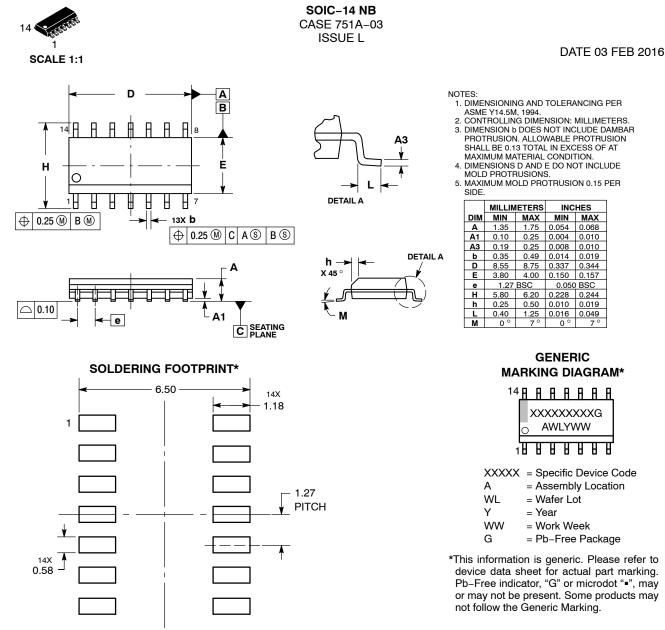

0.068

0.019

0.344

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **STYLES ON PAGE 2**

Electronic versions are uncontrolled except when accessed directly from the Document Repository. DOCUMENT NUMBER: 98ASB42565B Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. **DESCRIPTION:** SOIC-14 NB PAGE 1 OF 2 onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

#### SOIC-14 CASE 751A-03 ISSUE L

#### DATE 03 FEB 2016

| STYLE 1:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. ANODE/CATHODE<br>8. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. NO CONNECTION<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                                                                   | STYLE 3:<br>PIN 1. NO CONNECTION<br>2. ANODE<br>3. ANODE<br>4. NO CONNECTION<br>5. ANODE<br>6. NO CONNECTION<br>7. ANODE<br>8. ANODE<br>9. ANODE<br>10. NO CONNECTION<br>11. ANODE<br>12. ANODE<br>13. NO CONNECTION<br>14. COMMON CATHODE                                            | STYLE 4:<br>PIN 1. NO CONNECTION<br>2. CATHODE<br>3. CATHODE<br>4. NO CONNECTION<br>5. CATHODE<br>6. NO CONNECTION<br>7. CATHODE<br>8. CATHODE<br>9. CATHODE<br>10. NO CONNECTION<br>11. CATHODE<br>12. CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. NO CONNECTION<br>7. COMMON ANODE<br>8. COMMON CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. ANODE/CATHODE<br>12. ANODE/CATHODE<br>13. NO CONNECTION<br>14. COMMON ANODE | STYLE 6:<br>PIN 1. CATHODE<br>2. CATHODE<br>3. CATHODE<br>4. CATHODE<br>5. CATHODE<br>6. CATHODE<br>7. CATHODE<br>8. ANODE<br>9. ANODE<br>10. ANODE<br>11. ANODE<br>12. ANODE<br>13. ANODE<br>14. ANODE | STYLE 7:<br>PIN 1. ANODE/CATHODE<br>2. COMMON ANDDE<br>3. COMMON CATHODE<br>4. ANODE/CATHODE<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. ANODE/CATHODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. COMMON CATHODE<br>12. COMMON ANODE<br>13. ANODE/CATHODE<br>14. ANODE/CATHODE | STYLE 8:<br>PIN 1. COMMON CATHODE<br>2. ANODE/CATHODE<br>3. ANODE/CATHODE<br>4. NO CONNECTION<br>5. ANODE/CATHODE<br>6. ANODE/CATHODE<br>7. COMMON ANODE<br>8. COMMON ANODE<br>9. ANODE/CATHODE<br>10. ANODE/CATHODE<br>11. NO CONNECTION<br>12. ANODE/CATHODE<br>13. ANODE/CATHODE<br>14. COMMON CATHODE |

| DOCUMENT NUMBER: | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from the Document Reposite<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |  |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| DESCRIPTION:     | SOIC-14 NB  |                                                                                                                                                                                  | PAGE 2 OF 2 |  |  |  |

|                  |             |                                                                                                                                                                                  |             |  |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative

٥