## STM6513

Dual push-button Smart

Reset<sup>TM</sup> with dual reset outputs and user-selectable setup delay

#### **Features**

- Dual Smart Reset push-button inputs with user-selectable extended reset setup delay (by three-state input logic): t<sub>SRC</sub> = 2, 6, 10 s (min.)

- Capacitor-adjustable reset pulse duration (t<sub>REC1</sub>)

- Power-on reset

- Dual reset output (RST1 is active-high, pushpull type, RST2 is active-low, open-drain)

- Factory-programmable thresholds to monitor V<sub>CC</sub> in the range of 1.575 to 4.625 V typ.

- Operating voltage 1.0 V (active-low output valid) to 5.5 V

- Low supply current 3 µA

- Operating temperature: industrial grade –40 °C to +85 °C

- TDFN8 package: 2 mm x 2 mm x 0.75 mm

- RoHS compliant

#### **Applications**

- Mobile phones, smartphones

- e-books

- MP3 players

- Games

- Portable navigation devices

- Any application that requires delayed reset push-button(s) response for improved system stability.

Contents STM6513

## **Contents**

| 1  | Description                                                                 |

|----|-----------------------------------------------------------------------------|

| 2  | Device overview                                                             |

| 3  | Pin descriptions 8                                                          |

|    | 3.1 Power supply (V <sub>CC</sub> ) 8                                       |

|    | 3.2 Ground (V <sub>SS</sub> )                                               |

|    | 3.3 Smart Reset inputs (SR0, SR1)                                           |

|    | 3.4 User-programmable Smart Reset delay (TSR pin) 8                         |

|    | 3.5 Reset outputs (RST1, RST2)                                              |

|    | 3.6 Adjustable output reset timeout period input pin (TREC <sub>ADJ</sub> ) |

| 4  | Block diagram 10                                                            |

| 5  | Typical operating characteristics                                           |

| 6  | Maximum rating 16                                                           |

| 7  | DC and AC parameters                                                        |

| 8  | Package mechanical data                                                     |

| 9  | Package footprint                                                           |

| 10 | Tape and reel information                                                   |

| 11 | Part numbering                                                              |

| 12 | Package marking information                                                 |

| 13 | Revision history                                                            |

STM6513 List of tables

## List of tables

| Table 1.  | Signal names                                                   | 7    |

|-----------|----------------------------------------------------------------|------|

| Table 2.  | t <sub>REC1</sub> programmed by an ideal external capacitor    | 9    |

| Table 3.  | Absolute maximum ratings                                       |      |

| Table 4.  | Operating and measurement conditions                           | . 17 |

| Table 5.  | DC and AC characteristics                                      | . 18 |

| Table 6.  | Possible V <sub>CC</sub> voltage thresholds                    | . 19 |

| Table 7.  | TDFN – 8-lead 2 x 2 x 0.75 mm, 0.5 mm package mechanical data  | . 21 |

| Table 8.  | Parameter for landing pattern - TDFN - 8-lead 2 x 2 mm package | . 22 |

| Table 9.  | Carrier tape dimensions                                        | . 23 |

| Table 10. | Reel dimensions                                                | . 24 |

| Table 11. | Ordering information scheme                                    | . 26 |

| Table 12. | Package marking                                                | . 27 |

| Table 13. | Document revision history                                      | . 28 |

|           |                                                                |      |

3/29

List of figures STM6513

# **List of figures**

| Figure 1.  | Logic diagram                                                                                    | 6    |

|------------|--------------------------------------------------------------------------------------------------|------|

| Figure 2.  | Pin connections                                                                                  |      |

| Figure 3.  | Block diagram                                                                                    |      |

| Figure 4.  | Typical application diagram                                                                      |      |

| Figure 5.  | Timing waveforms                                                                                 |      |

| Figure 6.  | Smart Reset delay $t_{SRC}$ vs. temperature and supply voltage $V_{CC}$ , $TSR = V_{SS}$         | 10   |

| Figure 7.  | Output reset timeout period t <sub>REC2</sub> vs. temperature and supply voltage V <sub>CC</sub> |      |

|            | (t <sub>REC</sub> option E)                                                                      |      |

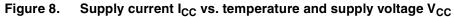

| Figure 8.  | Supply current I <sub>CC</sub> vs. temperature and supply voltage V <sub>CC</sub>                | . 13 |

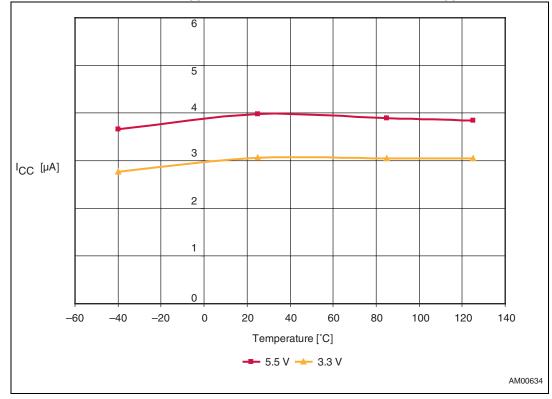

| Figure 9.  | Reset voltage V <sub>RST</sub> (falling) vs. temperature                                         |      |

|            | (threshold option S, 2.925 V typ.)                                                               | . 14 |

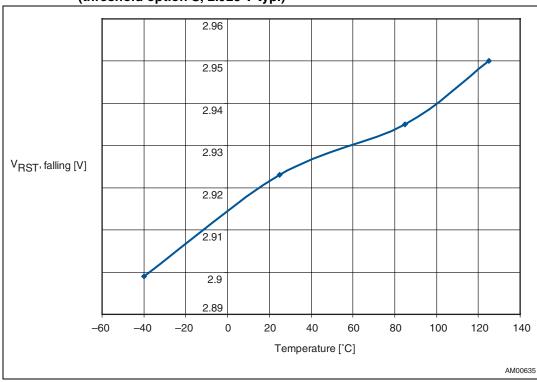

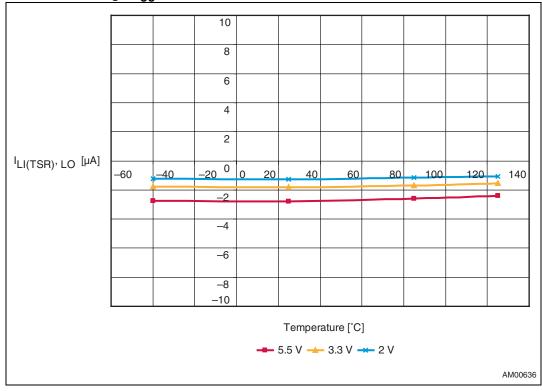

| Figure 10. | Input leakage current, TSR pin, logic low vs. temperature and supply voltage V <sub>CC</sub>     | . 14 |

| Figure 11. | Input leakage current, TSR pin, logic high vs. temperature and supply voltage V <sub>CC</sub>    | . 15 |

| Figure 12. | AC testing input/output waveforms                                                                | 17   |

| Figure 13. | TDFN - 8-lead, 2 x 2 x 0.75 mm, 0.5 mm pitch                                                     | . 20 |

| Figure 14. | Landing pattern - TDFN - 8-lead 2 x 2 mm without thermal pad                                     | . 22 |

| Figure 15. | Carrier tape                                                                                     | . 23 |

| Figure 16. | Reel dimensions                                                                                  | . 24 |

| Figure 17. | Tape trailer/leader                                                                              | . 25 |

| Figure 18. | Pin 1 orientation                                                                                |      |

| Figure 10  | Package marking area, ton view                                                                   | 27   |

STM6513 Description

### 1 Description

The STM6513 has two separate delayed Smart Reset inputs ( $\overline{SR0}$ ,  $\overline{SR1}$ ) which when taken low simultaneously provide three user-selectable delayed Smart Reset setup time ( $t_{SRC}$ ) options of 2 s, 6 s and 10 s. These are selected through a three-state TSR input pin: when connected to ground,  $t_{SRC}=2$  s; when left open,  $t_{SRC}=6$  s; when connected to  $V_{CC}$ ,  $t_{SRC}=10$  s (all the times are minimum). There are two reset outputs, both going active simultaneously after both the Smart Reset inputs were held active for the selected  $t_{SRC}$  delay time. The first reset output, RST1, is active-high, push-pull; the second reset output,  $\overline{RST2}$ , is active-low, open-drain requiring an external pull-up resistor. The duration of the output reset pulses is independently programmable:  $t_{REC1}$  is user-programmable (by external capacitor  $C_{tREC}$ ),  $t_{REC2}$  is factory-programmed to 210 ms (typ.), with the option of 360 ms typ. Additionally, the  $V_{CC}$  is monitored and if it drops below the selected  $V_{RST}$  threshold, both the reset outputs go active and remain so while  $V_{CC}$  is below the  $V_{RST}$  threshold, plus the defined duration of the reset pulse  $t_{RSC}$  on each output.

#### **Smart Reset devices**

The Smart Reset device family STM65xx provides a useful feature that ensures inadvertent short reset push-button closures do not cause system resets. This is done by implementing extended Smart Reset input delay ( $t_{SRC}$ ). Once the valid Smart Reset input levels and setup delay are met, the device generates an output reset pulse with user-programmable timeout period ( $t_{REC}$ ).

The Smart Reset inputs can be also connected to the applications interrupt to allow the control of both the interrupt pin and the hard reset functions. If the push-buttons are closed for a short time, the processor is only interrupted. If the system still does not respond properly, holding the push-buttons for the extended setup time (t<sub>SRC</sub>) causes hard reset of the processor through the reset outputs. The Smart Reset feature helps significantly increase system stability.

The STM65xx family of Smart Reset devices consists of low current microprocessor reset circuits targeted at applications such as MP3 players, navigation, smartphones or mobile phones; generally any application that requires delayed reset push-button(s) response for improved system stability. The STM65xx devices feature single or dual Smart Reset inputs (SR). The delayed Smart Reset setup time ( $t_{\rm SRC}$ ) options of 2 s, 6 s and 10 s (all min.) are adjustable by an external capacitor on the SRC pin or selectable by three-state logic. The delayed setup period ignores switch closures shorter than  $t_{\rm SRC}$ , thus preventing unwanted resets.

The STM65xx devices have active-low (optionally active-high) open-drain reset (RST) output(s) with or without internal pull-up resistor or push-pull as output options, with factory-programmed or capacitor-adjustable or push-buttons defined output reset pulse duration, with or without power-on reset function.

Some devices also have an undervoltage monitoring feature: the reset output is also asserted when the monitored supply voltage  $V_{CC}$  drops below the specified threshold. The reset output remains asserted for the reset timeout period ( $t_{REC}$ ) after the monitored supply voltage goes above the specified threshold.

Description STM6513

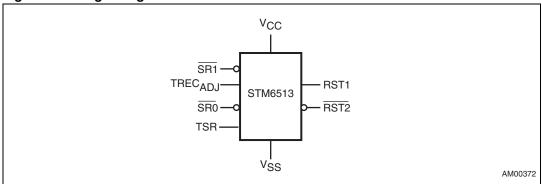

Figure 1. Logic diagram

Figure 2. Pin connections

STM6513 Device overview

## 2 Device overview

Table 1. Signal names

| Symbol              | Input/output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|---------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RST1                | Output       | First reset output, active-high, push-pull.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| RST2                | Output       | Second reset output, active-low, open-drain.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| SR0                 | Input        | Primary push-button Smart Reset input. Active-low.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| SR1                 | Input        | Secondary push-button Smart Reset input. Active-low.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| TSR                 | Input        | A Three-state Smart Reset input delay setup control. When connected to ground, $t_{SRC}=2$ s; when left open, $t_{SRC}=6$ s; when connected to $V_{CC},t_{SRC}=10$ s (all times are minimum). TSR is a DC-type input, intended to be either permanently grounded, permanently connected to $V_{CC}$ or permanently left open. If left open, for improved system glitch immunity it is strongly recommended to connect a 0.1 $\mu\text{F}$ decoupling ceramic capacitor between the TSR and $V_{SS}$ pins. |  |  |  |

| TREC <sub>ADJ</sub> | Input        | Input pin for $t_{REC1}$ reset pulse duration adjustment. Connect an external capacitor $C_{tREC}$ to this pin to determine $t_{REC1}$ ; $t_{REC2}$ is factory-programmed.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| V <sub>CC</sub>     | Supply       | Positive supply voltage input. Power supply for the device and an input for the monitored supply voltage. A 0.1 $\mu F$ decoupling ceramic capacitor is recommended to be connected between $V_{CC}$ and $V_{SS}$ pins.                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>SS</sub>     | Supply       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

Pin descriptions STM6513

### 3 Pin descriptions

#### 3.1 Power supply $(V_{CC})$

This pin is used to provide the power to the Smart Reset device and to monitor the power supply. A 0.1  $\mu$ F decoupling ceramic capacitor is recommended to be connected between  $V_{CC}$  and  $V_{SS}$  pins.

### 3.2 Ground (V<sub>SS</sub>)

This is the ground for the device and all supplies.

### 3.3 Smart Reset inputs (SR0, SR1)

Push-button Smart Reset inputs. Both inputs need to be held active at the same time for at least  $t_{SRC}$  to activate the reset outputs. When only one Smart Reset input is used, connect the unused one permanently to  $V_{SS}$ .

#### 3.4 User-programmable Smart Reset delay (TSR pin)

Used to allow the user to program the setup time before the push-buttons action is validated by reset output. Controlled by different voltage levels on the TSR pin: when connected to ground,  $t_{SRC}=2$  s; when left open,  $t_{SRC}=6$  s; when connected to  $V_{CC},\,t_{SRC}=10$  s (all times are minimum). TSR is a DC-type input, intended to be either permanently grounded, permanently connected to  $V_{CC}$  or permanently left open. If left open, for improved system glitch immunity it is strongly recommended to connect a 0.1  $\mu F$  decoupling ceramic capacitor between the TSR and  $V_{SS}$  pins.

## 3.5 Reset outputs (RST1, RST2)

Reset outputs, RST1 active-high, push-pull type, RST2 active-low, open-drain.

## 3.6 Adjustable output reset timeout period input pin (TREC<sub>ADJ</sub>)

The output reset timeout period ( $t_{REC1}$ ) on RST1 is adjustable by connecting an external capacitor  $C_{tREC}$  to the TREC<sub>ADJ</sub> pin. Calculated  $t_{REC}$  and  $C_{tREC}$  examples are given in *Table 2*. Refer also to *Table 5*.

57

STM6513 Pin descriptions

Table 2. t<sub>REC1</sub> programmed by an ideal external capacitor

| C value (uE)                 |      | Closest common |      |                              |

|------------------------------|------|----------------|------|------------------------------|

| C <sub>tREC</sub> value (μF) | Min. | Тур.           | Max. | C <sub>tREC</sub> value (µF) |

| 0.001                        | 10   | 15             | 20   | 0.001                        |

| 0.002                        | 20   | 30             | 40   | 0.0022                       |

| 0.01                         | 100  | 150            | 200  | 0.01                         |

| 0.014                        | 140  | 210            | 280  | 0.015                        |

| 0.028                        | 280  | 420            | 560  | 0.027                        |

| 0.056                        | 560  | 840            | 1120 | 0.056                        |

| 0.112                        | 1120 | 1680           | 2240 | 0.12                         |

<sup>1.</sup> At 25 ° C. Example calculations based on an ideal capacitor. During application design and component selection it should be considered that the current flowing into the external t<sub>REC</sub> programming capacitor (C<sub>tREC</sub>) is on the order of 100 nA, therefore a low-leakage capacitor (ceramic or film capacitor) should be used and placed as close as possible to the TREC<sub>ADJ</sub> pin. Also an adequate low-leakage PCB environment should be ensured to prevent t<sub>REC</sub> accuracy from being affected. A recommended minimum value of C<sub>tREC</sub> is 0.001 µF.

<sup>2.</sup> In case of repeated activations of the internal  $t_{REC}$  timer, an interval of 10 ms min. is needed between  $t_{REC}$  intervals to fully discharge  $C_{tREC}$ , so that the next  $t_{REC1}$  is as specified.

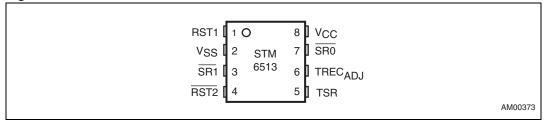

Block diagram STM6513

# 4 Block diagram

Figure 3. Block diagram

STM6513 Block diagram

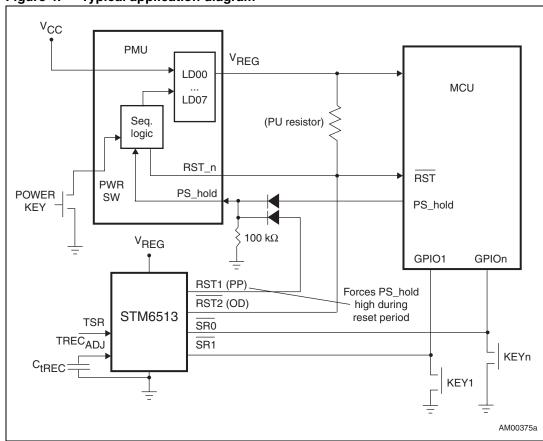

STM6513 hookup with RST1 and  $\overline{RST2}$ , bridging the PS\_hold reset pulse during the microprocessor reset initiated by the STM6513 Smart Reset device:

Figure 4. Typical application diagram

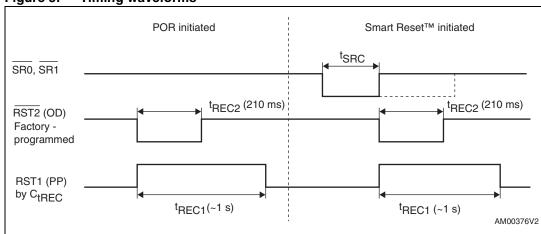

Figure 5. Timing waveforms

# 5 Typical operating characteristics

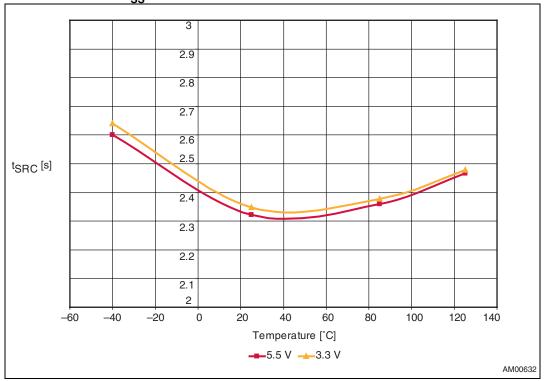

Figure 6. Smart Reset delay  $t_{SRC}$  vs. temperature and supply voltage  $V_{CC}$ ,  $TSR = V_{SS}$

12/29 Doc ID 16490 Rev 2

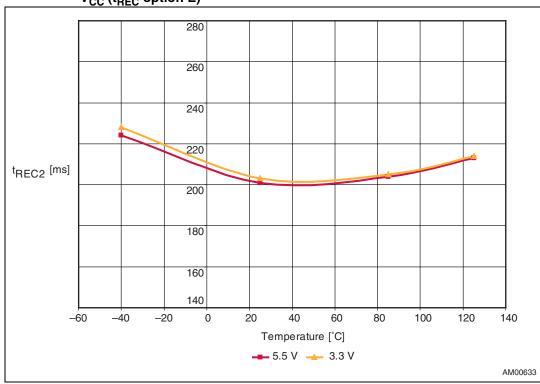

Figure 7. Output reset timeout period  $t_{REC2}$  vs. temperature and supply voltage  $V_{CC}\left(t_{REC}\right)$  option E

57

Doc ID 16490 Rev 2

13/29

Figure 9. Reset voltage V<sub>RST</sub> (falling) vs. temperature (threshold option S, 2.925 V typ.)

57

14/29 Doc ID 16490 Rev 2

Figure 11. Input leakage current, TSR pin, logic high vs. temperature and supply voltage  $V_{\text{CC}}$

Maximum rating STM6513

## 6 Maximum rating

Stressing the device above the rating listed in the *Table 3: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the Operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE Program and other relevant quality documents.

Table 3. Absolute maximum ratings

| Symbol                          | Parameter                                 | Value       | Unit                       |      |

|---------------------------------|-------------------------------------------|-------------|----------------------------|------|

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off) | -55 to +150 | °C                         |      |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds    | 260         | °C                         |      |

| $\theta_{JA}$                   | Thermal resistance (junction to ambient)  | TDFN8       | 149.0                      | °C/W |

| V <sub>IO</sub>                 | Input or output voltage                   |             | -0.3 to 5.5 <sup>(2)</sup> | V    |

| V <sub>CC</sub>                 | Supply voltage                            |             | –0.3 to 7                  | V    |

<sup>1.</sup> Reflow at peak temperature of 260  $^{\circ}\text{C}$  . The time above 255  $^{\circ}\text{C}$  must not exceed 30 s.

<sup>2.</sup> For RST1 -0.3 to  $V_{CC}$  +0.3 V only.

## 7 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in the *Table 5: DC and AC characteristics* that follow, are derived from tests performed under the Measurement Conditions summarized in *Table 4.: Operating and measurement conditions*. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

Table 4. Operating and measurement conditions

| Parameter                                       | Value                      | Unit |

|-------------------------------------------------|----------------------------|------|

| V <sub>CC</sub> supply voltage                  | 1.0 to 5.5                 | V    |

| Ambient operating temperature (T <sub>A</sub> ) | -40 to +85                 | °C   |

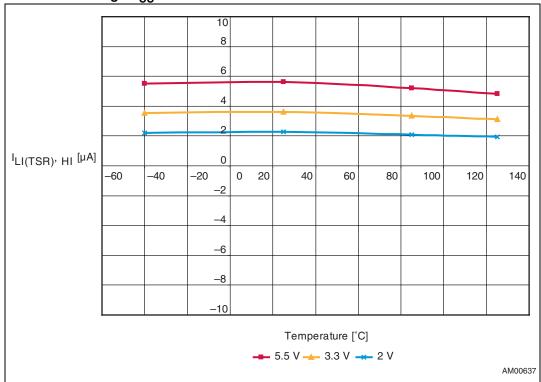

| Input rise and fall times                       | ≤ 5                        | ns   |

| Input pulse voltages                            | 0.2 to 0.8 V <sub>CC</sub> | V    |

| Input and output timing ref. voltages           | 0.3 to 0.7 V <sub>CC</sub> | V    |

Figure 12. AC testing input/output waveforms

Table 5. DC and AC characteristics

| Symbol            | Parameter                                                                     | Test conditions <sup>(1)</sup>                                                         | Min.                               | Typ. <sup>(2)</sup>                | Max.                               | Units |

|-------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|-------|

| V                 | Cumply voltage range                                                          | Reset output valid - active-low                                                        | 1.0                                |                                    | 5.5                                | V     |

| V <sub>CC</sub>   | Supply voltage range                                                          | Reset output valid - active-high                                                       | 1.2                                |                                    | 5.5                                | V     |

|                   | Supply current (V <sub>CC</sub> )                                             | V <sub>CC</sub> = 3.0 V, TSR left open <sup>(3)</sup>                                  |                                    | 3                                  | 5                                  | μΑ    |

| Icc               | Supply current (V <sub>CC</sub> )                                             | V <sub>CC</sub> = 5.0 V, TSR left open                                                 |                                    | 4                                  | 6                                  | μΑ    |

|                   |                                                                               | V <sub>CC</sub> ≥ 4.5 V, sinking 3.2 mA                                                |                                    |                                    | 0.3                                | V     |

| V <sub>OL</sub>   | Reset output voltage low                                                      | V <sub>CC</sub> ≥ 3.3 V, sinking 2.5 mA                                                |                                    |                                    | 0.3                                | V     |

|                   |                                                                               | V <sub>CC</sub> ≥ 1.0 V, sinking 0.1 mA                                                |                                    |                                    | 0.3                                | V     |

|                   | _                                                                             | $V_{CC} \ge 4.5 \text{ V}, I_{SOURCE} = 0.8 \text{ mA}$                                | 0.8 V <sub>CC</sub>                |                                    |                                    | V     |

| V <sub>OH</sub>   | Reset output voltage high, RST1                                               | $V_{CC} \ge 2.7 \text{ V}, I_{SOURCE} = 0.5 \text{ mA}$                                | 0.8 V <sub>CC</sub>                |                                    |                                    | V     |

|                   | , <b>.</b>                                                                    | V <sub>CC</sub> ≥ 1.2 V, I <sub>SOURCE</sub> = 0.05 mA                                 | 0.8 V <sub>CC</sub>                |                                    |                                    | V     |

|                   | Fixed voltage trip                                                            | −40 to +85 °C                                                                          | V <sub>RST</sub> -2.5%             | V <sub>RST</sub>                   | V <sub>RST</sub> +2.5%             | V     |

| V <sub>RST</sub>  | point for V <sub>CC</sub><br>monitoring (refer to<br><i>Table 6</i> )         | 25 °C                                                                                  | V <sub>RST</sub> -2.0%             | V <sub>RST</sub>                   | V <sub>RST</sub> +2.0%             | V     |

| V                 | Lhystoropic of V                                                              | L, M                                                                                   |                                    | 0.5%                               |                                    |       |

| V <sub>HYST</sub> | Hysteresis of V <sub>RST</sub>                                                | T, S, R, Z, Y, W, V                                                                    |                                    | 1%                                 |                                    |       |

|                   | V <sub>CC</sub> to reset delay <sup>(4)</sup>                                 | $V_{CC}$ falling from ( $V_{RST}$ + 100 mV) to ( $V_{RST}$ - 100 mV) at 10 mV/ $\mu$ s |                                    | 20                                 |                                    | μs    |

| _                 | Output reset timeout                                                          | Option E                                                                               | 140                                | 210                                | 280                                | ms    |

| t <sub>REC2</sub> | period on RST2, factory-programmed                                            | Option F                                                                               | 240                                | 360                                | 480                                | ms    |

| t <sub>REC1</sub> | User-adjustable output reset timeout period on RST1 Refer to <i>Table 2</i> . |                                                                                        | 10 000 x<br>C <sub>tREC</sub> (μF) | 15 000 x<br>C <sub>tREC</sub> (μF) | 20 000 x<br>C <sub>tREC</sub> (μF) | ms    |

18/29 Doc ID 16490 Rev 2

Table 5. DC and AC characteristics (continued)

| Symbol               | Parameter                                   | Test conditions <sup>(1)</sup>             | Min.                 | Typ. <sup>(2)</sup> | Max.                | Units |  |  |  |

|----------------------|---------------------------------------------|--------------------------------------------|----------------------|---------------------|---------------------|-------|--|--|--|

| Smart Re             | Smart Reset inputs (SRx)                    |                                            |                      |                     |                     |       |  |  |  |

|                      |                                             | TSR = V <sub>SS</sub>                      | 2                    | 2.5                 | 3                   | S     |  |  |  |

| t <sub>SRC</sub>     | Smart Reset delay                           | TSR = floating                             | 6                    | 7.5                 | 9                   | S     |  |  |  |

|                      |                                             | TSR = V <sub>CC</sub>                      | 10                   | 12.5                | 15                  | S     |  |  |  |

| V <sub>IL</sub>      | SR0, SR1 input voltage low                  |                                            | V <sub>SS</sub> -0.3 |                     | 0.3 V <sub>CC</sub> | ٧     |  |  |  |

| V <sub>IH</sub>      | SR0, SR1 input voltage high                 |                                            | 0.7 V <sub>CC</sub>  |                     | 5.5                 | ٧     |  |  |  |

|                      | Input glitch immunity <sup>(5)</sup>        | Corresponds to the actual t <sub>SRC</sub> |                      | t <sub>SRC</sub>    |                     | s     |  |  |  |

| I <sub>LI(SR)</sub>  | Input leakage<br>current (SR0, SR1<br>pins) |                                            | -1                   |                     | 1                   | μА    |  |  |  |

| I <sub>LI(TSR)</sub> | Input leakage<br>current (TSR pin)          |                                            | -5                   |                     | 7                   | μΑ    |  |  |  |

- 1. Valid for ambient operating temperature:  $T_A = -40$  to +85 °C;  $V_{CC} = 1.0$  V to 5.5 V (except where noted).

- 2. Typical value is at 25  $^{\circ}\text{C}$  and  $\text{V}_{\text{CC}}$  = 3.3 V unless otherwise noted.

- 3. For devices with  $V_{RST}$  < 3.0 V.

- 4. Guaranteed by design.

- 5. Input glitch immunity is equal to  $t_{\mbox{\footnotesize SRC}}$  (when both SR inputs are low), otherwise infinite.

Table 6. Possible V<sub>CC</sub> voltage thresholds

| V <sub>CC</sub> monitoring | Turo  | ±2.5% (–40 °C to +85 °C) |       | ±2.0% (25 °C) |       | Unit  |

|----------------------------|-------|--------------------------|-------|---------------|-------|-------|

| threshold V <sub>RST</sub> | Тур.  | Min.                     | Max.  | Min.          | Max.  | Offic |

| L (falling)                | 4.625 | 4.509                    | 4.741 | 4.533         | 4.718 | V     |

| M (falling)                | 4.375 | 4.266                    | 4.484 | 4.288         | 4.463 | V     |

| T (falling)                | 3.075 | 2.998                    | 3.152 | 3.014         | 3.137 | V     |

| S (falling)                | 2.925 | 2.852                    | 2.998 | 2.867         | 2.984 | V     |

| R (falling)                | 2.625 | 2.559                    | 2.691 | 2.573         | 2.678 | V     |

| Z (falling)                | 2.313 | 2.255                    | 2.371 | 2.267         | 2.359 | V     |

| Y (falling)                | 2.188 | 2.133                    | 2.243 | 2.144         | 2.232 | V     |

| W (falling)                | 1.665 | 1.623                    | 1.707 | 1.632         | 1.698 | V     |

| V (falling)                | 1.575 | 1.536                    | 1.614 | 1.544         | 1.607 | V     |

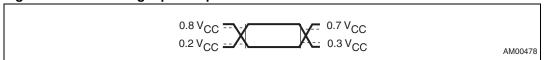

#### Package mechanical data 8

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

Figure 13. TDFN - 8-lead, 2 x 2 x 0.75 mm, 0.5 mm pitch

Table 7. TDFN – 8-lead 2 x 2 x 0.75 mm, 0.5 mm package mechanical data

| Cymhal   | Dimension (mm) |      |      | Dimension (inches) |       |       |

|----------|----------------|------|------|--------------------|-------|-------|

| Symbol   | Min.           | Nom. | Max. | Min.               | Nom.  | Max.  |

| А        | 0.70           | 0.75 | 0.80 | 0.028              | 0.030 | 0.031 |

| A1       | 0.00           | 0.02 | 0.05 | 0.000              | 0.001 | 0.002 |

| b        | 0.15           | 0.20 | 0.25 | 0.006              | 0.008 | 0.010 |

| D<br>BSC | 1.9            | 2.00 | 2.1  | 0.075              | 0.079 | 0.083 |

| E<br>BSC | 1.9            | 2.00 | 2.1  | 0.075              | 0.079 | 0.083 |

| е        |                | 0.50 |      |                    | 0.020 |       |

| L        | 0.45           | 0.55 | 0.65 | 0.018              | 0.022 | 0.026 |

Package footprint STM6513

# 9 Package footprint

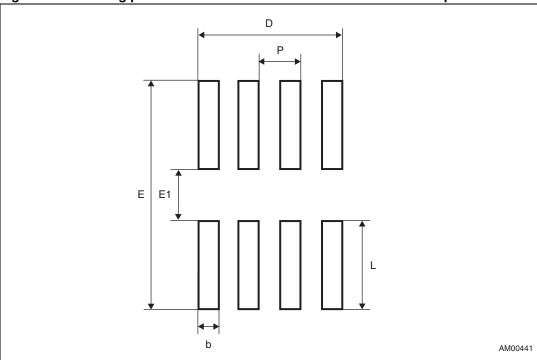

Figure 14. Landing pattern - TDFN - 8-lead 2 x 2 mm without thermal pad

Table 8. Parameter for landing pattern - TDFN - 8-lead 2 x 2 mm package

| Parameter | Description                   | Dimension (mm) |      |      |  |

|-----------|-------------------------------|----------------|------|------|--|

|           | Description                   | Min.           | Nom. | Max. |  |

| L         | Contact length                | 1.05           | _    | 1.15 |  |

| b         | Contact width                 | 0.25           | _    | 0.30 |  |

| E         | Max. land pattern Y-direction | _              | 2.85 | _    |  |

| E1        | Contact gap spacing           | _              | 0.65 | _    |  |

| D         | Max. land pattern X-direction | _              | 1.75 | _    |  |

| Р         | Contact pitch                 | _              | 0.5  | _    |  |

# 10 Tape and reel information

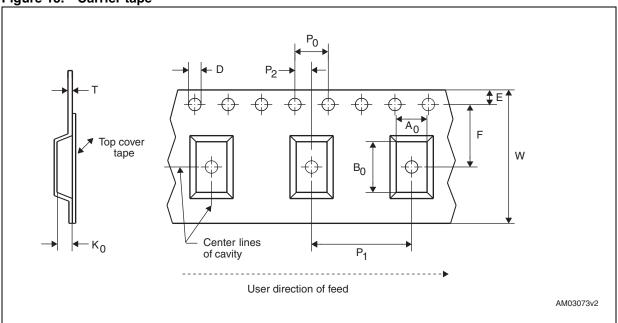

Figure 15. Carrier tape

Table 9. Carrier tape dimensions

| Package | w                      | D                       | Ш             | P <sub>0</sub> | P <sub>2</sub> | F             | <b>A</b> <sub>0</sub> | B <sub>0</sub> | K <sub>0</sub> | P <sub>1</sub> | Т              | Unit | Bulk<br>qty. |

|---------|------------------------|-------------------------|---------------|----------------|----------------|---------------|-----------------------|----------------|----------------|----------------|----------------|------|--------------|

| TDFN8   | 8.00<br>+0.30<br>-0.10 | 1.50<br>+0.10/<br>-0.00 | 1.75<br>±0.10 | 4.00<br>±0.10  | 2.00<br>±0.10  | 3.50<br>±0.05 | 2.30<br>±0.05         | 2.30<br>±0.05  | 1.00<br>±0.05  | 4.00<br>±0.10  | 0.250<br>±0.05 | mm   | 3000         |

Figure 16. Reel dimensions 40 mm min. acces hole at slot location Α Full radius Tape slot in core for tape start 25 mm min width G measured at hub

Table 10. **Reel dimensions**

| Tape sizes | A max.         | B min. | С             | D min. | N min. | G         | T max. |

|------------|----------------|--------|---------------|--------|--------|-----------|--------|

| 8 mm       | 180 (7 inches) | 1.50   | 13.0 +/- 0.20 | 20.20  | 60     | 8.4 +2/-0 | 14.40  |

AM00443

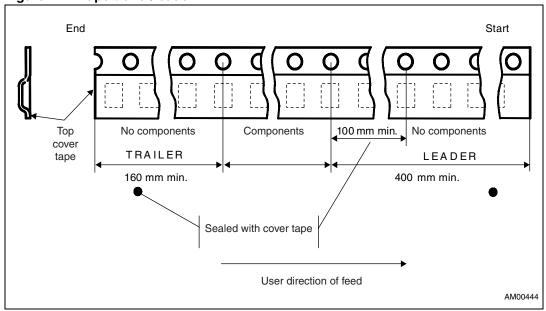

Figure 17. Tape trailer/leader

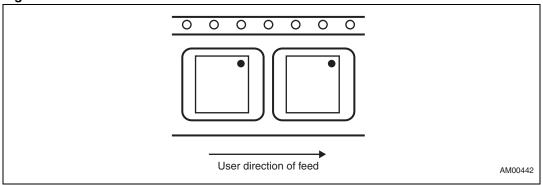

Figure 18. Pin 1 orientation

Note: 1 Drawings are not to scale.

2 All dimensions are in mm, unless otherwise noted.

57

Doc ID 16490 Rev 2

Part numbering STM6513

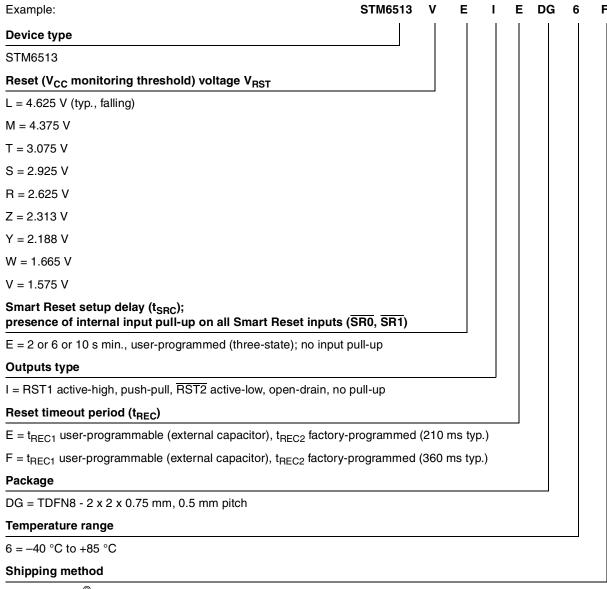

## 11 Part numbering

Table 11. Ordering information scheme

F = ECOPACK® package, tape and reel

For other options, voltage threshold values etc. or for more information on any aspect of this device, please contact the ST sales office nearest you.

5

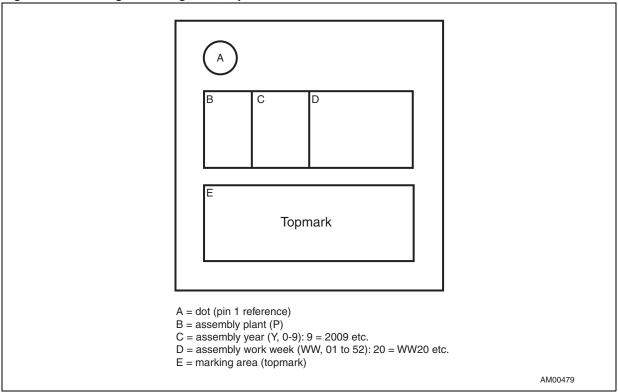

## 12 Package marking information

Table 12. Package marking

| Full part number | t <sub>SRC</sub><br>delay<br>control | Smart<br>Reset<br>inputs type | V <sub>RST</sub> | RST1<br>output<br>type | t <sub>REC1</sub> programming | RST2 output<br>type | t <sub>REC2</sub><br>option | Topmark |

|------------------|--------------------------------------|-------------------------------|------------------|------------------------|-------------------------------|---------------------|-----------------------------|---------|

| STM6513VEIEDG6F  | TSR                                  | AL, NPU                       | V                | AH, PP                 | C <sub>tREC</sub>             | AL, OD, NPU         | Е                           | 9AH     |

| STM6513SEIEDG6F  | TSR                                  | AL, NPU                       | S                | AH, PP                 | C <sub>tREC</sub>             | AL, OD, NPU         | Е                           | 9SH     |

| STM6513REIEDG6F  | TSR                                  | AL, NPU                       | R                | AH, PP                 | C <sub>tREC</sub>             | AL, OD, NPU         | Е                           | 9RH     |

Note: AL = active-low, AH = active-high; PP = push-pull, OD = open-drain, PU = internal pull-up resistor, NPU = no internal pull-up resistor.

Figure 19. Package marking area, top view

5/

Revision history STM6513

# 13 Revision history

Table 13. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 22-Oct-2009 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 21-Jun-2010 | 2        | Updated title, <i>Features</i> , <i>Applications</i> , replaced "smart reset" by "Smart Reset™" and "Smart Reset", updated <i>Section 1</i> , <i>Table 1</i> , <i>Section 3</i> , <i>Table 2</i> , <i>Figure 3</i> , <i>Figure 5</i> , <i>Figure 6</i> , <i>Table 3</i> , <i>Table 5</i> to <i>Table 8</i> , <i>Table 11</i> and <i>Table 12</i> . |  |  |  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16490 Rev 2

29/29