October 1987 Revised January 2004

# MM74C925 • MM74C926 4-Digit Counters with Multiplexed 7-Segment Output Drivers

# **General Description**

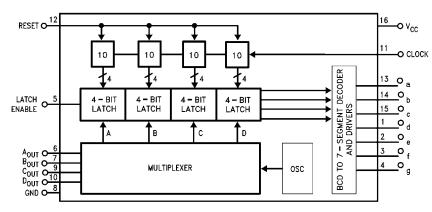

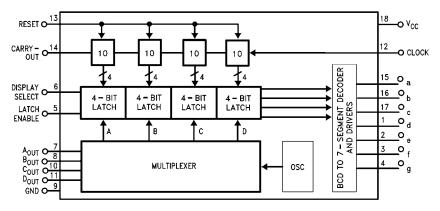

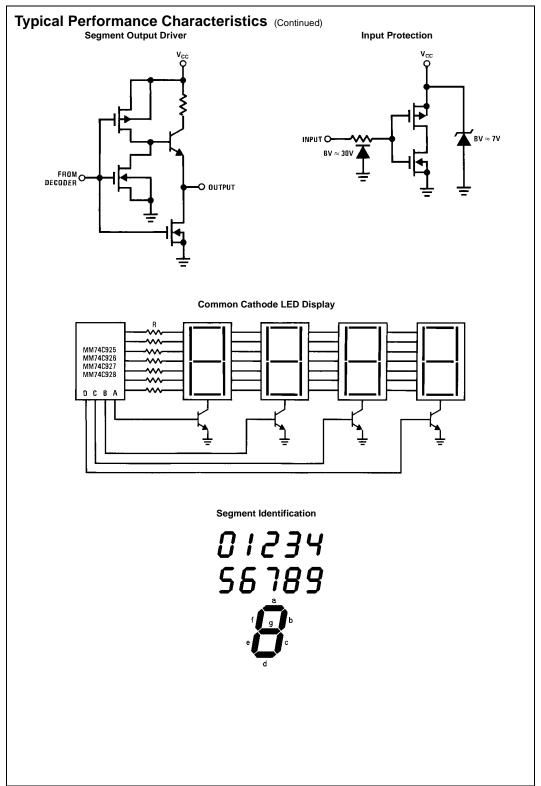

The MM74C925 and MM74C926 CMOS counters consist of a 4-digit counter, an internal output latch, NPN output sourcing drivers for a 7-segment display, and an internal multiplexing circuitry with four multiplexing outputs. The multiplexing circuit has its own free-running oscillator, and requires no external clock. The counters advance on negative edge of clock. A HIGH signal on the Reset input will reset the counter to zero, and reset the carry-out LOW. A LOW signal on the Latch Enable input will latch the number in the counters into the internal output latches. A HIGH signal on Display Select input will select the number in the counter to be displayed; a LOW level signal on the Display Select will select the number in the output latch to be displayed.

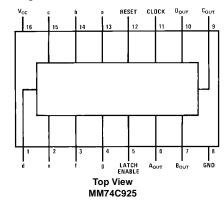

The MM74C925 is a 4-decade counter and has Latch Enable, Clock and Reset inputs.

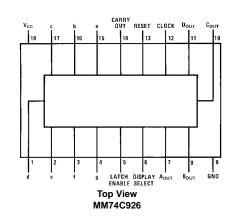

The MM74C926 is like the MM74C925 except that it has a display select and a carry-out used for cascading counters. The carry-out signal goes HIGH at 6000, goes back LOW at 0000.

#### **Features**

■ Wide supply voltage range: 3V to 6V

■ Guaranteed noise margin: 1V

$\blacksquare$  High noise immunity: 0.45  $V_{CC}$  (typ.)

■ High segment sourcing current: 40 mA

@ V<sub>CC</sub> - 1.6V, V<sub>CC</sub> = 5V

■ Internal multiplexing circuitry

#### **Design Considerations**

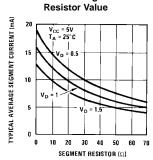

Segment resistors are desirable to minimize power dissipation and chip heating. The DS75492 serves as a good digit driver when it is desired to drive bright displays. When using this driver with a 5V supply at room temperature, the display can be driven without segment resistors to full illumination. The user must use caution in this mode however, to prevent overheating of the device by using too high a supply voltage or by operating at high ambient temperatures.

The input protection circuitry consists of a series resistor, and a diode to ground. Thus input signals exceeding  $V_{\rm CC}$  will not be clamped. This input signal should not be allowed to exceed 15V.

## **Ordering Code:**

| Order Number | Package Number | Package Description                                                    |  |  |  |

|--------------|----------------|------------------------------------------------------------------------|--|--|--|

| MM74C925N    | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |  |  |  |

| MM74C926N    | N18B           | 18-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide |  |  |  |

## **Connection Diagrams**

Pin Assignments for DIP

© 2004 Fairchild Semiconductor Corporation

DS005919

www.fairchildsemi.com

# **Functional Description**

Reset — Asynchronous, active high

Display Select — High, displays output of counter

Low, displays output of latch

Latch Enable — High, flow through condition

Low, latch condition

Clock —Negative edge sensitive

Segment Output — Current sourcing with 40 mA @V $_{OUT}$  =  $V_{CC} - 1.6V$  (typ.) Also, sink capability = 2

LTTL loads

Digit Output — Current sourcing with 1 mA  $@V_{OUT} = 1.75V$ . Also, sink capability = 2 LTTL loads

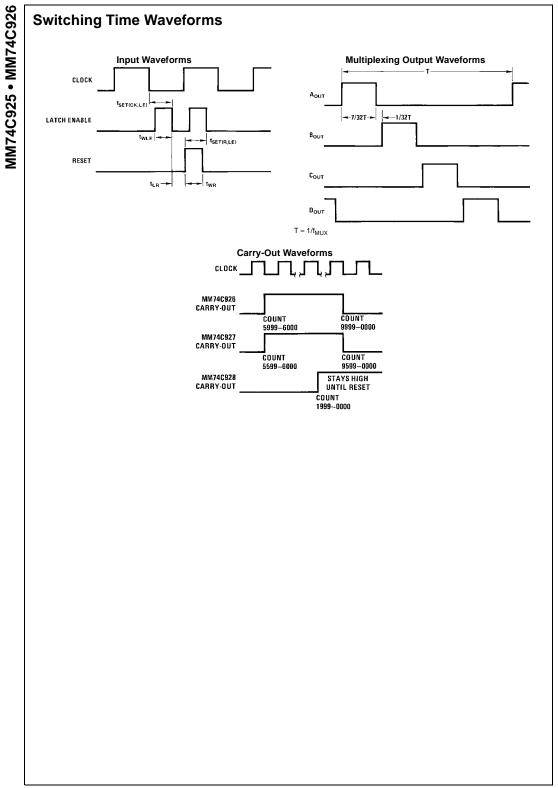

Carry-Out — 2 LTTL loads. See carry-out waveforms.

# **Logic Diagrams**

#### MM74C925

#### MM74C926

# **Absolute Maximum Ratings**(Note 1)

$\label{eq:continuous} \begin{array}{ll} \mbox{Voltage at Any Output Pin} & \mbox{GND} - 0.3 \mbox{V to V}_{CC} + 0.3 \mbox{V} \\ \mbox{Voltage at Any Input Pin} & \mbox{GND} - 0.3 \mbox{V to } +15 \mbox{V} \\ \end{array}$

Operating Temperature

$\begin{tabular}{lll} Range (T_A) & -40^{\circ}C \ to \ +85^{\circ}C \\ Storage Temperature Range & -65^{\circ}C \ to \ +150^{\circ}C \\ \end{tabular}$

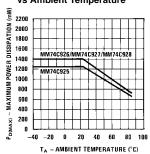

Power Dissipation ( $P_D$ ) Refer to  $P_{D(MAX)}$  vs  $T_A$  Graph Operating  $V_{CC}$  Range 3V to 6V

Operating  $V_{CC}$  Range 3V to 6V  $V_{CC}$  6.5V

V<sub>CC</sub> 6.5 Lead Temperature

(Soldering, 10 seconds) 260°C

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The Electrical Characteristics table provides conditions for actual device operation.

## **DC Electrical Characteristics**

Min/Max limits apply at  $-40^{\circ}C \leq t_{j} \!\! \leq +85^{\circ}C,$  unless otherwise noted

| Symbol              | Parameter                                                    | Conditions                                                          | Min                   | Тур                   | Max  | Units |

|---------------------|--------------------------------------------------------------|---------------------------------------------------------------------|-----------------------|-----------------------|------|-------|

| CMOS TO             | смоѕ                                                         |                                                                     |                       |                       |      | l     |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage                                    | V <sub>CC</sub> = 5V                                                | 3.5                   |                       |      | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage                                    | V <sub>CC</sub> = 5V                                                |                       |                       | 1.5  | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage $V_{CC} = 5V$ , $I_O = -10 \mu A$ |                                                                     |                       |                       |      |       |

|                     | (Carry-Out and Digit Output Only)                            |                                                                     | 4.5                   |                       |      | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                                   | $V_{CC} = 5V, I_{O} = 10 \mu A$                                     |                       |                       | 0.5  | V     |

| I <sub>IN(1)</sub>  | Logical "1" Input Current                                    | $V_{CC} = 5V, V_{IN} = 15V$                                         |                       | 0.005                 | 1    | μΑ    |

| I <sub>IN(0)</sub>  | Logical "0" Input Current                                    | $V_{CC} = 5V, V_{IN} = 0V$                                          | -1                    | -0.005                |      | μΑ    |

| I <sub>CC</sub>     | Supply Current                                               | V <sub>CC</sub> = 5V, Outputs Open Circuit,                         |                       | 20                    | 1000 | μΑ    |

|                     |                                                              | V <sub>IN</sub> = 0V or 5V                                          |                       |                       |      |       |

| CMOS/LPT            | TL INTERFACE                                                 |                                                                     | •                     |                       |      |       |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage                                    | V <sub>CC</sub> = 4.75V                                             | V <sub>CC</sub> - 2   |                       |      | V     |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage                                    | V <sub>CC</sub> = 4.75V                                             |                       |                       | 0.8  | V     |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                                   | Voltage $V_{CC} = 4.75V$ ,                                          |                       |                       |      |       |

|                     | (Carry-Out and Digit Output Only)                            | $I_O = -360 \mu A$                                                  | 2.4                   |                       |      | V     |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                                   | $V_{CC} = 4.75V$ , $I_{O} = 360 \mu A$                              |                       |                       | 0.4  | V     |

| OUTPUT D            | RIVE                                                         |                                                                     | U                     |                       |      |       |

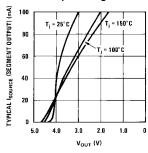

| V <sub>OUT</sub>    | Output Voltage                                               | $I_{OUT} = -65 \text{ mA}, V_{CC} = 5V, T_j = 25^{\circ}\text{C}$   | V <sub>CC</sub> - 2   | V <sub>CC</sub> - 1.3 |      | V     |

|                     | (Segment Sourcing Output)                                    | $I_{OUT} = -40 \text{ mA}, V_{CC} = 5V$ $T_j = 100^{\circ}\text{C}$ | V <sub>CC</sub> - 1.6 | V <sub>CC</sub> - 1.2 |      | V     |

|                     |                                                              | T <sub>j</sub> = 150°C                                              | V <sub>CC</sub> - 2   | V <sub>CC</sub> - 1.4 |      | V     |

| R <sub>ON</sub>     | Output Resistance                                            | $I_{OUT} = -65 \text{ mA}, V_{CC} = 5V, T_j = 25^{\circ}\text{C}$   |                       | 20                    | 32   | Ω     |

|                     | (Segment Sourcing Output)                                    | $I_{OUT} = -40 \text{ mA}, V_{CC} = 5V$ $T_j = 100^{\circ}\text{C}$ |                       | 30                    | 40   | Ω     |

|                     |                                                              | T <sub>j</sub> = 150°C                                              |                       | 35                    | 50   | Ω     |

|                     | Output Resistance (Segment Output)                           |                                                                     |                       | 0.6                   | 0.8  | %/°C  |

|                     | Temperature Coefficient                                      |                                                                     |                       |                       |      |       |

| I <sub>SOURCE</sub> | Output Source Current                                        | rrent $V_{CC} = 4.75V, V_{OUT} = 1.75V, T_j = 150^{\circ}C$         |                       | -2                    |      | mA    |

|                     | (Digit Output)                                               |                                                                     |                       |                       |      |       |

| I <sub>SOURCE</sub> | Output Source Current                                        | $V_{CC} = 5V, V_{OUT} = 0V, T_j = 25^{\circ}C$                      | -1.75                 | -3.3                  |      | mA    |

|                     | (Carry-Out)                                                  |                                                                     |                       |                       |      |       |

| I <sub>SINK</sub>   | Output Sink Current                                          | $V_{CC} = 5V, V_{OUT} = V_{CC}, T_j = 25^{\circ}C$                  | 1.75                  | 3.6                   |      | mA    |

|                     | (All Outputs)                                                | ·                                                                   |                       |                       |      |       |

| $\theta_{jA}$       | Thermal Resistance MM74C925: (Note 2)                        |                                                                     |                       | 75                    | 100  | °C/W  |

| •                   |                                                              | MM74C926                                                            |                       | 70                    | 90   | °C/W  |

Note 2:  $\theta_{jA}$  measured in free-air with device soldered into printed circuit board.

www.fairchildsemi.com

# **AC Electrical Characteristics** (Note 3)

$T_A=25^{\circ}C,\ C_L=50$  pF, unless otherwise noted

| Symbol                          | Parameter                         | Conditions           |                       | Min  | Тур  | Max | Units |

|---------------------------------|-----------------------------------|----------------------|-----------------------|------|------|-----|-------|

| f <sub>MAX</sub>                | Maximum Clock Frequency           | $V_{CC} = 5V$ ,      | T <sub>j</sub> = 25°C | 2    | 4    |     | MHz   |

|                                 |                                   | Square Wave Clock    |                       | 1.5  | 3    |     | MHz   |

| t <sub>r</sub> , t <sub>f</sub> | Maximum Clock Rise or Fall Time   | V <sub>CC</sub> = 5V |                       |      |      | 15  | μs    |

| t <sub>WR</sub>                 | Reset Pulse Width                 | V <sub>CC</sub> = 5V | $T_j = 25^{\circ}C$   | 250  | 100  |     | ns    |

|                                 |                                   |                      | $T_j = 100^{\circ}C$  | 320  | 125  |     | ns    |

| t <sub>WLE</sub>                | Latch Enable Pulse Width          | V <sub>CC</sub> = 5V | $T_j = 25^{\circ}C$   | 250  | 100  |     | ns    |

|                                 |                                   |                      | $T_j = 100^{\circ}C$  | 320  | 125  |     | ns    |

| t <sub>SET(CK, LE)</sub>        | Clock to Latch Enable Set-Up Time | V <sub>CC</sub> = 5V | $T_j = 25^{\circ}C$   | 2500 | 1250 |     | ns    |

|                                 |                                   |                      | $T_j = 100^{\circ}C$  | 3200 | 1600 |     | ns    |

| t <sub>LR</sub>                 | Latch Enable to Reset Wait Time   | V <sub>CC</sub> = 5V | $T_j = 25^{\circ}C$   | 0    | -100 |     | ns    |

|                                 |                                   |                      | $T_j = 100^{\circ}C$  | 0    | -100 |     | ns    |

| t <sub>SET(R, LE)</sub>         | Reset to Latch Enable Set-Up Time | V <sub>CC</sub> = 5V | $T_j = 25^{\circ}C$   | 320  | 160  |     | ns    |

|                                 |                                   |                      | $T_j = 100^{\circ}C$  | 400  | 200  |     | ns    |

| f <sub>MUX</sub>                | Multiplexing Output Frequency     | $V_{CC} = 5V$        |                       | 1000 |      |     | Hz    |

| C <sub>IN</sub>                 | Input Capacitance                 | Any Input (Note 4)   |                       | 5    |      |     | pF    |

Note 3: AC Parameters are guaranteed by DC correlated testing.

Note 4: Capacitance is guaranteed by periodic testing.

# **Typical Performance Characteristics**

Note:  $V_D = Voltage$  across digit driver

# Maximum Power Dissipation vs Ambient Temperature

Typical Average Segment Current vs Segment

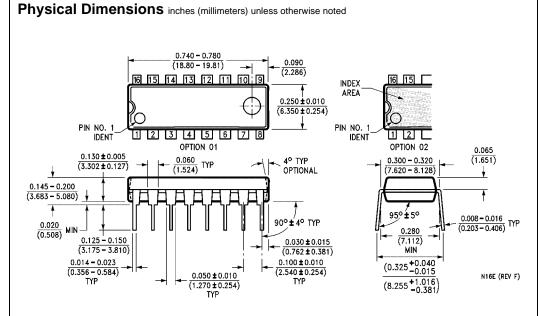

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

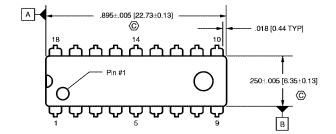

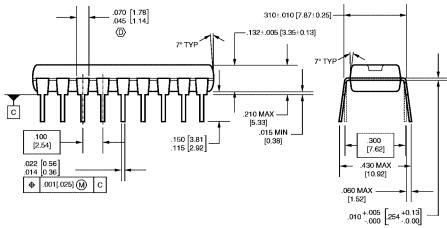

# Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

- NOTES:

A. CONFORMS TO JEDEC REGISTRATION MS-001, VARIATIONS AC, DATED 6/1993.

B. CONTROLLING DIMENSIONS ARE IN INCHES

- REFERENCE DIMENSIONS ARE IN MILLIMETERS.

© DOES NOT INCLUDE MOLD FLASH OR PROTRUSIONS MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED

- .010 INCHES OR 0.25MM.

(D) DOES NOT INCLUDE DAMBAR PROTRUSIONS. DAMBAR PROTRUSIONS SHALL NOT EXCEED .010 INCHES OR 0.25MM.

- E. DIMENSIONING AND TOLERANCING PER ASMEY14.5M-1994.

N18BrevA

#### 18-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N18B

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

www.fairchildsemi.com