# **ON Semiconductor**

## Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and Onsemi. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# **LUPA3000: 3 MegaPixel High Speed CMOS Sensor**

#### **Features**

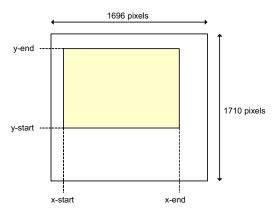

- 1696 x 1710 Active Pixels

- 8 µm x 8 µm Square Pixels

- 1.2 inch Optical Format

- Monochrome or Color Digital Output

- 485 Frames per Second (fps) Frame Rate

- 64 On-Chip 8-Bit ADCs

- 32 Low-Voltage Digital Signaling (LVDS) Serial Outputs

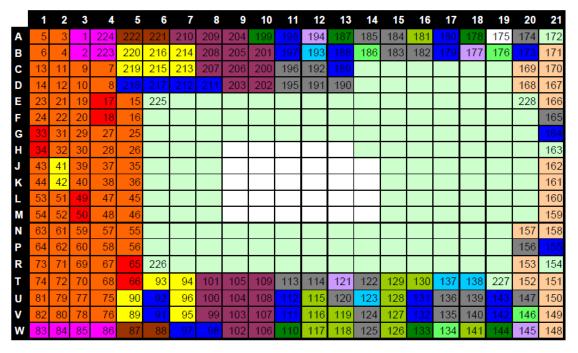

- Random Programmable Region of Interest (ROI) Readout

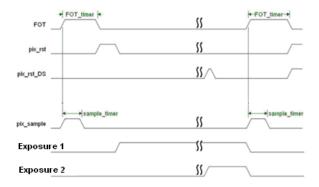

- Pipelined and Triggered Global Shutter

- Serial Peripheral Interface (SPI)

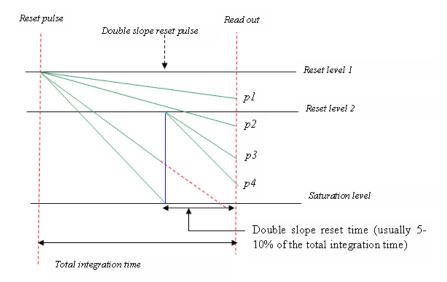

- Dynamic Range Extended by Double Slope

- Limited Supplies: Nominal 2.5 V and 3.3 V

- 0°C to 60°C Operational Temperature Range

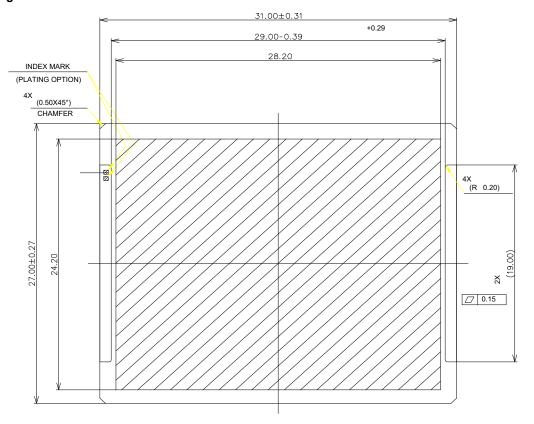

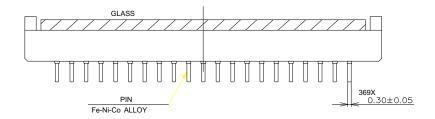

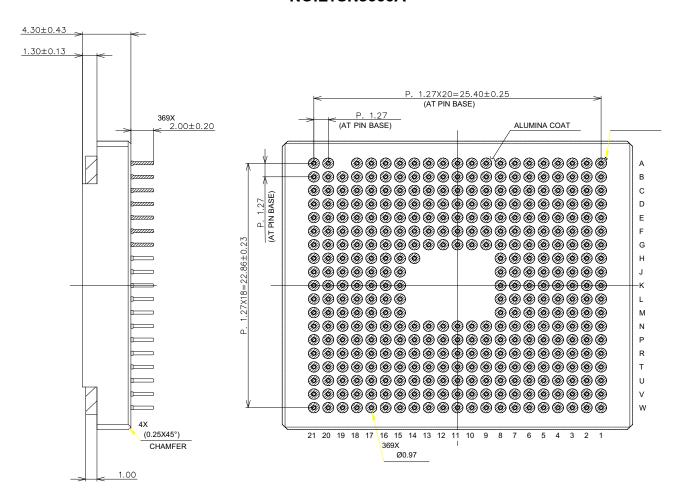

- 369-Pin μPGA Package

- 1.1 W Power Dissipation

- These Devices are Pb-Free and are RoHS Compliant

#### **Applications**

- High Speed Machine Vision

- Holographic Data Storage

- Motion Analysis

- Intelligent Traffic System

- Medical Imaging

- Industrial Imaging

# ON

#### ON Semiconductor®

www.onsemi.com

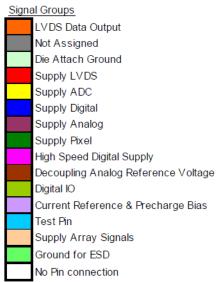

Figure 1. LUPA3000 Package Photo

#### Description

The LUPA3000 is a high-speed CMOS image sensor with an image resolution of 1696 by 1710 pixels. The pixels are  $8 \mu m \times 8 \mu m$  in size and consist of high sensitivity 6T pipelined global shutter capability where integration during readout is possible. The LUPA3000 delivers 8-bit color or monochrome digital images with a 3 Megapixels resolution at 485 fps that makes this product ideal for high-speed vision machine, intelligent traffic system, and holographic data storage. The LUPA3000 captures complex high-speed events for traditional machine vision applications and various high-speed imaging applications.

The LUPA3000 production package is housed in a 369-pin ceramic µPGA package and is available in a monochrome version or Bayer (RGB) patterned color filter array with micro lens. Contact your local ON Semiconductor representative for more information.

#### **ORDERING INFORMATION**

| Marketing Part Number | Mono / Color                | Package      |

|-----------------------|-----------------------------|--------------|

| NOIL1SN3000A-GDC      | Mono micro lens with glass  | 369-pin μPGA |

| NOIL1SE3000A-GDC      | Color micro lens with glass |              |

NOTE: Refer to Ordering Code Definition on page 54 for more information.

#### **CONTENTS**

| Features             | 1 | Operating Modes                      | 32         |

|----------------------|---|--------------------------------------|------------|

| Applications         | 1 | Image Sensor Timing and Readout      | 34         |

| Description          | 1 | Additional Features                  | 41         |

| Ordering Information | 1 | Package Information                  | <b>4</b> 4 |

| <b>Contents</b>      | 2 | Specifications and Useful References | <b>5</b> 4 |

| Specifications       | 3 | Acronyms                             | 55         |

| Overview             | 6 | Glossary                             | 56         |

| Sensor Architecture  | 8 |                                      |            |

#### **SPECIFICATIONS**

#### **Key Specifications**

#### **Table 1. GENERAL SPECIFICATIONS**

| Parameter              | Specifications                                                                                             |

|------------------------|------------------------------------------------------------------------------------------------------------|

| Active pixels          | 1696 (H) x 1710 (V)                                                                                        |

| Pixel size             | 8 μm x 8 μm                                                                                                |

| Pixel type             | 6T pixel architecture                                                                                      |

| Data rate              | 412 Mbps (32 serial LVDS outputs)                                                                          |

| Shutter type           | Pipelined and Triggered Global<br>Shutter                                                                  |

| Frame rate             | 485 fps at full frame                                                                                      |

| Master clock           | 206 MHz                                                                                                    |

| Windowing (ROI)        | Randomly programmable ROI read out. Implemented as scanning of lines or columns from an uploaded position. |

| ADC resolution         | 8-bit, on-chip                                                                                             |

| Extended dynamic range | Double slope (up to 80 dB optical dynamic range)                                                           |

#### Table 2. ELECTRO-OPTICAL SPECIFICATIONS

| Parameter                                     | Specifications                                       |

|-----------------------------------------------|------------------------------------------------------|

| Conversion gain                               | 39.2 μV/e <sup>-</sup>                               |

| Full well charge                              | 27000 e <sup>-</sup>                                 |

| Responsivity                                  | 1270 V.m <sup>2</sup> /W.s at 550 nm with micro lens |

| Parasitic light sensitivity                   | < 1/5000                                             |

| Dark noise                                    | 21 e <sup>-</sup>                                    |

| Quantum efficiency (QE)<br>x Fill-factor (FF) | 37% at 680 nm with micro lens                        |

| Fixed pattern noise (FPN)                     | 2% of Vsweep <sub>RMS</sub>                          |

| Photo response non-uniformity (PRNU)          | 2.2% of Vsignal                                      |

| Dark signal                                   | 277 mV/s at 25°C                                     |

| Power dissipation                             | 1.1 W at 485 fps                                     |

#### **Table 3. RECOMMENDED OPERATING RATINGS**

#### Table 4. ABSOLUTE MAXIMUM RATINGS (Note 1)

| Symbol                        | Description                       | Min  | Max                   | Units |

|-------------------------------|-----------------------------------|------|-----------------------|-------|

| ABS (2.5 V supply group)      | ABS rating for 2.5 V supply group | -0.5 | 3.0                   | ٧     |

| ABS (3.3 V supply group)      | ABS rating for 3.3 V supply group | -0.5 | 4.3                   | V     |

| T <sub>S</sub>                | ABS Storage temperature range     | -40  | +150                  | °C    |

| (Notes 3 and 4)               | ABS Storage humidity range        | 5    | 90                    | %RH   |

| Electrostatic Discharge (ESD) | Human Body Model (HBM)            | 2000 |                       | V     |

| (Note 3)                      | Charged Device Model (CDM)        | 500  |                       | V     |

| LU                            | Latch-up                          |      | not rated for<br>n-up | mA    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Absolute maximum ratings are limits beyond which damage may occur.

- Operating ratings are conditions in which operation of the device is intended to be functional.

ON Semiconductor recommends that customers become familiar with, and follow the procedures in JEDEC Standard JESD625–A. Refer to Application Note AN52561. Long term exposure toward the maximum storage temperature will accelerate color filter degradation.

- 4. Caution needs to be taken to avoid dried stains on the underside of the glass due to condensation. The glass lid glue is permeable and can absorb moisture if the sensor is placed in a high % RH environment.

#### **Electrical Specifications**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

Table 5. POWER SUPPLY RATINGS (Notes 1, 2 and 3)

$\textbf{Limits in bold apply for } \textbf{T}_{\textbf{A}} = \textbf{T}_{\textbf{MIN}} \textbf{ to } \textbf{T}_{\textbf{MAX}}, \text{ all other limits } \textbf{T}_{\textbf{A}} = +25^{\circ}\text{C}. \text{ System speed} = 50 \text{ MHz}, \text{ Sensor clock} = 200 \text{ MHz}$

| Power Supply            | Parameter                                                                                                                                                                                                                                       | Condition                        | Min                                                      | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Max           | Units                                                                             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------|

| Analog Supply           | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Dynamic Current                                                                                                                                                                                                                                 | Clock enabled, lux = 0           |                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | mA                                                                                |

|                         | Peak Current                                                                                                                                                                                                                                    | Row overhead time (ROT)          |                                                          | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

| Digital Supply          | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Dynamic Current                                                                                                                                                                                                                                 | Clock enabled, lux = 0           |                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | mA                                                                                |

|                         | Peak Current                                                                                                                                                                                                                                    | Frame overhead time (FOT)        |                                                          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | mA                                                                                |

| Digital Supply          | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

| high speed              | Dynamic Current                                                                                                                                                                                                                                 | Clock enabled, lux = 0           |                                                          | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

|                         | Peak Current                                                                                                                                                                                                                                    | FOT                              |                                                          | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | mA                                                                                |

| Pixel Supply            | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Peak Current during FOT                                                                                                                                                                                                                         | Transient duration = 2 μs        |                                                          | 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

|                         | Peak Current during ROT                                                                                                                                                                                                                         | Transient duration = 0.5 μs      |                                                          | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

| LVDS Supply             | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Dynamic Current                                                                                                                                                                                                                                 | Clock enabled, lux = 0           |                                                          | 170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

|                         | Peak Current                                                                                                                                                                                                                                    | ROT                              |                                                          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | mA                                                                                |

| ADC Supply              | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Dynamic Current                                                                                                                                                                                                                                 | Clock enabled, lux = 0           |                                                          | 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

|                         | Peak Current                                                                                                                                                                                                                                    | Clock enabled, lux = 0           |                                                          | 275                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

| Reset Supply            | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

|                         | Peak current during FOT                                                                                                                                                                                                                         | Transient duration: 200 ns       |                                                          | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | mA                                                                                |

| Reset dual slope supply | Operating Voltage                                                                                                                                                                                                                               |                                  | 1.8                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3.5           | V                                                                                 |

| Memory Element          | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

| low level supply        | Peak current during FOT                                                                                                                                                                                                                         | Clock enabled, bright            |                                                          | 180                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               | mA                                                                                |

| Memory Element          | Operating Voltage                                                                                                                                                                                                                               |                                  | -5%                                                      | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | +5%           | V                                                                                 |

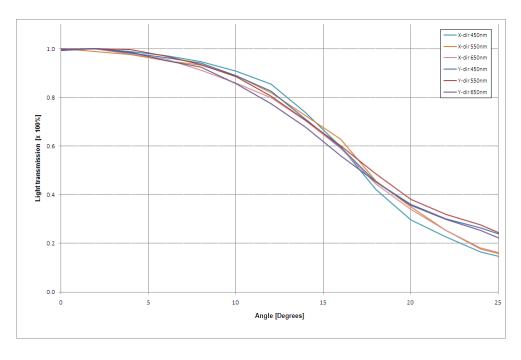

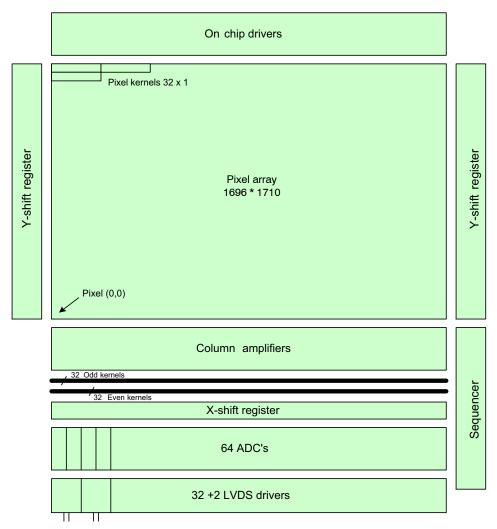

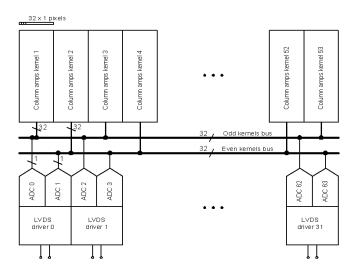

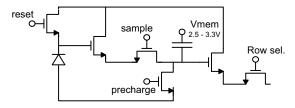

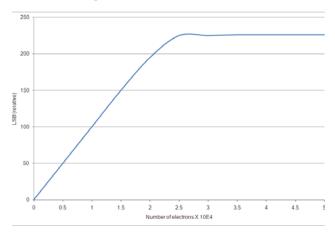

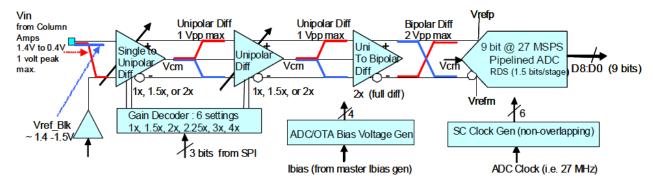

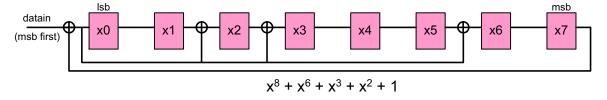

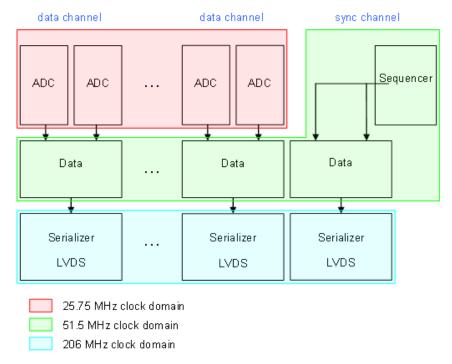

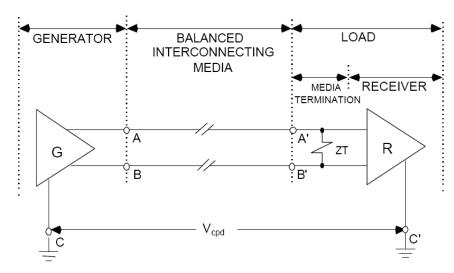

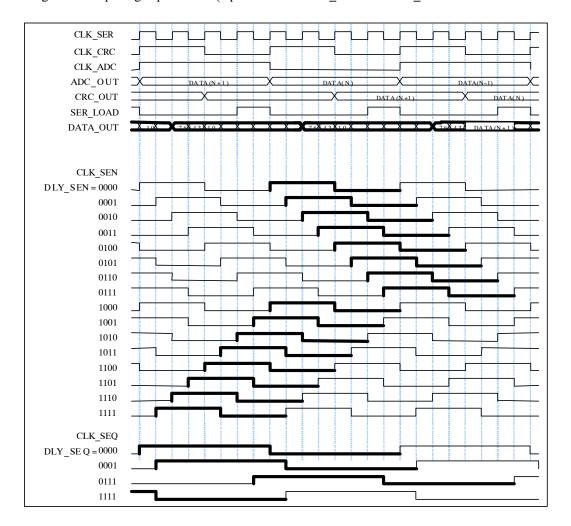

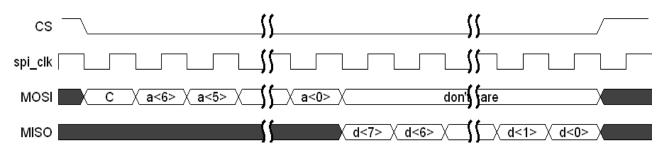

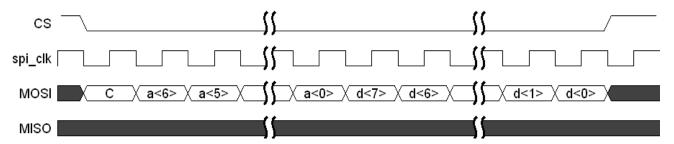

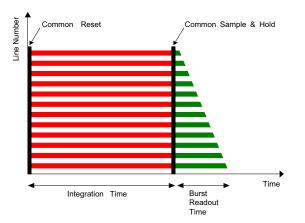

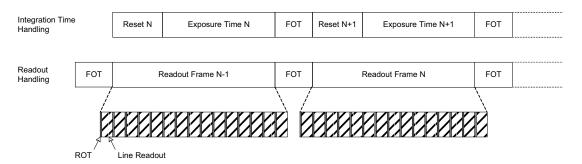

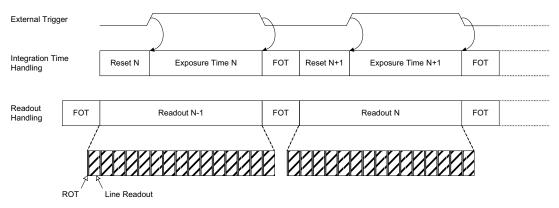

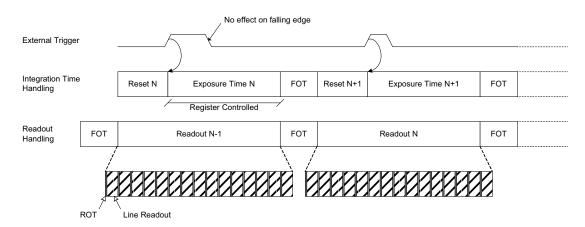

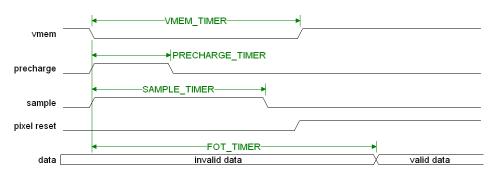

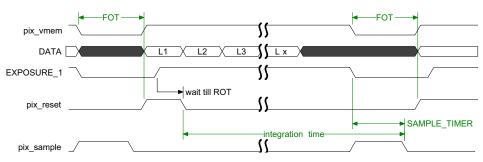

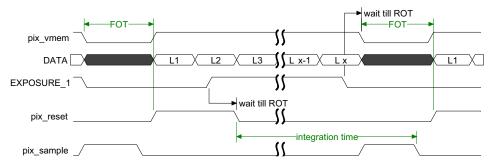

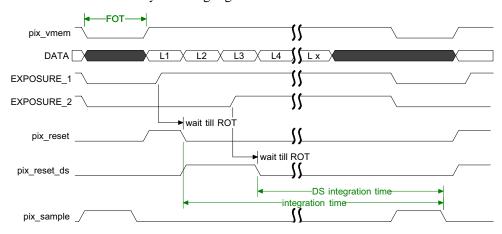

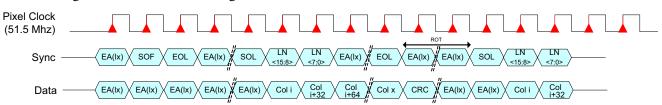

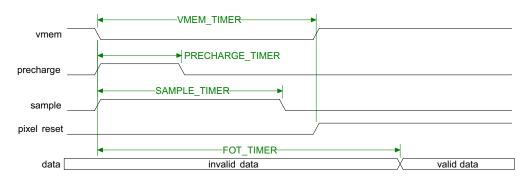

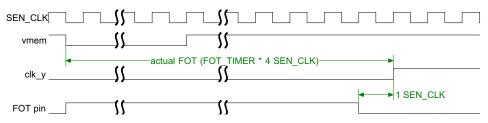

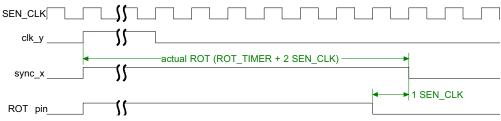

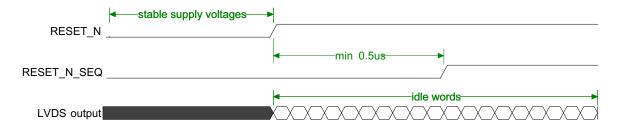

| high level supply       | Peak current during FOT                                                                                                                                                                                                                         |                                  |                                                          | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | mA                                                                                |