# Advanced Pulse Frequency Modulation (PFM) Controller for Half-Bridge Resonant Converters

## **FAN7631**

#### Description

The FAN7631 is a pulse-frequency modulation controller for high-efficiency half-bridge resonant converters that includes a high-side gate drive circuit, an accurate current-controlled oscillator, and various protection functions. The FAN7631 features include variable dead time, operating frequency up to 600 kHz, protections such as LUVLO, and a selectable latch or A/R protection using the LS pin for user convenience.

The Zero-Voltage-Switching (ZVS) technique reduces the switching losses and improves the efficiency significantly. ZVS also reduces the switching noise noticeably, which allows a small Electromagnetic Interference (EMI) filter.

Offering everything necessary to build a reliable and robust resonant converter, the FAN7631 simplifies designs and improves productivity and performance. The FAN7631 can be applied to resonant converter topologies such as series resonant, parallel resonant, and LLC resonant converters.

#### **Features**

- Variable Frequency Control with 50% Duty Cycle for Half-Bridge Resonant Converter Topologies

- High Efficiency with Zero-Voltage-Switching (ZVS)

- Up to 600 kHz Operating Frequency

- Built-in High-Side Gate Driver

- High Gate-Driving Current: +500 mA/-1000 mA

- Programmable Dead Time with a Resistor

- Pulse Skipping and Burst Operation for Frequency Limit (Programmable) at Light–Load Condition

- Simple Remote On/Off Control with Latch or Auto-Restart (A/R) Using FI or LS Pin

- Protection Functions: Over-Voltage Protection (OVP), Overload Protection (OLP), Over-Current Protection (OCP), Abnormal Over-Current Protection (AOCP), Internal Thermal Shutdown (TSD), and High Precise Line Under-Voltage Lockout (LUVLO)

- Level-Change OCP Function During Startup

#### **Applications**

- PDP and LCD Tvs

- Desktop PCs and Servers

- Video Game Consoles

- Adapters

- Telecom Power Supplies

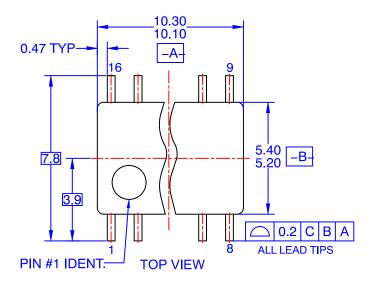

SOP16 CASE 565BF

#### MARKING DIAGRAM

FAN7631 = Device Code

\$Y = Logo

&Z = Assembly Plant Code &2 = 2-Digit Date Code

&K = 2-Digits Lot Run Traceability Code

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 17 of this data sheet.

#### **Related Resources**

<u>AN4151 — Half-Bridge LLC Resonant</u> <u>Converter Design Using FSFR-Series Power</u> <u>Switch</u>

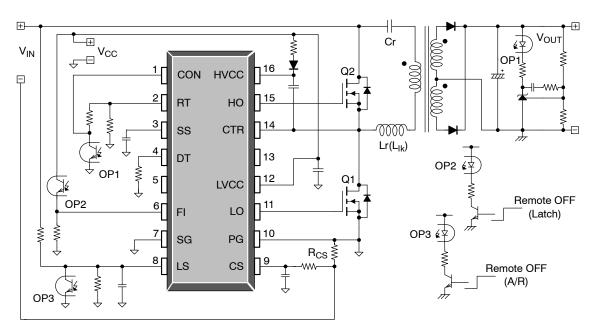

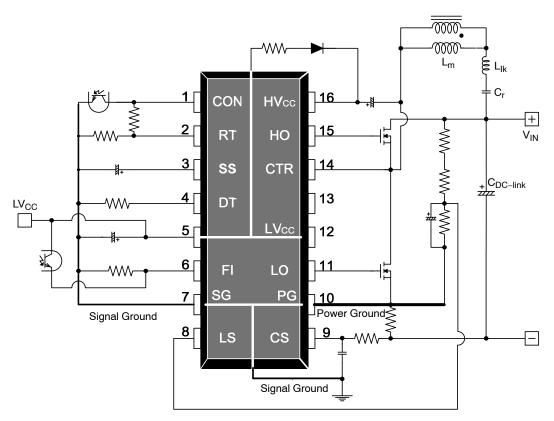

#### **APPLICATION CIRCUIT DIAGRAM**

Figure 1. Typical Application Circuit (Resonant Half-Bridge Converter)

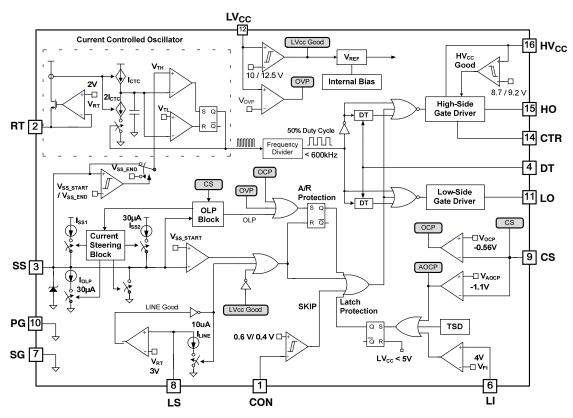

## **BLOCK DIAGRAM**

Figure 2. Internal Block Diagram

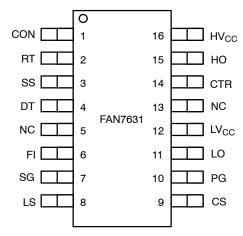

## **PIN CONFIGURATION**

Figure 3. Package Pin Assignments (SOP16)

#### **PIN DEFINITIONS**

| Pin No. | Name                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | CON                                                                                                                                                                                                                   | This pin is used to enable / disable the gate drive outputs for pulse–skipping operation. When the voltage of this pin is above 0.6 V, the gate drive outputs are enabled. When the voltage of this pin drops below 0.4 V, gate drive signals for both MOSFETs are disabled. |  |  |

| 2       | RT                                                                                                                                                                                                                    | This pin programs the switching frequency. Typically, an opto-coupler is connected to this pin to control the switching frequency for the output voltage regulation.                                                                                                         |  |  |

| 3       | SS This pin is used to program the soft–start time and overload protection delay. It also programs the rewards when the converter auto recovers from the protection states. Typically, a small capacitor is connected |                                                                                                                                                                                                                                                                              |  |  |

| 4       | DT                                                                                                                                                                                                                    | This pin is to adjust the dead time using an external resistor.                                                                                                                                                                                                              |  |  |

| 5       | NC                                                                                                                                                                                                                    | No connection                                                                                                                                                                                                                                                                |  |  |

| 6       | FI                                                                                                                                                                                                                    | User protection function / fault input. This pin can be used as a latch protection, which is operated when a voltage applied to this pin is higher than $4V_{DC}$ .                                                                                                          |  |  |

| 7       | SG                                                                                                                                                                                                                    | This pin is the ground of the control part.                                                                                                                                                                                                                                  |  |  |

| 8       | LS                                                                                                                                                                                                                    | This pin senses the line voltage for line under-voltage lockout (LUVLO).                                                                                                                                                                                                     |  |  |

| 9       | CS                                                                                                                                                                                                                    | This pin senses the current flowing through the main MOSFET. Typically, negative voltage is applied on this pin.                                                                                                                                                             |  |  |

| 10      | PG                                                                                                                                                                                                                    | This pin is the power ground. This pin typically connects to the source of the low-side MOSFET.                                                                                                                                                                              |  |  |

| 11      | LO                                                                                                                                                                                                                    | This pin is used for the low-side gate-driving signal.                                                                                                                                                                                                                       |  |  |

| 12      | LV <sub>CC</sub>                                                                                                                                                                                                      | This pin is for the supply voltage of the control IC and low-side gate-driving circuit.                                                                                                                                                                                      |  |  |

| 13      | NC                                                                                                                                                                                                                    | No connection                                                                                                                                                                                                                                                                |  |  |

| 14      | CTR                                                                                                                                                                                                                   | This pin is connected to the drain of the low-side MOSFET. Typically, a transformer is connected to this pin.                                                                                                                                                                |  |  |

| 15      | НО                                                                                                                                                                                                                    | This pin is used for the high-side gate-driving signal.                                                                                                                                                                                                                      |  |  |

| 16      | HV <sub>CC</sub>                                                                                                                                                                                                      | This pin is used for the supply voltage of the high-side gate-driving circuit.                                                                                                                                                                                               |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                               | Parameter                                                                                    | Min                    | Max                               | Unit |

|--------------------------------------|----------------------------------------------------------------------------------------------|------------------------|-----------------------------------|------|

| HV <sub>CC</sub> to V <sub>CTR</sub> | High-Side V <sub>CC</sub> Pin to Center Voltage                                              | -0.3                   | 25.0                              | ٧    |

| HV <sub>CC</sub>                     | High-Side Floating Supply Voltage                                                            | -0.3                   | 625.0                             | ٧    |

| V <sub>HO</sub>                      | High-Side Gate\-Driving Voltage                                                              | V <sub>CTR</sub> - 0.3 | HV <sub>CC</sub> + 0.3            | V    |

| V <sub>CTR</sub>                     | High-Side Offset Voltage                                                                     | HV <sub>CC</sub> - 25  | HV <sub>CC</sub> + 0.3            | V    |

|                                      | Allowable Negative V <sub>CTR</sub> at 15V <sub>DC</sub> Applied HV <sub>CC</sub> to CTR Pin | -9.8                   | -7.0                              | V    |

| LV <sub>CC</sub>                     | Low-Side Supply Voltage                                                                      | -0.3                   | 25.0                              | V    |

| $V_{LO}$                             | Low-Side Gate Driving Voltage                                                                | -0.3                   | LV <sub>CC</sub>                  | V    |

| $V_{CON}$                            | Control Pin Input Voltage                                                                    | -0.3                   | LV <sub>CC</sub>                  | V    |

| V <sub>CS</sub>                      | Current Sense (CS) Pin Input Voltage                                                         | -5.0                   | 1.0                               | V    |

| V <sub>RT</sub>                      | RT Pin Input Voltage                                                                         | -0.3                   | 5.0                               | V    |

| f <sub>SW</sub>                      | Recommended Switching Frequency                                                              | 10                     | 600                               | kHz  |

| $V_{LS}$                             | LS Pin Input Voltage                                                                         | -0.3                   | LV <sub>CC</sub>                  | V    |

| V <sub>FI</sub>                      | FI Pin Input Voltage                                                                         | -0.3                   | LV <sub>CC</sub>                  | V    |

| V <sub>SS</sub>                      | SS Pin Input Voltage                                                                         | -0.3                   | Internally<br>Clamped<br>(Note 1) | V    |

| V <sub>DT</sub>                      | DT Pin Input Voltage                                                                         | -0.3                   | Internally<br>Clamped<br>(Note 1) | V    |

| dV <sub>CTR</sub> /dt                | Allowable CTR Voltage Slew Rate                                                              | -                      | 50                                | V/ns |

| $P_{D}$                              | Total Power Dissipation                                                                      | -                      | 1.24                              | W    |

| $T_J$                                | Maximum Junction Temperature (Note 2)                                                        | -                      | +150                              | °C   |

|                                      | Recommended Operating Junction Temperature (Note 2)                                          | -40                    | +130                              |      |

| T <sub>STG</sub>                     | Storage Temperature Range                                                                    | -55                    | +150                              | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. V<sub>SS</sub> and V<sub>DT</sub> are internally clamped at 5.0 V, which has a tolerance between 4.75 V and 5.25 V.

2. The maximum value of the recommended operating junction temperature is limited by thermal shutdown.

#### THERMAL CHARACTERISTICS

| Symbol            | Parameter                             | Value | Unit |

|-------------------|---------------------------------------|-------|------|

| $\theta_{\sf JA}$ | Junction-to-Ambient Thermal Impedance | 102   | °C/W |

## **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ and $LV_{CC} = 17~V$ unless otherwise specified)

| Symbol                          | Parameter                                                      | Test Condition                                                                                 | Min  | Тур  | Max  | Unit |

|---------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY SECTION                  | DN                                                             |                                                                                                |      |      |      |      |

| I <sub>LK</sub>                 | Offset Supply Leakage Current                                  | HV <sub>CC</sub> = V <sub>CTR</sub>                                                            | _    | _    | 50   | μΑ   |

| $I_QHV_{CC}$                    | Quiescent HV <sub>CC</sub> Supply Current                      | HV <sub>CC, START</sub> - 0.1 V, V <sub>CTR</sub> = 0 V                                        | -    | 50   | 120  | μΑ   |

| $I_{Q}LV_{CC}$                  | Quiescent LV <sub>CC</sub> Supply Current                      | LV <sub>CC, START</sub> - 0.1 V, V <sub>CTR</sub> = 0 V                                        | -    | 100  | 200  | μΑ   |

| I <sub>O</sub> HV <sub>CC</sub> | Operating HV <sub>CC</sub> Supply Current (RMS Value) (Note 3) | $f_{OSC}$ = 100 kHz, $C_{Load}$ = 1 nF, $V_{CON}$ > 0.6 V, $V_{CTR}$ = 0 V                     | -    | 3.0  | 4.5  | mA   |

|                                 |                                                                | $f_{OSC}$ = 300 kHz, $C_{Load}$ = 1 nF, $V_{CON}$ > 0.6 V, $V_{CTR}$ = 0 V                     | -    | 8    | 10   | mA   |

|                                 |                                                                | f <sub>OSC</sub> = 300 kHz, V <sub>CON</sub> < 0.4 V,<br>V <sub>CTR</sub> = 0 V (No Switching) | -    | 100  | 200  | μА   |

| I <sub>O</sub> LV <sub>CC</sub> | Operating LV <sub>CC</sub> Supply Current (RMS Value) (Note 3) | $f_{OSC}$ = 100 kHz, $C_{Load}$ = 1 nF, $V_{CON}$ > 0.6 V, $V_{CTR}$ = 0 V                     | -    | 5    | 7    | mA   |

|                                 |                                                                | $f_{OSC}$ = 300 kHz, $C_{Load}$ = 1 nF, $V_{CON}$ > 0.6 V, $V_{CTR}$ = 0 V                     | -    | 10   | 14   | mA   |

|                                 |                                                                | f <sub>OSC</sub> = 300 kHz, V <sub>CON</sub> < 0.4 V,<br>V <sub>CTR</sub> = 0 V (No Switching) | -    | 2.6  | 3.5  | mA   |

| JVLO SECTION                    |                                                                | •                                                                                              | •    | •    | •    | •    |

| LV <sub>CC, START</sub>         | LV <sub>CC</sub> UVLO Turn-On Threshold                        |                                                                                                | 11.2 | 12.5 | 13.8 | V    |

| LV <sub>CC, STOP</sub>          | LV <sub>CC</sub> UVLO Turn-Off Threshold                       |                                                                                                | 8.9  | 10.0 | 11.1 | V    |

| LV <sub>CC, HYS</sub>           | LV <sub>CC</sub> UVLO Hysteresis                               |                                                                                                | _    | 2.5  | -    | V    |

| HV <sub>CC, START</sub>         | HV <sub>CC</sub> UVLO Turn-On Threshold                        |                                                                                                | 8.2  | 9.2  | 10.2 | V    |

| HV <sub>CC, STOP</sub>          | LV <sub>CC</sub> UVLO Turn-Off Threshold                       |                                                                                                | 7.8  | 8.7  | 9.6  | V    |

| HV <sub>CC, HYS</sub>           | HV <sub>CC</sub> UVLO Hysteresis                               |                                                                                                | _    | 0.5  | -    | V    |

| OSCILLATOR &                    | FEEDBACK SECTION                                               |                                                                                                | •    | •    |      | L.   |

| $V_{BH}$                        | Pulse Skip Disable Threshold<br>Voltage                        |                                                                                                | 0.54 | 0.60 | 0.66 | ٧    |

| $V_{BL}$                        | Pulse Skip Enable Threshold<br>Voltage                         |                                                                                                | 0.36 | 0.40 | 0.44 | V    |

| V <sub>RT</sub>                 | Regulated RT Voltage                                           |                                                                                                | 1.5  | 2.0  | 2.5  | V    |

| f <sub>OSC</sub>                | Output Oscillation Frequency                                   | $R_T$ = 11.6 k $\Omega$ , $C_{SS}$ = 1 nF                                                      | 48   | 50   | 52   | kHz  |

|                                 |                                                                | $R_T = 2.7 \text{ k}\Omega, C_{SS} = 1 \text{ nF}$                                             | 188  | 200  | 212  | 1    |

| DC                              | Output Duty Cycle                                              | $R_T = 11.6 \text{ k}\Omega, C_{Load} = 100 \text{ pF}$                                        | 49   | 50   | 51   | %    |

|                                 |                                                                | $R_T = 2.7 \text{ k}\Omega, C_{Load} = 100 \text{ pF}$                                         | 48   | 50   | 52   | 1    |

| SOFT-START A                    | ND RESTART SECTION                                             |                                                                                                | •    | •    |      | u.   |

| I <sub>SS1</sub>                | Soft-Start Current 1                                           | V <sub>CSS</sub> = 0 V, LV <sub>CC</sub> = 17 V                                                | 3    | -    | -    | mA   |

| I <sub>SS2</sub>                | Soft-Start Current 2                                           | V <sub>CSS</sub> = 1.6 V, LV <sub>CC</sub> = 17 V                                              | 25   | 30   | 35   | μА   |

| V <sub>SS START</sub>           | Soft-Start Start Voltage                                       | C <sub>SS</sub> = 1 nF, V <sub>CON</sub> = 3 V                                                 | 1.5  | 1.6  | 1.7  | V    |

| V <sub>SS END</sub>             | Soft-Start End Voltage                                         | C <sub>SS</sub> = 1 nF, V <sub>CON</sub> = 3 V                                                 | 4.0  | 4.2  | 4.4  | V    |

| V <sub>SSC</sub>                | Clamped Soft-Start Voltage                                     | C <sub>SS</sub> = 1 nF, V <sub>CON</sub> = 3 V                                                 | 4.75 | 5.00 | 5.25 | V    |

| fosc_ss                         | Initial Output Oscillation Frequency                           | R <sub>T</sub> = 11.6 kΩ, V <sub>CSS</sub> = 1.6 V                                             | -    | 300  | _    | kHz  |

|                                 | During Soft-Start                                              | R <sub>T</sub> = 5.8 kΩ                                                                        | -    | 530  | _    | 1    |

|                                 |                                                                | R <sub>T</sub> = 2.7 kΩ                                                                        | 600  | -    | -    | 1    |

| V <sub>RT-CON</sub>             | RT-CON Voltage for Startup                                     |                                                                                                | _    | 60   | 120  | mV   |

#### ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C and LV<sub>CC</sub> = 17 V unless otherwise specified) (continued)

| Symbol              | Parameter                                                                     | Test Condition                                                               | Min   | Тур   | Max   | Unit |

|---------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|------|

| JTPUT SECTI         | ON                                                                            | •                                                                            | •     | •     | •     | .48. |

| I <sub>source</sub> | Peak Sourcing Current                                                         | LV <sub>CC</sub> = HV <sub>CC</sub> = 17 V,<br>T <sub>J</sub> = 40°C ~ 130°C | 500   | _     | -     | mA   |

| I <sub>sink</sub>   | Peak Sinking Current                                                          | HV <sub>CC</sub> = 17 V,<br>T <sub>J</sub> = 40°C ~ 130°C                    | 1000  | _     | _     | mA   |

| t <sub>r</sub>      | Rising Time                                                                   | HV <sub>CC</sub> = 17 V, C <sub>Load</sub> = 1 nF                            | -     | 40    | -     | ns   |

| t <sub>f</sub>      | Falling Time                                                                  |                                                                              | -     | 20    | -     | ns   |

| V <sub>HOH</sub>    | High Level of High-Side Gate<br>Signal (V <sub>HVCC</sub> -V <sub>HO</sub> )  | I <sub>O</sub> = 20 mA                                                       | -     | -     | 1.0   | ٧    |

| $V_{HOL}$           | Low Level of High-Side Gate<br>Signal                                         |                                                                              | _     | _     | 0.6   | V    |

| $V_{LOH}$           | High Level of Low-Side Gate<br>Signal (V <sub>LVCC</sub> -V <sub>LO</sub> )   |                                                                              | -     | _     | 1.0   | V    |

| $V_{LOL}$           | Low Level of Low-Side Gate<br>Signal                                          |                                                                              | -     | -     | 0.6   | V    |

| ROTECTION S         | SECTION                                                                       |                                                                              |       |       |       |      |

| I <sub>OLP</sub>    | OLP Sink Current                                                              |                                                                              | 25    | 30    | 35    | μΑ   |

| V <sub>OLP</sub>    | OLP Threshold Voltage                                                         |                                                                              | -0.42 | -0.37 | -0.32 | ٧    |

| t <sub>BOL</sub>    | OLP Blanking Time (Note 3)                                                    |                                                                              | 150   | 200   | 250   | ns   |

| V <sub>OCP</sub>    | OCP Threshold Voltage                                                         |                                                                              | -0.62 | -0.56 | -0.50 | V    |

| t <sub>BO</sub>     | OCP Blanking Time (Note 3)                                                    |                                                                              | 150   | 200   | 250   | ns   |

| V <sub>AOCP</sub>   | AOCP Threshold Voltage                                                        |                                                                              | -1.21 | -1.10 | -0.99 | V    |

| t <sub>BAO</sub>    | AOCP Blanking Time (Note 3)                                                   |                                                                              | -     | 50    | -     | ns   |

| t <sub>DA</sub>     | Delay Time (Low Side) Detecting from V <sub>AOCP</sub> to Switch Off (Note 3) |                                                                              | -     | 250   | 400   | ns   |

| V <sub>OVP</sub>    | LV <sub>CC</sub> Over-Voltage Protection                                      |                                                                              | 21    | 23    | 25    | ٧    |

| $V_{LINE}$          | Line UVLO Threshold Voltage                                                   | V <sub>LS</sub> Sweep, 40°C ~ 130°C                                          | 2.88  | 3.00  | 3.12  | ٧    |

| I <sub>LINE</sub>   | Line UVLO Hysteresis Current                                                  | V <sub>LS</sub> = 2 V                                                        | 9     | 10    | 11    | μΑ   |

| T <sub>SD</sub>     | Thermal Shutdown Temperature (Note 3)                                         |                                                                              | 130   | 140   | 150   | °C   |

| V <sub>FI</sub>     | Fault Input Threshold Voltage for Latch Operation                             |                                                                              | 3.8   | 4.0   | 4.2   | ٧    |

| I <sub>LR</sub>     | Latch-Protection Sustain LV <sub>CC</sub><br>Supply Current                   | LV <sub>CC</sub> = 7.5 V                                                     | =     | 100   | 150   | μΑ   |

| $V_{LR}$            | Latch-Protection Reset LV <sub>CC</sub><br>Supply Voltage                     |                                                                              | 5     | -     | -     | V    |

| EAD-TIME CO         | ONTROL SECTION                                                                |                                                                              |       |       |       |      |

| D <sub>T</sub>      | Dead Time                                                                     | $R_{DT} = 2.7 \text{ k}\Omega, C_{Load} = 1 \text{ nF}$                      | 100   | 150   | 200   | ns   |

|                     |                                                                               | $R_{DT}$ = 18 kΩ, $C_{Load}$ = 1 nF                                          | 250   | 350   | 450   | 1    |

|                     |                                                                               | Short, C <sub>Load</sub> = 1 nF                                              | -     | 50    | -     |      |

|                     |                                                                               | Open, C <sub>Load</sub> = 1 nF                                               | -     | 1000  | -     |      |

|                     | Recommended Dead Time Range                                                   |                                                                              | 100   | -     | 600   | 1    |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

3. This parameter, although guaranteed, is not tested in production.

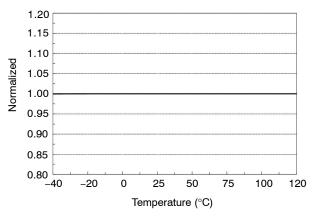

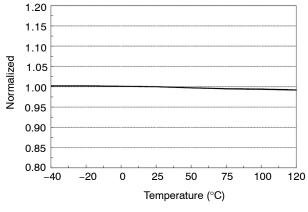

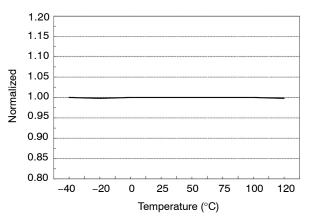

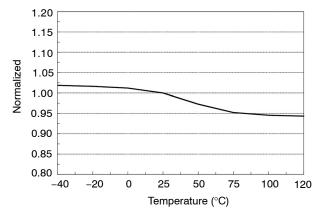

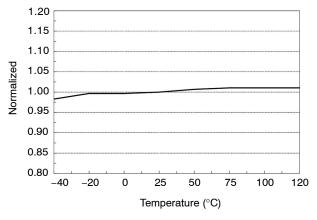

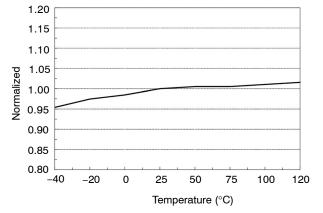

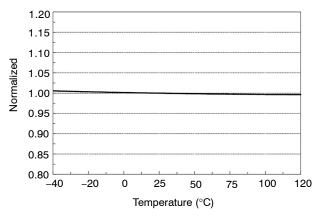

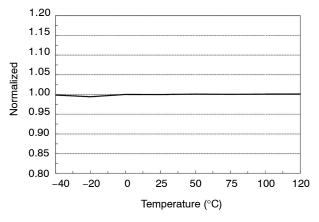

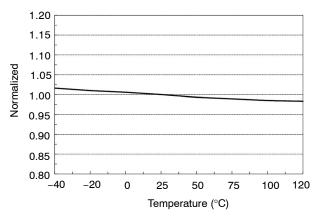

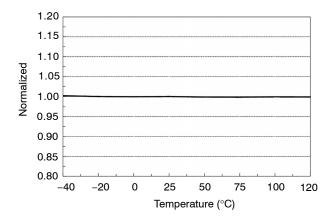

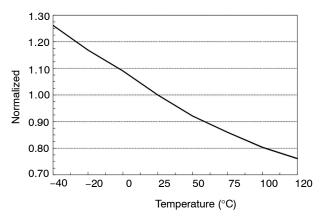

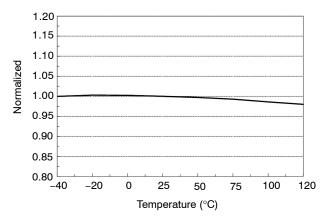

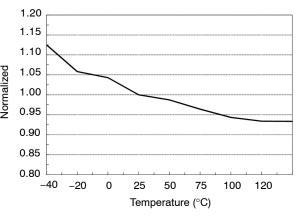

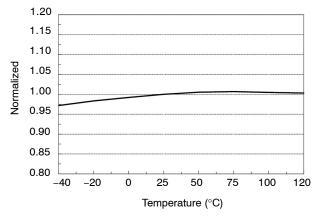

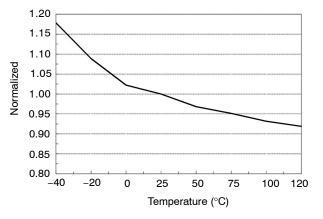

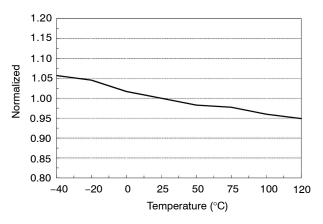

## **TYPICAL CHARACTERISTICS** (These characteristic graphs are normalized at $T_A$ = 25°C)

Figure 4. LV<sub>CC</sub> Start Voltage vs. Temperature

Figure 5. LV<sub>CC</sub> Stop Voltage vs. Temperature

Figure 6. HV<sub>CC</sub> Start Voltage vs. Temperature

Figure 7.  $HV_{CC}$  Stop Voltage vs. Temperature

Figure 8. Pulse Skip Disable vs. Temperature

Figure 9. Pulse Skip Enable Voltage vs. Temperature

## TYPICAL CHARACTERISTICS (These characteristic graphs are normalized at T<sub>A</sub> = 25°C) (continued)

Figure 10. Regulated R<sub>T</sub> Voltage vs. Temperature

Figure 12. Output Oscillation Frequency  $(R_T = 2.7 \text{ k}\Omega)$  vs. Temperature

Figure 14. Output Duty Cycle (R<sub>T</sub> = 2.7 k $\Omega$ ) vs. Temperature

Figure 11. Output Oscillation Frequency  $(R_T = 11.6 \text{ k}\Omega) \text{ vs. Temperature}$

Figure 13. Output Duty Cycle ( $R_T$  = 11.6 k $\Omega$ ) vs. Temperature

Figure 15. I<sub>SS1</sub> vs. Temperature

## **TYPICAL CHARACTERISTICS** (These characteristic graphs are normalized at $T_A = 25$ °C) (continued)

Figure 16.  $I_{SS2}$  vs. Temperature

Figure 18.  $f_{OSC\_SS}$  (R<sub>T</sub> = 2.7 k $\Omega$ ) vs. Temperature

Figure 20. I<sub>OLP</sub> vs. Temperature

Figure 17.  $f_{OSC\_SS}$  (R<sub>T</sub> = 11.6 k $\Omega$ ) vs. Temperature

Figure 19. V<sub>OLP</sub> vs. Temperature

Figure 21.  $V_{\mbox{\scriptsize OCP}}$  vs. Temperature

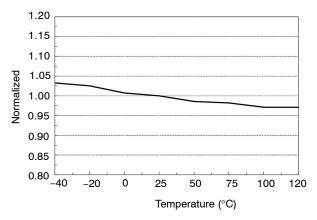

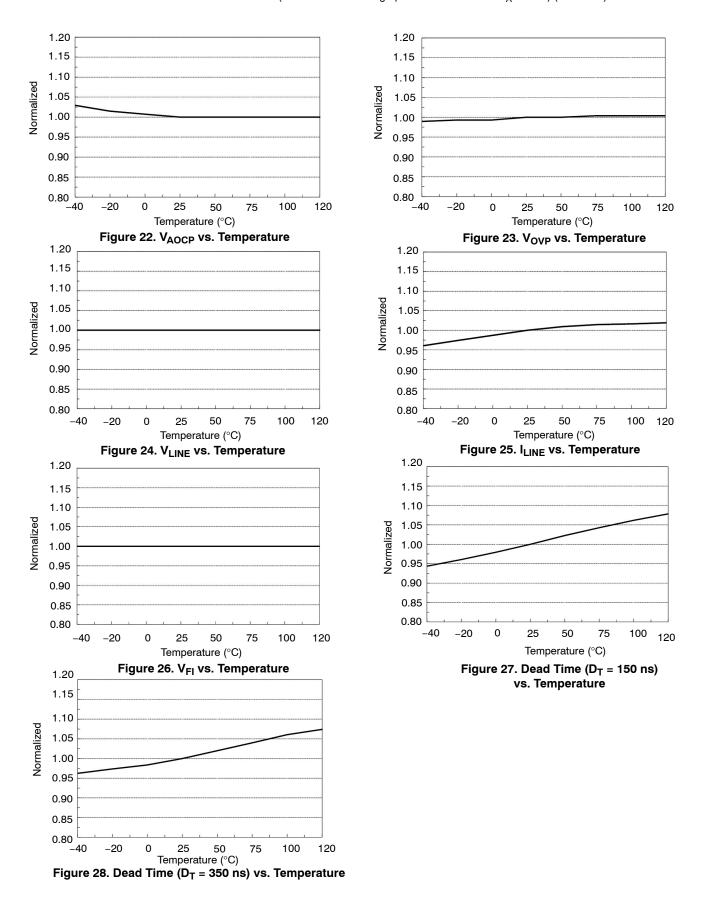

## **TYPICAL CHARACTERISTICS** (These characteristic graphs are normalized at $T_A = 25$ °C) (continued)

#### **FUNCTIONAL DESCRIPTION**

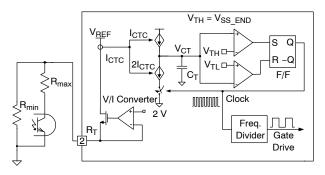

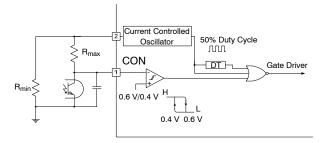

#### **Internal Oscillator**

Figure 29 shows the simplified circuit of internal current–controlled oscillator and typical circuit configuration for the RT pin. Internally, the voltage on the RT pin is regulated at 2 V by the V/I converter. The charging / discharging current for the oscillator capacitor,  $C_T$ , is obtained by mirroring the current flowing out of the RT pin ( $I_{\rm CTC}$ ). By comparing the capacitor voltage with  $V_{\rm TH}$  and  $V_{\rm TL}$  and driving S/R flip–flop with the comparator outputs, the clock signal is obtained. Thus, the switching frequency increases as the RT pin current increases.

As can be seen in Figure 29, an opto-coupler transistor is typically connected to the RT pin through  $R_{max}$  to modulate the switching frequency. During an overload condition, the opto-coupler is fully turned off and  $I_{CTC}$  is solely determined by  $R_{min}$ , which sets the minimum frequency. Meanwhile, the maximum switching frequency is obtained when the opto-coupler is fully turned on. Considering the typical saturation voltage of opto-transistor (0.2 V), the maximum frequency can be obtained by  $R_{max}$  and  $R_{min}$  as:

$$f_{min} = \frac{11, 6 \, k\Omega}{R_{min}} \times 50 \, kHz$$

$$f_{\text{max}} = \left(\frac{11,6 \text{ k}\Omega}{R_{\text{min}}} + \frac{10.4 \text{ k}\Omega}{R_{\text{max}}}\right) \times 50 \text{ kHz}$$

(eq. 1)

Figure 29. Current-Controlled Oscillator

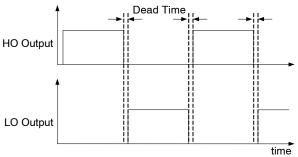

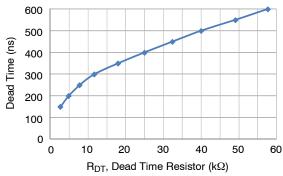

#### **Gate Driver and Dead Time Programming**

The FAN7631 employs a gate drive circuit with high driving capability (source:  $0.5~A/\sin k$ : 1~A) to cover a wide variety of applications. The two gate drive signals (LO and HO) are complimentary; each signal has 50% duty cycle, including the dead time, as shown in Figure 30.

The dead time can be programmed by the resistor,  $R_{DT}$ , as shown in Figure 31. Internally, the voltage on the DT pin is regulated at 1.4 V by the V/I converter and  $I_{DT}$  programs the dead time using  $R_{DT}$ . To improve the noise immunity of the dead time circuit, a sample–and–hold circuit is internally employed. However, severe noises in a high–power application can affect the dead time circuit operation and it is therefore recommended to use a bypass capacitor of

around 10 nF in parallel with the R<sub>DT</sub>. As a protective measure against abnormal conditions, such as DT pin short–to–ground and lift open, shuntresistor and series resistor R<sub>DT,Short</sub> and R<sub>DT,Open</sub> are internally connected to the DT pin. Even when this pin is shorted to ground and lifted open, the dead time is limited to 50 ns (short to ground) and 1000 ns (lifted open). Since the internal resistors have relatively large tolerance, it is recommended to set the dead time between 150 ns and 600 ns to minimize the dead time variation by the internal resistor tolerance.

Figure 30. Gate Driving Signals

Figure 31. Dead Time vs. R<sub>DT</sub>

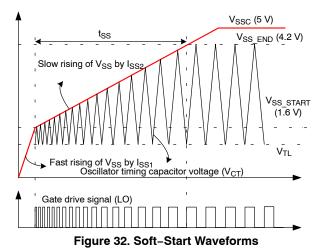

#### Soft-Start

Since the voltage gain of the resonant converter is inversely proportional to the switching frequency, the soft–start is implemented by sweeping down the switching frequency from a high initial frequency until the output voltage is established. The current–steering circuit connected to SS pin adaptively changes the sinking and sourcing current of the SS pin to set soft–start time, OLP shutdown delay, and restart time. As illustrated in Figure 32, the sourcing current,  $I_{SS1}$  (3 mA), is enabled at the beginning of startup, which rapidly raises  $V_{SS}$  up to  $V_{SS\_START}$  (1.6 V). Then the sourcing current is switched to  $I_{SS2}$  (30  $\mu$ A) and gate drive signals are enabled. Due to the small value of  $I_{SS2}$ , the SS pin voltage slowly rises, allowing slow decrease of the switching frequency.

To minimize the frequency variation while the output capacitance of the opto-transistor is charged up, softstart is

delayed until the CON pin voltage (opto-coupler transistor voltage) reaches the RT pin voltage. Thus, the initial switching frequency is not affected by  $R_{max}$  and is solely determined as six times the minimum switching frequency set by  $R_{min}$  as in Equation 1. The maximum switching frequency is also internally limited at 600 kHz.

When  $V_{SS}$  reaches  $V_{SS\_END}$  (4.2 V), soft-start ends. Then, the high threshold of  $V_{CT}$  comparator,  $V_{TH}$ , is clamped at  $V_{SS\_END}$  while  $V_{SS}$  keeps increasing until it reaches  $V_{SSC}$  (5 V). The soft-start time is given as:

$$t_{SS} = C_{SS} \frac{2.6}{3 \times 10^{-5}}$$

(eq. 2)

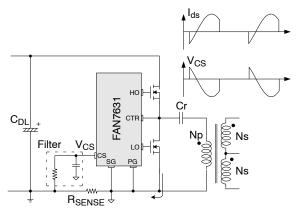

**Current Sensing**

FAN7631 employs a negative voltage sensing method to sense the drain current of the MOSFET. This allows sensing the current without a leading edge spike caused by the low-side MOSFET's driving current. Therefore, the resistive-sensing method requires only a small RC filter. The capacitive-sensing method is also available.

#### Resistive Sensing Method

The FAN7631 can sense the drain current as a negative voltage, as shown in Figure 33. An RC filter with a time constant of  $1/30\sim1/10$  of the operating period is typical.

Figure 33. Resistive Sensing

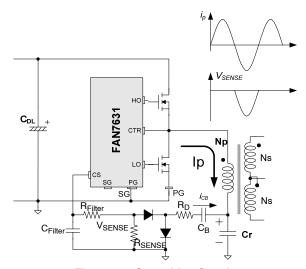

#### Capacitive Sensing Method

The MOSFET drain current can be sensed using an additional capacitor in parallel with the resonant capacitor, as shown in Figure 34. While the low–side switch is turned on, the current,  $I_{CB}$ , through CB introduces  $V_{SENSE}$  across  $R_{SENSE}$ . The  $I_{CB}$  is a fraction of the transformer primary–side current,  $I_p$ , determined by the current divider with capacitors  $C_r$  and  $C_B$  as:

$$i_{CB} = \frac{C_B}{C_r + C_B} i_p \cong \frac{C_B}{C_r} i_p$$

(eq. 3)

Generally,  $1/100\sim1/1000$  is adequate for the ratio of  $C_B/C_r$ .  $R_D$  is used as a damper for reducing noise generated by the switching transition. To prevent the damping resistor from affecting the current divider ratio, the resistor should be much smaller than the impedance of  $C_B$  at the switching frequency, calculated as:

$$R_{\rm D} < < \frac{1}{2\pi f_{\rm S} C_{\rm B}}$$

(eq. 4)

Then, V<sub>SENSE</sub> can be obtained as:

$$V_{Sense} = \frac{C_B}{C_r} R_{sense} i_p$$

(eq. 5)

Figure 34. Capacitive Sensing

#### **Protection Circuit**

The FAN7631 has several self-protective functions: Overload Protection (OLP), Over-Current Protection (OCP), level-change OCP, Abnormal Over-Current Protection (AOCP), Over-Voltage Protection (OVP), Thermal Shutdown (TSD), Fault Input (FI), and Line Under-Voltage Lockout (LUVLO or also called brownout). Level-change OCP, OLP, OCP, OVP, and LUVLO are Auto-Restart Mode protections while AOCP, TSD, and fault input are Latch Mode protections.

Once auto-restart protection is triggered, switching is instantly terminated and the MOSFETs remain off. Then the FAN7631 keeps attempting to restart after the restart delay until the protection situation is removed. When a Latch

Mode protection is triggered, the FAN7631 remains off until  $LV_{CC}$  drops to  $V_{LR}$  (5 V) and then rises above  $LV_{CC,START}$  (12.5 V).

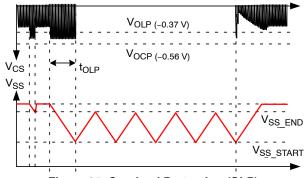

#### Overload Protection (OLP)

When the sensed voltage on the CS pin drops below  $V_{OLP}$  (-0.37 V) for more than OLP blanking time,  $t_{BOL}$  (200 ns),  $C_{SS}$  starts to be discharged by sinking current  $I_{OLP}$ . If the sensed voltage on the CS pin does not drop below  $V_{OLP}$  in the next switching cycle, the current on the SS pin is switched to charging current  $I_{SS1}$ , restoring  $V_{SS}$  as illustrated in Figure 35. If the CS pin voltage drops below  $V_{OLP}$  for in next consecutive switching cycle until  $C_{SS}$  voltage,  $V_{SS}$ , reaches  $V_{SS\_START}$  (1.6 V); OLP is triggered and the gate drive signals remain off. Once the OLP is triggered, FAN7631 repeats charging and discharging  $C_{SS}$  four times, then restarts. The OLP delay,  $t_{OLP}$  and self auto-restart time,  $t_{AR}$ , are given as:

$$t_{OLP} = C_{SS} \frac{3.4}{3 \times 10^{-5}}$$

(eq. 6)

$$t_{AR} = 8 \times C_{SS} \frac{2.6}{3 \times 10^{-5}}$$

(eq. 7)

Figure 35. Overload Protection (OLP)

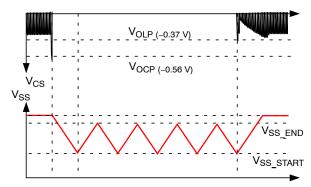

#### Over-Current Protection (OCP)

When the CS pin voltage drops below  $V_{OCP}$  (-0.54 V) for longer than the OCP blanking time,  $t_{BO}$  (200 ns), OCP is triggered, terminating switching operation. Then, FAN7631 repeats charging and discharging  $C_{SS}$  four times before restarting.

Figure 36. Over-Current Protection (OCP)

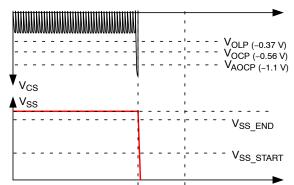

#### **Abnormal Over-Current Protection (AOCP)**

If the secondary-side rectifier diodes are shorted, a large current with extremely high di/dt can flow through the MOSFET before OCP is triggered. AOCP is triggered with a short blanking time of 50 ns,  $t_{\rm BAO}$ , when the sensed voltage drops below -1.10 V, terminating the switching operation. Once the protection is triggered,  $V_{\rm SS}$  is discharged by an internal switch. Since it is a Latch Mode protection, the protection is reset when LV<sub>CC</sub> drops to  $V_{\rm LR}$  (5 V).

Figure 37. Abnormal Over-Current Protection (AOCP)

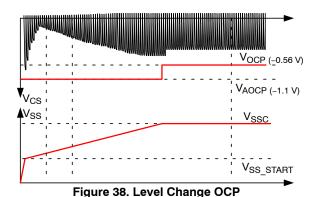

#### Level-Change Over-Current Protection (OCP)

Even with soft–start, there can be large overshoot current for the initial several switching cycles until the resonant capacitor voltage reaches its steady–state value. To prevent the startup failure by OCP, the OCP threshold is changed to  $V_{AOCP}$  level while the Latch Mode AOCP is disabled during soft–start.

Over-Voltage Protection (OVP)

When the  $LV_{CC}$  reaches 23 V, OVP is triggered. This protection is used when auxiliary winding of the transformer is utilized to supply  $V_{CC}$  to the FAN7631.

#### Thermal Shutdown (TSD)

The thermal shutdown function is integrated to detect abnormal over–temperature, such as abnormal ambient temperature rising or over–driving of gate drive circuit. If the junction temperature exceeds  $T_{\rm SD}$  (130°C), thermal shutdown is triggered in Latch Mode.

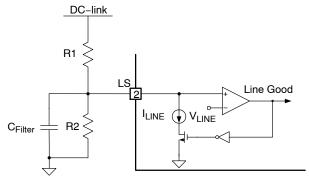

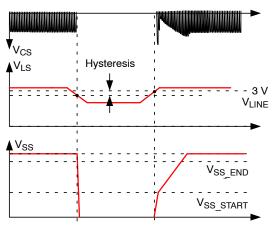

Line-UVLO

FAN7631 includes a precise line–UVLO (or brownout) function with programmable hysteresis voltage, as can be seen in Figure 39. When the line voltage is recovered, it starts up with soft–start, as shown in Figure 39. A hysteresis voltage between the start and stop voltage is programmable by I<sub>LINE</sub> and external resistor R1. In normal operation, the comparator's output is HIGH and I<sub>LINE</sub> is disabled I<sub>LINE</sub> is activated when the comparator's output is LOW, introducing hysteresis.

If necessary,  $C_{Filter}$  can be used to reduce noise interference. Generally, hundreds of pico-farad to tens of nano-farad is adequate depending on the level of noise.

Figure 39. Line-UVLO

Figure 40. Line UVLO Waveforms

The DC link input-voltages for start and stop are calculated as:

$$V_{DL, STOP} = V_{LINE} \times \frac{R1 + R2}{R2}$$

$$V_{DL, START} = V_{DL, STOP} + I_{LINE} \times R1$$

(eq. 8)

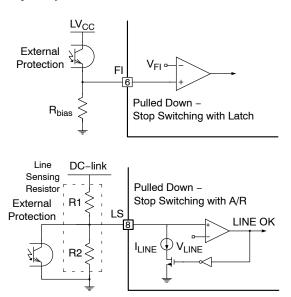

#### Simple Remote-On/Off

The power stage can be shut down with Latch Mode or Auto-Restart Mode, as shown in Figure 41. For the Latch

Mode protection, the FI pin is used, which stops the switching immediately once the voltage on FI pin is pulled above  $V_{FI}$  (4 V) using an opto–coupler. To configure an external protection with Auto–Restart Mode, an optocoupler can be used on the LS pin. When voltage on the LS pin is pulled below  $V_{LINE}$  (3 V), line UVLO is triggered. When LS pin voltage is pulled HIGH, above 3 V, FAN7631 starts up softly.

Figure 41. External Protection Circuits (Top: Latch Mode, Bottom: A/R Mode)

#### **Skip Cycle Operation**

The FAN7631 provides the pulse–skip function to prevent the switching frequency from increasing too much at noload condition. Figure 42 shows the internal block diagram for the control (CON) pin and its external configuration. The CON pin is typically connected to the collector terminal of the opto–coupler and the FAN7631 stops switching when the CON pin voltage drops below 0.4 V. FAN7631 resumes switching when the CON pin voltage rises above 0.6 V. The frequency that causes pulse skipping is given as:

$$f_{SKIP} = \left(\frac{5.8 \text{ k}\Omega}{\text{R}_{\text{min}}} + \frac{4.6 \text{ k}\Omega}{\text{R}_{\text{max}}}\right) \times 100 \text{ kHz} \qquad \text{(eq. 9)}$$

Figure 42. Pulse-Skipping Circuit

#### **PCB Layout Guideline**

Figure 43 shows the PCB layout guideline to minimize the usage of jumpers. Good PCB layout improves power system efficiency and reliability and minimizes EMI. The Power

Ground (PG) and Signal Ground (SG) should meet at a single point. Jumpers should be avoided, especially for the ground trace.

Figure 43. PCB Layout Guideline

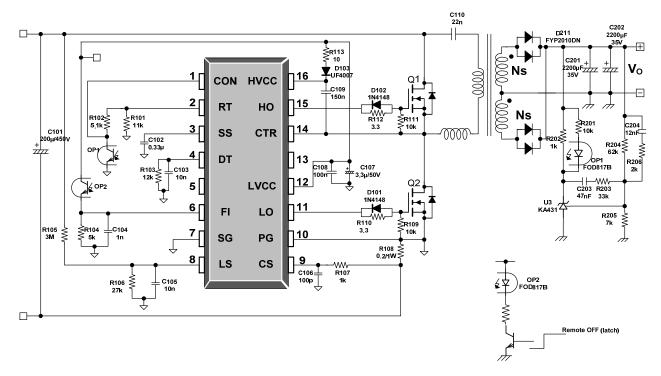

# TYPICAL APPLICATION CIRCUIT (Half-Bridge LLC Resonant Converter)

| Application | Device  | Input Voltage Range        | Rated Output Power | Output Voltage<br>(Rated Current) |

|-------------|---------|----------------------------|--------------------|-----------------------------------|

| LCD TV      | FAN7631 | 400 V (20 ms Hold-Up Time) | 192 W              | 24 V-8 A                          |

#### **Features**

- High efficiency (>94% at 400 V<sub>DC</sub> input).

- Reduced EMI noise through zero-voltage-switching (ZVS).

- Enhanced system reliability with various protection functions.

Figure 44. Typical Application Circuit

## TYPICAL APPLICATION CIRCUIT (continued)

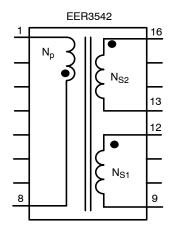

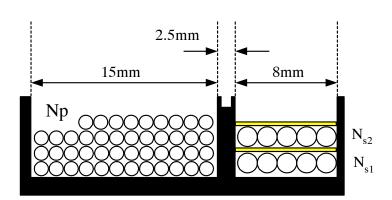

Usually, the LLC resonant converter requires large leakage inductance value. To obtain a large leakage inductance, sectional winding method is used.

- Core: EER3542 (Ae = 107 mm<sup>2</sup>)

- Bobbin: EER3542 (Horizontal)

Figure 45. Winding Specifications

**Table 1. WINDING SPECIFICATIONS**

|                 | Pin (S → F) | Wire                                             | Turns | Winding Method  |

|-----------------|-------------|--------------------------------------------------|-------|-----------------|

| N <sub>p</sub>  | 8 → 1       | 0.12 $\varphi \rightarrow$ 30 (Litz Wire)        | 45    | Section Winding |

| N <sub>S1</sub> | 12 → 9      | $0.1~\varphi \rightarrow 100~\text{(Litz Wire)}$ | 5     | Section Winding |

| N <sub>S2</sub> | 16 → 13     | $0.1 \ \varphi \rightarrow 100 \ (Litz \ Wire)$  | 5     | Section Winding |

|                                                  | Pin | Specifications | Remark                              |

|--------------------------------------------------|-----|----------------|-------------------------------------|

| Primary-Side Inductance (L <sub>P</sub> )        | 1–8 | 630 μH ±5%     | 100 kHz, 1 V                        |

| Primary-Side Effective Leakage (L <sub>R</sub> ) | 1–8 | 145 μH ±5%     | Short One of the Secondary Windings |

#### **ORDERING INFORMATION**

| Part Number | Operating Temperature Range | Package                              | Shipping <sup>†</sup> |

|-------------|-----------------------------|--------------------------------------|-----------------------|

| FAN7631SJX  | −40°C ~ 130°C               | 16-Lead, Small-Outline Package (SOP) | 2000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

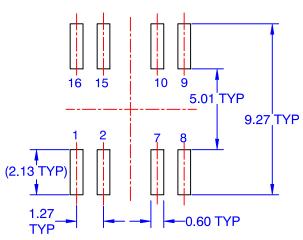

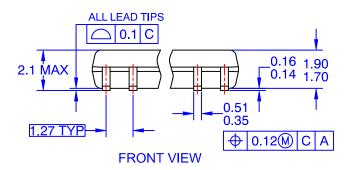

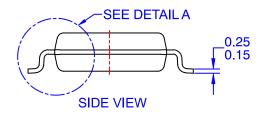

#### SOP16 CASE 565BF **ISSUE O**

**DATE 31 DEC 2016**

LAND PATTERN RECOMMENDATION

# **GAGE PLANE** 0-8° TYP 0.25 MIN SEATING PLANE 0.25 <del>-</del>1.25<del>-</del>

**DETAIL A**

## NOTES:

- A. CONFORMS TO EIAJ EDR-7320 REGISTRATION, ESTABLISHED IN DECEMBER, 1998. B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

| DOCUMENT NUMBER: | 98AON13763G | Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOP16       |                                                                                                                                                                               | PAGE 1 OF 1 |  |  |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

## PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative