# INTEGRATED CIRCUITS

Product data sheet Supersedes data of 1998 Sep 04 2006 Aug 04

Philips Semiconductors

## SCC2691

#### DESCRIPTION

The Philips Semiconductors SCC2691 Universal Asynchronous Receiver/Transmitter (UART) is a single-chip CMOS-LSI communications device that provides a full-duplex asynchronous receiver/transmitter. It is fabricated with Philips Semiconductors CMOS technology which combines the benefits of high density and low power consumption.

The operating speed of the receiver and transmitter can be selected independently as one of 18 fixed baud rates, a 16X clock derived from a programmable counter/timer, or an external 1X or 16X clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the UART particularly attractive for dual-speed channel applications such as clustered terminal systems.

The receiver is quadruple buffered to minimize the potential of receiver overrun or to reduce interrupt overhead in interrupt driven systems. In addition, a handshaking capability is provided to disable a remote UART transmitter when the receiver buffer is full.

The UART provides a power-down mode in which the oscillator is frozen but the register contents are stored. This results in reduced power consumption on the order of several magnitudes.

The UART is fully TTL compatible and operates from a single +5V power supply.

#### FEATURES

- Full-duplex asynchronous receiver/transmitter

- Quadruple buffered receiver data register

- Programmable data format:

- 5 to 8 data bits plus parity

- Odd, even, no parity or force parity

- 1, 1.5 or 2 stop bits programmable in 1/16-bit increments

- 16-bit programmable Counter/Timer

- Baud rate for the receiver and transmitter selectable from:

- 22 fixed rates: 50 to 115.2K baud

- Non-standard rates to 115.2 kb

- Non-standard user-defined rate derived from programmable timer/ counter

- External 1X or 16X clock

- Parity, framing, and overrun detection

- False start bit detection

- Line break detection and generation

- Programmable channel mode

- Normal (full-duplex)

- Automatic echo

- Local loopback

- Remote Loopback

- Multi-function programmable 16-bit counter/timer

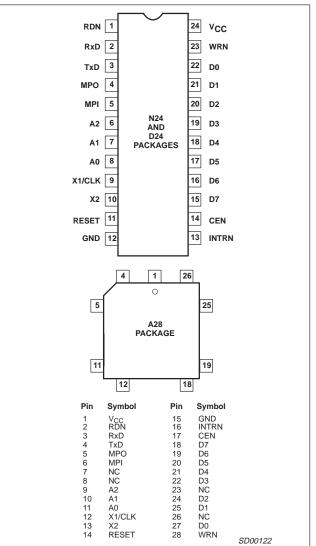

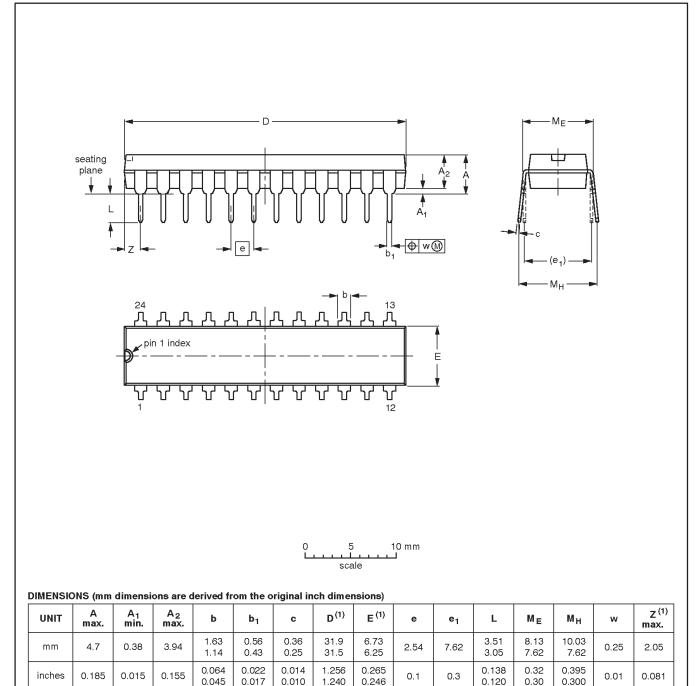

#### **PIN CONFIGURATIONS**

Figure 1. Pin Configurations

- Single interrupt output with seven maskable interrupting conditions

- On-chip crystal oscillator

- Low power mode

- TTL compatible

- Single +5V power supply

- Commercial (0°C to +70°C) and industrial (-40°C to +85°C) temperature versions available

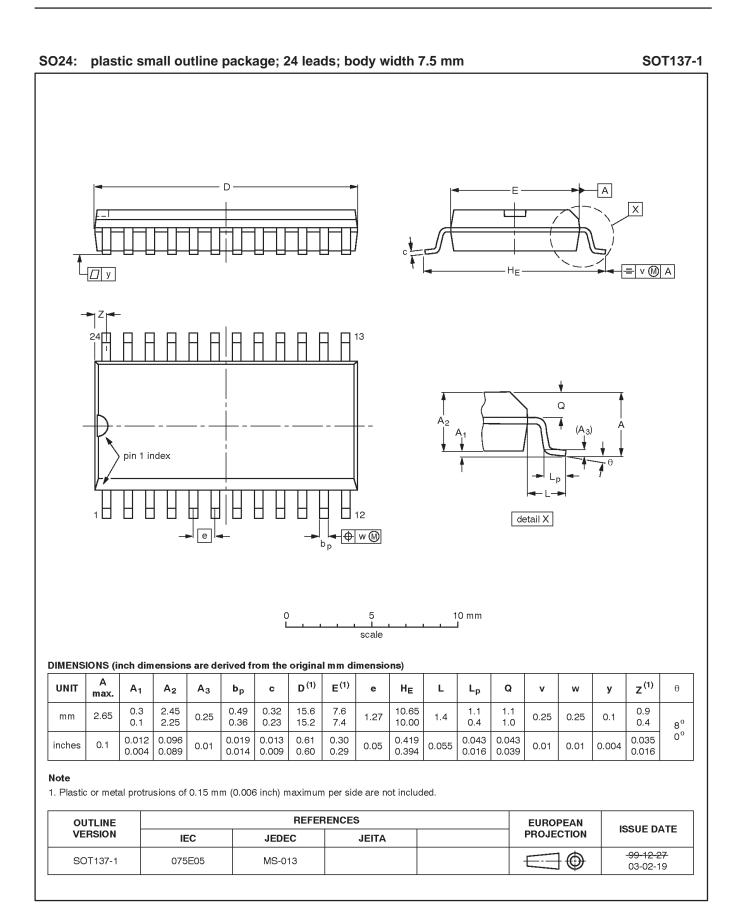

- SOL, PLCC and 300 mil wide DIP packages available

Product data sheet

#### **ORDERING INFORMATION**

|                                                   | COMMERCIAL                                                           | INDUSTRIAL                                                             |          |

|---------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|----------|

| PACKAGES                                          | V <sub>CC</sub> = +5V <u>+</u> 10%,<br>T <sub>A</sub> = 0°C to +70°C | V <sub>CC</sub> = +5V <u>+</u> 10%,<br>T <sub>A</sub> = −40°C to +85°C | VERSION  |

| 24-Pin Plastic Dual In-Line Package (DIP)         | SCC2691AC1N24                                                        | SCC2691AE1N24                                                          | SOT222-1 |

| 28-Pin Plastic Leaded Chip Carrier (PLCC) Package | SCC2691AC1A28                                                        | SCC2691AE1A28                                                          | SOT261-2 |

| 24-Pin Plastic Small Outline Large (SOL) Package  | SCC2691AC1D24                                                        |                                                                        | SOT137-1 |

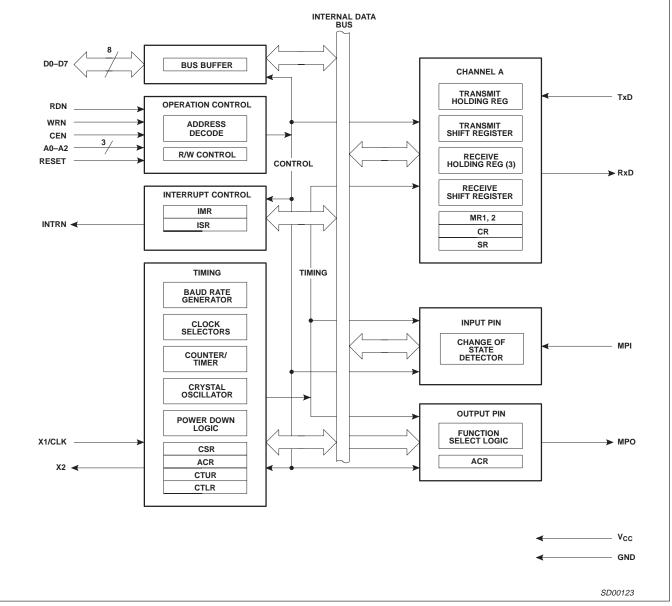

#### **BLOCK DIAGRAM**

Figure 2. Block Diagram

## **PIN DESCRIPTION**

|                 | PIN   | NO.                     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-------|-------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC        | DIP   | PLCC                    | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D0D7            | 22–15 | 27, 25,<br>24,<br>22–18 | I    | <b>Data Bus:</b> Active-high 8-bit bidirectional 3-State data bus. Bit 0 is the LSB and bit 7 is the MSB. All data, command, and status transfers between the CPU and the UART take place over this bus. The direction of the transfer is controlled by the WRN and RDN inputs when the CEN input is low. When the CEN input is high, the data bus is in the 3-State condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CEN             | 14    | 17                      | I    | <b>Chip Enable:</b> Active-low input. When low, data transfers between the CPU and the UART are enabled on D0–D7 as controlled by the WRN, RDN and A0–A2 inputs. When CEN is high, the UART is effectively isolated from the data bus and D0–D7 are placed in the 3-State condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WRN             | 23    | 28                      | I    | <b>Write Strobe:</b> Active-low input. A low on this pin while CEN is low causes the contents of the data bus to be transferred to the register selected by A0–A2. The transfer occurs on the trailing (rising) edge of the signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RDN             | 1     | 2                       | I    | <b>Read Strobe:</b> Active-low input. A low on this pin while CEN is low causes the contents of the register selected by A0–A2 to be placed on the data bus. The read cycle begins on the leading (falling) edge of RDN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A0–A2           | 8–6   | 11–9                    | I    | Address Inputs: Active-high address inputs to select the UART registers for read/write operations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET           | 11    | 14                      | I    | <b>Reset:</b> Master reset. A high on this pin clears the status register (SR), the interrupt mask register (IMR), and the interrupt status register (ISR), sets the mode register pointer to MR1, and places the receiver and transmitter in the inactive state causing the TxD output to go to the marking (high) state. Clears Test modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INTRN           | 13    | 16                      | 0    | <b>Interrupt Request:</b> This active-low output is asserted upon occurrence of one or more of seven maskable interrupting conditions. The CPU can read the interrupt status register to determine the interrupting condition(s). This open-drain output requires a pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

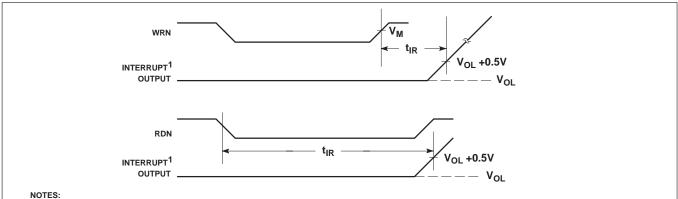

| X1/CLK          | 9     | 12                      | I    | <b>Crystal 1:</b> Crystal connection or an external clock input. A crystal of a clock the appropriate frequency (nominally 3.6864 MHz) must be supplied at all times. For crystal connections see Figure 7, Clock Timing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| X2              | 10    | 13                      | I    | <b>Crystal 2:</b> Crystal connection. See Figure 7. If a crystal is not used it is best to keep this pin not connected although it is permissible to ground it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RxD             | 2     | 3                       | I    | <b>Receiver Serial Data Input:</b> The least significant bit is received first. If external receiver clock is specified, this input is sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TxD             | 3     | 4                       | 0    | <b>Transmitter Serial Data Output:</b> The least significant bit is transmitted first. This output is held in the marking (high) condition when the transmitter is idle or disabled and when the UART is operating in local loopback mode. If external transmitter is specified, the data is shifted on the falling edge of the transmitter clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MPO             | 4     | 5                       | Ο    | Multi-Purpose Output: One of the following functions can be selected for this output pin by programming the auxiliary control register:<br>RTSN – Request to send active-low output. This output is asserted and negated via the command register. By appropriate programming of the mode registers, RTSN can be programmed to be automatically reset after the character in the transmitter is completely shifted or when the receiver FIFO and shift register are full.<br>C/TO – The counter/timer output.<br>TxC1X – The 1X clock for the transmitter.<br>TxC16X – The 16X clock for the transmitter.<br>RxC16X – The 16X clock for the receiver.<br>TxRDY – The transmitter holding register empty signal. Active-low output. (Open drain)<br>RxRDY/FFULL – The receiver FIFO not empty/full signal. Active-low output. (Open drain) |

| MPI             | 5     | 6                       | I    | Multi-Purpose Input: This pin can serve as an input for one of the following functions:<br>GPI – General purpose input. The current state of the pin can be determined by reading the<br>ISR.<br>CTSN – Clear-to-send active-low input.<br>CTCLK – Counter/timer external clock input.<br>RTCLK – Receiver and/or transmitter external clock input. This may be a 1X or 16X clock as<br>programmed by CSR[3:0] or CSR[7:4].<br>Pin has an internal V <sub>CC</sub> pull-up device supplying 1 to 4 $\mu$ A of current.                                                                                                                                                                                                                                                                                                                    |

| V <sub>CC</sub> | 24    | 1                       | I    | Power Supply: +5V supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| GND             | 12    | 15                      |      | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

SCC2691

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | PARAMETER                                        | RATING                        | UNIT |

|------------------|--------------------------------------------------|-------------------------------|------|

| T <sub>A</sub>   | Operating ambient temperature range <sup>2</sup> | Note 4                        | °C   |

| T <sub>STG</sub> | Storage temperature range                        | -65 to +150                   | °C   |

| V <sub>CC</sub>  | Voltage from V <sub>CC</sub> to GND <sup>3</sup> | -0.5 to + 7.0                 | V    |

| V <sub>S</sub>   | Voltage from any pin to ground <sup>3</sup>      | –0.5 to V <sub>CC ±</sub> 10% | V    |

| PD               | Power Dissipation                                | 300                           | mW   |

#### NOTES:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operation section of this specification is not implied.

2. For operating at elevated temperature, the device must be derated based on +150°C maximum junction temperature.

This product includes circuitry specifically designed for the protection of its internal devices from damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying any voltages larger than the rated maxima.

Parameters are valid over specified temperature range. See Ordering Information table for applicable operating temperature and Vac supply

Parameters are valid over specified temperature range. See Ordering Information table for applicable operating temperature and V<sub>CC</sub> supply range.

| SYMBOL                                          | PARAMETER TEST CONDITIONS                 |                                 |                         | LIMITS     |                 |          |  |

|-------------------------------------------------|-------------------------------------------|---------------------------------|-------------------------|------------|-----------------|----------|--|

| STMBOL                                          | PARAMETER                                 | TEST CONDITIONS                 | Min                     | Тур        | Max             |          |  |

| V <sub>IL</sub><br>V <sub>IH</sub>              | Input low voltage<br>Input high voltage   |                                 |                         |            | 0.8             | V        |  |

|                                                 | All except X1/CLK<br>X1/CLK               |                                 | 2<br>0.8V <sub>CC</sub> |            | V <sub>CC</sub> | V<br>V   |  |

| V <sub>OL</sub><br>V <sub>OH</sub> <sup>4</sup> | Output low voltage<br>Output high voltage | I <sub>OL</sub> = 2.4mA         |                         |            | 0.4             | V        |  |

|                                                 | (except open drain outputs)               | I <sub>OH</sub> = -400μA        | 2.4                     |            |                 | V        |  |

| IIL                                             | Input leakage current                     | $V_{IN} = 0$ to $V_{CC}$        | -10                     |            | 10              | μA       |  |

| ILL                                             | Data bus 3-State leakage current          | $V_{O} = 0.4$ to $V_{CC}$       | -10                     |            | 10              | μΑ       |  |

| I <sub>OD</sub>                                 | Open-drain output leakage current         | $V_{O} = 0.4$ to $V_{CC}$       | -10                     |            | 10              | μA       |  |

| I <sub>XIL</sub>                                | X1/CLK low input current                  | V <sub>IN</sub> = 0, X2 floated | -100                    | -30        | 0               | μΑ       |  |

| I <sub>XIH</sub>                                | X1/CLK high input current                 | $V_{IN} = V_{CC}$ , X2 floated  | 0                       | 30         | 100             | μΑ       |  |

| I <sub>X2L</sub>                                | X2 low output current                     | $V_{OUT} = 0, X1/CLK = V_{CC}$  | -100                    |            |                 | μΑ       |  |

| I <sub>X2H</sub>                                | X2 high output current                    | $V_{OUT} = V_{CC}, X1/CLK = 0V$ |                         |            | 100             | μA       |  |

| I <sub>CCA</sub>                                | Power supply current, active              | 0°C to +70°C<br>-40°C to +85°C  |                         | 0.8<br>1.0 | 2.0<br>2.5      | mA<br>mA |  |

| ICCD                                            | Power down current <sup>5</sup>           |                                 |                         |            | 500             | μΑ       |  |

#### DC ELECTRICAL CHARACTERISTICS<sup>1, 2, 3</sup>

NOTES:

1. Parameters are valid over specified temperature range. See Ordering Information table for applicable operating temperature and V<sub>CC</sub> supply range.

All voltage measurements are referenced to ground (GND). For testing, all input signals swing between 0V and 3.0V with a transition time of 20ns max. For X1/CLK, this swing is between 0.4V and 4.0V. All time measurements are referenced at input voltages of 0.8V and 2V and output voltages of 0.8V and 2V as appropriate.

3. Typical values are at +25°C, typical supply voltages, and typical processing parameters.

4. Test condition for outputs:  $C_L = 150$  pF, except interrupt outputs. Test conditions for interrupt outputs:  $C_L = 50$  pF,  $R_L = 2.7$  k $\Omega$  to V<sub>CC</sub>.

5. For power down current levels in the 1µA region see the UART application note.

Downloaded from Arrow.com.

# Universal asynchronous receiver/transmitter (UART)

## AC ELECTRICAL CHARACTERISTICS<sup>1, 2, 3, 4</sup>

| SYMBOL                        | DADAMETED                                                             | LIMITS |        |            |            |  |

|-------------------------------|-----------------------------------------------------------------------|--------|--------|------------|------------|--|

| STMBUL                        | PARAMETER —                                                           | Min    | Тур    | Max        | UNIT       |  |

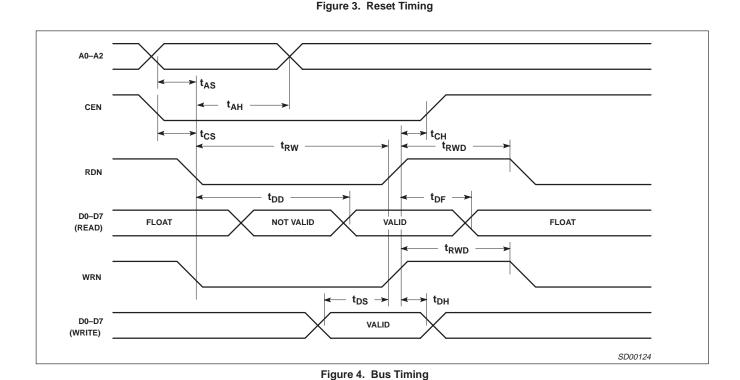

| Reset timing                  | (Figure 3)                                                            |        | •      | •          |            |  |

| RES                           | Reset pulse width                                                     | 100    |        |            | ns         |  |

| Bus timing (                  | Figure 4) <sup>5</sup>                                                |        | •      | •          |            |  |

| t <sub>AS</sub>               | A0–A2 setup time to RDN, WRN low                                      | 10     |        |            | ns         |  |

| t <sub>AH</sub>               | A0–A2 hold time from RDN, WRN low                                     | 100    |        |            | ns         |  |

| t <sub>CS</sub>               | CEN setup time to RDN, WRN low                                        | 0      |        |            | ns         |  |

| t <sub>CH</sub>               | CEN hold time from RDN, WRN high                                      | 0      |        |            | ns         |  |

| t <sub>RW</sub>               | WRN, RDN pulse width                                                  | 150    |        |            | ns         |  |

| t <sub>DD</sub>               | Data valid after RDN low                                              |        |        | 125        | ns         |  |

| t <sub>DF</sub>               | Data bus floating after RDN high                                      |        |        | 110        | ns         |  |

| t <sub>DS</sub>               | Data setup time before WRN high                                       | 50     |        |            | ns         |  |

| t <sub>DH</sub>               | Data hold time after WRN high                                         | 30     |        |            | ns         |  |

| t <sub>RWD</sub>              | Time between reads and/or writes <sup>6, 7</sup>                      | 150    |        |            | ns         |  |

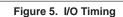

| MPI and MP                    | O timing (Figure 5) <sup>5</sup>                                      |        | •      | •          |            |  |

| t <sub>PS</sub>               | MPI input setup time before RDN low                                   | 30     |        |            | ns         |  |

| t <sub>PH</sub>               | MI input hold time after RDN low                                      | 30     |        |            | ns         |  |

| t <sub>PD</sub>               | MPO output valid after WRN high                                       |        |        | 370        | ns         |  |

| Interrupt tim                 | ing (Figure 6)                                                        |        | •      | •          |            |  |

| t <sub>IR</sub>               | INTRN negated                                                         |        |        |            |            |  |

|                               | Read RHR (RxRDY/FFULL interrupt)                                      |        |        | 370        | ns         |  |

|                               | Write THR (TxRDY, TxEMT interrupt)                                    |        |        | 370        | ns         |  |

|                               | Reset command (break change interrupt)                                |        |        | 370        | ns         |  |

|                               | Reset command (MPI change interrupt)                                  |        |        | 370        | ns         |  |

|                               | Stop C/T command (counter interrupt)                                  |        |        | 370        | ns         |  |

|                               | Write IMR (clear of interrupt mask bit)                               |        |        | 270        | ns         |  |

| Clock timing                  | ; (Figure 7)                                                          |        | •      | •          |            |  |

| t <sub>CLK</sub>              | X1/CLK high or low time                                               | 100    |        |            | ns         |  |

| f <sub>CLK</sub> <sup>9</sup> | X1/CLK frequency                                                      | 0      |        | 4.0        | MHz        |  |

| tстс                          | Counter/timer clock high or low time                                  | 100    |        |            | ns         |  |

| fcTc <sup>8</sup>             | Counter/timer clock frequency                                         | 0      |        | 4.0        | MHz        |  |

| t <sub>RX</sub>               | RxC high or low time                                                  | 220    |        |            | ns         |  |

| f <sub>RX</sub> <sup>8</sup>  | RxC frequency (16X)<br>RxC frequency (1X)                             | 0<br>0 | 3.6864 | 2.0<br>1.0 | MHz<br>MHz |  |

| t <sub>TX</sub>               | TxC high or low time                                                  | 220    |        |            | ns         |  |

| f <sub>TX</sub> 8             | TxC frequency (16X)<br>TxC frequency (1X)                             | 0<br>0 |        | 2.0<br>1.0 | MHz<br>MHz |  |

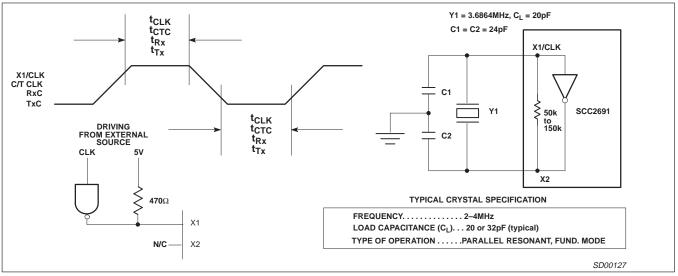

| Transmitter                   | timing (Figure 8)                                                     |        |        |            |            |  |

| t <sub>TXD</sub>              | TxD output delay from TxC external clock input on IP pin              |        |        | 350        | ns         |  |

| t <sub>TCS</sub>              | Output delay from TxC low at OP pin to TxD data output                | 0      |        | 150        | ns         |  |

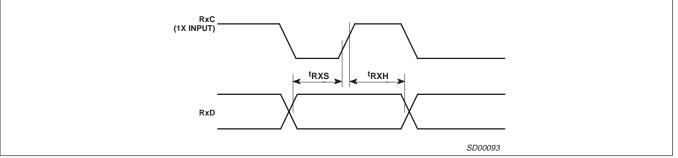

| Receiver tim                  | ning (Figure 9)                                                       |        | •      | •          | •          |  |

| t <sub>RXS</sub>              | RxD data setup time before RxC high at external clock input on IP pin | 100    |        |            | ns         |  |

| t <sub>RXH</sub>              | RxD data hold time after RxC high at external clock input on IP pin   | 100    |        |            | ns         |  |

NOTES:

1. Parameters are valid over specified temp. range. See Ordering Information table for applicable operating temp. and V<sub>CC</sub> supply range.

2. All voltage measurements are referenced to ground (GND). For testing, all input signals swing between 0V and 3.0V with a transition time of 20ns max. For X1/CLK, this swing is between 0.4V and 4.0V. All time measurements are referenced at input voltages of 0.8V and 2V and output voltages of 0.8V and 2V as appropriate.

3. Typical values are at +25°C, typical supply voltages, and typical processing parameters.

4. Test condition for outputs:  $C_L = 150$  pF, except interrupt outputs. Test conditions for interrupt outputs:  $C_L = 50$  pF,  $R_L = 2.7$  k $\Omega$  to V<sub>CC</sub>.

5. Timing is illustrated and referenced to the WRN and RDN inputs. The device may also be operated with CEN as the 'strobing' input. In this case, all timing specifications apply referenced to the falling and rising edges of CEN. CEN and RDN (also CEN and WRN) are ORed internally. As a consequence, this signal asserted last initiates the cycle and the signal negated first terminates the cycle.

6. If CEN is used as the 'strobing' input, this parameter defines the minimum high time between one CEN and the next. The RDN signal must be negated for t<sub>RWD</sub> guarantee that any status register changes are valid.

7. Consecutive write operations to the command register require at least three rising edges of the X1 clock between writes.

8. These parameters are guaranteed by design, but are not 100% tested in production.

9. Operation to 0MHz is assured by design. Minimum test frequency is 2MHz.

## SCC2691

#### **BLOCK DIAGRAM**

As shown in the block diagram, the UART consists of: data bus buffer, interrupt control, operation control, timing, receiver and transmitter.

#### **Data Bus Buffer**

The data bus buffer provides the interface between the external and internal data busses. It is controlled by the operation control block to allow read and write operations to take place between the controlling CPU and UART.

#### Interrupt Control

A single interrupt output (INTRN) is provided which may be asserted upon occurrence of any of the following internal events:

- Transmit holding register ready

- Transmit shift register empty

- Receive holding register ready or FIFO full

- Change in break received status

- Counter reached terminal count

- Change in MPI input

- Assertion of MPI input

Associated with the interrupt system are the interrupt mask register (IMR) and the interrupt status register (ISR). The IMR can be programmed to select only certain of the above conditions to cause INTRN to be asserted. The ISR can be read by the CPU to determine all currently active interrupting conditions. However, the bits of the ISR are not masked by the IMR.

#### **Operation Control**

The operation control logic receives operation commands from the CPU and generates appropriate signals to internal sections to control device operation. It contains address decoding and read and write circuits to permit communications with the microprocessor via the data bus buffer. The functions performed by the CPU read and write operations are shown in Table 1.

#### Table 1. Register Addressing

| A2 | A1 | A0 | READ<br>(RDN = 0) | WRITE<br>(WRN = 0) |

|----|----|----|-------------------|--------------------|

| 0  | 0  | 0  | MR1, MR2          | MR1, MR2           |

| 0  | 0  | 1  | SR                | CSR                |

| 0  | 1  | 0  | BRG Test          | CR                 |

| 0  | 1  | 1  | RHR               | THR                |

| 1  | 0  | 0  | 1X/16X Test       | ACR                |

| 1  | 0  | 1  | ISR               | IMR                |

| 1  | 1  | 0  | CTU               | CTUR               |

| 1  | 1  | 1  | CTL               | CTLR               |

#### NOTE;

\*Reserved registers should never be read during operation since they are reserved for internal diagnostics.

ACR = Auxiliary control register

- CR = Command register

- CSR = Clock select register

- CTL = Counter/timer lower output register

- CTLR = Counter/timer lower preset register

- CTU = Counter/timer upper output register

- CTUR = Counter/timer upper preset register

- MR = Mode register A

SR = Status register

THR = Tx holding register

\* See Table 6 for BRG Test frequencies in this data sheet, and "Extended baud rates for SCN2681, SCN68681, SCC2691, *SCC2692, SCC68681 and SCC2698B*" Philips Semiconductors ICs for Data Communications, IC-19, 1994.

Mode registers 1 and 2 are accessed via an auxiliary pointer. The pointer is set to MR1 by RESET or by issuing a reset pointer command via the command register. Any read or write of the mode register while the pointer is at MR1 switches the pointer to MR2. the pointer then remains at MR2 so that subsequent accesses are to MR2, unless the pointer is reset to MR1 as described above.

#### **Timing Circuits**

The timing block consists of a crystal oscillator, a baud rate generator, a programmable 16-bit counter/timer, and two clock selectors.

The crystal oscillator operates directly from a 3.6864MHz crystal connected across the X1/ CLK and X2 inputs with a minimum of external components. If an external clock of the appropriate frequency is available, it may be connected to X1/CLK. If an external clock is used instead of a crystal, X1/CLK is driven using a configuration similar to the one in Figure 7. In this case, the input high-voltage must be capable of attaining the voltage specified in the DC Electrical Characteristics. The clock serves as the basic timing reference for the baud rate generator (BRG), the counter/timer, and other internal circuits. A clock frequency, within the limits specified in the electrical specifications, must be supplied if the internal BRG is not used.

The baud rate generator operates from the oscillator or external clock input and is capable of generating 18 commonly used data communications baud rates ranging from 50 to 38.4K baud. Thirteen of these are available simultaneously for use by the receiver and transmitter. Eight are fixed, and one of two sets of five can be selected by programming ACR[7]. The clock outputs from the BRG are at 16X the actual baud rate. The counter/timer can be used as a timer to produce a 16X clock for any other baud rate by counting down the crystal clock or an external clock. The clock selectors allow the independent selection by the receiver and transmitter of any of these baud rates or an external timing signal.

#### Counter/Timer (C/T)

The C/T operation is programmed by ACR[6:4]. One of eight timing sources can be used as the input to the C/T. The output of the C/T is available to the clock selectors and can be programmed by ACR[2:0] to be output on the MPO pin.

In the timer mode, the C/T generates a square wave whose period is twice the number of clock periods loaded into the C/T upper and lower registers. The counter ready bit in the ISR is set once each cycle of the square wave. If the value in CTUR or CTLR is changed, the current half-period will not be affected, but subsequent half-periods will be affected. In this mode the C/T runs continuously and does not recognize the stop counter command (the command only resets the counter ready bit in the ISR). Receipt of a start C/T command causes the counter to terminate the current timing cycle and to begin a new cycle using the values in CTUR and CTLR.

In the counter mode, the C/T counts down the number of pulses loaded into CTUR and CTLR. Counting begins upon receipt of a start C/T command. Upon reaching terminal count, the counter ready bit in the ISR is set. The counter continues counting past the terminal count until stopped by the CPU. If MPO is programmed to be the output of the C/T, the output remains high until terminal count is reached, at which time it goes low. The output returns to the high state and the counter ready bit is cleared when the counter is stopped by a stop counter command. the CPU may change the

values of CTUR and CTLR at any time, but the new count becomes effective only on the next start counter command following a stop counter command. If new values have not been loaded, the previous count values are preserved and used for the next count cycle.

In the counter mode, the current value of the upper and lower eight bits of the counter may be read by the CPU. It is recommended that the counter be stopped when reading to prevent potential problems which may occur if a carry from the lower eight bits to the upper eight bits occurs between the times that both halves of the counter are read. However, a subsequent start counter command causes the counter to begin a new count cycle using the values in CTUR and CTLR. See further description in CTUR/CTLR section.

#### **Receiver and Transmitter**

The UART is a full-duplex asynchronous receiver/transmitter. The operating frequency for the receiver and transmitter can be selected independently from the baud rate generator, the counter/timer, or from an external input. Registers associated with the communications channel are: the mode registers (MR1 and MR2), the clock select register (CSR), the command register (CR), the status register (SR), the transmit holding register (THR), and the receive holding register (RHR).

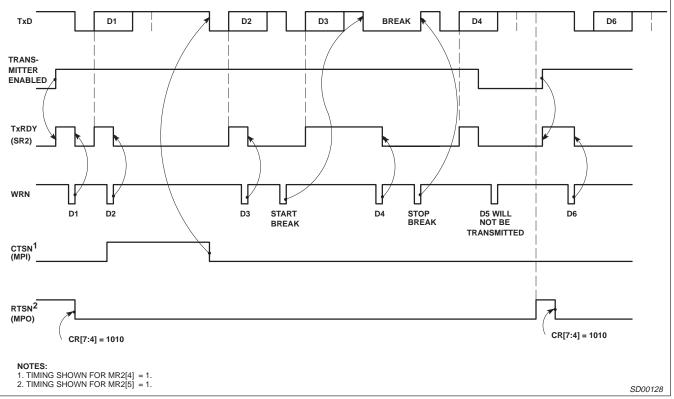

#### Transmitter

The transmitter accepts parallel data from the CPU and converts it to a serial bit stream on the TxD output pin. It automatically sends a start bit followed by the programmed number of data bits, an optional parity bit, and the programmed number of stop bits. The least significant bit is sent first. Following the transmission of the stop bits, if a new character is not available in the THR, the TxD output remains high and the TxEMT bit in the SR will be set to 1. Transmission resumes and the TxEMT bit is cleared when the CPU loads a new character in the THR. In the 16X clock mode, this also resynchronizes the internal 1X transmitter clock so that transmission of the new character begins with minimum delay.

The transmitter can be forced to send a break (continuous low condition) by issuing a start break command via the CR. The break is terminated by a stop break command.

If the transmitter is disabled, it continues operating until the character currently being transmitted and the character in the THR, if any, are completely sent out. Characters cannot be loaded in the THR while the transmitter is disabled.

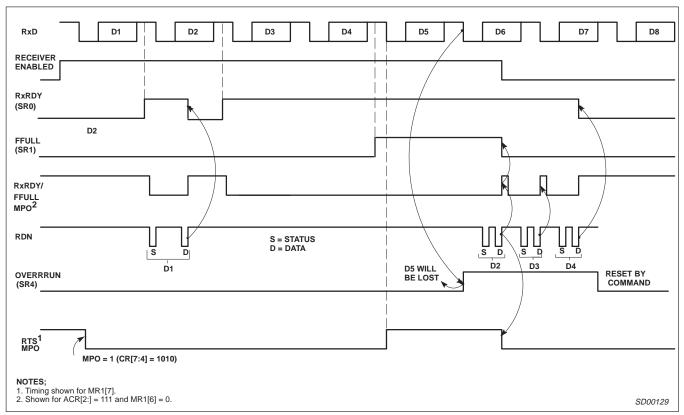

#### Receiver

The receiver accepts serial data on the RxD pin, converts the serial input to parallel format, checks for start bit, stop bit, parity bit (if any), or break condition, and presents the assembled character to the CPU. The receiver looks for a high-to-low (mark-to-space) transition of the start bit on the RxD input pin. If a transition is detected, the state of the RxD pin is sampled again each 16X clock for 7-1/2 clocks (16X clock mode) or at the next rising edge of the bit time clock (1X clock mode). If RxD is sampled high, the start bit is invalid and the search for a valid start bit begins again. If RxD is still low, a valid start bit is assumed and the receiver continues to sample the input at one bit time intervals at the theoretical center of the bit, until the proper number of data bits and the parity bit (if any) have been assembled, and one sop bit has been detected. The data is then transferred to the RHR and the RxRDY bit in the SR is set to a 1. If the character length is less than eight bits, the most significant unused bits in the RHR are set to zero.

After the stop bit is detected, the receiver will immediately look for the next start bit. However, if a non-zero character was received without a stop bit (i.e. framing error) and RxD remains low for

one-half of the bit period after the stop bit was sampled, then the receiver operates as if a new start bit transition had been detected at that point(one-half bit time after the stop bit was sampled).

The parity error, framing error and overrun error (if any) are strobed into the SR at the received character boundary, before the RxRDY status bit is set.

If a break condition is detected (RxD is low for the entire character including the stop bit), only one character consisting of all zeros will be loaded in the FIFO and the received SR break bit is set to 1. The RxD input must return to high for two (2) clock edges of the X1 crystal clock for the receiver to recognize the end of the break condition and begin the search for a start bit. This will usually require a high time of one X1 clock period or 3 X1 edges since the clock of the controller is not synchronous to the X1 clock.

#### **RECEIVER FIFO**

The RHR consists of a first-in-first-out (FIFO) queue with a capacity of three characters. Data is loaded from the receive shift register into the top-most empty position of the FIFO. The RxRDY bit in the status register (SR) is set whenever one or more characters are available to be read, and a FFULL status bit is set if all three queue positions are filled with data. Either of these bits can be selected to cause an interrupt. A read of the RHR outputs the data at the top of the FIFO. After the read cycle, the data FIFO and its associated status bits are 'popped' thus emptying a FIFO position for new data.

#### **Receiver Status Bits**

In addition to the data word, three status bits (parity error, framing error, and received break) are appended to each data character in the FIFO. Status can be provided in two ways, as programmed by the error mode control bit in mode register 1. In the character mode, status is provided on a character-by-character basis: the status applies only to the character at the top of the FIFO. In the block mode, the status provided in the SR for these three bits is the logical-OR of the status for all characters coming to the top of the FIFO since the last reset error command was issued. In either mode, reading the SR does not affect the FIFO. The FIFO is 'popped' only when the RHR is read. Therefore, the SR should be read prior to reading the corresponding data character.

The receiver can control the deactivation of RTS. If programmed to operate in this mode, the RTSN output will be negated when a valid start bit was received and the FIFO is full. When a FIFO position becomes available, the RTSN output will be re-asserted automatically. This feature can be used to prevent an overrun, in the receiver, by connecting the RTSN output to the CTSN input of the transmitting device.

#### **Receiver Reset and Disable**

Receiver disable stops the receiver immediately – data being assembled if the receiver shift register is lost. Data and status in the FIFO is preserved and may be read. A re-enable of the receiver after a disable will cause the receiver to begin assembling characters at the next start bit detected. A receiver reset will discard the present shift register data, reset the receiver ready bit (RxRDY), clear the status of the byte at the top of the FIFO and re-align the FIFO read/write pointers. This has the appearance of "clearing or flushing" the receiver FIFO. In fact, the FIFO is NEVER cleared! The data in the FIFO remains valid until overwritten by another received character. Because of this, erroneous reading or extra reads of the receiver FIFO will miss-align the FIFO pointers and result in the reading of previously read data. A receiver reset will re-align the pointers.

Product data sheet

## SCC2691

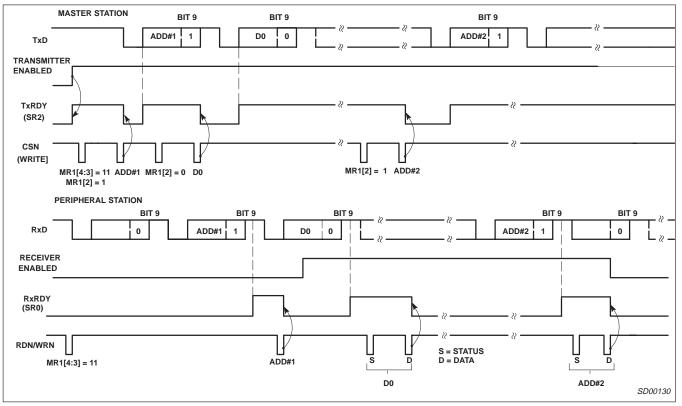

In addition to the normal transmitter and receiver operation described above, the UART incorporates a special mode which provides automatic wake-up of the receiver through address frame recognition for multi-processor communications. This mode is selected by programming bits MR1[4:3] to '11'.

In this mode of operation, a 'master' station transmits an address character followed by data characters for the addressed 'slave' station. The slave stations, whose receivers are normally disabled, examine the received data stream and 'wake-up' the CPU [by setting RxRDY) only upon receipt of an address character. The CPU compares the received address to its station address and enables the receiver if it wishes to receive the subsequent data characters. Upon receipt of another address character, the CPU may disable the receiver to initiate the process again.

A transmitted character consists of a start bit, the programmed number of data bits, an address/data (A/D) bit, and the programmed number of stop bits. The polarity of the transmitted A/D bit is selected by the CPU by programming bit MR1[2]. MR1[2] = 0 transmits a zero in the A/D bit position which identifies the corresponding data bits as data, while MR1[2] = 1 transmits a one in the A/D bit position which identifies the corresponding data bits as an address. The CPU should program the mode register prior to loading the corresponding data bits in the THR.

While in this mode, the receiver continuously looks at the received data stream, whether it is enabled or disabled. If disabled, it sets the RxRDY status bit and loads the character in the RHR FIFO if the received A/D bit is a one, but discards the received character if the received A/D bit is a zero. If enabled, all received characters are then transferred to the CPU via the RHR. In either case, the data bits are loaded in the data FIFO while the A/D bit is loaded in the status FIFO position normally used for parity error (SR[5]). Framing error, overrun error, and break detect operate normally whether or not the receiver is enabled.

#### **MULTI-PURPOSE INPUT PIN**

The MPI pin can be programmed as an input to one of several UART circuits. The function of the pin is selected by programming the appropriate control register (MR2[4]), ACR[6:4], CSR [7:4, 3:0]}. Only one of the functions may be selected at any given time. If CTS or GPI is selected, a change of state detector provided with the pin is activated. A high-to-low or low-to-high transition of the inputs lasting longer than  $25-50\mu$ s sets the MPI change-of-state bit in the interrupt status register. The bit is cleared via a command. The change-of-state can be programmed to generate an interrupt to the CPU by setting the corresponding bit in the interrupt mask register.

The input port pulse detection circuitry uses a 38.4kHz sampling clock derived from one of the baud rate generator taps. This produces a sampling period of slightly more than 25µs (assuming a 3.6864MHz oscillator input). The detection circuitry, in order to guarantee that a true change in level has occurred, requires two successive samples at the new logic level be observed. As a consequence, the minimum duration of the signal change is 25µs if the transition occurs coincident with the first sample pulse. The 50µs time refers to the condition where the change of state is just missed and the first change of state is not detected until after an additional 25µs. The MPI pin has a small pull-up device that will source 1 to 4 µA of current from  $V_{CC}$ . This pin does not require pull-up devices or  $V_{CC}$  connection if it is not used.

#### **MULTI-PURPOSE OUTPUT PIN**

This pin can be programmed to serve as a request-to-send output, the counter/timer output, the output for the 1X or 16X transmitter or receiver clocks, the TxRDY output or the RxRDY/FFULL output (see ACR[2:0] – MPO Output Select). Please note that this pin drives both high and low. HOWEVER when it is programmed to represent interrupt type functions (such as receiver ready, transmitter ready or counter/timer ready) it will be switched to an open drain configuration in which case an external pull-up device would be required.

#### REGISTERS

The operation of the UART is programmed by writing control words in the appropriate registers. Operational feedback is provided via status registers which can be read by the CPU. Addressing of the registers is as described in Table 1.

The contents of certain control registers are initialized to zero on reset (see RESET pin description). Care should be exercised if the contents of a register are changed during operation, since certain changes may cause operational problems. For example, changing the number of bits per character while the transmitter is active may cause the transmission of an incorrect character. The contents of the MR, the CSR, and the ACR should only be changed while the receiver and transmitter are disabled, and certain changes to the ACR should only be made while the C/T is stopped. The bit formats of the UART are shown in Table 2.

#### MR1 – Mode Register 1

MR1 is accessed when the MR pointer points to MR1. The pointer is set to MR1 by RESET or by a set pointer command applied via the CR. After reading or writing MR1, the pointers are set at MR2.

#### MR1[7] – Receiver Request-to-Send Control

The bit controls the deactivation of the RTSN output (MPO) by the receiver. This output is normally asserted and negated by commands applied via the command register. MR1[7] = 1 causes RTSN to be automatically negated upon receipt of a valid start bit if the receiver FIFO is full. RTSN is reasserted when an empty FIFO position is available. This feature can be used to prevent overrun in the receiver by using the RTSN output signal to control the CTS input of the transmitting device.

#### MR1[6] – Receiver Interrupt Select

This bit selects either the receiver ready status (RxRDY) or the FIFO full status (FFULL) to be used for CPU interrupts.

#### MR1[5] - Error Mode Select

This bit selects the operating mode of the three FIFOed status bits (FE, PE, received break). In the character mode, status is provided on a character-by-character basis. The status applies only to the character at the top of the FIFO. In the block mode, the status provided in the SR for these bits is the accumulation (logical-OR) of the status for all characters coming to the top of the FIFO since the last reset error command was issued.

#### MR1[4:3] - Parity Mode Select

If with parity or force parity is selected, a parity bit is added to the transmitted character and the receiver performs a parity check on incoming data. MR![4:3] = 11 selects the channel to operate in the special wake-up mode.

#### MR1[2] – Parity Type Select

This bit selects the parity type (odd or even) if the with parity mode is programmed by MR1[4:3], and the polarity of the forced parity bit if the force parity mode is programmed. It has no effect if the no

SCC2691

parity mode is programmed. In the special wake-up mode, it selects the polarity of the transmitted A/D bit.

#### MR1[1:0] - Bits Per Character Select

This field selects the number of data bits per character to be transmitted and received. The character length does not include the start, parity, and stop bits.

#### MR2 – Mode Register 2

MR2 is accessed when the channel MR pointer points to MR2, which occurs after any access to MR1. Accesses to MR2 do not change the pointer.

#### MR2[7:6] - Mode Select

The UART can operate in one of four modes. MR2[7:6] = 00 is the normal mode, with the transmitter and receiver operating independently. MR2[7:6] = 01 places the channel in the automatic echo mode, which automatically re-transmits the received data. The following conditions are true while in automatic echo mode:

- Received data is re-clocked and retransmitted on the TxD output.

- 2. The receive clock is used for the transmitter.

- 3. The receiver must be enabled, but the transmitter need not be enabled.

- 4. The TxRDY and TxEMT status bits are inactive.

- 5. The received parity is checked, but is not regenerated for transmission, i.e., transmitted parity bit is as received.

- 6. Character framing is checked, but the stop bits are retransmitted as received.

- 7. A received break is echoed as received until the next valid start bit is detected.

- CPU-to-receiver communication continues normally, but the CPU-to-transmitter link is disabled.

Two diagnostic modes can also be selected. MR2[7:6] = 10 selects local loopback mode. In this mode:

- 1. The transmitter output is internally connected to the receiver input.

- 2. The transmit clock is used for the receiver.

- 3. The TxD output is held high.

- 4. The RxD input is ignored.

- 5. The transmitter must be enabled, but the receiver need not be enabled.

- CPU to transmitter and receiver communications continue normally.

The second diagnostic mode is the remote loopback mode, selected by MR2[7:6] = 11. In this mode:

- 1. Received data is re-clocked and retransmitted on the TxD output.

- 2. The receive clock is used for the transmitter.

- 3. Received data is not sent to the local CPU, and the error status conditions are inactive.

- 4. The received parity is not checked and is not regenerated for transmission, i.e., the transmitted parity bit is as received.

- 5. The receiver must be enabled, but the transmitter need not be enabled.

- 6. Character framing is not checked, and the stop bits are retransmitted as received.

- 7. A received break is echoed as received until the next valid start bit is detected.

When switching in and out of the various modes, the selected mode is activated immediately upon mode selection, even if this occurs in the middle of a received or transmitted character. Likewise, if a mode is deselected, the device will switch out of the mode immediately. An exception to this is switching out of auto-echo or remote loopback modes; if the deselection occurs just after the receiver has sampled the stop bit (indicated in auto-echo by assertion o fRxRDY), and the transmitter is enabled, the transmitter will remain in auto-echo mode until one full stop bit has been retransmitted.

#### MR2[5] - Transmitter Request-to-Send Control

CAUTION: When the transmitter controls the OP pin (usually used for the RTSN signal) the meaning of the pin is not RTSN at all! Rather, it signals that the transmitter has finished the transmission (i.e., end of block).

This bit allows deactivation of the RTSN output by the transmitter. This output is manually asserted and negated by the appropriate commands issued via the command register. MR2[5] set to 1 caused the RTSN to be reset automatically one bit time after the character(s) in the transmit shift register and in the THR (if any) are completely transmitted (including the programmed number of stop bits) if a previously issued transmitter disable is pending. This feature can be used to automatically terminate the transmission as follows:

- 1. Program the auto-reset mode: MR2[5]=1

- 2. Enable transmitter, if not already enabled

- 3. Assert RTSN via command

- 4. Send message

- After the last character of the message is loaded to the THR, disable the transmitter. (If the transmitter is underrun, a special case exists. See note below.)

- 6. The last character will be transmitted and the RTSN will be reset one bit time after the last stop bit is sent.

NOTE: The transmitter is in an underrun condition when both the TxRDY and the TxEMT bits are set. This condition also exists immediately after the transmitter is enabled from the disabled or reset state. When using the above procedure with the transmitter in the underrun condition, the issuing of the transmitter disable must be delayed from the loading of a single, or last, character until the TxRDY becomes active again after the character is loaded.

#### MR2[4] – Clear-to-Send Control

The sate of this bit determines if the CTSN input (MPI) controls the operation of the transmitter. If this bit is 0, CTSN has no effect on the transmitter. If this bit is a 1, the transmitter checks the sate of CTSN each time it is ready to send a character. If it is asserted (low), the character is transmitted. If it is negated (high), the TxD output remains in the marking state and the transmission is delayed until CTSN goes low. Changes in CTSN while a character is being transmitted do not affect the transmission of that character. This feature can be used to prevent overrun of a remote receiver.

#### MR2[3:0] - Stop Bit Length Select

This field programs the length of the stop bit appended to the transmitted character. Stop bit lengths of 9/16 to 1 and 1–9/16 to 2 bits, in increments of 1/16 bit, can be programmed for character lengths of 6, 7, and 8 bits. For a character length of 5 bits, 1–1/16 to 2 stop bits can be programmed in increments of 1/16 bit. In all cases, the receiver only checks for a mark condition at the center of the first stop bit position (one bit time after the last data bit, or after the parity bit if parity is enabled). If an external 1X clock is used for the transmitter, MR2[3] = 0 selects one stop bit and MR2[3] = 1 selects two stop bits to be transmitted.

| Table 2. Reg                                                                              | gister Bit Forr                         | nats                                     |                         |                                                                                |                                                                                                                     |                            |                                          |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|-------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------|--|

| Bit 7                                                                                     | Bit 6                                   | Bit 5                                    | Bit 4                   | Bit 3                                                                          | Bit 2                                                                                                               | Bit 1                      | Bit 0                                    |  |

| MR1 (Mode Reg                                                                             | gister 1)                               |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| RxRTS Control                                                                             | RxINT Select                            | Error Mode*                              | Parity                  | Mode                                                                           | Parity Type                                                                                                         | Bits per (                 | Character                                |  |

| 0 = no<br>1 = yes                                                                         | 0 = RxRDY<br>1 = FFULL                  | 0 = Char<br>1 = Block                    | 01 = Force<br>10 = No p | 00 = With parity0 = Even01 = Force parity1 = Odd10 = No parity1 = Special mode |                                                                                                                     |                            | 00 = 5<br>01 = 6<br>10 = 7<br>11 = 8     |  |

| NOTE:<br>*In block error mod                                                              | de, block error con                     | ditions must be c                        | eared by using th       | e error reset comm                                                             | nand (command 4                                                                                                     | x) or a receiver r         | eset.                                    |  |

| MR2 (Mode Reg                                                                             | gister 2)                               |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| Channe                                                                                    | l Mode                                  | TxRTS<br>Control                         | CTS Enable<br>Tx        | e Stop Bit Length*                                                             |                                                                                                                     |                            |                                          |  |

| 00 = Norm<br>01 = Auto e<br>10 = Local<br>11 = Remot                                      | echo<br>loop<br>re loop                 | 0 = No<br>1 = Yes                        | 0 = No<br>1 = Yes       | $0 = 0.563 \\ 1 = 0.625 \\ 2 = 0.688 \\ 3 = 0.750 \\ $                         | 5 = 0.875<br>6 = 0.938                                                                                              | 9 = 1.625 D<br>A = 1.688 E | = 1.813<br>= 1.875<br>= 1.938<br>= 2.000 |  |

| NOTE: *Add 0.5 t                                                                          |                                         | r 0–7 if channel is                      | programmed for          | 5 bits/character.                                                              |                                                                                                                     |                            |                                          |  |

| CSR (Clock Sel                                                                            | Receiver Clo                            | ock Select                               |                         |                                                                                | Transmitter C                                                                                                       | lock Select                |                                          |  |

|                                                                                           | See 7                                   |                                          |                         |                                                                                | See 7                                                                                                               |                            |                                          |  |

| See Table 6 for BR and SCC2698B" P                                                        | G Test frequencies                      | in this data sheet                       |                         |                                                                                |                                                                                                                     |                            | 692, SCC68681                            |  |

| CR (Command                                                                               | Register)                               |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

|                                                                                           | Miscellaneous                           |                                          |                         | Disable Tx                                                                     | Enable Tx                                                                                                           | Disable Rx                 | Enable Rx                                |  |

|                                                                                           | See 1                                   | ēxt                                      |                         | 0 = No<br>1 = Yes                                                              | 0 = No<br>1 = Yes                                                                                                   | 0 = No<br>1 = Yes          | 0 = No<br>1 = Yes                        |  |

| NOTE:<br>Access to the misc                                                               | cellaneous comma                        | nds should be se                         | parated by 3 X1 c       | lock edges. A disa                                                             | abled transmitter c                                                                                                 | annot be loaded            |                                          |  |

| SR (Channel St                                                                            | atus Register)                          |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| Received Break                                                                            | Framing<br>Error                        | Parity<br>Error                          | Overrun<br>Error        | TxEMT                                                                          | TxRDY                                                                                                               | FFULL                      | RxRDY                                    |  |

| 0 = No<br>1 = Yes                                                                         | 0 = No<br>1 = Yes<br>*                  | 0 = No<br>1 = Yes<br>*                   | 0 = No<br>1 = Yes       | 0 = No<br>1 = Yes                                                              | 0 = No<br>1 = Yes                                                                                                   | 0 = No<br>1 = Yes          | 0 = No<br>1 = Yes                        |  |

| NOTE:<br>*These status bits<br>from the top of the<br>the corresponding<br>command (comma | FIFO together with<br>data character is | h bits [4;0]. These<br>read from the FIF | bits are cleared by     | a reset error statu                                                            | s command. In cha                                                                                                   | aracter mode the           | / are reset when                         |  |

| ACR (Auxiliary                                                                            | Control Regist                          | er)                                      |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| BRG Set<br>Select                                                                         |                                         | Counter/Timer                            | )                       | Power-Down<br>Mode                                                             |                                                                                                                     | MPO Pin<br>Function Select |                                          |  |

| 0 = Set 1<br>1 = Set 2                                                                    | See Text                                |                                          |                         | 0 = On<br>PWRDN Active<br>1 = Off<br>Normal                                    | VRDN Active         001 = C/TO         101 = RxC (16X)           1 = Off         010 = TxC (1X)         110 = TxRDY |                            |                                          |  |

| ISR (Interrupt S                                                                          | tatus Register)                         |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| MPI Pin<br>Change                                                                         | MPI Pin<br>Current State                | Not used                                 | Counter<br>Ready        | Delta<br>Break                                                                 | RxRDY/<br>FFULL                                                                                                     | TxEMT                      | TxRDY                                    |  |

| 0 = No<br>1 = Yes                                                                         | 0 = Low<br>1 = High                     |                                          | 0 = No<br>1 = Yes       | 0 = No<br>1 = Yes                                                              | 0 = No<br>1 = Yes                                                                                                   | 0 = No<br>1 = Yes          | 0 = No<br>1 = Yes                        |  |

| IMR (Interrupt N                                                                          | Mask Resister)                          |                                          |                         |                                                                                |                                                                                                                     |                            |                                          |  |

| MPI Change<br>Interrupt                                                                   | MPI Level<br>Interrupt                  | Not used                                 | Counter<br>Ready Int    | Delta Break<br>Interrupt                                                       | RxRDY/FFULL<br>Interrupt                                                                                            | TxEMT<br>Interrupt         | TxRDY<br>Interrupt                       |  |

| 0 = Off<br>1 = On                                                                         | 0 = Off<br>1 = On                       |                                          | 0 = Off<br>1 = On       | 0 = Off<br>1 = On                                                              | 0 = Off<br>1 = On                                                                                                   | 0 = Off<br>1 = On          | 0 = Off<br>1 = On                        |  |

| CTUR (Counter/Timer Upper Register) |         |         |         |         |         |        |        |

|-------------------------------------|---------|---------|---------|---------|---------|--------|--------|

| C/T[15]                             | C/T[14] | C/T[13] | C/T[12] | C/T[11] | C/T[10] | C/T[9] | C/T[8] |

|                                     |         |         |         |         |         |        |        |

| Bit 7                               | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1  | Bit 0  |

| CTLR (Counter/Timer Lower Register) |         |         |         |         |         |        |        |

| C/T[7]                              | C/T[6]  | C/T[5]  | C/T[4]  | C/T[3]  | C/T[2]  | C/T[1] | C/T[0] |

|                                     |         |         |         |         |         |        |        |

#### Table 2. Register Bit Formats (Continued)

CSR – Clock Select Register (see Table 6. also) Table 3. **Baud Rate Selection**

| CSR[3:0]/ [7:4]       | ACR[7] = 0               | ACR[7] = 1               |

|-----------------------|--------------------------|--------------------------|

| 0000                  | 50                       | 75                       |

| 0001                  | 110                      | 110                      |

| 0010                  | 134.5                    | 134.5                    |

| 0011                  | 200                      | 150                      |

| 0100                  | 300                      | 300                      |

| 0101                  | 600                      | 600                      |

| 0110                  | 1,200                    | 1,200                    |

| 0111                  | 1,050                    | 2,000                    |

| 1000                  | 2,400                    | 2,400                    |

| 1001                  | 4,800                    | 4,800                    |

| 1010                  | 7,200                    | 1,800                    |

| 1011                  | 9,600                    | 9,600                    |