## 48 V smart high-side MOSFET gate driver with SPI

### **Features**

- Extended supply voltage range: 20 70 V

- Two independent high-side gate driver outputs

- 1 A pull down, 0.3 A pull up for fast switch off/on

- Device control, configuration and diagnostic via SPI

- Low supply current in sleep mode  $I_{BAT_Q} < 5 \mu A$

- Supports back-to-back MOSFET topologies (common drain and common source)

- One bidirectional high or low-side analog current sense interface with configurable gain

- Configurable overcurrent/short circuit protection

- Gate undervoltage lock-out

- Safe state mode (both channels OFF) activated by direct input pin

- Ground loss detection

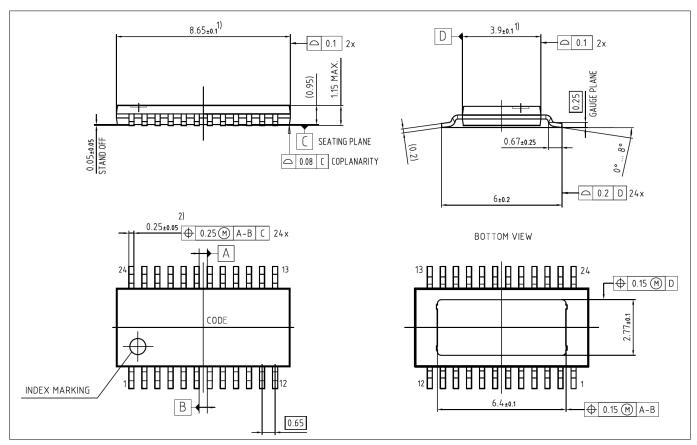

| Package     | Marking    |

|-------------|------------|

| PG-TSDSO-24 | 2ED4820-EM |

# **Potential applications**

- 48 V battery protection switch

- 48 V input protection switch for DCDC converters, motor control unit etc.

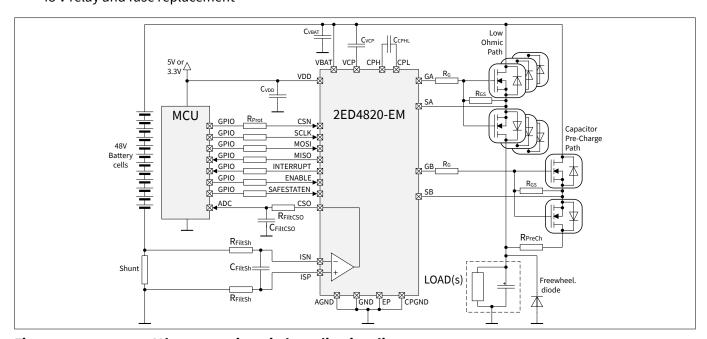

- 48 V relay and fuse replacement

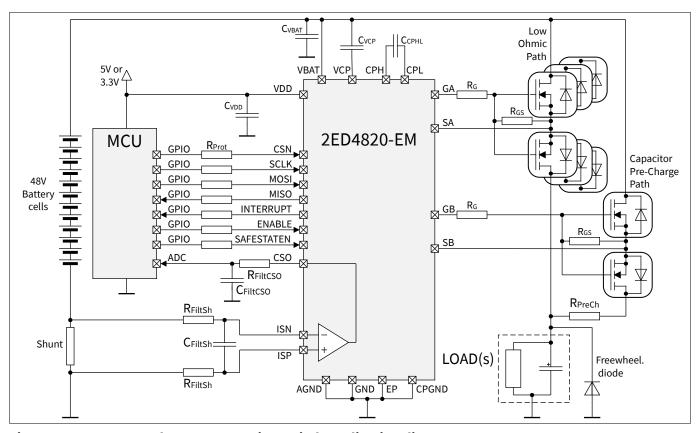

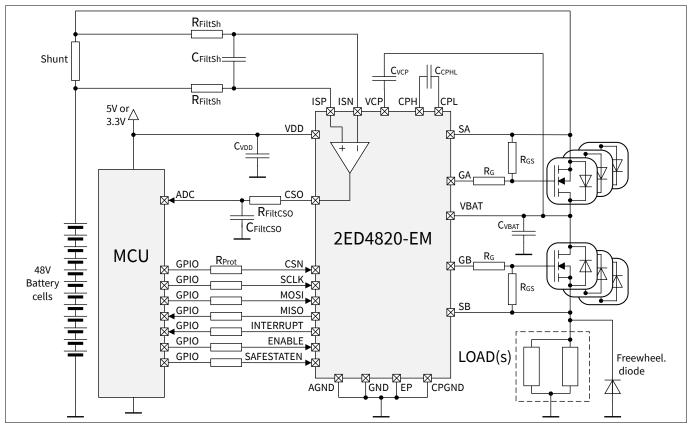

Figure 1 48 V battery main switch application diagram

### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100 grade 1.

# 48 V smart high-side MOSFET gate driver with SPI

**Description**

# **Description**

2ED4820-EM is a gate driver designed for high current 48 V automotive applications, with powerful gate outputs to drive many MOSFETs in parallel in order to minimize the conduction losses. It supports the back-to-back configuration, both common source and common drain structures, thanks to its two gate outputs.

In common source configuration, one gate output can be used to pre-charge highly capacitive loads.

2ED4820-EM generates the supply for the gate outputs based on an integrated one-stage charge pump with external pump and tank capacitors.

2ED4820-EM comes with an SPI interface, for easy configuration, diagnosis and control.

Several protection mechanisms are provided:

- Supply under- and overvoltage detection with configurable restart timer

- Charge pump undervoltage detection

- Gate to source undervoltage detection with immediate lock-out to prevent linear mode conduction of the **MOSFETs**

- Configurable drain to source overvoltage detection, which can also be deactivated

- Configurable overcurrent protection based on an analog current sense amplifier compatible for high-side or low-side shunt topologies

- Internal overtemperature warning and protection

An interrupt pin informs the MCU whenever one of these protections is triggered. Status registers can then be read by the MCU to understand what was the trigger for the notification.

The output of the current sense amplifier can be monitored by the MCU to implement additional protections, such as wire overtemperature.

In addition, 2ED4820-EM enables to implement an open load detection mechanism, checking the source voltage of the MOSFETs with respect to ground in the OFF state.

### **Table of contents**

# **Table of contents**

|       | Features                                           | 1  |

|-------|----------------------------------------------------|----|

|       | Potential applications                             | 1  |

|       | Product validation                                 | 1  |

|       | Description                                        | 2  |

|       | Table of contents                                  | 3  |

| 1     | Block diagram                                      | 5  |

| 2     | Pin configuration                                  | 6  |

| 3     | General product characteristic                     | 8  |

| 3.1   | Absolute maximum ratings                           |    |

| 3.2   | Functional range                                   |    |

| 3.3   | Thermal resistance                                 |    |

| 4     | General product description                        | 11 |

| 4.1   | Power supply                                       |    |

| 4.2   | Operation mode                                     |    |

| 4.2.1 | Normal mode                                        |    |

| 4.2.2 | Sleep mode                                         |    |

| 4.2.3 | Safe state mode                                    |    |

| 4.2.4 | Reset behavior                                     |    |

| 4.3   | Charge pump                                        |    |

| 4.4   | Electrical characteristics: supply                 |    |

| 4.5   | Electrical characteristics: digital IOs            | 13 |

| 4.6   | Electrical characteristics: charge pump            | 14 |

| 5     | High-side gate driver                              | 16 |

| 5.1   | Channel activation                                 | 16 |

| 5.2   | Channel deactivation                               | 17 |

| 5.3   | MOSFET driver output                               | 17 |

| 6     | Protection and monitoring                          | 19 |

| 6.1   | Monitorings                                        | 19 |

| 6.1.1 | Source voltage monitoring in OFF state             | 19 |

| 6.1.2 | Charge pump voltage monitoring                     | 19 |

| 6.1.3 | SPI address monitoring                             | 19 |

| 6.2   | Warnings                                           | 19 |

| 6.2.1 | Temperature warning                                | 19 |

| 6.2.2 | One time programmable (OTP) memory data corruption | 19 |

| 6.2.3 | Ground loss                                        | 19 |

| 6.3   | Failures detection                                 | 20 |

# 48 V smart high-side MOSFET gate driver with SPI

## **Table of contents**

|           | Disclaimer                                                                           | 45 |

|-----------|--------------------------------------------------------------------------------------|----|

|           | Revision history                                                                     | 44 |

| 10        | Package                                                                              | 43 |

| 9.3       | Bill of material                                                                     |    |

| 9.2       | Common drain with high-side current sense                                            |    |

| 9.1       | 48 V battery protection switch with low-side current sense and capacitive pre-charge |    |

| 9         | Application information                                                              |    |

|           | -                                                                                    |    |

| 8.1       | Control registers                                                                    |    |

| 8         | Register specification                                                               | 36 |

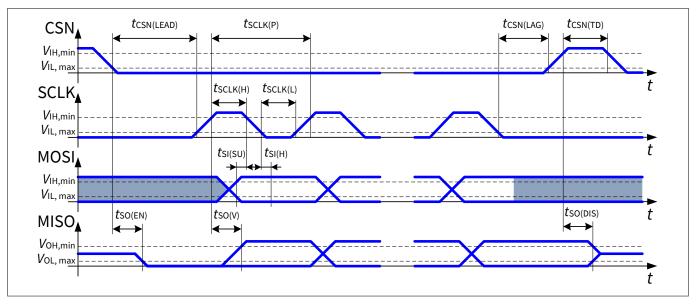

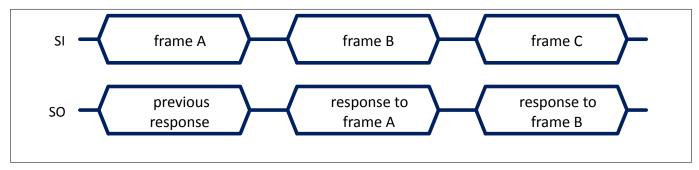

| 7.5       | SPI Protocol                                                                         |    |

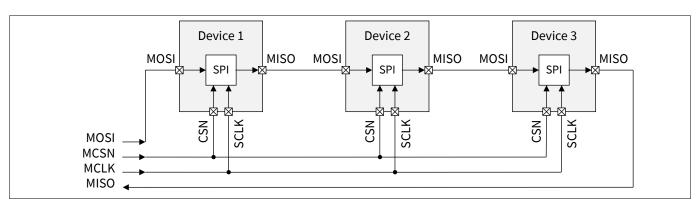

| 7.4       | Daisy Chain                                                                          |    |

| 7.3       | SPI: electrical characteristics: timings                                             | 34 |

| 7.2       | Communication end                                                                    | 34 |

| 7.1       | Communication start                                                                  | 33 |

| 7         | SPI                                                                                  | 33 |

| 6.5       | Electrical characteristics: protection and monitoring                                | 29 |

| 6.4       | INTERRUPT pin control                                                                |    |

| 6.3.3.9.5 | Electrical characteristics: current sense                                            |    |

| 6.3.3.9.4 | Overcurrent detection                                                                |    |

| 6.3.3.9.3 | Current sense output load                                                            |    |

| 6.3.3.9.2 | Current sense position                                                               |    |

| 6.3.3.9.1 | Gain configuration                                                                   |    |

| 6.3.3.9   | Current sense amplifier and overcurrent comparator                                   |    |

| 6.3.3.8   | Overtemperature                                                                      |    |

| 6.3.3.7   | SAFESTATEN activation                                                                |    |

| 6.3.3.6   | VCP undervoltage                                                                     |    |

| 6.3.3.5   | VDD undervoltage                                                                     |    |

| 6.3.3.4   | Channel cross-control                                                                |    |

| 6.3.3.3   | Gate-source undervoltage                                                             |    |

| 6.3.3.2   | Drain-source overvoltage                                                             |    |

| 6.3.3.1.2 | Filter time                                                                          |    |

| 6.3.3.1.1 | Blank time                                                                           |    |

| 6.3.3.1   | Blank time and filter time for failures detections                                   |    |

| 6.3.3     | Latching failures                                                                    |    |

| 6.3.2.2   | VBAT undervoltage                                                                    |    |

| 6.3.2.1   | VBAT overvoltage                                                                     |    |

| 6.3.2     | Non-latching failures                                                                | 20 |

| 6.3.1     | Failure notification and clearing                                                    |    |

|           |                                                                                      |    |

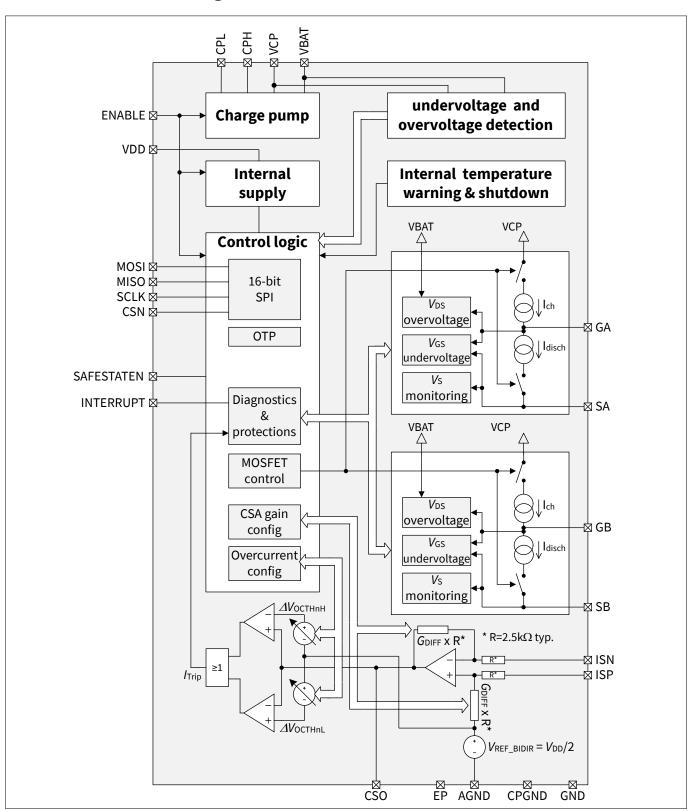

1 Block diagram

# 1 Block diagram

Figure 2 Block diagram

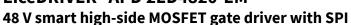

#### **Pin configuration** 2

2 Pin configuration

Figure 3 Pin assignment

Pin definitions and functions Table 1

| Pin No. | Function          | Symbol     | Comment                                      |

|---------|-------------------|------------|----------------------------------------------|

| 1       | μController       | SAFESTATEN | Watchdog connection for safe state mode      |

| 2       | μController       | INTERRUPT  | Interrupt signal output                      |

| 3       | SPI               | SCLK       | SPI clock input with internal pull-down      |

| 4       | SPI               | CSN        | Chip select not with internal pull-up        |

| 5       | SPI               | MOSI       | Master out slave in with internal pull-down  |

| 6       | SPI               | MISO       | Master in slave out                          |

| 7       | μController       | ENABLE     | Switch device ON/OFF with internal pull-down |

| 8       | Supply            | VDD        | Main supply                                  |

| 9       | μController       | CSO        | Current sense amplifier output               |

| 10      | V-Sensing         | ISN        | Negative input for shunt voltage             |

| 11      | V-Sensing         | ISP        | Positive input for shunt voltage             |

| 12      | Supply            | AGND       | Analog GND                                   |

| 13      | Supply            | GND        | Common usage ground                          |

| 14      | Gate connection   | GB         | Gate connection to channel B                 |

| 15      | Source connection | SB         | Source connection to channel B               |

| 16      |                   | NC         | Not connected                                |

| 17      | Source connection | SA         | Source connection to channel A               |

| 18      | Gate connection   | GA         | Gate connection to channel A                 |

| 19      | Supply            | CPGND      | Charge pump GND                              |

| 20      |                   | NC         | Not connected                                |

| 21      | ChargePump        | CPL        | Negative terminal of CP capacitor            |

# 2 Pin configuration

## Table 1 (continued) Pin definitions and functions

| Pin No. | Function   | Symbol | Comment                                                              |

|---------|------------|--------|----------------------------------------------------------------------|

| 22      | ChargePump | СРН    | Positive terminal of CP capacitor                                    |

| 23      | ChargePump | VCP    | Charge pump output / connection buffer capacitor                     |

| 24      | Supply     | VBAT   | 48 V supply                                                          |

|         |            | E.P.   | Exposed pad (for cooling purpose only, do not use as electrical GND) |

## 48 V smart high-side MOSFET gate driver with SPI

3 General product characteristic

#### **General product characteristic** 3

#### **Absolute maximum ratings** 3.1

Unless otherwise specified:  $T_J = -40$ °C to +150°C; all voltages are referenced to GND.

Table 2 **Absolute maximum ratings**

| Parameter                                                        | Symbol                                                                                                            |                       | Values |                      |   | Note or condition | P-      |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------|--------|----------------------|---|-------------------|---------|

|                                                                  |                                                                                                                   | Min.                  | Тур.   | Max.                 |   |                   | Number  |

| VBAT supply voltage                                              | $V_{BAT}$                                                                                                         | -0.3                  | _      | 105                  | ٧ | 1)                | PRQ-9   |

| Gate voltage with respect to Source                              | V <sub>Gx_S</sub>                                                                                                 | -0.3                  | _      | 18                   | V | 1)                | PRQ-11  |

| Gate voltage with respect to VBAT                                | V <sub>Gx_BAT</sub>                                                                                               | -80                   | -      | 18                   | V | 1)                | PRQ-10  |

| Gate voltage                                                     | $V_{Gx}$                                                                                                          | -80                   | _      | V <sub>CP</sub>      | ٧ | 1)                | PRQ-12  |

| Source voltage                                                   | $V_{Sx}$                                                                                                          | -90                   | _      | 105                  | ٧ | 1)                | PRQ-199 |

| Source voltage with respect to VBAT                              | V <sub>Sx_VBAT</sub>                                                                                              | -90                   | _      | 2                    | V | 1)                | PRQ-92  |

| VDD logic supply voltage                                         | $V_{DD}$                                                                                                          | -0.3                  | _      | 5.5                  | V | 1)                | PRQ-98  |

| Current sense                                                    |                                                                                                                   |                       |        |                      |   |                   |         |

| ISP and ISN voltage                                              | $V_{\rm ISP}, V_{\rm ISN}$                                                                                        | -6                    | _      | 105                  | V | 1)                | PRQ-13  |

| ISP and ISN voltage with respect to VBAT                         | V <sub>ISP_ISN_VBAT</sub>                                                                                         | -105                  | _      | 2                    | V | 1)                | PRQ-542 |

| ISP and ISN differential voltage                                 | V <sub>ISP_ISN_DIFF</sub>                                                                                         | -5                    | -      | 5                    | V | 1)                | PRQ-204 |

| CSO voltage                                                      | V <sub>CSO</sub>                                                                                                  | -0.3                  | _      | V <sub>DD</sub> +0.3 | V | 1)                | PRQ-97  |

| Logic                                                            | 1                                                                                                                 |                       |        |                      |   |                   |         |

| Logic input voltages (SCLK,<br>CSN, MOSI, SAFESTATEN,<br>ENABLE) | V <sub>SCLK</sub> , V <sub>CSN</sub> ,<br>V <sub>MOSI</sub> ,<br>V <sub>SAFESTATEN</sub> ,<br>V <sub>ENABLE</sub> | -0.3                  | -      | V <sub>DD</sub> +0.3 | V | 1)                | PRQ-94  |

| Logic output voltages<br>(MISO, INTERRUPT)                       | V <sub>MISO</sub> ,<br>V <sub>INTERRUPT</sub>                                                                     | -0.3                  | -      | V <sub>DD</sub> +0.3 | V | 1)                | PRQ-96  |

| Charge pump                                                      |                                                                                                                   |                       |        |                      |   |                   |         |

| Charge pump voltage (VCP)                                        | V <sub>CP</sub>                                                                                                   | -0.3                  | _      | 105                  | V | 1)                | PRQ-337 |

| Charge pump voltage (VCP) with respect to VBAT                   | V <sub>CP_VBAT</sub>                                                                                              | -0.3                  | _      | 18                   | V | 1)                | PRQ-400 |

| Charge pump voltage (CPL)                                        | V <sub>CPL</sub>                                                                                                  | -0.3                  | _      | $V_{BAT}$            | V | 1)                | PRQ-95  |

| Charge pump voltage (CPH)                                        | V <sub>CPH</sub>                                                                                                  | V <sub>BAT</sub> -0.3 | _      | V <sub>CP</sub> +0.3 | V | 1)                | PRQ-261 |

#### 3 General product characteristic

Table 2 (continued) Absolute maximum ratings

| Parameter                                                    | Symbol                |      | Values |      | Unit | Note or condition    | P-      |

|--------------------------------------------------------------|-----------------------|------|--------|------|------|----------------------|---------|

|                                                              |                       | Min. | Тур.   | Max. |      |                      | Number  |

| Charge pump ground and analog ground voltage                 | $V_{CPGND}, V_{AGND}$ | -0.3 | -      | 0.3  | V    | 1)                   | PRQ-205 |

| Temperature                                                  |                       |      |        |      |      |                      |         |

| Junction temperature                                         | TJ                    | -40  | -      | 150  | °C   | 1)                   | PRQ-17  |

| Storage temperature                                          | $T_{STG}$             | -55  | -      | 150  | °C   | 1)                   | PRQ-19  |

| ESD susceptibility                                           |                       |      |        |      |      |                      |         |

| ESD susceptibility at all pins (HBM)                         | V <sub>ESD_HBM1</sub> | -2   | _      | 2    | kV   | 1) 2) HBM            | PRQ-20  |

| ESD susceptibility of VBAT pin versus GND (HBM)              | V <sub>ESD_HBM2</sub> | -4   | -      | 4    | kV   | <sup>1) 2)</sup> HBM | PRQ-100 |

| ESD susceptibility at all pins (CDM)                         | V <sub>ESD_CDM</sub>  | -500 | -      | 500  | V    | 1) 3) CDM            | PRQ-401 |

| ESD susceptibility at corner pins (CDM) (pins 1, 12, 13, 24) | V <sub>ESD_CDM</sub>  | -750 | -      | 750  | V    | 1) 3) CDM            | PRQ-414 |

- 1) Not subject to production test, specified by design.

- 2) ESD susceptibility, human body model "HBM", according to AEC Q100-002

- 3) ESD susceptibility, charged device model "CDM", according to AEC Q100-011

# **3.2** Functional range

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_J = -40^{\circ}\text{C}$  to +150°C; all voltages are referenced to GND; positive current flowing into pin.

Table 3 Functional range

| Parameter                                      | Symbol                                    |      | Values |                   | Unit | Note or condition             | P-      |

|------------------------------------------------|-------------------------------------------|------|--------|-------------------|------|-------------------------------|---------|

|                                                |                                           | Min. | Тур.   | Max.              |      |                               | Number  |

| VBAT supply voltage range for normal operation | V <sub>BAT(NORM)</sub>                    | 24   | _      | 54                | V    | -                             | PRQ-101 |

| VBAT extended supply voltage range             | V <sub>BAT(EXT)</sub>                     | 20   | _      | 70                | V    | Parameter deviations possible | PRQ-102 |

| VBAT supply transients slew rate               | $dV_{BAT}/dt$                             | -10  | _      | 10                | V/µs | 1)                            | PRQ-397 |

| Logic supply voltage (VDD)                     | $V_{\mathrm{DD}}$                         | 3.0  | -      | 5.5               | V    | _                             | PRQ-105 |

| VDD logic supply transients slew rate          | $dV_{DD}/dt$                              | -10  | _      | 10                | V/µs | 1)                            | PRQ-398 |

| SPI logic input voltage                        | $V_{\rm SCLK}, V_{\rm CSN}, V_{\rm MOSI}$ | 0    | _      | $V_{\mathrm{DD}}$ | V    | -                             | PRQ-106 |

# infineon

#### 3 General product characteristic

Table 3 (continued) Functional range

| Parameter                            | Symbol                                           | Values |      |          | Unit | Note or condition | P-      |

|--------------------------------------|--------------------------------------------------|--------|------|----------|------|-------------------|---------|

|                                      |                                                  | Min.   | Тур. | Max.     |      |                   | Number  |

| Source voltage transients slew rate  | dV <sub>Sx</sub> /dt                             | -70    | _    | 70       | V/µs | 1)                | PRQ-399 |

| Logic input voltage                  | V <sub>SAFESTATEN</sub> ,<br>V <sub>ENABLE</sub> | 0      | _    | $V_{DD}$ | V    | -                 | PRQ-107 |

| CSO output current                   | I <sub>CSO</sub>                                 | -4     | _    | 0        | mA   | _                 | PRQ-355 |

| ISP, ISN input voltage               | $V_{\rm ISP}, V_{\rm ISN}$                       | -2     | _    | VBAT +   | V    | -                 | PRQ-508 |

| ISP, ISN common mode slew rate       | V <sub>SENSE_COMMO</sub>                         | -70    | _    | 70       | V/µs | 1)                | PRQ-491 |

| ISP, ISN differential mode slew rate | V <sub>SENSE_DIFFERE</sub>                       | -5     | _    | 5        | V/µs | 1)                | PRQ-492 |

| Junction temp                        | TJ                                               | -40    | _    | 150      | °C   | -                 | PRQ-18  |

<sup>1)</sup> Not subject to production test, specified by design.

#### 3.3 Thermal resistance

$T_{\rm J}$  = -40°C to +150°C.

Table 4 Thermal resistance

| Parameter                       | Symbol                      | Values |      | Unit | Note or condition | P-    |        |

|---------------------------------|-----------------------------|--------|------|------|-------------------|-------|--------|

|                                 |                             | Min.   | Тур. | Max. |                   |       | Number |

| Junction to case, TA = -40°C    | R <sub>thJC_cold</sub>      | -      | 4    | -    | K/W               | 1)    | PRQ-99 |

| Junction to case, TA = 85°C     | R <sub>thJC_hot</sub>       | _      | 5    | _    | K/W               | 1)    | PRQ-71 |

| Junction to ambient, TA = -40°C | R <sub>thJA_cold_2s2p</sub> | _      | 38   | _    | K/W               | 1) 2) | PRQ-72 |

| Junction to ambient, TA = 85°C  | R <sub>thJA_hot_2s2p</sub>  | _      | 31   | -    | K/W               | 1) 2) | PRQ-73 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified RthJA value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; the product (chip+package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 μm Cu, 2 × 35 μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer. The device is dissipating 1 W power.

## 48 V smart high-side MOSFET gate driver with SPI

4 General product description

#### **General product description** 4

#### 4.1 **Power supply**

The device is externally supplied by two pins: VDD and VBAT.

The gate driver requires multiple power supplies:

- VBAT supplies the charge pump and parts of the gate control block

- VDD supplies SPI interface, internal logic, protection functions as well as the current sense interface

- Internally generated charge pump voltage VCP supplies the gate control block,  $V_{DS}$  and  $V_{GS}$  detection blocks and current sense amplifier

#### **Operation mode** 4.2

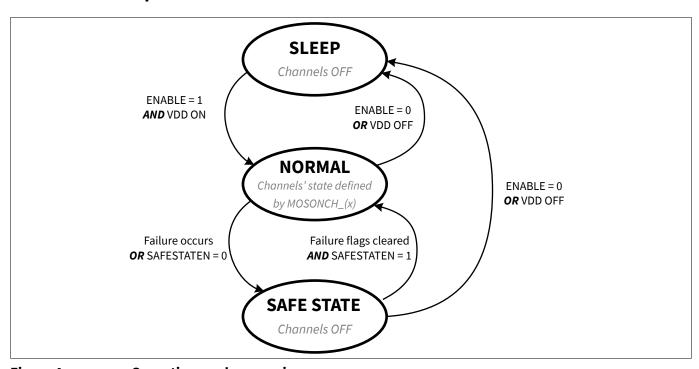

Figure 4 **Operation modes overview**

#### 4.2.1 Normal mode

The device enters normal mode after the SPI setup time  $t_{\rm SET-SPI}$ , if the microcontroller sets the pin ENABLE to

In normal mode, the MOSFET gate driver is enabled and can be configured through the SPI interface, provided that the voltages applied to VBAT and VDD are within the operating range.

#### 4.2.2 Sleep mode

The device enters sleep mode if the microcontroller sets the ENABLE pin to low.

In sleep mode, most of the internal circuitry is deactivated: the current consumption of VBAT and VDD is reduced respectively to  $I_{VBAT}$  o and  $I_{VDD}$  o.

#### 4.2.3 Safe state mode

The device will enter safe state if the pin SAFESTATEN is set to low.

In safe state the external MOSFETs of both channels are deactivated (e.g. switched off).

## 48 V smart high-side MOSFET gate driver with SPI

#### 4 General product description

To bring the device from safe state back to normal mode, the pin SAFESTATEN has to be set to high and the failure flag SAFESTATE must be cleared via SAFESTATE\_CL or FAIL\_RST\_0 together with FAIL\_RST\_1. If the microcontroller sets the ENABLE pin to low, the device enters the sleep mode.

#### **Reset behavior** 4.2.4

After the ENABLE pin is pulled high or after an undervoltage event at VDD, the logic content is reset. In both cases, the failure flag VDD UV is set to high to indicate that a reset was performed.

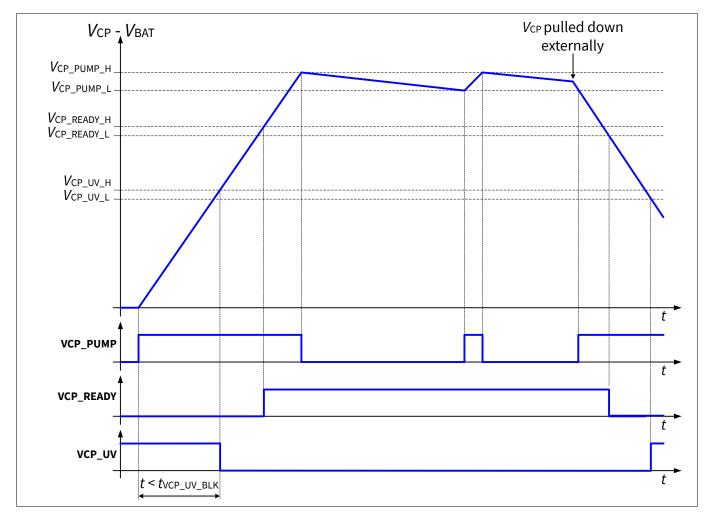

#### 4.3 **Charge pump**

The charge pump generates the positive supply for the gate control block, for the  $V_{GS}$  and  $V_{DS}$  comparators and for the current sense amplifier.

$V_{\text{CP-PUMP}}$  thresholds define hysteresis control of the charge pump output voltage by activating/deactivating charge pumping.

$V_{\text{CP}}$  READY thresholds flag the microcontroller that the charge pump output voltage is high enough to activate a channel.

$V_{CP-LIV}$  thresholds flag a charge pump output under voltage failure. In this case, turning on and protecting a channel cannot be ensured any more, so the channels are switched off.

Figure 5 Charge pump operating

The charge pump is ready to operate according the VCP\_PUMP signal when the following condition is fulfilled: ENABLE = high **AND** TSD = low **AND** VBAT\_OV = low **AND** VCP\_UV = low.

#### 48 V smart high-side MOSFET gate driver with SPI

#### 4 General product description

At the first activation of the charge pump, the VCP\_UV diagnostic will be blanked for the  $t_{\text{VCP}\_\text{UV}\_\text{BLK}}$  duration in order to operate a safe start.

Note that a triggering of VCP\_UV will therefore switch off the charge pump in a latched way.

The VCP\_PUMP signal is controlling the charge pump activity:

- When the charge pump is enabled it is pumping as long as the VCP\_PUMP signal is high

- As soon as the  $V_{CP}$   $V_{BAT}$  voltage gets above the  $V_{CP\_PUMP\_H}$  threshold, the VCP\\_PUMP signal is turned low and the charge pump stops pumping

- As soon as the  $V_{CP}$   $V_{BAT}$  voltage gets below the  $V_{CP\_PUMP\_L}$  threshold, the VCP\\_PUMP signal is turned high and the charge pump is pumping

The VCP\_READY bit is set to 1 once the  $V_{CP}$  -  $V_{BAT}$  voltage gets higher than the  $V_{CP}$  READY H threshold.

The VCP\_READY bit is set to 0 once the  $V_{CP}$  -  $V_{BAT}$  voltage gets lower than the  $V_{CP}$  READY L threshold.

The VCP\_UV bit is set to 0 once the  $V_{CP}$  -  $V_{BAT}$  voltage gets higher than the  $V_{CP}$  UV H threshold.

The VCP\_UV bit is set to 1 once the  $V_{CP}$  -  $V_{BAT}$  voltage gets lower than the  $V_{CP\_UV\_L}$  threshold.

VCP\_UV is blanked for a duration of  $t_{\text{VCP}\_UV\_BLK}$  after charge pump gets enabled (e.g.: after device enable or after clearing VCP\_UV failure flag).

### 4.4 Electrical characteristics: supply

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_J = -40$ °C to +150°C; CSO pin left open; all voltages are referenced to GND; positive current flowing into pin.

Table 5 Electrical characteristics: supply

| Parameter                          | Symbol                         |         | Values |      | Unit | Note or condition                                                                                      | P-       |

|------------------------------------|--------------------------------|---------|--------|------|------|--------------------------------------------------------------------------------------------------------|----------|

|                                    |                                | Min.    | Тур.   | Max. |      |                                                                                                        | Number   |

| Quiescent current consum           | ption, ENABL                   | E = LOW |        |      |      |                                                                                                        |          |

| VBAT supply quiescent current      | I <sub>BAT_Q</sub>             | -       | _      | 5    | μΑ   | 1) T <sub>A</sub> ≤ 85°C                                                                               | PRQ-112  |

| VDD logic supply quiescent current | $I_{\mathrm{DD}_{\mathbf{Q}}}$ | -       | _      | 7    | μΑ   | 1) T <sub>A</sub> ≤ 85°C                                                                               | PRQ-114  |

| Current consumption, ENA           | BLE = HIGH                     |         |        | 1    |      |                                                                                                        | <u>'</u> |

| VBAT supply current                | / <sub>BAT_SUP</sub>           | -       | -      | 10   | mA   | 1) MOSONCH_A = 1;<br>MOSONCH_B = 1;<br>$R_{GS} \ge 1 \text{ M}\Omega$ ;<br>$C_{VCP} = 2.2 \mu\text{F}$ | PRQ-27   |

| VDD logic supply current           | I <sub>DD_SUP</sub>            | -       | _      | 10   | mA   | CSA_HSS = 0;<br>CSA_COUTSEL = 0                                                                        | PRQ-118  |

| VDD logic supply current           | I <sub>DD_SUP</sub>            | -       | -      | 15   | mA   | 1) CSA_HSS = 1;<br>CSA_COUTSEL = 1                                                                     | PRQ-543  |

<sup>1)</sup> Not subject to production test, specified by characterization.

# 4.5 Electrical characteristics: digital IOs

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_J$  = -40°C to +150°C; all voltages are referenced to GND; positive current flowing into pin; pull-up resistors connected to VDD, pull-down resistors connected to GND.

# infineon

#### 4 General product description

Table 6 Electrical characteristics: digital IOs

| Parameter                        | Symbol V                  |                       | Values                | Values   |    | Note or condition       | P-      |

|----------------------------------|---------------------------|-----------------------|-----------------------|----------|----|-------------------------|---------|

|                                  |                           | Min.                  | Тур.                  | Max.     |    |                         | Number  |

| Logic input voltage              | •                         |                       |                       |          | •  |                         |         |

| Logic high input voltage         | V <sub>IH</sub>           | 0.7*V <sub>DD</sub>   | _                     | $V_{DD}$ | V  | -                       | PRQ-30  |

| Logic low input voltage          | $V_{IL}$                  | 0                     | _                     | 0.7      | ٧  | _                       | PRQ-31  |

| Logic input threshold hysteresis | $V_{IHY}$                 | 100                   | -                     | -        | mV | -                       | PRQ-32  |

| Logic output voltage             |                           |                       |                       |          |    |                         |         |

| Logic high output voltage level  | V <sub>OH</sub>           | V <sub>DD</sub> - 0.4 | V <sub>DD</sub> - 0.2 | $V_{DD}$ | V  | $I_0 = -1.6 \text{ mA}$ | PRQ-415 |

| Logic low output voltage level   | V <sub>OL</sub>           | 0                     | 0.2                   | 0.4      | V  | I <sub>O</sub> = 1.6 mA | PRQ-416 |

| Pull-up / -down resistors        |                           | •                     |                       |          | '  |                         |         |

| ENABLE pull-down resistor        | R <sub>PD_ENABLE</sub>    | 30                    | 40                    | 50       | kΩ | -                       | PRQ-126 |

| SCLK pull-down resistor          | R <sub>PD_SCLK</sub>      | 30                    | 40                    | 50       | kΩ | -                       | PRQ-410 |

| SAFESTATEN pull-down resistor    | R <sub>PD_SAFESTATE</sub> | 30                    | 40                    | 50       | kΩ | -                       | PRQ-409 |

| MOSI pull-down resistor          | R <sub>PD_MOSI</sub>      | 30                    | 40                    | 50       | kΩ | -                       | PRQ-411 |

| INTERRUPT pull-down resistor     | R <sub>PD_INTERRUPT</sub> | 30                    | 40                    | 50       | kΩ | -                       | PRQ-479 |

| CSN pull-up resistor             | R <sub>PU_CSN</sub>       | 30                    | 40                    | 50       | kΩ | _                       | PRQ-412 |

| SPI interface setup time         |                           | •                     | •                     | •        | •  |                         |         |

| SPI interface setup time         | t <sub>SET_SPI</sub>      | _                     | _                     | 150      | μs | _                       | PRQ-413 |

# 4.6 Electrical characteristics: charge pump

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_J$  = -40°C to +150°C; all voltages are referenced to GND; positive current flowing into pin.

Table 7 Electrical characteristics: charge pump

| Parameter             | Symbol                  |      | Values |      | Unit | Note or condition | P-      |

|-----------------------|-------------------------|------|--------|------|------|-------------------|---------|

|                       |                         | Min. | Тур.   | Max. |      |                   | Number  |

| Charge pump frequency | $f_{CP}$                | 140  | 156    | 172  | kHz  | -                 | PRQ-127 |

| VCP_PUMP              |                         |      | 1      |      |      |                   |         |

| VCP_PUMP_H threshold  | V <sub>CP_PUMP_H</sub>  | 12.7 | 14     | 15   | V    | _                 | PRQ-343 |

| VCP_PUMP_L threshold  | V <sub>CP_PUMP_L</sub>  | 11.7 | 13     | 14   | V    | _                 | PRQ-344 |

| VCP_PUMP hysteresis   | V <sub>CP_PUMP_HY</sub> | 0.5  | 1      | 1.5  | V    | _                 | PRQ-402 |

#### VCP\_READY

# 48 V smart high-side MOSFET gate driver with SPI

## 4 General product description

(continued) Electrical characteristics: charge pump Table 7

| Parameter                                    | Symbol                   |      | Values |      | Unit | Note or condition           | P-<br>Number |

|----------------------------------------------|--------------------------|------|--------|------|------|-----------------------------|--------------|

|                                              |                          | Min. | Тур.   | Max. |      |                             |              |

| VCP_READY_H threshold                        | V <sub>CP_READY_H</sub>  | 10   | 11     | 11.7 | V    | -                           | PRQ-345      |

| VCP_READY_L threshold                        | V <sub>CP_READY_L</sub>  | 9.5  | 10.5   | 11.2 | V    | -                           | PRQ-346      |

| VCP_READY hysteresis                         | V <sub>CP_READY_HY</sub> | 0.38 | 0.5    | 0.62 | V    | -                           | PRQ-403      |

| VCP_UV                                       |                          |      |        | •    |      |                             |              |

| VCP_UV_H threshold                           | V <sub>CP_UV_H</sub>     | 5.7  | 6.5    | 7    | V    | -                           | PRQ-347      |

| VCP_UV_L threshold                           | V <sub>CP_UV_L</sub>     | 5.2  | 6      | 6.5  | V    | _                           | PRQ-348      |

| VCP_UV hysteresis                            | V <sub>CP_UV_HY</sub>    | 0.25 | 0.5    | 0.75 | V    | _                           | PRQ-404      |

| VCP_UV Blanking time                         | t <sub>VCP_UV_BLK</sub>  | 2.4  | 3      | 4    | ms   | _                           | PRQ-494      |

| Charge pump output curr                      | ent                      |      |        |      | -    |                             | <u> </u>     |

| Charge pump output current capability at VCP | I <sub>CPO</sub>         | -    | -      | -10  | mA   | C <sub>CPHL</sub> = 220 nF; | PRQ-349      |

| CPL pulsed current                           | I <sub>CPL_PULSE</sub>   | 60   | 80     | 110  | mA   | _                           | PRQ-487      |

5 High-side gate driver

# 5 High-side gate driver

The high-side gate driver is capable to drive multiple external MOSFETs for high current capability. Two independent channels are available, and they can be switched on and off by the SPI register commands. The gate drivers are supplied by an internal one-stage charge pump with external capacitors.

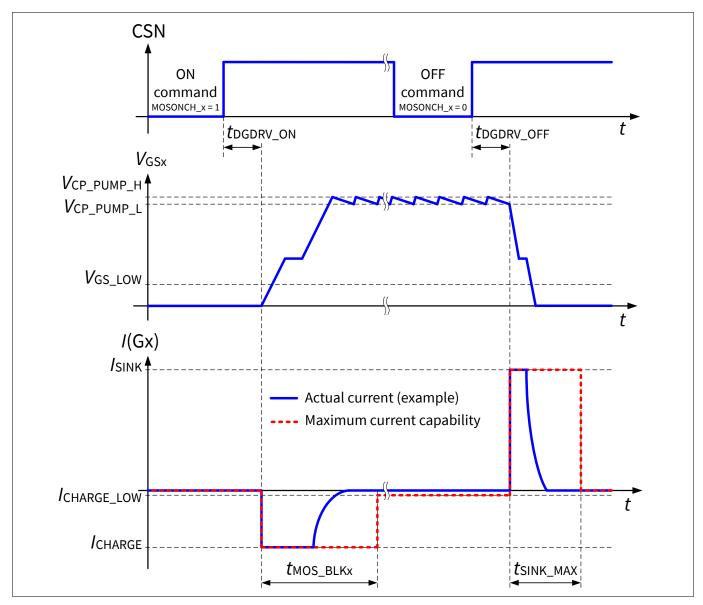

Figure 6 Maximum gate driving capability

#### 5.1 Channel activation

The selected channel is activated under the following condition: ENABLE = high **AND** MOSONCH\_(x) = high **AND** SAFESTATEN = high.

Table 8 MOSFET activation

| MOSONCH_(x)[0] | MOSFET activation state                |

|----------------|----------------------------------------|

| 0              | MOSFET channel not activated (default) |

| 1              | MOSFET channel activated               |

# 48 V smart high-side MOSFET gate driver with SPI

5 High-side gate driver

When a channel is activated through the SPI interface, its output gate current capability is set to  $I_{CHARGE}$  for a duration of maximum  $t_{MOS\ BLKx}$  (MOS blanking time).  $I_{CHARGE}$  is active until  $V_{GS}$  reaches  $V_{CP}$ , so the actual time depends on the MOSFETs gate capacitance.

Once the  $t_{MOS-BLKx}$  time expires, the output gate current capability is reduced to maximum  $l_{CHARGE-LOW}$ ; the actual current delivered by the driver depends on external leakages, coming for example from an external pull-down resistor added between gate and source of the MOSFETs.

#### 5.2 Channel deactivation

The channel is deactivated by discharging the external MOSFET's gate if one of the following conditions are met:

- MOSONCH\_(x) set from high to low

- Pin ENABLE set from high to low

- SAFESTATEN set from high to low

Note:

In case of a failure, MOSONCH\_(x) is automatically set from high to low, which immediately triggers a channel deactivation.

When a channel is deactivated either due to MOSONCH\_(x) or pin SAFESTATEN set from high to low, the output gate control pulls a high discharge current, set to  $I_{SINK}$  for a duration of maximum  $t_{SINK-MAX}$ .  $I_{SINK}$  is active until  $V_{\rm GS}$  is zero, so the actual time depends on the MOSFETs gate capacitance.

Once  $t_{SINK-MAX}$  expires, the output gate control changes to a voltage clamping structure, which limits the gate to source voltage ( $V_{GS}$ ) to maximum  $V_{GS LOW}$ . This clamping structure ensures that the MOSFETs'  $V_{GS}$  is below V<sub>GS(th)</sub> to keep them OFF.

When the channels are deactivated due to pin ENABLE set from high to low, the output gate control does not pull the high discharge current ( $I_{SINK}$ ), it immediately changes to the voltage clamping structure.

#### 5.3 **MOSFET driver output**

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_1 = -40$ °C to +150°C; all voltages are referenced to GND; positive current flowing into pin.

Table 9 **MOSFET driver output**

| Parameter                                  | Symbol                  |                     | Values |                            | Unit | Note or condition                                                          | lition P-<br>Number |

|--------------------------------------------|-------------------------|---------------------|--------|----------------------------|------|----------------------------------------------------------------------------|---------------------|

|                                            |                         | Min.                | Тур.   | Max.                       |      |                                                                            |                     |

| Gate charge current high                   | I <sub>CHARGE</sub>     | _                   | _      | -300                       | mA   | $V_{Gx} = V_{Sx} = 0 \text{ V}$                                            | PRQ-133             |

| Gate charge current low                    | I <sub>CHARGE_LOW</sub> | -5                  | -4     | -2.5                       | mA   | _                                                                          | PRQ-488             |

| Gate discharge current                     | I <sub>SINK</sub>       | 0.9                 | 1.1    | 1.3                        | Α    | $V_{\rm Gx} - V_{\rm Sx} = 13  \rm V$                                      | PRQ-134             |

| Gate discharge current maximum active time | t <sub>SINK_MAX</sub>   | 8                   | 10     | 12                         | μs   | 1)                                                                         | PRQ-539             |

| High level output voltage Gx vs. Sx        | $V_{GS}$                | V <sub>CP_PUM</sub> | _      | V <sub>CP_PUM</sub><br>P_H | V    | Current between Gx and Sx = 1 mA                                           | PRQ-135             |

| Low level output voltage<br>Gx vs. Sx      | V <sub>GS_LOW</sub>     | -                   | -      | 1.7                        | V    | T <sub>J</sub> < 25°C<br>Current beween Gx<br>and Sx = 100 mA              | PRQ-498             |

|                                            |                         |                     |        |                            |      | $0 V \le V_{BAT}$ $\le V_{BAT(EXT)\_MAX}$ $0 V \le V_{DD} \le V_{DD\_MAX}$ |                     |

# 48 V smart high-side MOSFET gate driver with SPI

5 High-side gate driver

#### (continued) MOSFET driver output Table 9

| eter Sy                                                         | ymbol             |      | Values |      | Unit | Note or condition                                                                                                                               | P-      |

|-----------------------------------------------------------------|-------------------|------|--------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                 |                   | Min. | Тур.   | Max. |      |                                                                                                                                                 | Number  |

| vel output voltage V <sub>0</sub><br>Sx                         | ,<br>GS_LOW       | -    | -      | 1.5  | V    | $T_J \ge 25^{\circ}\text{C}$<br>Current between Gx<br>and Sx = 100 mA                                                                           | PRQ-524 |

|                                                                 |                   |      |        |      |      | $0 \text{ V} \leq V_{\text{BAT}}$ $\leq V_{\text{BAT}(\text{EXT})\_\text{MAX}}$ $0 \text{ V} \leq V_{\text{DD}} \leq V_{\text{DD}\_\text{MAX}}$ |         |

| river dynamic paramet                                           | ter               | I    | 1      | 1    |      |                                                                                                                                                 |         |

| ırn-on delay time t <sub>D</sub>                                | OGDRV_ON          | _    | -      | 3    | μs   | Duration between<br>CSN goes from low<br>to high and gate<br>charge current is<br>activated                                                     | PRQ-137 |

| ırn-off delay time $t_{	extsf{D}}$                              | DGDRV_OFF         | _    | _      | 3    | μs   | Duration between<br>CSN goes from low<br>to high and gate<br>dicharge current is<br>activated                                                   | PRQ-139 |

| ime for gate turn-off t <sub>D</sub><br>ed by SAFESTATEN        | DGOFF_SFSTN       | _    | -      | 3    | μs   | Duration between<br>SAFESTATEN goes<br>from high to<br>low and gate<br>dicharge current is<br>activated                                         | PRQ-527 |

| source clamped $V_0$                                            | ,<br>GS_TH        | 15.5 | -      | 19.5 | V    | -                                                                                                                                               | PRQ-476 |

| zener clamping                                                  |                   |      |        |      |      |                                                                                                                                                 |         |

| ener clamping with $V_0$ t to VBAT                              | ,<br>CLAMP_G_VBAT | 78   | 82     | 87   | V    | I_G = -2.5 mA                                                                                                                                   | PRQ-489 |

| ener clamping with $V_0$                                        | ,<br>CLAMP_G_GND  | 78   | 82     | 87   | V    | I_G = -2.5 mA                                                                                                                                   | PRQ-490 |

| zener clamping ener clamping with to VBAT ener clamping with Vo | CLAMP_G_GND       | 78   | 82     |      |      |                                                                                                                                                 |         |

1) Not subject to production test, specified by design.

#### 48 V smart high-side MOSFET gate driver with SPI

**6 Protection and monitoring**

#### **Protection and monitoring** 6

The device provides three sets of features to protect and monitor:

- Monitorings, which give a status to the MCU

- Warnings, which inform the MCU of critical events with limited impact

- Failure detections, which trigger internal actions (channel deactivation mainly) and notify immediately the MCU

#### 6.1 **Monitorings**

#### Source voltage monitoring in OFF state 6.1.1

If the source voltage  $V_{Sx}$  of a deactivated channel rises above  $V_{STH}$ , and ENABLE is high, then the appropriate flag VSOURCE\_(x) is set to 1.

This warning allows to implement an "open load detection in OFF state", since the voltage on the source pin Sx would be pulled up by the leakage of the gate driver if there is no load connected.

#### Charge pump voltage monitoring 6.1.2

If the charge pump voltage VCP is above  $V_{CP}$  READY H, then the VCP\_READY flag is set to 1.

#### 6.1.3 **SPI address monitoring**

If the MCU tries to read or write a register with an address which is not available, then the ADD\_NOT\_AVAIL flag is set to 1.

#### Warnings 6.2

In order to inform the MCU about any warning on the driver, the warning flags will be used and updated by the device, which notifies the MCU by setting the INTERRUPT pin to high.

The warnings are not latched and will be reset, if the condition no longer applies.

The warnings do not change the state of the output channels.

#### 6.2.1 **Temperature warning**

The OT\_WARNING is set to 1 if the overtemperature warning threshold  $T_{\rm JW}$  is reached and exceeded.

#### One time programmable (OTP) memory data corruption 6.2.2

The device embeds an OTP to store internal settings, used to trim internal blocks for full specification compliance. These settings are written during manufacturing and this memory cannot be accessed by SPI.

The MEM\_FAIL flag is set to 1 if OTP data is corrupted or if OTP readout failed. In this case all affected trimmings are set to default values, therefore parameter deviations are possible. OTP is checked and read out right after the device is enabled.

OTP cannot be read in case of a not connected ground pin. Note:

#### **Ground loss** 6.2.3

In case of a voltage difference between 2 ground pins (whether GND, AGND or CPGND) higher than  $V_{\text{GND\_LOSS}}$ , the corresponding LOG\_(x) warning flags will be set to 1. This is typically the case for not connected ground pins.

Disconnecting AGND will trigger LOG\_A and LOG\_CP flags

#### 48 V smart high-side MOSFET gate driver with SPI

#### **6 Protection and monitoring**

- Disconnecting CPGND will trigger LOG\_CP and LOG\_D flags

- Disconnecting DGND will trigger LOG\_A and LOG\_D flags

#### 6.3 Failures detection

Failures detection is provided to implement protections for the external MOSFETs and eventually for the load. There are two types of failures detected by the gate driver:

- Latching failures, which require to be cleared before the gate driver can operate again. This category is split into two sub-categories:

- Latching failures for which clearing the flag will automatically turn the channel on again. They include:

- Undervoltage on the charge pump

- Undervoltage on gate-source voltage ( $V_{GS} = [V_{Gx} V_{Sx}]$ )

- Overvoltage on drain-source voltage ( $V_{DS} = [V_{BAT} V_{Sx}]$ ), when VDS(x)\_SS\_[0] = 0 to enable the protection

- Latching failures for which an SPI command has to follow the flag clearing in order to turn the channel on again. They include:

- Undervoltage on V<sub>DD</sub>

- SAFESTATEN pin activation

- Overtemperature shut down

- Overcurrent

- Non-latching failures, which do not need to be cleared: once the failure source is gone, the gate driver can operate again after a configurable delay. They include:

- Overvoltage on V<sub>BAT</sub>

- Undervoltage on V<sub>BAT</sub>

## **6.3.1** Failure notification and clearing

In case of failure detection, the FAILURE flag is set to high, the INTERRUPT pin is set to high and the corresponding channel(s) is (are) deactivated automatically by setting register bit MOSONCH\_(x) to 0 (except for drain-source failure detection when it is disabled through the VDS(x)\_SS register).

A latching failure can only be cleared when the failure is not present anymore, except for VCP\_UV, VGSTH\_(x) and VDSTRIP\_(x).

# 6.3.2 Non-latching failures

The non-latching failures do not need to be reset: the gate driver activates the MOSFET again, if the failure does not exist anymore.

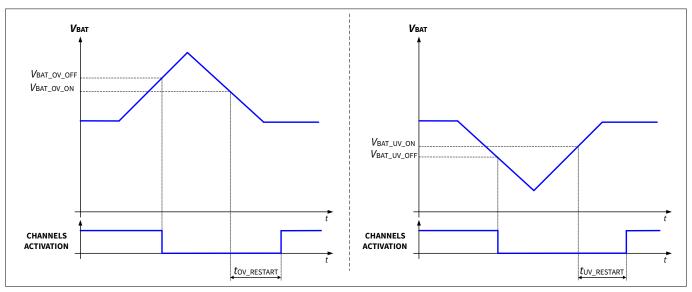

# 6.3.2.1 VBAT overvoltage

If  $V_{\rm BAT}$  exceeds  $V_{\rm BAT\_OV\_OFF}$ , the FAILURE bit and VBAT\_OV flag are set to 1.

If the  $V_{\rm BAT}$  gets lower than  $V_{\rm BAT}$  OV ON, then the restart will be done after  $t_{\rm OV}$  RESTART.

While the device is in auto-restart duration, none of the channels can be activated by the uC.

#### Table 10 VBAT overvoltage auto-restart time

| VBATOVARST[1:0] | VBAT overvoltage auto-restart time (typical): $t_{\text{OV\_RESTART}}$ |

|-----------------|------------------------------------------------------------------------|

| 00              | 10 μs (default)                                                        |

| 01              | 50 μs                                                                  |

| 10              | 200 μs                                                                 |

| 11              | 1 ms                                                                   |

## 48 V smart high-side MOSFET gate driver with SPI

#### **6 Protection and monitoring**

Figure 7 VBAT overvoltage and undervoltage auto-restart time diagrams

### 6.3.2.2 VBAT undervoltage

If  $V_{\rm BAT}$  gets lower than  $V_{\rm BAT\ UV\ OFF}$ , the FAILURE bit and VBAT\_UV flag are set to 1.

If the  $V_{\text{BAT}}$  gets higher than  $V_{\text{BAT\_UV\_ON}}$ , then the restart will be done after  $t_{\text{UV\_RESTART}}$ .

While the device is in auto-restart duration, none of the channels can be activated by the  $\mu C$ .

Table 11 VBAT undervoltage auto-restart time

| VBATUVARST[1:0] | VBAT undervoltage auto-restart time $t_{UV\_RESTART}$ (typical) |

|-----------------|-----------------------------------------------------------------|

| 00              | 1 ms (default)                                                  |

| 01              | 5 ms                                                            |

| 10              | 20 ms                                                           |

| 11              | 50 ms                                                           |

# 6.3.3 Latching failures

Once a latching failure (except VDD\_UV) has been detected, a reset can be operated either by toggling ENABLE, VDD (Chapter 4.2.4), or by an SPI command.

## **6.3.3.1** Blank time and filter time for failures detections

#### 6.3.3.1.1 Blank time

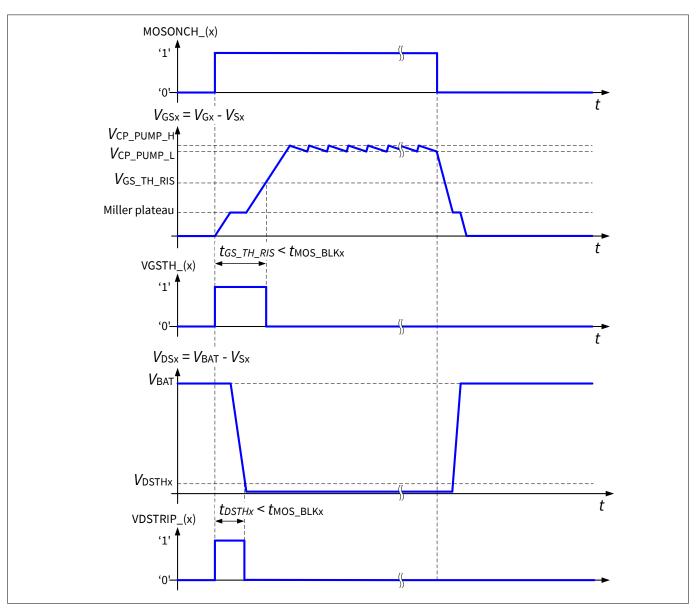

Both drain-source and gate-source failure detections are inherently triggered at the turn-on of a channel. Turning on a MOSFET implies a transient phase where the gate-source voltage is rising and drain-source voltage is decreasing before they reach their steady state.

Both failure detections have therefore to be temporary blanked at turn-on, which is the purpose of the configurable blank time:  $t_{\text{MOS\_BLKx}}$ . Its value is configured for each channel independently, based on the MOSFETs characteristics (total  $C_{\text{GS}}$  mainly).

Note: As described in Chapter 5.1,  $t_{MOS\ BLKx}$  also defines the maximum duration of the  $I_{CHARGE}$  current.

#### 48 V smart high-side MOSFET gate driver with SPI

#### **6 Protection and monitoring**

Figure 8 Blank time at MOSFET turn-on

A configurable blank time for the drain-source and gate-source failure detections is applied at the turn-on of the selected channel. During the blank time  $t_{MOS\_BLKx}$ , a drain-source or gate-source overvoltage failure is masked.

Table 12 MOSFET voltage blank time

| MOSBLK_(x)_[1:0] | MOSFET voltage blank time (typical) $t_{MOS\_BLKx}$ |

|------------------|-----------------------------------------------------|

| 00               | 10 μs (default)                                     |

| 01               | 20 μs                                               |

| 10               | 50 μs                                               |

| 11               | 100 μs                                              |

#### 48 V smart high-side MOSFET gate driver with SPI

**6 Protection and monitoring**

#### 6.3.3.1.2 Filter time

Both drain-source and gate-source failure detections may be wrongly triggered due to noisy signals on the monitored pins. A configurable filter time is therefore provided for each channel independently, which applies for the two failure detections:  $t_{\text{MOS FLTx}}$ .

Table 13 MOSFET voltage filter time

| MOSFLT_(x)_[1:0] | MOSFET voltage filter time (typical) $t_{MOS\_FLTx}$ |

|------------------|------------------------------------------------------|

| 00               | 0.5 μs                                               |

| 01               | 1 μs (default)                                       |

| 10               | 2 μs                                                 |

| 11               | 5 μs                                                 |

## 6.3.3.2 Drain-source overvoltage

The drain to source voltage of activated channel(s) is continuously monitored in order to protect high-side MOSFETs against a short circuit to ground during ON-state.

If a channel is activated and the  $V_{\rm BAT}$  (drain) to  $V_{\rm Sx}$  (source) voltage  $V_{\rm DS}$  exceeds  $V_{\rm DSTHx}$  for longer than the filter time  $t_{\rm MOS\_FLTx}$  after the blanking time  $t_{\rm MOS\_BLKx}$ , the bit FAILURE and the VDSTRIP\_(x) bit are set to 1 and the register bit MOSONCH\_(x) is set to 0 if the VDS(x)\_SS bit is set to 0.

Otherwise (VDS(x)\_SS bit is set to 1) only the bit FAILURE and the VDSTRIP\_(x) bit are set to 1 and the register bit MOSONCH\_(x) is still set to 1.

Each channel has a dedicated threshold that can be selected by the register VDSTH\_(x).

When VDS(x)\_SS bit is set to 0 and the VDSTRIP\_(x) failure flag is cleared, the selected channel immediately turns on again. If the  $V_{\rm DS}$  of the channel is still above  $V_{\rm DSTHx}$  for longer than the filter time  $t_{\rm MOS\_FLTx}$  after the blanking time  $t_{\rm MOS\_BLKx}$  (e.g. the failure cause is still present), the channel is disabled again.

Table 14 Drain-source overvoltage threshold

| VDSTH_(x)_[2:0] | Positive drain-source overvoltage threshold (typical) V <sub>DSTHx</sub> | Negative drain-source overvoltage threshold |

|-----------------|--------------------------------------------------------------------------|---------------------------------------------|

| 000             | 100 mV                                                                   | -100 mV                                     |

| 001             | 150 mV                                                                   | -150 mV                                     |

| 010             | 200 mV (default)                                                         | - 200 mV (default)                          |

| 011             | 250 mV                                                                   | -250 mV                                     |

| 100             | 300 mV                                                                   | -300 mV                                     |

| 101             | 400 mV                                                                   | - 400 mV                                    |

| 110             | 500 mV                                                                   | - 500 mV                                    |

| 111             | 600 mV                                                                   | - 600 mV                                    |

Table 15 Drain-source channel de-activation condition

| VDS(x)_SS_[0] | Drain-source channel condition                                        |

|---------------|-----------------------------------------------------------------------|

| 0             | Channel is de-activated in case of drain-source overvoltage (default) |

| 1             | Channel is not de-activated in case of drain-source overvoltage       |

#### 48 V smart high-side MOSFET gate driver with SPI

# infineon

**6 Protection and monitoring**

#### 6.3.3.3 Gate-source undervoltage

The device reports a gate-source undervoltage failure if the following conditions are both met:

- After expiration of the configured blank time  $t_{\text{MOS BLKx}}$

- If the gate-source voltage is less than the threshold  $V_{GS\_TH(x)}$  for the selected channel for a duration longer than the configured filter time  $t_{MOS\_FLTx}$

In case of gate-source undervoltage failure, the bit FAILURE and the bit VGSTH\_(x) are set to 1.

When the VGSTH\_(x) flag is cleared, the selected channel automatically turns on again. If the  $V_{\rm GS}$  of the channel is still below VGS\_TH\_RIS for longer than the filter time  $t_{\rm MOS\_FLTx}$  after the blanking time  $t_{\rm MOS\_BLKx}$  (e.g. the failure cause is still present), the channel is disabled again.

#### 6.3.3.4 Channel cross-control

While activating both channels, VGSTH\_(x) and VDSTRIP\_(x) failures related to one channel may or may not affect the other channel. This cross-control between the 2 channels is programmable by SPI.

While the CHCRCTRL bit is set to 1, any of the following failures will deactivate the channels A (CHA) and B (CHB) according this overview:

- In case of VGSTH\_(x) = 1 -> CHA = OFF and CHB = OFF

- In case of VDSTRIP\_A = 1, VDSA\_SS = 0 and VDSB\_SS = 0 -> CHA = OFF and CHB = OFF

- In case of VDSTRIP\_A = 1, VDSA\_SS = 1 and VDSB\_SS = 0 -> CHA = Keep previous state (ON) and CHB = OFF

- In case of VDSTRIP\_A = 1, VDSA\_SS = 0 and VDSB\_SS = 1 -> CHA = OFF and CHB = Keep previous state

- In case of VDSTRIP\_A = 1, VDSA\_SS = 1 and VDSB\_SS = 1 -> CHA = Keep previous state (ON) and CHB = Keep previous state

- In case of VDSTRIP\_B = 1, VDSA\_SS = 0 and VDSB\_SS = 0 -> CHA = OFF and CHB = OFF

- In case of VDSTRIP\_B = 1, VDSA\_SS = 1 and VDSB\_SS = 0 -> CHA = Keep previous state and CHB = OFF

- In case of VDSTRIP B = 1, VDSA SS = 0 and VDSB SS = 1 -> CHA = OFF and CHB = Keep previous state (ON)

- In case of VDSTRIP\_B = 1, VDSA\_SS = 1 and VDSB\_SS = 1 -> CHA = **Keep previous state** and CHB = **Keep previous state** (ON)

If the CHCRCTRL bit is set to 0, only the faulty channel will be treated.

#### Table 16 Channel cross-control

| CHCRCTRL[0] | Channel cross-control status      |  |  |  |

|-------------|-----------------------------------|--|--|--|

| 0           | Cross-control deactivated         |  |  |  |

| 1           | Cross-control activated (default) |  |  |  |

## 6.3.3.5 VDD undervoltage

If the VDD voltage falls below the  $V_{\rm DD\_UV\_ON}$  threshold, the device is reset. When  $V_{\rm DD\_UV}$  comes back above the  $V_{\rm DD\_UV\_ON}$  threshold, VDD\_UV bit is set to 1.

### 6.3.3.6 VCP undervoltage

The VCP\_UV bit and the FAILURE bit are set to 1 as soon as the  $(V_{CP} - V_{BAT})$  voltage gets lower than the  $V_{CP_{UV_L}}$  threshold. The charge pump is immediately disabled.

When the failure flag VCP\_UV is cleared, the charge pump immediately restarts. If the  $(V_{CP} - V_{BAT})$  voltage is still below  $V_{CP\_UV\_H}$  after the startup blanking time  $t_{VCP\_UV\_BLK}$ , (e.g. the failure cause is still present), the charge pump is disabled again.

#### 6.3.3.7 SAFESTATEN activation

Once the SAFESTATEN signal is set to low, the FAILURE bit is set to 1.

#### 48 V smart high-side MOSFET gate driver with SPI

**6 Protection and monitoring**

#### 6.3.3.8 Overtemperature

If the internal temperature sensor reaches  $T_{\rm JSD}$ , the gate drivers are latched off, the charge pump and the current sense amplifier are deactivated and the TSD and FAILURE flags are set to 1.

### 6.3.3.9 Current sense amplifier and overcurrent comparator

Current sense amplifier is used for monitoring the voltage drop across the shunt resistor as a sensor for the load current. If overcurrent is detected, this will switch off both channels.

Current sense comparator and amplifier are active under the following condition:

ENABLE = high **AND** VCP\_UV = low **AND** VBAT\_UV = low **AND** VBAT\_OV = low **AND** TSD = low **AND**  $V_{DD} > V_{DD}$  UV ON.

### **6.3.3.9.1** Gain configuration

The differential gain of the current sense amplifier is configurable by the configuration bits CSAG\_(x).

Table 17 Configuration of the current sense amplifier gain

| CSAG[2:0] | Current sense amplifier gain G <sub>DIFF</sub> (typical) |

|-----------|----------------------------------------------------------|

| 000       | 10 V/V                                                   |

| 001       | 15 V/V                                                   |

| 010       | 20 V/V                                                   |

| 011       | 25 V/V                                                   |

| 100       | 31.5 V/V                                                 |

| 101       | 35 V/V (default)                                         |

| 110       | 40 V/V                                                   |

| 111       | 47.7 V/V                                                 |

## 6.3.3.9.2 Current sense position

In order to adjust the internal circuitry to the proper shunt position (high-side or low-side), the CSA\_HSS needs to be set.

While the CSA\_HSS bit is set to 0, the internal circuitry is optimized for a current sense in low-side position.

If the CSA\_HSS bit is set to 1, the internal circuitry is optimized for a current sense in high-side position.

Table 18 Current sense position adjustment

| CSA_HSS[0] | Current sense position                  |

|------------|-----------------------------------------|

| 0          | Shunt is in low-side position (default) |

| 1          | Shunt is in high-side position          |

### 6.3.3.9.3 Current sense output load

In order to adjust to the amount of output charge connected to the CSO pin, some internal circuitry can be activated.

While the CSA\_COUTSEL bit is set to 1, the internal circuitry is optimized for an external load capacitance higher than 100 pF.

If the CSA\_COUTSEL bit is set to 0, the internal circuitry is optimized for an external load capacitance lower than 100 pF.

## 48 V smart high-side MOSFET gate driver with SPI

#### **6 Protection and monitoring**

Table 19 Current sense output load adjustment

| CSA_COUTSEL[0] | Current sense output charge    |

|----------------|--------------------------------|

| 0              | Output load < 100 pF (default) |

| 1              | Output load > 100 pF           |

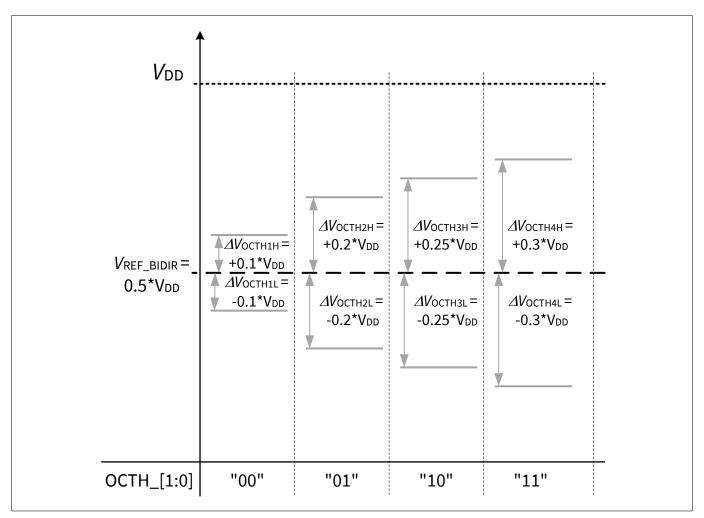

#### 6.3.3.9.4 Overcurrent detection

A comparator at CSO detects overcurrent conditions.

If the CSA output is out of the range between threshold voltages  $\Delta VOCTHxL$  and  $\Delta VOCTHxH$  configured in OCTH, all channels are switched off and the bits FAILURE and ITRIP are set to 1 if at least one channel was in ON state.

Figure 9 Overcurrent detection thresholds

#### 6.3.3.9.5 Electrical characteristics: current sense

Unless otherwise specified: VBAT and VDD inside the normal operation range;  $T_J$  = -40°C to +150°C; all voltages are referenced to GND; positive current flowing into pin.

# infineon

## **6 Protection and monitoring**

Table 20 **Electrical characteristics: current sense**

| Parameter                                                  | Symbol                                       |      | Values         |      | Unit             | Note or condition                                                                                            | P-      |  |

|------------------------------------------------------------|----------------------------------------------|------|----------------|------|------------------|--------------------------------------------------------------------------------------------------------------|---------|--|

|                                                            |                                              | Min. | Тур.           | Max. |                  |                                                                                                              | Number  |  |

| Input offset voltage                                       | V <sub>OFFSET</sub>                          | -1.4 | 0              | 1.4  | mV               | -                                                                                                            | PRQ-52  |  |

| Integrated output noise voltage at CSO pin                 | V <sub>CSO_NOISE</sub>                       | -    | -              | 5    | mV <sub>rm</sub> | <sup>1)</sup> ISP shorted to<br>ISN; all gain settings;<br>output open (no<br>load at CSO)                   | PRQ-262 |  |

| PSRR - Power supply rejection ratio VCP                    | P <sub>SRR</sub>                             | 60   | _              | _    | dB               | DC up to 1 kHz                                                                                               | PRQ-63  |  |

| Settling time to 98%                                       | t <sub>SET</sub>                             | -    | _              | 7    | μs               | Duration between<br>CSN goes from low<br>to high and signal<br>at CSO pin is settled<br>(98% of final value) | PRQ-222 |  |

| Reference voltage for bidirectional CSA                    | V <sub>REF_BIDIR</sub>                       | -2%  | $V_{\rm DD}/2$ | +2%  | V                | -                                                                                                            | PRQ-228 |  |

| Digital glitch filter time for ITRIP                       | t <sub>ITRIP_FLT</sub>                       | 1.2  | 1.5            | 1.8  | μs               | 1)                                                                                                           | PRQ-505 |  |

| ISP, ISN leakage current while off                         | I <sub>SP_OFF</sub> ,<br>I <sub>SN_OFF</sub> | -5   | -              | 5    | μΑ               | ENABLE = 0; $V_{\rm ISP}$ = $V_{\rm ISN}$ ; 0 V $\leq$ $V_{\rm ISN}$ , $V_{\rm ISP}$ $\leq$ $V_{\rm BAT}$    | PRQ-392 |  |

| Common mode rejection r                                    | atio                                         | ·    |                |      | ·                |                                                                                                              |         |  |

| CMRR - common mode<br>rejection ratio @ Gain = 10<br>V/V   | C <sub>MRR10</sub>                           | 69   | -              | -    | dB               | DC up to 1 kHz                                                                                               | PRQ-64  |  |

| CMRR - common mode rejection ratio @ Gain = 15 V/V         | C <sub>MRR15</sub>                           | 72.5 | -              | -    | dB               | DC up to 1 kHz                                                                                               | PRQ-148 |  |

| CMRR - common mode rejection ratio @ Gain = 20 V/V         | C <sub>MRR20</sub>                           | 75   | -              | -    | dB               | DC up to 1 kHz                                                                                               | PRQ-149 |  |

| CMRR - common mode rejection ratio @ Gain = 25 V/V         | C <sub>MRR25</sub>                           | 77   | -              | -    | dB               | dB DC up to 1 kHz                                                                                            |         |  |

| CMRR - common mode<br>rejection ratio @ Gain =<br>31.5 V/V | C <sub>MRR31.5</sub>                         | 78.5 | -              | -    | dB               | DC up to 1 kHz                                                                                               | PRQ-210 |  |

| CMRR - common mode rejection ratio @ Gain = 35 V/V         | C <sub>MRR35</sub>                           | 79.5 | -              | -    | dB               | DC up to 1 kHz                                                                                               | PRQ-211 |  |

# **(infineon**

## **6 Protection and monitoring**

Table 20 (continued) Electrical characteristics: current sense

| Parameter                                                  | Symbol                |                            | Values                     |                            | Unit | Note or condition                                                                                                  | P-      |  |

|------------------------------------------------------------|-----------------------|----------------------------|----------------------------|----------------------------|------|--------------------------------------------------------------------------------------------------------------------|---------|--|

|                                                            |                       | Min.                       | Тур.                       | Max.                       |      |                                                                                                                    | Number  |  |

| CMRR - common mode<br>rejection ratio @ Gain = 40<br>V/V   | C <sub>MRR40</sub>    | 81                         | -                          | -                          | dB   | DC up to 1 kHz                                                                                                     | PRQ-212 |  |

| CMRR - common mode<br>rejection ratio @ Gain =<br>47.7 V/V | C <sub>MRR47.7</sub>  | 82.5                       | -                          | -                          | dB   | DC up to 1 kHz                                                                                                     | PRQ-213 |  |

| Current sense amplifier di                                 | fferential ga         | in                         |                            |                            |      |                                                                                                                    |         |  |