K4A4G045WD K4A4G085WD

# 4Gb D-die DDR4 SDRAM

78FBGA with Lead-Free & Halogen-Free (RoHS compliant)

# datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

(C) 2015 Samsung Electronics Co., Ltd. All rights reserved.

## **Revision History**

| Revision No. | <u>History</u>                                                                                                     | Draft Date     | <u>Remark</u> | <u>Editor</u> |

|--------------|--------------------------------------------------------------------------------------------------------------------|----------------|---------------|---------------|

| 1.0          | - First SPEC release                                                                                               | Feb. 2014      | -             | S.H.Kim       |

| 1.1          | - Add x8 Product                                                                                                   | Feb. 2014      | -             | S.H.Kim       |

| 1.2          | - Add IDD & IPP value of x8 Product.                                                                               | May. 2014      | -             | S.H.Kim       |

|              | - Change IPP Value of x4 Product.                                                                                  |                |               |               |

| 1.21         | - Corrected typo.                                                                                                  | Jun. 2014      | -             | S.H.Kim       |

| 1.3          | - Change [Table 3] Input/Output function description on page 8~9                                                   | Sep. 2014      | -             | J.Y.Lee       |

|              | <ul> <li>Change [Table 8] Allowed time before ringback(tDVAC) for CK_t - CK_c<br/>on page 13</li> </ul>            |                |               |               |

|              | <ul> <li>- Add Slew Rate Definition for Single-ended Input Signals ( CMD/ADD )<br/>on page 18</li> </ul>           |                |               |               |

|              | - Change Alert_n output Drive Characteristic on page 26                                                            |                |               |               |

|              | - Change Speed Bin on page 31~34                                                                                   |                |               |               |

|              | - Change IDD, IPP and IDDQ Measurement Conditions on page 35                                                       |                |               |               |

|              | - Change [Table 34] Timings used for IDD, IPP and IDDQ Measurement-<br>Loop Patterns on page 37                    |                |               |               |

|              | <ul> <li>Change [Table 41] IDD4W, IDD4WA, IDD4WB and IDD4W_par Measure<br/>ment-Loop Pattern on page 46</li> </ul> |                |               |               |

|              | - Change [Table 42] IDD4WC Measurement-Loop Pattern on page 47                                                     |                |               |               |

|              | - Change [Table 48] Silicon pad I/O Capacitance on page 52                                                         |                |               |               |

|              | - Change [Table 52] Timing Parameters by Speed Grade                                                               |                |               |               |

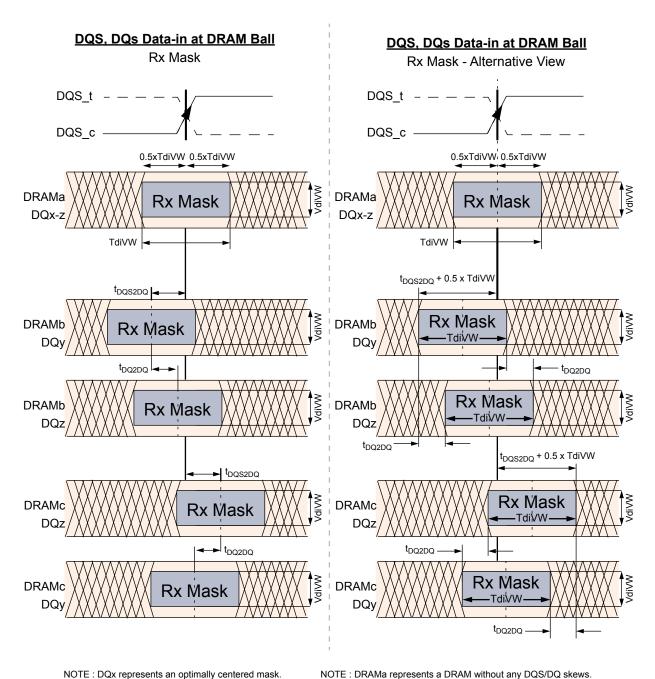

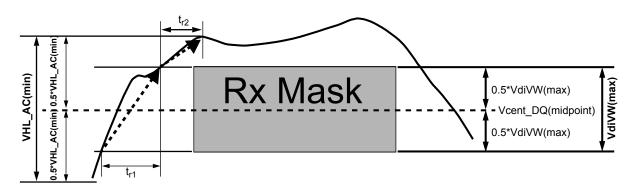

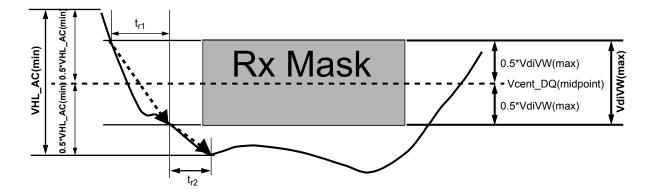

|              | <ul> <li>Change The DQ input receiver compliance mask for voltage and timing<br/>on page 62</li> </ul>             |                |               |               |

|              | <ul> <li>Change [Figure 26] DQS to DQ and DQ to DQ Timings at DRAM Balls<br/>on page 62</li> </ul>                 |                |               |               |

|              | - Delete [Figure 25] DQS to DQS Timings at DRAM latch                                                              |                |               |               |

|              | - Delete [Figure 26] DQ TdIPW and SRIN_divw defintion                                                              |                |               |               |

|              | - Add [Figure 27] Slew Rate Conditions For Rising Transition on page 63                                            |                |               |               |

|              | - Add [Figure 28] Slew Rate Conditions For Falling Transition on page 63                                           |                |               |               |

|              | - Change [Table 52] DRAM DQs In Receive Mode on page 64                                                            |                |               |               |

|              | - Change [Table 53] Function Matrix on page 65                                                                     |                |               |               |

| 1.4          | - Add DRAM Data Timing (tDVWd , tDVWp ) on page 56                                                                 | Sep. 2014      | -             | J.Y.Lee       |

|              | - Change FBGA Package Dimension on page 7                                                                          |                |               |               |

| 1.41         | - Corrected typo.                                                                                                  | Dec. 2014      | -             | J.Y.Lee       |

| 1.5          | - Added values on page 11 [Table 5]                                                                                | 26th Oct. 2015 | -             | J.Y.Lee       |

| 1.6          | - Change of IDD7 value on page 50~51                                                                               | 12th Nov. 2015 | -             | J.Y.Lee       |

| 1.7          | - Add information about I-temp                                                                                     | 3th Dec. 2015  | -             | J.Y.Lee       |

## **Table Of Contents**

## 4Gb D-die DDR4 SDRAM

| 1. Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 2. Key Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                       |

| 3. Package pinout/Mechanical Dimension & Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5<br>6                                                                  |

| 4. Input/Output Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                                                                       |

| 5. DDR4 SDRAM Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11                                                                      |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12                                                                      |

| 7. AC & DC Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                      |

| 8. AC & DC Input Measurement Levels 8.1 AC & DC Logic Input Levels for Single-ended Signals 8.2 VREF Tolerances 8.3 AC & DC Logic Input Levels for Differential Signals 8.3.1. Differential Signals Definition 8.3.2. Differential Swing Requirement for Clock (CK_t - CK_c) 8.3.3. Single-ended Requirements for Differential Signals 8.3.4. Address, Command and Control Overshoot and Undershoot Specifications 8.3.5. Clock Overshoot and Undershoot Specifications 8.3.6. Data, Strobe and Mask Overshoot and Undershoot Specifications 8.4. Slew Rate Definitions 8.4.1. Slew Rate Definitions for Differential Input Signals (CK) 8.4.2. Slew Rate Definition for Single-ended Input Signals (CMD/ADD) 8.5. Differential Input Cross Point Voltage 8.6. CMOS Rail to Rail Input Levels 8.6.1. CMOS Rail to Rail Input Levels for RESET_n 8.7 AC and DC Logic Input Levels for DQS Signals 8.7.1. Differential Signal Definition 8.7.2. Differential Swing Requirements for DQS (DQS_t - DQS_c) 8.7.3. Peak Voltage Calculation Method 8.7.4. Differential Input Cross Point Voltage 8.7.5. Differential Input Slew Rate Definition | 13 13 13 13 14 14 14 15 15 16 17 17 20 20 21 21 22 22 22 22 22 22 22 23 |

| 9. AC and DC Output Measurement Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                         |

| 10. Speed Bin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                         |

| 11. IDD and IDDQ Specification Parameters and Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36<br>36                                                                |

| 12. Input/Output Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                      |

| 13. Electrical Characteristics & AC Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                      |

# datasheet

## **DDR4 SDRAM**

| 13.3 Timing Parameters by Speed Grade                             | 56 |

|-------------------------------------------------------------------|----|

| 13.4 The DQ Input Receiver Compliance Mask for Voltage and Timing | 62 |

| 13.5 DDR4 Function Matrix                                         |    |

|                                                                   |    |

## 1. Ordering Information

#### [ Table 1 ] Samsung 4Gb DDR4 D-die ordering information table

| Organization | DDR4-2133 (15-15-15) | DDR4-2400 (17-17-17) <sup>2</sup> | Package |

|--------------|----------------------|-----------------------------------|---------|

| 1Gx4         | K4A4G045WD-BCPB      | K4A4G045WD-BCRC                   | 78 FBGA |

| 512Mx8       | K4A4G085WD-BCPB      | K4A4G085WD-BCRC                   | 78 FBGA |

| 512Mx8       | K4A4G085WD-BIPB      | K4A4G085WD-BIRC                   | 78 FBGA |

#### NOTE

- 1. Speed bin is in order of CL-tRCD-tRP.

- 2. Backward compatible to DDR4-2133(15-15-15)

- 3. 13th digit stands for below.

- "C": Commercial temp/Normal power

- "I": Industrial temp/Normal power

## 2. Key Features

#### [ Table 2 ] 4Gb DDR4 D-die Speed bins

| Speed       | DDR4-1600 | DDR4-1866 | DDR4-2133 | DDR4-2400 | Unit  |

|-------------|-----------|-----------|-----------|-----------|-------|

| Speed       | 11-11-11  | 13-13-13  | 15-15-15  | 17-17-17  | Offic |

| tCK(min)    | 1.25      | 1.071     | 0.938     | 0.833     | ns    |

| CAS Latency | 11        | 13        | 15        | 17        | nCK   |

| tRCD(min)   | 13.75     | 13.92     | 14.06     | 14.16     | ns    |

| tRP(min)    | 13.75     | 13.92     | 14.06     | 14.16     | ns    |

| tRAS(min)   | 35        | 34        | 33        | 32        | ns    |

| tRC(min)    | 48.75     | 47.92     | 47.06     | 46.16     | ns    |

- JEDEC standard 1.2V (1.14V~1.26V)

- V<sub>DDQ</sub> = 1.2V (1.14V~1.26V)

- 800 MHz f<sub>CK</sub> for 1600Mb/sec/pin,933 MHz f<sub>CK</sub> for 1866Mb/sec/pin, 1067MHz f<sub>CK</sub> for 2133Mb/sec/pin, 1200MHz f<sub>CK</sub> for2400Mb/sec/pin

- 16 Banks (4 Bank Groups)

- Programmable CAS Latency(posted CAS): 10,11,12,13,14,15,16,17,18

- Programmable Additive Latency: 0, CL-2 or CL-1 clock

- Programmable CAS Write Latency (CWL) = 9,11 (DDR4-1600), 10,12 (DDR4-1866), 11,14 (DDR4-2133) and 12,16 (DDR4-2400)

- · 8-bit pre-fetch

- Burst Length: 8, 4 with tCCD = 4 which does not allow seamless read or write [either On the fly using A12 or MRS]

- · Bi-directional Differential Data-Strobe

- Internal(self) calibration: Internal self calibration through ZQ pin (RZQ: 240 ohm ± 1%)

- · On Die Termination using ODT pin

- Average Refresh Period 7.8us at lower than T<sub>CASE</sub> 85°C, 3.9us at 85°C < T<sub>CASE</sub>  $\leq$  95 °C

- Support Industrial Temp ( -40  $\sim 95^{\circ}C$  )

- tREFI 7.8us at -40 °C ≤ TCASE ≤ 85°C

- tREFI 3.9us at 85 °C < TCASE ≤ 95°C

- · Asynchronous Reset

- Package: 78 balls FBGA x4/x8

- All of Lead-Free products are compliant for RoHS

- All of products are Halogen-free

- CRC(Cyclic Redundancy Check) for Read/Write data security

- Command address parity check

- · DBI(Data Bus Inversion)

- Gear down mode

- POD (Pseudo Open Drain) interface for data input/output

- Internal VREF for data inputs

- · External VPP for DRAM Activating Power

• PPR is supported

NOTE: 1. This data sheet is an abstract of full DDR4 specification and does not cover the common features which are described in "DDR4 SDRAM Device Operation & Timing

2. The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

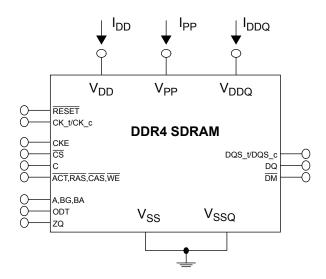

The 4Gb DDR4 SDRAM D-die is organized as a 64Mbit x 4 I/Os x 16banks or 32Mbit x8 I/Os x 16banks device. This synchronous device achieves high speed double-data-rate transfer rates of up to 2400Mb/sec/pin (DDR4-2400) for general applications.

The chip is designed to comply with the following key DDR4 SDRAM features such as posted CAS, Programmable CWL, Internal (Self) Calibration, On Die Termination using ODT pin and Asynchronous Reset .

All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the crosspoint of differential clocks (CK rising and  $\overline{\text{CK}}$  falling). All I/Os are synchronized with a pair of bidirectional strobes (DQS and  $\overline{\text{DQS}}$ ) in a source synchronous fashion. The address bus is used to convey row, column, and bank address information in a  $\overline{\text{RAS}}/\overline{\text{CAS}}$  multiplexing style. The DDR4 device operates with a single 1.2V (1.14V~1.26V) power supply and 1.2V (1.14V~1.26V) . The 4Gb DDR4 D-die device is available in 78ball FBGAs(x4/x8).

## 3. Package pinout/Mechanical Dimension & Addressing

## 3.1 x4 Package Pinout (Top view): 78ball FBGA Package

|   | 1       | 2           | 3         | 4 | 5 | 6 | 7            | 8          | 9       |   |   |

|---|---------|-------------|-----------|---|---|---|--------------|------------|---------|---|---|

| Α | VDD     | VSSQ        | NC        |   |   |   | NC           | VSSQ       | VSS     |   | Α |

| В | VPP     | VDDQ        | DQS_c     |   |   |   | DQ1          | VDDQ       | ZQ      | ı | В |

| С | VDDQ    | DQ0         | DQS_t     |   |   |   | VDD          | VSS        | VDDQ    |   | С |

| D | VSSQ    | NC          | DQ2       |   |   |   | DQ3          | NC         | VSSQ    |   | D |

| Е | VSS     | VDDQ        | NC        |   |   |   | NC           | VDDQ       | vss     | Ī | Е |

| F | VDD     | NC          | ODT       |   |   |   | CK_t         | CK_c       | VDD     | ı | F |

| G | VSS     | NC          | CKE       |   |   |   | CS_n         | NC         | NC      |   | G |

| н | VDD     | WE_n<br>A14 | ACT_n     |   |   |   | CAS_n<br>A15 | RAS_n      | vss     |   | Н |

| J | VREFCA  | BG0         | A10<br>AP |   |   |   | A12<br>BC_n  | BG1        | VDD     |   | J |

| K | VSS     | BA0         | A4        |   |   |   | А3           | BA1        | VSS     |   | K |

| L | RESET_n | A6          | A0        |   |   |   | A1           | A5         | ALERT_n |   | L |

| M | VDD     | A8          | A2        |   |   |   | A9           | <b>A</b> 7 | VPP     |   | М |

| N | VSS     | A11         | PAR       |   |   |   | NC           | A13        | VDD     |   | N |

## **Ball Locations (x4)**

- Populated ball

- + Ball not populated

Top view

(See the balls through the package)

## 3.2 x8 Package Pinout (Top view): 78ball FBGA Package

|   | 1       | 2           | 3         | 4 | 5 | 6 | 7                         | 8          | 9       |   |

|---|---------|-------------|-----------|---|---|---|---------------------------|------------|---------|---|

| A | VDD     | VSSQ        | TDQS_c    |   |   |   | DM_n,<br>DBI_n,<br>TDQS_t | VSSQ       | vss     | Α |

| В | VPP     | VDDQ        | DQS_c     |   |   |   | DQ1                       | VDDQ       | ZQ      | В |

| С | VDDQ    | DQ0         | DQS_t     |   |   |   | VDD                       | VSS        | VDDQ    | С |

| D | VSSQ    | DQ4         | DQ2       |   |   |   | DQ3                       | DQ5        | VSSQ    | D |

| E | VSS     | VDDQ        | DQ6       |   |   |   | DQ7                       | VDDQ       | VSS     | Е |

| F | VDD     | NC          | ODT       |   |   |   | CK_t                      | CK_c       | VDD     | F |

| G | VSS     | NC          | CKE       |   |   |   | CS_n                      | NC         | NC      | G |

| н | VDD     | WE_n<br>A14 | ACT_n     |   |   |   | CAS_n                     | RAS_n      | vss     | Н |

| J | VREFCA  | BG0         | A10<br>AP |   |   |   | A12<br>BC_n               | BG1        | VDD     | J |

| K | VSS     | BA0         | A4        |   |   |   | A3                        | BA1        | VSS     | K |

| L | RESET_n | A6          | A0        |   |   |   | A1                        | A5         | ALERT_n | L |

| M | VDD     | A8          | A2        |   |   |   | A9                        | <b>A</b> 7 | VPP     | М |

| N | VSS     | A11         | PAR       |   |   |   | NC                        | A13        | VDD     | N |

## **Ball Locations (x8)**

- Populated ball

- + Ball not populated

Top view

(See the balls through the package)

| A B C D E F G H J K L M N N                                   |   | _1 | 2            | 3            | 4 | 5 | 6 | 7            | 8            | 9            |

|---------------------------------------------------------------|---|----|--------------|--------------|---|---|---|--------------|--------------|--------------|

| C                                                             | Α | •  | •            | •            | + | + | + | •            | •            | •            |

| D E F G H J K L M                                             | В |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| E F G H J K L M                                               | С |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| F G H J K L M                                                 | D |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| G H J K L M                                                   | E |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| H J K L M                                                     | F |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| J K L M                                                       | G |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| K                                                             | Н | •  | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$         | J |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| $M \qquad \qquad \bullet  \bullet  +  +  +  \bullet  \bullet$ | K | •  | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

|                                                               | L |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

| N • • + + + • •                                               | М |    | lacktriangle | lacktriangle | + | + | + | lacktriangle | lacktriangle | lacktriangle |

|                                                               | N | •  | •            | •            | + | + | + | •            | •            | •            |

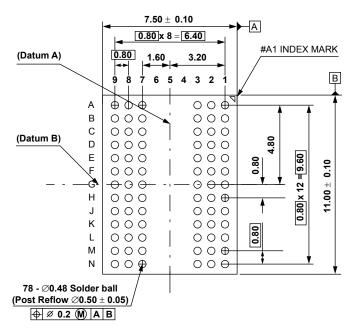

## 3.3 FBGA Package Dimension (x4/x8)

Units: Millimeters

**BOTTOM VIEW**

## 4. Input/Output Functional Description

| Symbol                                                  | Туре           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                                              | Input          | Clock: CK_t and CK_c are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CKE, (CKE1)                                             | Input          | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active in any bank). CKE is synchronous for Self-Refresh exit. After VREFCA and Internal DQ Vref have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK_t,CK_c, ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| CS_n, (CS1_n)                                           | Input          | Chip Select: All commands are masked when CS_n is registered HIGH. CS_n provides for external Rank selection on systems with multiple Ranks. CS_n is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C0,C1,C2                                                | Input          | Chip ID: Chip ID is only used for 3DS for 2,4,8high stack via TSV to select each slice of stacked component. Chip ID is considered part of the command code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ODT, (ODT1)                                             | Input          | On Die Termination: ODT (registered HIGH) enables RTT_NOM termination resistance internal to the DDR4 SDRAM. When enabled, ODT is only applied to each DQ, DQS_t, DQS_c and DM_n/DBI_n/TDQS_t, NU/TDQS_c (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 conurations. For x16 conuration ODT is applied to each DQ, DQSU_t, DQSU_c, DQSL_t, DQSL_c, DMU_n, and DML_n signal. The ODT pin will be ignored if MR1 is programmed to disable RTT_NOM.                                                                                                                                                                                                                                           |

| ACT_n                                                   | Input          | Activation Command Input: ACT_n defines the Activation command being entered along with CS_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be considered as Row Address A16, A15 and A14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAS_n/A16. CAS_n/<br>A15. WE_n/A14                      | Input          | Command Inputs: RAS_n/A16, CAS_n/A15 and WE_n/A14 (along with CS_n) define the command being entered. Those pins have multi function. For example, for activation with ACT_n Low, those are Addressing like A16,A15 and A14 but for non-activation command with ACT_n High, those are Command pins for Read, Write and other command defined in command truth table                                                                                                                                                                                                                                                                                                                                             |

| DM_n/DBI_n/TDQS_t,<br>(DMU_n/DBIU_n),<br>(DML_n/DBIL_n) | Input/Output   | Input Data Mask and Data Bus Inversion: DM_n is an input mask signal for write data. Input data is masked when DM_n is sampled LOW coincident with that input data during a Write access. DM_n is sampled on both edges of DQS. DM is muxed with DBI function by Mode Register A10,A11,A12 setting in MR5. For x8 device, the function of DM or TDQS is enabled by Mode Register A11 setting in MR1. DBI_n is an input/output identifing whether to store/output the true or inverted data. If DBI_n is LOW, the data will be stored/output after inversion inside the DDR4 SDRAM and not inverted if DBI_n is HIGH. TDQS is only supported in X8                                                               |

| BG0 - BG1                                               | Input          | Bank Group Inputs: BG0 - BG1 define to which bank group an Active, Read, Write or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle. X4/8 have BG0 and BG1 but X16 has only BG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BA0 - BA1                                               | Input          | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A0 - A17                                                | Input          | Address Inputs: Provide the row address for ACTIVATE Commands and the column address for Read/ Write commands to select one location out of the memory array in the respective bank. (A10/AP, A12/BC_n, RAS_n/A16, CAS_n/A15 and WE_n/A14 have additional functions, see other rows. The address inputs also provide the op-code during Mode Register Set commands. A17 is only defined for the x4 conuration.                                                                                                                                                                                                                                                                                                  |

| A10 / AP                                                | Input          | Auto-precharge: A10 is sampled during Read/Write commands to determine whether Autoprecharge should be performed to the accessed bank after the Read/Write operation. (HIGH: Autoprecharge; LOW: no Autoprecharge).A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                                                                            |

| A12 / BC_n                                              | Input          | Burst Chop: A12 / BC_n is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

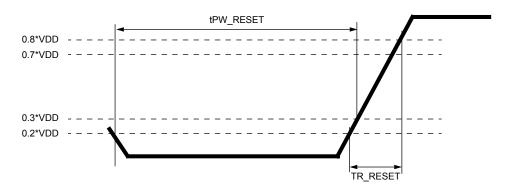

| RESET_n                                                 | Input          | Active Low Asynchronous Reset: Reset is active when RESET_n is LOW, and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation. RESET_n is a CMOS rail to rail signal with DC high and low at 80% and 20% of V <sub>DD</sub> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQ                                                      | Input / Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0~DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. During this mode, RTT value should be set to Hi-Z. Refer to vendor specific datasheets to determine which DQ is used.                                                                                                                                                                                                                                                                                                                                             |

| DQS_t, DQS_c, DQSU_t, DQSU_c, DQSL_t, DQSL_c            | Input / Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For the x16, DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobe DQS_t, DQSL_t and DQSU_t are paired with differential signals DQS_c, DQSL_c, and DQSU_c, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended.                                                                                                                                                                                                    |

## **DDR4 SDRAM**

| Symbol                    | Туре               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDQS_t, TDQS_c            | Output             | Termination Data Strobe: TDQS_t/TDQS_c is applicable for x8 DRAMs only. When enabled via Mode Register A11 = 1 in MR1, the DRAM will enable the same termination resistance function on TDQS_t/TDQS_c that is applied to DQS_t/DQS_c. When disabled via mode register A11 = 0 in MR1, DM/DBI/TDQS will provide the data mask function or Data Bus Inversion depending on MR5; A11,12,10and TDQS_c is not used. x4/x16 DRAMs must disable the TDQS function via mode register A11 = 0 in MR1.                                                                                |

| PAR                       | Input              | Command and Address Parity Input: DDR4 Supports Even Parity check in DRAM with MR setting. Once it's enabled via Register in MR5, then DRAM calculates Parity with ACT_n,RAS_n/A16,CAS_n/A15,WE_n/A14,BG0-BG1,BA0-BA1,A17-A0, and C0-C2 (3DS devices). Input parity should maintain at the rising edge of the clock and at the same time with command & address with CS_n LOW                                                                                                                                                                                               |

| ALERT_n                   | Input/Output       | Alert: It has multi functions such as CRC error flag, Command and Address Parity error flag as Output signal. If there is error in CRC, then Alert_n goes LOW for the period time interval and goes back HIGH. If there is error in Command Address Parity Check, then Alert_n goes LOW for relatively long period until on going DRAM internal recovery transaction to complete. During Connectivity Test mode, this pin works as input. Using this signal or not is dependent on system. In case of not connected as Signal, ALERT_n Pin must be bounded to VDD on board. |

| TEN                       | Input              | Connectivity Test Mode Enable: Required on X16 devices and optional input on x4/x8 with densities equal to or greater than 8Gb.HIGH in this pin will enable Connectivity Test Mode operation along with other pins. It is a CMOS rail to rail signal with AC high and low at 80% and 20% of VDD. Using this signal or not is dependent on System. This pin may be DRAM internally pulled low through a weak pull-down resistor to VSS.                                                                                                                                      |

| NC                        |                    | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDDQ                      | Supply             | DQ Power Supply: 1.2 V +/- 0.06 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VSSQ                      | Supply             | DQ Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VDD                       | Supply             | Power Supply: 1.2 V +/- 0.06 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VSS                       | Supply             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VPP                       | Supply             | DRAM Activating Power Supply: 2.5V ( 2.375V min , 2.75V max)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VREFCA                    | Supply             | Reference voltage for CA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ZQ                        | Supply             | Reference Pin for ZQ calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NOTE Input only pins (BG0 | )-BG1,BA0-BA1, A0- | A17, ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, CS_n, CKE, ODT, and RESET_n) do not supply termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## 5. DDR4 SDRAM Addressing

### 2 Gb Addressing Table

| Configuration |                      | 512 Mb x4      | 256 Mb x8 | 128 Mb x16 |  |

|---------------|----------------------|----------------|-----------|------------|--|

|               | # of Bank Groups     | 4              | 4         | 2          |  |

| Bank Address  | BG Address           | BG0~BG1        | BG0~BG1   | BG0        |  |

|               | Bank Address in a BG | BA0~BA1        | BA0~BA1   | BA0~BA1    |  |

| Ro            | ow Address           | A0~A14         | A0~A13    | A0~A13     |  |

| Col           | Column Address A0~A9 |                | A0~A9     | A0~A9      |  |

| Page size     |                      | Page size 512B |           | 2KB        |  |

### 4 Gb Addressing Table

| Configuration |                      | 1 Gb x4        | 512 Mb x8 | 256 Mb x16 |

|---------------|----------------------|----------------|-----------|------------|

|               | # of Bank Groups     | 4              | 4         | 2          |

| Bank Address  | BG Address           | BG0~BG1        | BG0~BG1   | BG0        |

|               | Bank Address in a BG | BA0~BA1        | BA0~BA1   | BA0~BA1    |

| Ro            | ow Address           | A0~A15         | A0~A14    | A0~A14     |

| Col           | Column Address A0~A9 |                | A0~A9     | A0~A9      |

| Page size     |                      | Page size 512B |           | 2KB        |

### 8 Gb Addressing Table

| Configuration |                      | 2 Gb x4         | 1 Gb x8 | 512 Mb x16 |

|---------------|----------------------|-----------------|---------|------------|

|               | # of Bank Groups     | 4               | 4       | 2          |

| Bank Address  | BG Address           | BG0~BG1         | BG0~BG1 | BG0        |

|               | Bank Address in a BG | BA0~BA1         | BA0~BA1 | BA0~BA1    |

| R             | ow Address           | A0~A16          | A0~A15  | A0~A15     |

| Col           | umn Address          | ess A0~A9 A0~A9 |         | A0~A9      |

| Page size     |                      | 512B            | 1KB     | 2KB        |

### 16 Gb Addressing Table

| Configuration                            |                      | 4 Gb x4 | 2 Gb x8 | 1 Gb x16 |

|------------------------------------------|----------------------|---------|---------|----------|

| # of Bank Groups Bank Address BG Address |                      | 4       | 4       | 2        |

|                                          |                      | BG0~BG1 | BG0~BG1 | BG0      |

|                                          | Bank Address in a BG | BA0~BA1 | BA0~BA1 | BA0~BA1  |

| Ro                                       | ow Address           | A0~A17  | A0~A16  | A0~A16   |

| Column Address                           |                      | A0~A9   | A0~A9   | A0~A9    |

| Page size                                |                      | 512B    | 1KB     | 2KB      |

NOTE 1 : Page size is the number of bytes of data delivered from the array to the internal sense amplifiers when an ACTIVE command is registered.

Page size is per bank, calculated as follows: page size = 2 COLBITS \* ORG÷8

where, COLBITS = the number of column address bits, ORG = the number of I/O (DQ) bits

## 6. Absolute Maximum Ratings

## 6.1 Absolute Maximum DC Ratings

[ Table 4 ] Absolute Maximum DC Ratings

| Symbol                            | Parameter                                        | Rating      | Units | NOTE  |

|-----------------------------------|--------------------------------------------------|-------------|-------|-------|

| VDD                               | Voltage on VDD pin relative to Vss               | -0.3 ~ 1.5  | V     | 1,3   |

| VDDQ                              | Voltage on VDDQ pin relative to Vss              | -0.3 ~ 1.5  | V     | 1,3   |

| VPP                               | Voltage on VPP pin relative to Vss               | -0.3 ~ 3.0  | V     | 4     |

| V <sub>IN,</sub> V <sub>OUT</sub> | Voltage on any pin except VREFCA relative to Vss | -0.3 ~ 1.5  | V     | 1,3,5 |

| T <sub>STG</sub>                  | Storage Temperature                              | -55 to +100 | °C    | 1,2   |

#### NOTE:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300 mV of each other at all times; and VREFCA must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500 mV; VREFCA may be equal to or less than 300 mV

- 4. VPP must be equal or greater than VDD/VDDQ at all times.

- 5. Overshoot area above 1.5 V is specified in section 8.3.4, 8.3.5 and section 8.3.6.

### 6.2 DRAM Component Operating Temperature Range

#### [ Table 5 ] Temperature Range

| Symbol | Parameter                   |            | rating    | Unit | NOTE    |

|--------|-----------------------------|------------|-----------|------|---------|

| T      | Operating Temperature Range | Normal     | 0 to 95   | °C   | 1, 2, 4 |

| OPER   |                             | Industrial | -40 to 95 | °C   | 1, 3, 4 |

#### NOTE:

- 1. Operating Temperature T<sub>OPER</sub> is the case surface temperature on the center/top side of the DRAM.

- 2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0-85°C under all operating conditions

- 3. The Industrial Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between -40-95°C under all operating conditions

- 4. Some applications require operation of the Extended Temperature Range between 85°C and 95°C case temperature. Full specifications are guaranteed in this range, but the following additional conditions apply:

- a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to 3.9us.

- b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 A6 = 0<sub>b</sub> and MR2 A7 = 1<sub>b</sub>).

## 7. AC & DC Operating Conditions

#### [ Table 6 ] Recommended DC Operating Conditions

| Symbol | Parameter                 | Rating |      | Unit | NOTE |       |

|--------|---------------------------|--------|------|------|------|-------|

| Зушьог | raiametei                 | Min.   | Тур. | Max. | Onit | NOIL  |

| VDD    | Supply Voltage            | 1.14   | 1.2  | 1.26 | V    | 1,2,3 |

| VDDQ   | Supply Voltage for Output | 1.14   | 1.2  | 1.26 | V    | 1,2,3 |

| VPP    | Peak-to-Peak Voltage      | 2.375  | 2.5  | 2.75 | V    | 3     |

### NOTE :

- Under all conditions VDDQ must be less than or equal to VDD.

- 2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

- 3. DC bandwidth is limited to 20MHz.

## 8. AC & DC Input Measurement Levels

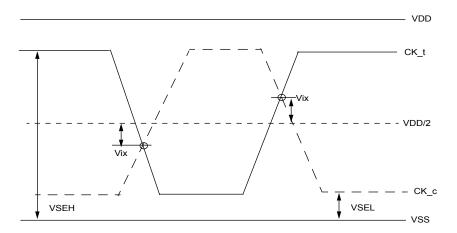

## 8.1 AC & DC Logic Input Levels for Single-ended Signals

[ Table 7 ] Single-ended AC & DC input Levels for Command and Address

| Symbol        | Parameter                             | DDR4-1600/1866/2133/2400 |                      | Unit  | NOTE |

|---------------|---------------------------------------|--------------------------|----------------------|-------|------|

| Symbol        | raiametei                             | Min.                     | Max.                 | Oilit | NOTE |

| VIH.CA(DC75)  | DC input logic high                   | VREFCA+ 0.075            | Vdd                  | V     |      |

| VIL.CA(DC75)  | DC input logic low                    | Vss                      | VREFCA-0.075         | V     |      |

| VIH.CA(AC100) | AC input logic high                   | VREF + 0.1               | Note 2               | V     | 1    |

| VIL.CA(AC100) | AC input logic low                    | Note 2                   | VREF - 0.1           | V     | 1    |

| VREFCA(DC)    | Reference Voltage for ADD, CMD inputs | 0.49*V <sub>DD</sub>     | 0.51*V <sub>DD</sub> | V     | 2,3  |

#### NOTE:

- 1. See "Overshoot and Undershoot Specifications".

- 2. The AC peak noise on VREFCA may not allow VREFCA to deviate from VREFCA(DC) by more than ± 1% VDD (for reference : approx. ± 12mV)

- 3. For reference : approx. VDD/2 ± 12mV

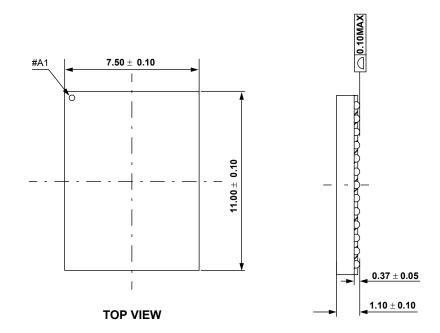

## 8.2 V<sub>RFF</sub> Tolerances

The dc-tolerance limits and ac-noise limits for the reference voltages  $V_{REFCA}$  is illustrated in 1. It shows a valid reference voltage  $V_{REF}(t)$  as a function of time. ( $V_{REF}$  stands for  $V_{REFCA}$  and  $V_{REFCA}$  likewise).

$V_{REF}(DC)$  is the linear average of  $V_{REF}(t)$  over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirement in Table 7 on page 13. Furthermore  $V_{REF}(t)$  may temporarily deviate from  $V_{REF}(DC)$  by no more than  $\pm$  1%  $V_{DD}$ .

Figure 1. Illustration of V<sub>REF</sub>(DC) tolerance and VREF ac-noise limits

The voltage levels for setup and hold time measurements  $V_{IH}(AC)$ ,  $V_{IH}(DC)$ ,  $V_{IL}(AC)$  and  $V_{IL}(DC)$  are dependent on  $V_{REF}$ .

" $V_{REF}$ " shall be understood as  $V_{REF}(DC)$ , as defined in 1.

This clarifies, that dc-variations of  $V_{REF}$  affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to which setup and hold is measured. System timing and voltage budgets need to account for  $V_{REF}(DC)$  deviations from the optimum position within the data-eye of the input signals.

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with  $V_{REF}$  ac-noise. Timing and voltage effects due to ac-noise on  $V_{REF}$  up to the specified limit (+/-1% of  $V_{DD}$ ) are included in DRAM timings and their associated deratings.

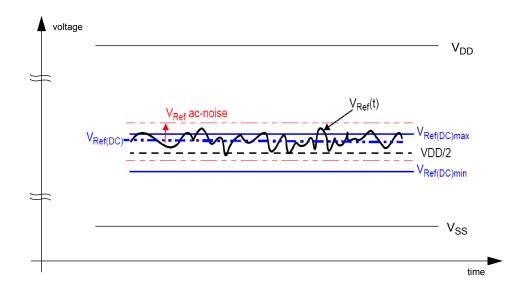

## 8.3 AC & DC Logic Input Levels for Differential Signals

## 8.3.1 Differential Signals Definition

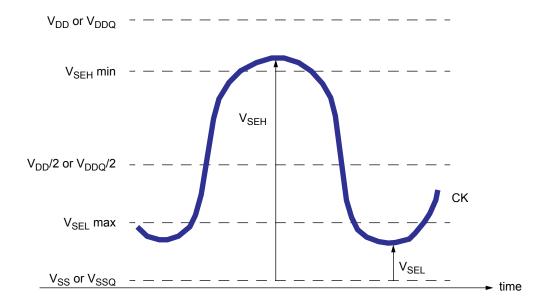

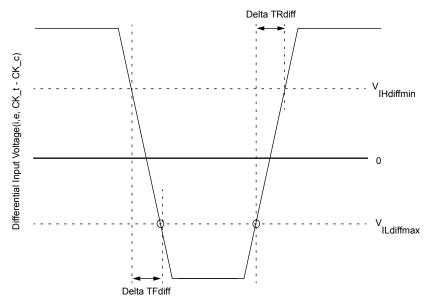

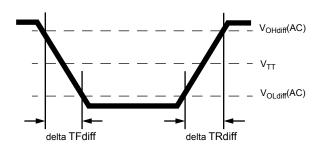

Figure 2. Definition of differential ac-swing and "time above ac level" tDVAC

#### NOTE:

- 1. Differential signal rising edge from VIL.DIFF.MAX to VIH.DIFF.MIN must be monotonic slope.

- 2. Differential signal falling edge from VIH.DIFF.MIN to VIL.DIFF.MAX must be monotonic slope.

## 8.3.2 Differential Swing Requirement for Clock (CK\_t - CK\_c)

[ Table 8 ] Differential AC & DC Input Levels

| Symbol Parameter         |                            | DDR4 -1600/1866/2133                           |                                                | DDR4 -2400                                     |                                                |      | NOTE |

|--------------------------|----------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------|------|

| Symbol                   | Farameter                  | min max min max                                |                                                | max                                            | unit                                           | NOTE |      |

| $V_{IHdiff}$             | differential input high    | +0.150                                         | NOTE 3                                         | TBD                                            | NOTE 3                                         | V    | 1    |

| $V_{ILdiff}$             | differential input low     | NOTE 3                                         | -0.150                                         | NOTE 3                                         | TBD                                            | ٧    | 1    |

| V <sub>IHdiff</sub> (AC) | differential input high ac | 2 x (V <sub>IH</sub> (AC) - V <sub>REF</sub> ) | NOTE 3                                         | 2 x (V <sub>IH</sub> (AC) - V <sub>REF</sub> ) | NOTE 3                                         | ٧    | 2    |

| V <sub>ILdiff</sub> (AC) | differential input low ac  | NOTE 3                                         | 2 x (V <sub>IL</sub> (AC) - V <sub>REF</sub> ) | NOTE 3                                         | 2 x (V <sub>IL</sub> (AC) - V <sub>REF</sub> ) | V    | 2    |

#### NOTE

- 1. Used to define a differential signal slew-rate.

- 2. for CK\_t CK\_c use  $V_{IHCA}/V_{ILCA}(AC)$  of ADD/CMD and  $V_{REFCA}$ ;

- 3. These values are not defined; however, the differential signals CK\_t CK\_c, need to be within the respective limits (V<sub>IHCA</sub>(DC) max, V<sub>ILCA</sub>(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot.

| [ Table 9 ] Allowed Time Before Ringba | ack (tDVAC) for CK_t - CK_c |

|----------------------------------------|-----------------------------|

|----------------------------------------|-----------------------------|

| Slew Rate [V/ns] | tDVAC [ps] @  V <sub>IH/Ldiff</sub> (AC)  = 200mV |     |  |

|------------------|---------------------------------------------------|-----|--|

| olon nato (moj   | min                                               | max |  |

| > 4.0            | 120                                               | -   |  |

| 4.0              | 115                                               | -   |  |

| 3.0              | 110                                               | -   |  |

| 2.0              | 105                                               | -   |  |

| 1.8              | 100                                               | -   |  |

| 1.6              | 95                                                | -   |  |

| 1.4              | 90                                                | -   |  |

| 1.2              | 85                                                | -   |  |

| 1.0              | 80                                                | -   |  |

| < 1.0            | 80                                                | -   |  |

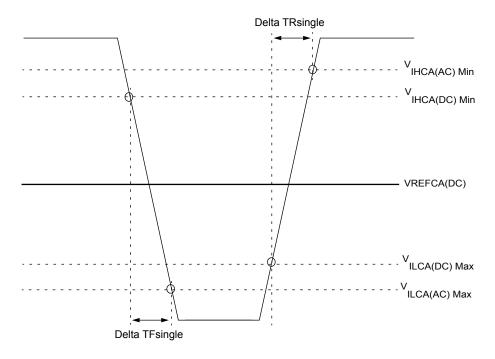

### 8.3.3 Single-ended Requirements for Differential Signals

Each individual component of a differential signal (CK\_t, CK\_c) has also to comply with certain requirements for single-ended signals. CK\_t and CK\_c have to approximately reach  $V_{SEL}$ max [approximately equal to the ac-levels {  $V_{IH.CA}(AC) / V_{IL.CA}(AC)$ } for ADD/CMD signals] in every half-cycle.

Note that the applicable ac-levels for ADD/CMD might be different per speed-bin etc. E.g. if Different value than  $V_{IH.CA}(AC100)/V_{IL.CA}(AC100)$  is used for ADD/CMD signals, then these ac-levels apply also for the single-ended signals CK\_t and CK\_c.

Figure 3. Single-ended requirement for differential signals

Note that while ADD/CMD signal requirements are with respect to  $V_{REFCA}$ , the single-ended components of differential signals have a requirement with respect to  $V_{DD}/2$ ; this is nominally the same. The transition of single-ended signals through the ac-levels is used to measure setup time. For single-ended components of differential signals the requirement to reach  $V_{SEL}$ max,  $V_{SEH}$ min has no bearing on timing, but adds a restriction on the common mode characteristics of these signals.

#### [ Table 10 ] Single-ended Levels for CK\_t, CK\_c

|        | Symbol           | Symbol Parameter                           |               | DDR4-1600/1866/2133 |       | DDR4-2400 |      |      |

|--------|------------------|--------------------------------------------|---------------|---------------------|-------|-----------|------|------|

| Symbol |                  | Farameter                                  | Min           | Max                 | Min   | Max       | Unit | NOTE |

|        | V <sub>SEH</sub> | Single-ended high-level for CK_t , CK_c    | (VDD/2)+0.100 | NOTE3               | TBD   | NOTE3     | V    | 1, 2 |

|        | $V_{SEL}$        | Single-ended low-level for $CK_t$ , $CK_c$ | NOTE3         | (VDD/2)-0.100       | NOTE3 | TBD       | V    | 1, 2 |

#### NOTE:

- 1. For CK\_t CK\_c use  $V_{IH.CA}/V_{IL.CA}(AC)$  of ADD/CMD;

- 2.  $V_{IH}(AC)/V_{IL}(AC)$  for ADD/CMD is based on  $V_{REFCA}$ ;

- 3. These values are not defined, however the single-ended signals CK\_t CK\_c need to be within the respective limits (V<sub>IH.CA</sub>(DC) max, V<sub>IL.CA</sub>(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot.

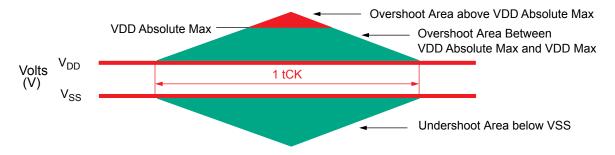

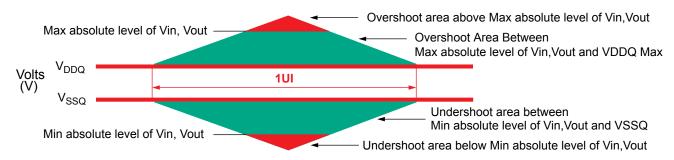

### 8.3.4 Address, Command and Control Overshoot and Undershoot Specifications

[ Table 11 ] AC Overshoot/Undershoot Specification for Address, Command and Control Pins

| Parameter                                                                   |              | Specification |           |                                                                            |      |  |  |  |  |  |  |

|-----------------------------------------------------------------------------|--------------|---------------|-----------|----------------------------------------------------------------------------|------|--|--|--|--|--|--|

| Falanietei                                                                  | DDR4-1600    | DDR4-1866     | DDR4-2133 | DDR4-2400                                                                  | Unit |  |  |  |  |  |  |

| Maximum peak amplitude above VDD Absolute Max allowed for overshoot area    | 0.06         | 0.06          | 0.06      | 0.06                                                                       | V    |  |  |  |  |  |  |

| Delta value between VDD Absolute Max and VDD Max allowed for overshoot area | 0.24         | 0.24          | 0.24      | 0.24                                                                       | V    |  |  |  |  |  |  |

| Maximum peak amplitude allowed for undershoot area                          | 0.3          | 0.3           | 0.3       | 0.3                                                                        | V-ns |  |  |  |  |  |  |

| Maximum overshoot area per 1tCK Above Absolute Max                          | 0.0083       | 0.0071        | 0.0062    | 0.0055                                                                     | V-ns |  |  |  |  |  |  |

| Maximum overshoot area per 1tCK Between Absolute Max and VDD Max            | 0.2550       | 0.2185        | 0.1914    | 0.1699                                                                     | V-ns |  |  |  |  |  |  |

| Maximum undershoot area per 1tCK Below VSS                                  | 0.2644       | 0.2265        | 0.1984    | 0.1762                                                                     | V-ns |  |  |  |  |  |  |

| (A0-A13,BG0-BG1,BA0-BA1,ACT_n,RAS_n,CAS_n/A1                                | 5,WE_n/A14,C | S_n,CKE,OD    | T,C2-C0)  | (A0-A13,BG0-BG1,BA0-BA1,ACT_n,RAS_n,CAS_n/A15,WE_n/A14,CS_n,CKE,ODT,C2-C0) |      |  |  |  |  |  |  |

Figure 4. Address, Command and Control Overshoot and Undershoot Definition

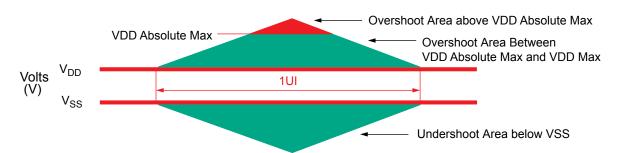

### 8.3.5 Clock Overshoot and Undershoot Specifications

[ Table 12 ] AC Overshoot/Undershoot Specification for Clock

| Parameter                                                                   |           | Specification |           |           |      |  |

|-----------------------------------------------------------------------------|-----------|---------------|-----------|-----------|------|--|

| raianietei                                                                  | DDR4-1600 | DDR4-1866     | DDR4-2133 | DDR4-2400 | Unit |  |

| Maximum peak amplitude above VDD Absolute Max allowed for overshoot area    | 0.06      | 0.06          | 0.06      | 0.06      | V    |  |

| Delta value between VDD Absolute Max and VDD Max allowed for overshoot area | 0.24      | 0.24          | 0.24      | 0.24      | V    |  |

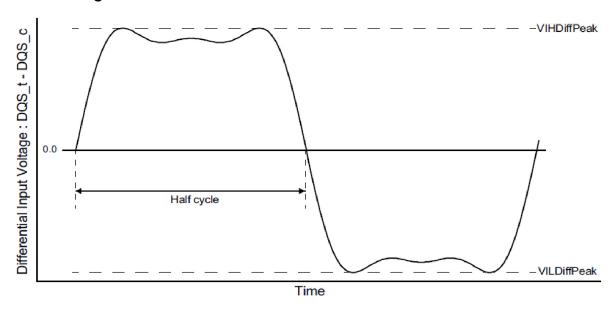

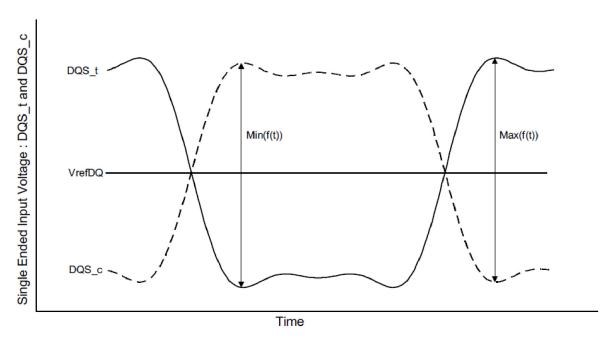

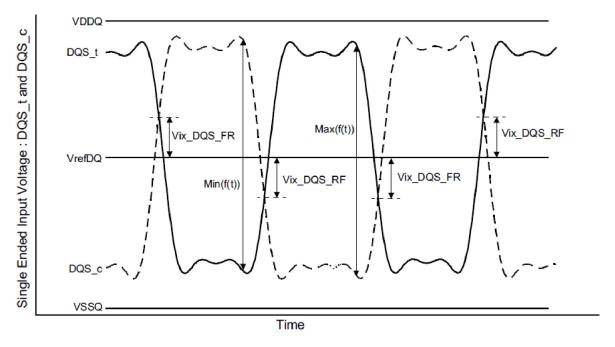

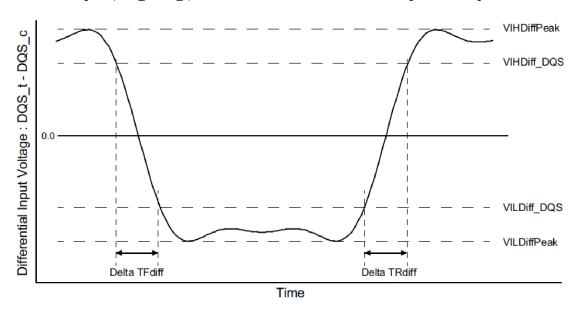

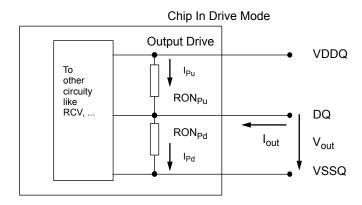

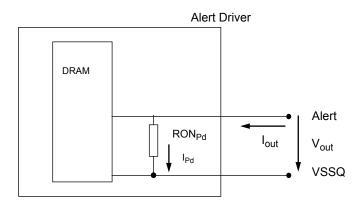

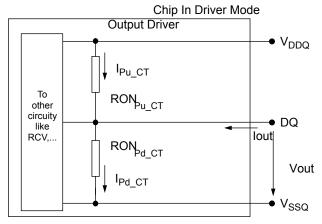

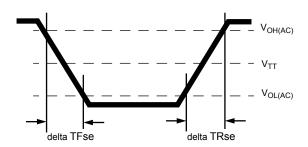

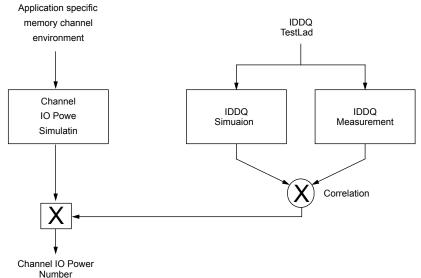

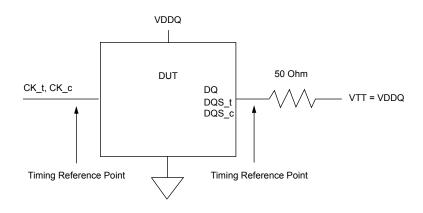

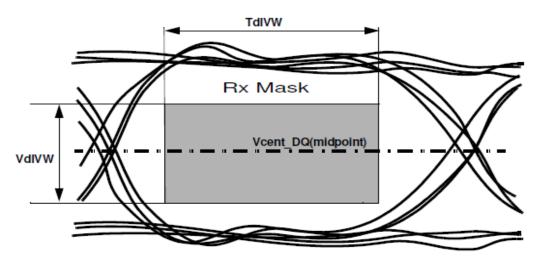

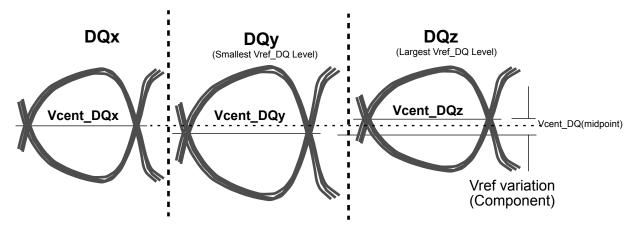

| Maximum peak amplitude allowed for undershoot area                          | 0.3       | 0.3           | 0.3       | 0.3       | V    |  |