## 2M x 16Bit x 4 Banks Mobile SDRAM in 54FBGA

## **FEATURES**

- 3.0V & 3.3V power supply.

- · LVCMOS compatible with multiplexed address.

- · Four banks operation.

- MRS cycle with address key programs.

- -. CAS latency (1, 2 & 3).

- -. Burst length (1, 2, 4, 8 & Full page).

- -. Burst type (Sequential & Interleave).

- · EMRS cycle with address key programs.

- All inputs are sampled at the positive going edge of the system clock.

- Burst read single-bit write operation.

- · Special Function Support.

- -. PASR (Partial Array Self Refresh).

- -. Internal TCSR (Temperature Compensated Self Refresh)

- · DQM for masking.

- · Auto refresh.

- 64ms refresh period (4K cycle).

- Commercial Temperature Operation (-25°C ~ 70°C).

- Extended Temperature Operation (-25°C ~ 85°C).

- 54Balls FBGA with 0.8mm ball pitch

(-RXXX: Leaded, -BXXX: Lead Free).

## **GENERAL DESCRIPTION**

The K4M281633F is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 16 bits, fabricated with SAMSUNG's high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock and I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst lengths and programmable latencies allow the same device to be useful for a variety of high bandwidth and high performance memory system applications.

#### ORDERING INFORMATION

| Part No.                     | Max Freq.      | Interface | Package                       |

|------------------------------|----------------|-----------|-------------------------------|

| K4M281633F-R(B)E/N/G/C/L/F75 | 133MHz(CL=3)   |           |                               |

| K4M281633F-R(B)E/N/G/C/L/F1H | 105MHz(CL=2)   | LVCMOS    | 54 FBGA<br>Leaded (Lead Free) |

| K4M281633F-R(B)E/N/G/C/L/F1L | 105MHz(CL=3)*1 |           |                               |

- R(B)E/N/G : Normal / Low / Low Power, Extended Temperature(-25°C  $\sim$  85°C)

- R(B)C/L/F : Normal / Low / Low Power, Commercial Temperature(-25°C ~ 70°C)

#### NOTES

- 1. In case of 40MHz Frequency, CL1 can be supported.

- 2. Samsung are not designed or manufactured for use in a device or system that is used under circumstance in which human life is potentially at stake. Please contact to the memory marketing team in samsung electronics when considering the use of a product contained herein for any specific purpose, such as medical, aerospace, nuclear, military, vehicular or undersea repeater use.

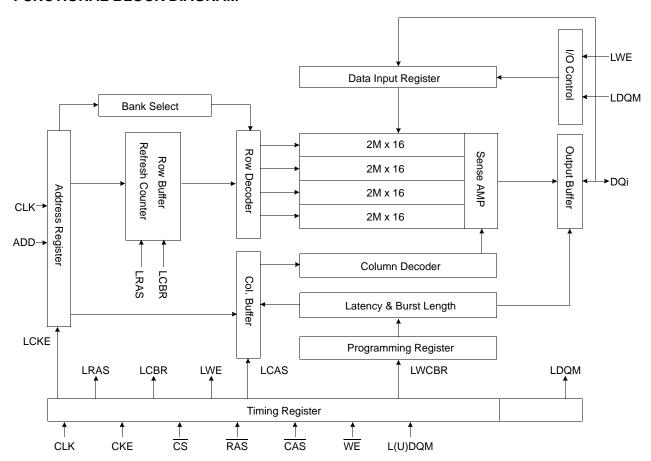

## **FUNCTIONAL BLOCK DIAGRAM**

# **Package Dimension and Pin Configuration**

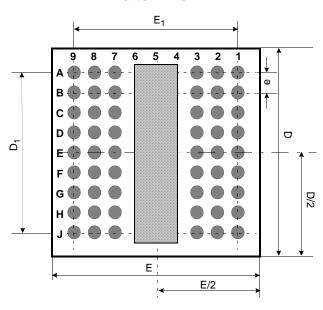

| 54Ball(6x9) FBGA |      |      |      |      |      |     |  |  |  |  |  |  |

|------------------|------|------|------|------|------|-----|--|--|--|--|--|--|

|                  | 1    | 2    | 3    | 7    | 8    | 9   |  |  |  |  |  |  |

| Α                | VSS  | DQ15 | VSSQ | VDDQ | DQ0  | VDD |  |  |  |  |  |  |

| В                | DQ14 | DQ13 | VDDQ | VSSQ | DQ2  | DQ1 |  |  |  |  |  |  |

| С                | DQ12 | DQ11 | VSSQ | VDDQ | DQ4  | DQ3 |  |  |  |  |  |  |

| D                | DQ10 | DQ9  | VDDQ | VSSQ | DQ6  | DQ5 |  |  |  |  |  |  |

| Е                | DQ8  | NC   | VSS  | VDD  | LDQM | DQ7 |  |  |  |  |  |  |

| F                | UDQM | CLK  | CKE  | CAS  | RAS  | WE  |  |  |  |  |  |  |

| G                | NC   | A11  | A9   | BA0  | BA1  | CS  |  |  |  |  |  |  |

| Н                | A8   | A7   | A6   | A0   | A1   | A10 |  |  |  |  |  |  |

| J                | VSS  | A5   | A4   | A3   | A2   | VDD |  |  |  |  |  |  |

| Pin Name      | Pin Function             |

|---------------|--------------------------|

| CLK           | System Clock             |

| <del>CS</del> | Chip Select              |

| CKE           | Clock Enable             |

| A0 ~ A11      | Address                  |

| BA0 ~ BA1     | Bank Select Address      |

| RAS           | Row Address Strobe       |

| CAS           | Column Address Strobe    |

| WE            | Write Enable             |

| L(U)DQM       | Data Input/Output Mask   |

| DQ0 ~ 15      | Data Input/Output        |

| VDD/Vss       | Power Supply/Ground      |

| VDDQ/VSSQ     | Data Output Power/Ground |

Тур

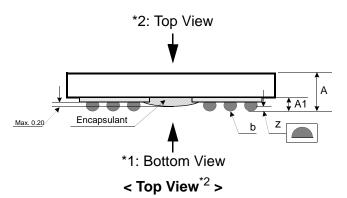

#A1 Ball Origin Indicator

Α 0.90 0.95  $A_1$ 0.30 0.35 Ε 8.00 6.40  $E_1$ D 8.00  $D_1$ 6.40 е 0.80 0.45 b 0.40

Min

**Symbol**

z

[Unit:mm]

Max

1.00

0.40

0.50

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                             | Symbol    | Value      | Unit |

|---------------------------------------|-----------|------------|------|

| Voltage on any pin relative to Vss    | VIN, VOUT | -1.0 ~ 4.6 | V    |

| Voltage on VDD supply relative to Vss | Vdd, Vddq | -1.0 ~ 4.6 | V    |

| Storage temperature                   | Тѕтс      | -55 ~ +150 | °C   |

| Power dissipation                     | Po        | 1.0        | W    |

| Short circuit current                 | los       | 50         | mA   |

#### NOTES:

Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

## DC OPERATING CONDITIONS

Recommended operating conditions (Voltage referenced to Vss = 0V, TA = -25 to 85°C for Extended, -25 to 70°C for Commercial)

| Parameter                 | Symbol | Min  | Тур | Max        | Unit | Note       |

|---------------------------|--------|------|-----|------------|------|------------|

| Supply voltage            | VDD    | 2.7  | 3.0 | 3.6        | V    |            |

| Supply voltage            | VDDQ   | 2.7  | 3.0 | 3.6        | V    |            |

| Input logic high voltage  | ViH    | 2.2  | 3.0 | VDDQ + 0.3 | V    | 1          |

| Input logic low voltage   | VIL    | -0.3 | 0   | 0.5        | V    | 2          |

| Output logic high voltage | Voн    | 2.4  | -   | -          | V    | Iон = -2mA |

| Output logic low voltage  | Vol    | -    | -   | 0.4        | V    | IoL = 2mA  |

| Input leakage current     | lu     | -10  | -   | 10         | uA   | 3          |

### NOTES:

- 1. VIH (max) = 5.3V AC.The overshoot voltage duration is  $\leq$  3ns.

- 2. VIL (min) = -2.0V AC. The undershoot voltage duration is  $\leq$  3ns.

- 3. Any input  $0V \le VIN \le VDDQ$ .

- Input leakage currents include Hi-Z output leakage for all bi-directional buffers with tri-state outputs.

- 4. Dout is disabled,  $0V \le VOUT \le VDDQ$ .

# $\textbf{CAPACITANCE} \text{ (VDD = 3.0V \& 3.3V, TA = 23°C, f = 1MHz, VREF = 0.9V <math>\pm 50 \text{ mV})}$

| Pin                        | Symbol | Min | Max | Unit | Note |

|----------------------------|--------|-----|-----|------|------|

| Clock                      | Сськ   | 2.0 | 4.0 | pF   |      |

| RAS, CAS, WE, CS, CKE, DQM | CIN    | 2.0 | 4.0 | pF   |      |

| Address                    | CADD   | 2.0 | 4.0 | pF   |      |

| DQ0 ~ DQ15                 | Соит   | 3.0 | 6.0 | pF   |      |

## **DC CHARACTERISTICS**

Recommended operating conditions (Voltage referenced to Vss = 0V, TA = -25 to  $85^{\circ}C$  for Extended, -25 to  $70^{\circ}C$  for Commercial)

| B                                             | 0      |                                                             |                   |                      |           | Versio | n         | Unit | Nete |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

|-----------------------------------------------|--------|-------------------------------------------------------------|-------------------|----------------------|-----------|--------|-----------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------------|-----|--|-----|--|--|

| Parameter                                     | Symbol | les                                                         | st Condi          | tion                 | -75       | -1H    | -1L       | Unit | Note |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Operating Current<br>(One Bank Active)        | Icc1   | Burst length = 1<br>tRC ≥ tRC(min)<br>lo = 0 mA             |                   |                      | 80        | 75     | 75        | mA   | 1    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Precharge Standby Current in                  | Icc2P  | CKE ≤ VIL(max), tcc                                         | c = 10ns          |                      |           | 0.5    |           | mA   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| power-down mode                               | Icc2PS | CKE & CLK ≤ VIL(m                                           | ax), tcc :        | = ∞                  |           | 0.5    | MA        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Precharge Standby Current                     | Icc2N  | CKE ≥ VIH(min), CS<br>Input signals are ch                  |                   |                      |           | 12     | mA        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| in non power-down mode                        | Icc2NS | CKE ≥ VIH(min), CL<br>Input signals are sta                 | K ≤ Vı∟(n<br>able | $nax), tcc = \infty$ |           | 10     |           | IIIA |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Active Standby Current                        | ІссзР  | CKE ≤ VIL(max), tcc                                         | c = 10ns          |                      | 7         |        |           | mA   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| in power-down mode                            | Icc3PS | CKE & CLK ≤ VIL(m                                           | ax), tcc =        | = ∞                  |           | 7      |           | ш    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Active Standby Current in non power-down mode | ІссзN  | CKE ≥ VIH(min), CS<br>Input signals are ch                  |                   | 23                   |           |        | mA        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| (One Bank Active)                             | Icc3NS | CKE ≥ VIH(min), CL<br>Input signals are sta                 | ,                 | nax), $tcc = \infty$ |           | 20     |           | mA   |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Operating Current<br>(Burst Mode)             | Icc4   | Io = 0 mA<br>Page burst<br>4Banks Activated<br>tccb = 2CLKs |                   |                      | 130       | 130    | 110       | mA   | 1    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Refresh Current                               | lcc5   | trc ≥ trc(min)                                              |                   |                      | 170       | 170    | 155       | mA   | 2    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

|                                               |        |                                                             |                   | -E/C                 |           | 700    |           | uA   | 4    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

|                                               |        |                                                             |                   | -N/L                 |           | 500    |           | uA   | 5    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Self Refresh Current                          | Icc6   | CKE ≤ 0.2V                                                  |                   | Internal TCSR        | Max 4     | 0 N    | lax 85/70 | °C   | 3    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

| Jen Kenesh Curtent                            | 1000   | ONE SULEV                                                   | -G/F              | -G/F                 | -G/F      | -G/F   | -G/F      | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | -G/F | Full Array | 350 |  | 500 |  |  |

|                                               |        | -                                                           | -3/1              | 1/2 of Full Array    | y 300 400 |        | uA        | 6    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

|                                               |        |                                                             | 1/4 of Full Array | 280                  |           | 360    |           |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |            |     |  |     |  |  |

#### NOTES:

- 1. Measured with outputs open.

- 2. Refresh period is 64ms.

- 3. Internal TCSR can be supported.

In commercial Temp : Max  $40^{\circ}$ C/Max  $70^{\circ}$ C, In extended Temp : Max  $40^{\circ}$ C/Max  $85^{\circ}$ C

- 4. K4M281633F-R(B)E/C\*\*

- 5. K4M281633F-R(B)N/L\*\*

- 6. K4M281633F-R(B)G/F\*\*

- 7. Unless otherwise noted, input swing level is CMOS(VIH /VIL=VDDQ/VSSQ).

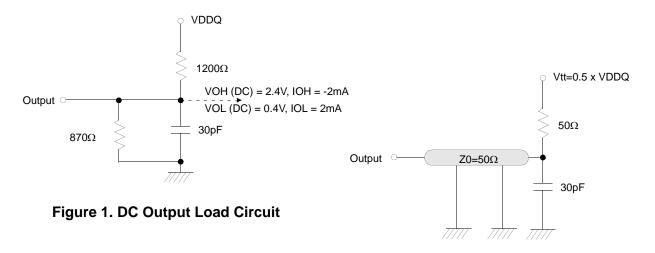

## AC OPERATING TEST CONDITIONS (VDD = 2.7V ~ 3.6V, TA = -25 to 85°C for Extended, -25 to 70°C for Commercial)

| Parameter                                 | Value        | Unit |

|-------------------------------------------|--------------|------|

| AC input levels (Vih/Vil)                 | 2.4 / 0.4    | V    |

| Input timing measurement reference level  | 0.5 x Vddq   | V    |

| Input rise and fall time                  | tr/tf = 1/1  | ns   |

| Output timing measurement reference level | 0.5 x Vddq   | V    |

| Output load condition                     | See Figure 2 |      |

Figure 2. AC Output Load Circuit

## **OPERATING AC PARAMETER**

(AC operating conditions unless otherwise noted)

| Parameter                       |          | Cumbal        |     | Version    |     | Unit   | Note |

|---------------------------------|----------|---------------|-----|------------|-----|--------|------|

| Parameter                       |          | Symbol        | -75 | -1H        | -1L | - Unit | Note |

| Row active to row active delay  |          | trrd(min)     | 15  | 19         | 19  | ns     | 1    |

| RAS to CAS delay                |          | trcd(min)     | 19  | 19         | 24  | ns     | 1    |

| Row precharge time              |          | trp(min)      | 19  | 19         | 24  | ns     | 1    |

| Row active time                 |          | tras(min)     | 45  | 50         | 60  | ns     | 1    |

|                                 |          | tras(max)     |     | 100        | us  |        |      |

| Row cycle time                  |          | trc(min)      | 64  | 69         | 84  | ns     | 1    |

| Last data in to row precharge   |          | tRDL(min)     |     | 2          | CLK | 2      |      |

| Last data in to Active delay    |          | tDAL(min)     |     | tRDL + tRP | -   | 3      |      |

| Last data in to new col. addres | ss delay | tcdl(min)     |     | 1          |     | CLK    | 2    |

| Last data in to burst stop      |          | tBDL(min)     |     | 1          |     | CLK    | 2    |

| Col. address to col. address d  | elay     | tccd(min)     |     | 1          |     | CLK    | 4    |

| Number of valid output data     | C        | CAS latency=3 |     | 2          |     |        |      |

| Number of valid output data     | C        | CAS latency=2 |     | 1          | ea  | 5      |      |

| Number of valid output data     | C        | CAS latency=1 |     | 0          |     |        |      |

#### NOTES:

<sup>1.</sup> The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then rounding off to the next higher integer.

<sup>2.</sup> Minimum delay is required to complete write.

<sup>3.</sup> Minimum tRDL=2CLK and tDAL(= tRDL + tRP) is required to complete both of last data write command(tRDL) and precharge command(tRP).

<sup>4.</sup> All parts allow every cycle column address change.

<sup>5.</sup> In case of row precharge interrupt, auto precharge and read burst stop.

## AC CHARACTERISTICS (AC operating conditions unless otherwise noted)

| Paramete                  | _                      | Symbol | -7  | 75   |     | IH.  |     | 1L   | Unit | Note |

|---------------------------|------------------------|--------|-----|------|-----|------|-----|------|------|------|

| Paramete                  | r                      | Symbol | Min | Max  | Min | Max  | Min | Max  | Unit | Note |

| CLK cycle time            | CAS latency=3          | tcc    | 7.5 |      | 9.5 |      | 9.5 |      |      |      |

| CLK cycle time            | CAS latency=2          | tcc    | 9.5 | 1000 | 9.5 | 1000 | 12  | 1000 | ns   | 1    |

| CLK cycle time            | CAS latency=1          | tcc    | -   |      | -   |      | 25  |      |      |      |

| CLK to valid output delay | CAS latency=3          | tsac   |     | 5.4  |     | 7    |     | 7    |      |      |

| CLK to valid output delay | CAS latency=2          | tsac   |     | 7    |     | 7    |     | 8    | ns   | 1,2  |

| CLK to valid output delay | CAS latency=1          | tsac   |     | -    |     | -    |     | 20   |      |      |

| Output data hold time     | CAS latency=3          | tон    | 2.5 |      | 2.5 |      | 2.5 |      |      |      |

| Output data hold time     | CAS latency=2          | tон    | 2.5 |      | 2.5 |      | 2.5 |      | ns   | 2    |

| Output data hold time     | CAS latency=1          | tон    | -   |      | -   |      | 2.5 |      |      |      |

| CLK high pulse width      |                        | tсн    | 2.5 |      | 3.0 |      | 3.0 |      | ns   | 3    |

| CLK low pulse width       |                        | tcL    | 2.5 |      | 3.0 |      | 3.0 |      | ns   | 3    |

| Input setup time          |                        | tss    | 2.0 |      | 2.5 |      | 2.5 |      | ns   | 3    |

| Input hold time           |                        | tsн    | 1.0 |      | 1.5 |      | 1.5 |      | ns   | 3    |

| CLK to output in Low-Z    | CLK to output in Low-Z |        | 1   |      | 1   |      | 1   |      | ns   | 2    |

|                           | CAS latency=3          |        |     | 5.4  |     | 7    |     | 7    |      |      |

| CLK to output in Hi-Z     | CAS latency=2          | tsHZ   |     | 7    |     | 7    |     | 8    | ns   |      |

|                           | CAS latency=1          |        |     | -    |     | -    |     | 20   |      |      |

#### NOTES:

<sup>1.</sup> Parameters depend on programmed CAS latency.

<sup>2.</sup> If clock rising time is longer than 1ns, (tr/2-0.5)ns should be added to the parameter.

<sup>3.</sup> Assumed input rise and fall time (tr & tf) = 1ns.

If tr & tf is longer than 1ns, transient time compensation should be considered,

i.e., [(tr + tf)/2-1]ns should be added to the parameter.

#### SIMPLIFIED TRUTH TABLE

| С                                | OMMAND          |              | CKEn-1 | CKEn | cs | RAS | CAS | WE       | DQM | BA0,1 | A10/AP   | A11,<br>A9 ~ A0    | Note |

|----------------------------------|-----------------|--------------|--------|------|----|-----|-----|----------|-----|-------|----------|--------------------|------|

| Register                         | Mode Regis      | ster Set     | Н      | Х    | L  | L   | L   | L        | Х   |       | OP COI   | DE                 | 1, 2 |

|                                  | Auto Refres     | sh           | Н      | Н    | L  | L   | L   | Н        | Х   |       | Х        |                    | 3    |

| Refresh                          | 0.11            | Entry        |        | L    | _  | _   | _   | ''       | ^   |       | ^        |                    | 3    |

| Reliesii                         | Self<br>Refresh | Exit         | L      | Н    | L  | Н   | Н   | Н        | х   |       | Х        |                    | 3    |

|                                  |                 | LXII         | _      | "    | Н  | Х   | Х   | Х        | ^   |       | <b>X</b> |                    | 3    |

| Bank Active & Ro                 | ow Addr.        |              | Н      | Х    | L  | L   | Н   | Н        | Х   | V     | Row      | Address            |      |

| Read &                           |                 | arge Disable |        | .,   |    |     |     |          |     | .,    | L        | Column             | 4    |

| Column Address                   | Auto Precha     | arge Enable  | Н      | X    | L  | Н   | L   | Н        | Х   | V     | Н        | Address<br>(A0~A8) | 4, 5 |

| Column Address                   |                 | arge Disable | – H    | V    |    |     |     | L        | V   | V     | L        | Column             | 4    |

|                                  |                 | arge Enable  |        | Х    | L  | Н   | L   | <u> </u> | Х   | V     | Н        | Address<br>(A0~A8) | 4, 5 |

| Burst Stop                       |                 |              | Н      | Х    | L  | Н   | Н   | L        | Х   |       | Х        |                    | 6    |

| Precharge                        | Bank Selection  |              | Н      | Х    | L  | L   | Н   | L        | Х   | V     | L        | Х                  |      |

| Frecharge                        | All Banks       |              | 11     | ^    | L  | _   | "   | L        | ^   | Х     | Н        | ^                  |      |

|                                  | 1               | Entry        | Н      |      | Н  | Х   | Х   | Х        | х   |       |          |                    |      |

| Clock Suspend of Active Power Do |                 | Entry        | П      | L    | L  | V   | ٧   | V        | ^   | X     |          |                    |      |

|                                  |                 | Exit         | L      | Н    | Χ  | Х   | Х   | Х        | Х   |       |          |                    |      |

|                                  |                 | Entry        | Н      | L    | Н  | Х   | Х   | Х        | х   |       |          |                    |      |

| Precharge Powe                   | r Down          | Entry        | П      | _    | L  | Н   | Н   | Н        | ^   |       | Х        |                    |      |

| Mode                             |                 | Exit         |        | Н    | Н  | Х   | Х   | Х        | х   |       | ^        |                    |      |

|                                  |                 | EXIL         | L      | П    | L  | V   | V   | V        | ^   |       |          |                    |      |

| DQM                              |                 | I            | Н      |      |    | Х   |     | 1        | V   |       | Х        |                    | 7    |

| No Operation Co                  |                 |              |        | Х    | Н  | Х   | Х   | Х        | V   |       | ~        |                    |      |

| No Operation Co                  | rrimana         |              | Н      | X    | L  | Н   | Н   | Н        | Х   |       | Χ        |                    |      |

(V=Valid, X=Don't Care, H=Logic High, L=Logic Low)

#### NOTES:

- 1. OP Code: Operand Code

- A0 ~ A11 & BA0 ~ BA1 : Program keys. (@MRS)

- 2. MRS can be issued only at all banks precharge state.

- A new command can be issued after 2 CLK cycles of MRS.

- 3. Auto refresh functions are the same as CBR refresh of DRAM.

- The automatical precharge without row precharge command is meant by "Auto".

- Auto/self refresh can be issued only at all banks precharge state.

- Partial self refresh can be issued only after setting partial self refresh mode of EMRS.

- 4. BA0 ~ BA1 : Bank select addresses.

- 5. During burst read or write with auto precharge, new read/write command can not be issued. Another bank read/write command can be issued after the end of burst.

- New row active of the associated bank can be issued at tRP after the end of burst.

- 6. Burst stop command is valid at every burst length.

- 7. DQM sampled at the positive going edge of CLK masks the data-in at that same CLK in write operation (Write DQM latency is 0), but in read operation, it makes the data-out Hi-Z state after 2 CLK cycles. (Read DQM latency is 2).

## A. MODE REGISTER FIELD TABLE TO PROGRAM MODES

Register Programmed with Normal MRS

| Address  | BA0 ~ BA1                     | A11 ~ A10/AP      | <b>A9</b> *2 | A8              | A7 | A6 | A5       | A4  | А3 | A2 | <b>A</b> 1 | Α0  |

|----------|-------------------------------|-------------------|--------------|-----------------|----|----|----------|-----|----|----|------------|-----|

| Function | "0" Setting for<br>Normal MRS | RFU <sup>*1</sup> | W.B.L        | W.B.L Test Mode |    | CA | AS Later | псу | вт | Bu | rst Lenç   | gth |

## **Normal MRS Mode**

|    | -     | Test Mode         | CAS Latency |    |    |          |     | Burst       | Туре                | Burst Length |            |    |           |          |  |

|----|-------|-------------------|-------------|----|----|----------|-----|-------------|---------------------|--------------|------------|----|-----------|----------|--|

| A8 | Α7    | Туре              | A6          | A5 | A4 | Latency  | А3  | Туре        |                     | A2           | <b>A</b> 1 | A0 | BT=0      | BT=1     |  |

| 0  | 0     | Mode Register Set | 0           | 0  | 0  | Reserved | 0   | Sequential  |                     | 0            | 0          | 0  | 1         | 1        |  |

| 0  | 1     | Reserved          | 0           | 0  | 1  | 1        | 1   | Interleave  |                     | 0            | 0          | 1  | 2         | 2        |  |

| 1  | 0     | Reserved          | 0           | 1  | 0  | 2        | ı   | Mode Select |                     |              | 1          | 0  | 4         | 4        |  |

| 1  | 1     | Reserved          | 0           | 1  | 1  | 3        | BA1 | BA0         | Mode                | 0            | 1          | 1  | 8         | 8        |  |

|    | Write | Burst Length      | 1           | 0  | 0  | Reserved |     |             |                     | 1            | 0          | 0  | Reserved  | Reserved |  |

| Α9 |       | Length            | 1           | 0  | 1  | Reserved | 0   | 0           | Setting<br>for Nor- | 1            | 0          | 1  | Reserved  | Reserved |  |

| 0  | Burst |                   | 1           | 1  | 0  | Reserved | J   | U           | mal MRS             | 1            | 1          | 0  | Reserved  | Reserved |  |

| 1  |       | Single Bit        | 1           | 1  | 1  | Reserved |     |             |                     | 1            | 1          | 1  | Full Page | Reserved |  |

Full Page Length x16: 128Mb(512)

## Register Programmed with Extended MRS

| Address  | BA1  | BA0    | A11 ~ A10/AP | A9                | A8 | A7 | A6 | A5 | A4    | А3 | A2   | A1 | A0 |

|----------|------|--------|--------------|-------------------|----|----|----|----|-------|----|------|----|----|

| Function | Mode | Select |              | RFU <sup>*1</sup> |    |    | D  | S  | RFU*1 |    | PASR |    |    |

# EMRS for PASR(Partial Array Self Ref.) & DS(Driver Strength)

|       |       | Mode Selec | t          |        | Driver Strength |                       |           |          |          | PASR |                         |                   |  |  |  |

|-------|-------|------------|------------|--------|-----------------|-----------------------|-----------|----------|----------|------|-------------------------|-------------------|--|--|--|

| BA1   | BA0   |            | Mode       |        |                 | A6 A5 Driver Strength |           | A2       | A2 A1 A0 |      | Size of Refreshed Array |                   |  |  |  |

| 0     | 0     | No         | rmal MRS   |        | 0               | 0                     | Full      |          | 0        | 0    | 0                       | Full Array        |  |  |  |

| 0     | 1     | R          | eserved    |        | 0 1             |                       |           | 1/2      | 0        | 0    | 1                       | 1/2 of Full Array |  |  |  |

| 1     | 0     | EMRS for   | Mobile SDR | AM     | 1 0             |                       | Reserved  |          | 0        | 1    | 0                       | 1/4 of Full Array |  |  |  |

| 1     | 1     | R          | eserved    |        | 1               | 1                     | R         | Reserved |          | 1    | 1                       | Reserved          |  |  |  |

|       |       |            | Reserved A | Addres | ss              |                       |           |          | 1        | 0    | 0                       | Reserved          |  |  |  |

| A11~A | 10/AP | A9         | A8         | А      | 7               | Δ                     | <b>\4</b> | А3       | 1        | 0    | 1                       | Reserved          |  |  |  |

| 0     |       | 0          | 0          | (      | )               |                       | 0         | 0        | 1        | 1    | 0                       | Reserved          |  |  |  |

|       |       |            |            |        |                 |                       |           |          | 1        | 1    | 1                       | Reserved          |  |  |  |

1.RFU(Reserved for future use) should stay "0" during MRS cycle.

2.If A9 is high during MRS cycle, "Burst Read Single Bit Write" function will be enabled.

## **Partial Array Self Refresh**

- 1. In order to save power consumption, Mobile SDRAM has PASR option.

- 2. Mobile SDRAM supports 3 kinds of PASR in self refresh mode :Full Array, 1/2 of Full Array and 1/4 of Full Array.

| BA1=0 | BA1=0 |

|-------|-------|

| BA0=0 | BA0=1 |

| BA1=1 | BA1=1 |

| BA0=0 | BA0=1 |

BA1=0 BA0=0 BA0=1 BA1=1 BA0=0 BA1=1 BA0=1 BA1=0 BA0=0 BA0=1 BA1=1 BA0=0 BA1=1 BA0=1

- Full Array

- 1/2 Array

- 1/4 Array

Partial Self Refresh Area

## Internal Temperature Compensated Self Refresh (TCSR)

- 1. In order to save power consumption, Mobile-DRAM includes the internal temperature sensor and control units to control the self refresh cycle automatically according to the two temperature range: Max 40 °C and Max 85 °C(for Extended), Max 70 °C(for Commercial).

- 2. If the EMRS for external TCSR is issued by the controller, this EMRS code for TCSR is ignored.

| Temperature Range | - E/C | - N/L |                                                |     | Unit |    |  |

|-------------------|-------|-------|------------------------------------------------|-----|------|----|--|

|                   | - E/C | - N/L | Full Array 1/2 of Full Array 1/4 of Full Array |     |      |    |  |

| Max 85/70 °C      | 700   | 500   | 500                                            | 400 | 360  | uA |  |

| Max 40 °C         | 700   | 300   | 350                                            | 300 | 280  | uA |  |

#### **B. POWER UP SEQUENCE**

- 1. Apply power and attempt to maintain CKE at a high state and all other inputs may be undefined.

- Apply VDD before or at the same time as VDDQ.

- 2. Maintain stable power, stable clock and NOP input condition for a minimum of 200us.

- 3. Issue precharge commands for all banks of the devices.

- 4. Issue 2 or more auto-refresh commands.

- 5. Issue a mode register set command to initialize the mode register.

- 6. Issue a extended mode register set command to define DS or PASR operating type of the device after normal MRS.

EMRS cycle is not mandatory and the EMRS command needs to be issued only when DS or PASR is used.

The default state without EMRS command issued is full driver strength and full array refreshed.

The device is now ready for the operation selected by EMRS.

For operating with DS or PASR , set DS or PASR mode in EMRS setting stage.

In order to adjust another mode in the state of DS or PASR mode, additional EMRS set is required but power up sequence is not needed again at this time. In that case, all banks have to be in idle state prior to adjusting EMRS set.

## **C. BURST SEQUENCE**

## 1. BURST LENGTH = 4

| Initial Address |    |   | Sean | ential  |   | Interleave |   |   |   |  |  |  |

|-----------------|----|---|------|---------|---|------------|---|---|---|--|--|--|

| A1              | A0 |   | Jequ | Cilliai |   | interieuve |   |   |   |  |  |  |

| 0               | 0  | 0 | 1    | 2       | 3 | 0          | 1 | 2 | 3 |  |  |  |

| 0               | 1  | 1 | 2    | 3       | 0 | 1          | 0 | 3 | 2 |  |  |  |

| 1               | 0  | 2 | 3    | 0       | 1 | 2          | 3 | 0 | 1 |  |  |  |

| 1               | 1  | 3 | 0    | 1       | 2 | 3          | 2 | 1 | 0 |  |  |  |

## 2. BURST LENGTH = 8

| Init | ial Addr | ess |   |   |   | Sean | ential  |   |   | Interleave |   |   |   |   |   |   |   |   |

|------|----------|-----|---|---|---|------|---------|---|---|------------|---|---|---|---|---|---|---|---|

| A2   | A1       | A0  |   |   |   | Jequ | Cilliai |   |   |            |   |   |   |   |   |   |   |   |

| 0    | 0        | 0   | 0 | 1 | 2 | 3    | 4       | 5 | 6 | 7          | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 0    | 0        | 1   | 1 | 2 | 3 | 4    | 5       | 6 | 7 | 0          | 1 | 0 | 3 | 2 | 5 | 4 | 7 | 6 |

| 0    | 1        | 0   | 2 | 3 | 4 | 5    | 6       | 7 | 0 | 1          | 2 | 3 | 0 | 1 | 6 | 7 | 4 | 5 |

| 0    | 1        | 1   | 3 | 4 | 5 | 6    | 7       | 0 | 1 | 2          | 3 | 2 | 1 | 0 | 7 | 6 | 5 | 4 |

| 1    | 0        | 0   | 4 | 5 | 6 | 7    | 0       | 1 | 2 | 3          | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 |

| 1    | 0        | 1   | 5 | 6 | 7 | 0    | 1       | 2 | 3 | 4          | 5 | 4 | 7 | 6 | 1 | 0 | 3 | 2 |

| 1    | 1        | 0   | 6 | 7 | 0 | 1    | 2       | 3 | 4 | 5          | 6 | 7 | 4 | 5 | 2 | 3 | 0 | 1 |

| 1    | 1        | 1   | 7 | 0 | 1 | 2    | 3       | 4 | 5 | 6          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |