## **Eight Channel Programmable** High Voltage Ultrasound Transmit Beamformer

#### Features

- Eight channels with return to zero

- Up to ±70V output voltage

- ±3.0A output current

- Store up to four different patterns

- Independent programmable delays

- Single 11x11 QFN-80 package

#### Application

- Medical ultrasound imaging

- NDT, non-destructive testing

- Arbitrary pattern generator

- High speed PIN diode driver

#### **General Description**

The Supertex HV7351 is an 8-channel programmable high voltage ultrasound transmit beamformer. Each channel is capable of swinging up to ±70V with an active discharge back to 0V. The outputs can source and sink more than 3.0A to achieve fast output rise and fall times. The active discharge is also capable of sourcing and sinking 3.0A for a fast return to ground. The topology of the HV7351 will significantly reduce the number of I/O logic control lines needed.

Each pulser has four associated 64-bit shift registers for storing pre-determined transmit patterns and a 10-bit delay counter for controlling the transmit time. One of four arbitrary patterns can be transmitted with adjustable delay, depending on the data loaded into these shift registers and the delay counter. The delay counter can be clocked up to 200MHz, allowing incremental delays down to 5ns.

Doc.# DSFP-HV7351 A011314

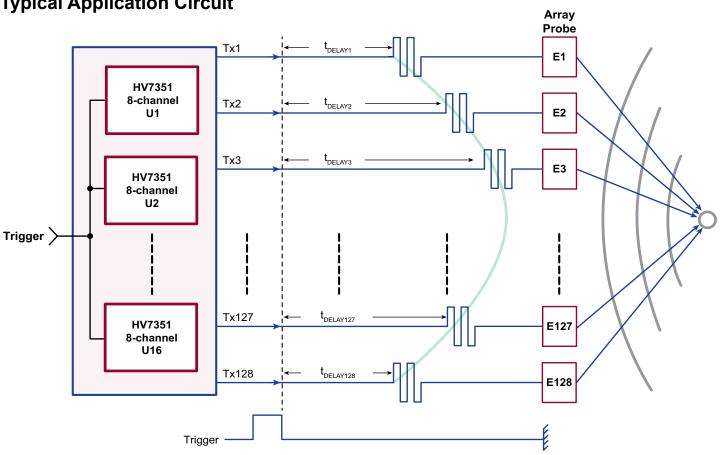

#### **Typical Application Circuit**

#### **Ordering Information**

| Part Number | Package Option      | Packing  |

|-------------|---------------------|----------|

| HV7351K6-G  | 80-Lead QFN (11x11) | 176/Tray |

-G denotes a lead (Pb)-free / RoHS compliant package

#### Absolute Maximum Ratings

| Parameter                                                                      | Value                                          |

|--------------------------------------------------------------------------------|------------------------------------------------|

| V <sub>LL</sub> , Positive logic supply                                        | -0.5V to 5.5V                                  |

| DV <sub>DD</sub> , Positive logic supply voltage                               | -0.5V to 5.5V                                  |

| $PV_{_{DD}},$ Positive gate drive supply voltage                               | -0.5V to 5.5V                                  |

| $AV_{DD}$ , Positive analog supply voltage                                     | -0.5V to 5.5V                                  |

| $PV_{_{SS}}$ , Negative gate drive supply voltage                              | +0.5V to -5.5V                                 |

| $V_{_{PP}}$ , High voltage positive supply voltage                             | -0.5V to +80V                                  |

| $V_{_{\rm NN}}$ , High voltage negative supply voltage                         | +0.5V to -80V                                  |

| $(V_{_{\mathrm{PP}}} - V_{_{\mathrm{NN}}})$ , Differential high voltage supply | +160V                                          |

| $V_{\mbox{\tiny PF}}$ Positive floating supply voltage                         | $V_{_{\rm PP}}\text{-}6.0V$ to $V_{_{\rm PP}}$ |

| $V_{\rm NF}$ , Negative floating supply voltage                                | $V_{_{\rm NN}}$ to $V_{_{\rm NN}}$ +6.0V       |

| $V_{_{\rm RP^{\!\prime}}}$ Positive supply for $V_{_{\rm NF}}$ regulator       | 0V to 15V                                      |

| $V_{_{\!R\!N}\!},$ Negative supply for $V_{_{\!P\!F}}$ regulator               | 0V to -15V                                     |

| Operating temperature                                                          | -40°C to +125°C                                |

| Storage temperature                                                            | -65°C to +150°C                                |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### **Pin Configuration**

#### Package Marking

| •<br>HV7351K6 | L = Lot Number<br>YY = Year Sealed |

|---------------|------------------------------------|

| LLLLLLLL      | WW = Week Sealed                   |

| YYWW          | A = Assembler ID                   |

| AAA CCC       | C = Country of Origin              |

|               | = "Green" Packaging                |

Package may or may not include the following marks: Si or 🎲

80-Lead QFN

#### **Typical Thermal Resistance**

| Package     | $oldsymbol{	heta}_{ja}$ |

|-------------|-------------------------|

| 80-Lead QFN | 14°C/W                  |

#### **Operating Supply Voltages**

$(T_{i} = 25^{\circ}C \text{ unless otherwise specified})$

| Sym              | Parameter                                      | Min   | Тур   | Max   | Units | Conditions |

|------------------|------------------------------------------------|-------|-------|-------|-------|------------|

| V <sub>PP</sub>  | Positive high voltage supply                   | 3.0   | -     | 70    | V     |            |

| V <sub>NN</sub>  | Negative high voltage supply                   | -70   | -     | -3.0  | V     |            |

| V                | Logic interface voltage                        | 2.85  | 3.30  | 3.6   | V     |            |

| AV <sub>DD</sub> | Low voltage positive analog supply voltage     | 4.75  | 5.00  | 5.25  | V     |            |

|                  | Low voltage positive digital<br>supply voltage | 4.75  | 5.00  | 5.25  | V     |            |

| PV <sub>DD</sub> | Low voltage positive gate drive supply voltage | 4.75  | 5.00  | 5.25  | V     |            |

| PV <sub>ss</sub> | Low voltage negative gate drive supply voltage | -5.25 | -5.00 | -4.75 | V     |            |

# **Operating Supply Voltages (cont.)** (*T*<sub>1</sub> = 25°C unless otherwise specified)

| Sym              | Parameter                                         | Min         | Тур                | Max                | Units | Conditions                           |

|------------------|---------------------------------------------------|-------------|--------------------|--------------------|-------|--------------------------------------|

| $V_{RP}$         | Low voltage positive supply for VNF regulator     | 4.75        | -                  | 12                 | V     |                                      |

| $V_{RN}$         | Low voltage negative supply for VPF regulator     | -12         | -                  | -4.75              | V     |                                      |

| TCK              | Reference voltage logic trip<br>point for TCK pin | $0.4V_{LL}$ | 0.5V <sub>LL</sub> | 0.6V <sub>LL</sub> | V     |                                      |

| I <sub>тск</sub> | TCK input current                                 | -           | -                  | ±10                | μA    | $V_{\overline{TCK}} = 0$ to $V_{LL}$ |

**Regulator Outputs** (Operating conditions unless otherwise specified,  $V_{LL} = 3.3V$ ,  $AV_{DD} = DV_{DD} = PV_{DD} = V_{RP} = 5.0V$ ,  $PV_{SS} = V_{RN} = -5.0V$ ,  $V_{PP} = +70V$ ,  $V_{NN} = -70V$ ,  $T_{J} = 25^{\circ}$ C)

| Sym         | Parameter                            | Min                   | Тур                   | Max                   | Units | Conditions                                                              |

|-------------|--------------------------------------|-----------------------|-----------------------|-----------------------|-------|-------------------------------------------------------------------------|

| $V_{PF}$    | Positive floating gate drive voltage | V <sub>PP</sub> -5.25 | V <sub>PP</sub> -5.00 | V <sub>PP</sub> -4.00 | V     | 4.0µF ceramic capacitor across $V_{_{\rm PF}}$ and $V_{_{\rm PP}}$      |

| $V_{_{NF}}$ | Negative floating gate drive voltage | V <sub>NN</sub> +4.00 | V <sub>NN</sub> +5.00 | V <sub>NN</sub> +5.25 | V     | $4.0\mu F$ ceramic capacitor across $V_{_{\rm NF}}$ and $V_{_{\rm NN}}$ |

#### **Electrical Characteristics**

(Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $PV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $T_{J}$  = 25°C)

| Sym                 | Parameter                                  | Min  | Тур   | Max | Units | Conditions                       |

|---------------------|--------------------------------------------|------|-------|-----|-------|----------------------------------|

| I <sub>vllq</sub>   | V <sub>LL</sub> quiescent current          | -    | 384   | 500 | μA    | EN = Low, all inputs are static  |

| I <sub>AVDDQ</sub>  | AV <sub>DD</sub> quiescent current         | -    | 12    | 30  |       |                                  |

| I <sub>dvddq</sub>  | DV <sub>DD</sub> quiescent current         | -    | 12    | 30  | μA    | EN = Low, all inputs are static  |

| I <sub>pvddq</sub>  | PV <sub>DD</sub> quiescent current         | -    | 70    | 100 |       |                                  |

| I <sub>vrpq</sub>   | V <sub>RP</sub> quiescent current          | -    | 0.3   | 6.0 |       | EN = Low, all inputs are static  |

| I <sub>vrnq</sub>   | V <sub>RN</sub> quiescent current          | -    | -0.01 | 6.0 | μA    | EN – Low, all inputs are static  |

| I <sub>PVSSQ</sub>  | PV <sub>ss</sub> quiescent current         | -85  | -45   | -   | μA    | EN = Low, all inputs are static  |

| I <sub>vppq</sub>   | V <sub>PP</sub> quiescent current          | -    | 2.6   | 6.0 |       | EN = Low, all inputs are static  |

| I <sub>VNNQ</sub>   | V <sub>NN</sub> quiescent current          | -    | -1.6  | 6.0 | μA    | EN – Low, all inputs are static  |

|                     | V <sub>LL</sub> enabled quiescent current  | -    | 390   | 500 | μA    | EN = High, all inputs are static |

| I <sub>AVDDEN</sub> | $AV_{_{DD}}$ enabled quiescent current     | -    | 600   | 800 |       | EN - High all inputs are static  |

|                     | $DV_{_{DD}}$ enabled quiescent current     | -    | 22    | 55  | μA    | EN = High, all inputs are static |

|                     | $PV_{_{DD}}$ enabled quiescent current     | -    | 44    | 100 | μA    | EN = High, all inputs are static |

| I <sub>vrpen</sub>  | $V_{_{\rm RP}}$ enabled quiescent current  | -    | 450   | 650 |       | EN - High all inputs are static  |

| I <sub>VRNEN</sub>  | $V_{_{RN}}$ enabled quiescent current      | -650 | -350  | -   | μA    | EN = High, all inputs are static |

| I <sub>PVSSEN</sub> | PV <sub>ss</sub> enabled quiescent current | -100 | -44   | -   | μA    | EN = High, all inputs are static |

| I <sub>VPPEN</sub>  | V <sub>PP</sub> enabled quiescent current  | -    | 370   | 620 |       | EN - High all inputs are static  |

| I <sub>vnnen</sub>  | $V_{_{NN}}$ enabled quiescent current      | -620 | -420  | -   | μA    | EN = High, all inputs are static |

**Electrical Characteristics (cont.)** (Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $PV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $T_{J}$  = 25°C)

| Sym                 | Parameter                              | Min | Тур | Max | Units | Conditions                                                                      |

|---------------------|----------------------------------------|-----|-----|-----|-------|---------------------------------------------------------------------------------|

| I <sub>VLLCW</sub>  | V <sub>LL</sub> current at TCK = 80MHz | -   | 500 | -   | μA    |                                                                                 |

| I <sub>DVDDCW</sub> | DV <sub>DD</sub> current at CW = 5MHz  | -   | 25  | -   | mA    | $V_{PP}$ = +5.0V, $V_{NN}$ = -5.0V, EN = High,<br>CW = High, 80MHz on TCK, 0.5V |

| I <sub>VPPCW</sub>  | V <sub>PP</sub> current at CW = 5MHz   | -   | 141 | -   | mA    | on TCK, all 8 channels active at                                                |

| I <sub>VNNCW</sub>  | V <sub>NN</sub> current at CW = 5MHz   | -   | 98  | -   | mA    | 5.0MHz, No load                                                                 |

**AC Electrical Characteristics** (Operating conditions unless otherwise specified,  $V_{LL} = 3.3V$ ,  $AV_{DD} = DV_{DD} = PV_{DD} = V_{RP} = 5.0V$ ,  $PV_{SS} = V_{RN} = -5.0V$ ,  $V_{PP} = +70V$ ,  $V_{NN} = -70V$ ,  $T_{J} = 25^{\circ}$ C)

| Sym                     | Parameter                                      | Min                     | Тур | Max | Units   | Conditions                                        |

|-------------------------|------------------------------------------------|-------------------------|-----|-----|---------|---------------------------------------------------|

| f <sub>тск</sub>        | Transmit clock frequency                       | 0                       | -   | 200 | MHz     |                                                   |

| £                       | Carial clash fragmanan                         | 0                       | -   | 80  | N 41 1- | No daisy chain                                    |

| f <sub>scк</sub>        | Serial clock frequency                         | 0                       | -   | 70  | MHz     | Daisy chained                                     |

| t <sub>su-DIN</sub>     | Set-up time data in to SCK                     | 2.0                     | 1.0 | -   | ns      |                                                   |

| t <sub>H-DIN</sub>      | Hold time SCK to data in                       | 2.0                     | 1.0 | -   | ns      |                                                   |

| t <sub>su-cs1</sub>     | Set-up time $\overline{\text{CS1}}$ low to SCK | 2.0                     | -   | -   | ns      |                                                   |

| $t_{\overline{SU-CS2}}$ | Set-up time $\overline{\text{CS2}}$ low to SCK | 2.0                     | -   | -   | ns      |                                                   |

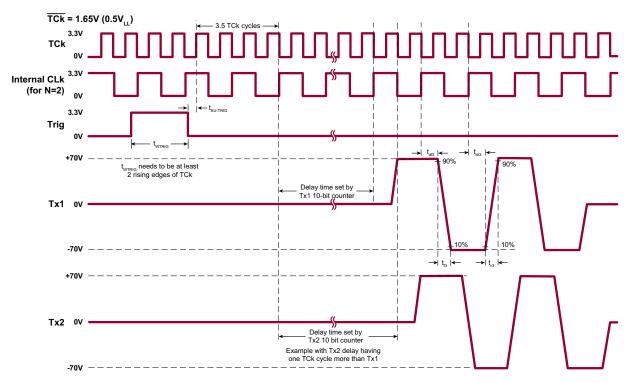

| t <sub>su-trig</sub>    | Set-up time TRIG low to TCK                    | 2.0                     | -   | -   | ns      |                                                   |

| t <sub>w-TRIG</sub>     | TRIG pulse width                               | 2TCK                    | -   | -   | -       |                                                   |

|                         | SCK to data out low to high                    | 3.0                     | 9.0 | 12  |         | For D <sub>out</sub> 1                            |

| t <sub>lhdo</sub>       | delay time                                     | 3.0                     | 9.0 | 10  | ns      | For D <sub>out</sub> 2                            |

| 4                       | SCK to data out high to low                    | 3.0                     | 9.0 | 12  |         | For D <sub>out</sub> 1                            |

| t <sub>HLDO</sub>       | delay time                                     | 3.0                     | 9.0 | 10  | ns      | For D <sub>out</sub> 2                            |

| t <sub>wa1A0</sub>      | A1A0 pulse width                               | t <sub>w-TRIG</sub> +40 | -   | -   |         |                                                   |

| t <sub>sua1a0</sub>     | Set-up time A1A0 to TRIG rising edge           | -                       | 20  | -   | ns      |                                                   |

| t <sub>HA1A0</sub>      | Hold time A1A0 to TRIG falling edge            | -                       | 20  | -   |         |                                                   |

| t <sub>en-on</sub>      | Device enable time                             | -                       | 1.0 | -   | ms      | 1.0µF capacitor on every VPF and VNF pin.         |

| t <sub>en-off</sub>     | Device disable time                            | -                       | -   | 100 | ns      |                                                   |

| t <sub>r1</sub>         | Output rise time from 0V to +HV                | -                       | 9.0 | 13  |         |                                                   |

| t <sub>f1</sub>         | Output fall time from 0V to -HV                | -                       | 9.0 | 13  |         |                                                   |

| t <sub>r2</sub>         | Damping output rise time from<br>-HV to 0V     | -                       | 9.0 | 13  |         |                                                   |

| t <sub>f2</sub>         | Damping output fall time from<br>+HV to 0V     | -                       | 9.0 | 13  | ns      | Load = 330pF//2.5kΩ                               |

| t <sub>r3</sub>         | Output rise time from -HV to +HV               | -                       | 17  | 23  | 1       |                                                   |

| t <sub>r3</sub>         | Output fall time from +HV to -HV               | -                       | 17  | 23  | 1       |                                                   |

| t <sub>rcw</sub>        | CW output rise time                            | -                       | 9.0 | 16  |         | V <sub>PP</sub> = +5.0V, V <sub>NN</sub> = -5.0V, |

| t <sub>fcw</sub>        | CW output fall time                            | -                       | 9.0 | 16  | ns      | Load = $330 \text{pF}//2.5 \text{k}\Omega$        |

#### AC Electrical Characteristics (cont.)

(Operating conditions unless otherwise specified,  $V_{LL}$  = 3.3V,  $AV_{DD}$  =  $DV_{DD}$  =  $PV_{DD}$  =  $V_{RP}$  = 5.0V,  $PV_{SS}$  =  $V_{RN}$  = -5.0V,  $V_{PP}$  = +70V,  $V_{NN}$  = -70V,  $T_{J}$  = 25°C)

| Sym                    | Parameter                                         | Min    | Тур    | Max    | Units | Conditions                                                           |  |

|------------------------|---------------------------------------------------|--------|--------|--------|-------|----------------------------------------------------------------------|--|

| t <sub>dr1</sub>       | Output propagation delay rise time 1              | 10.85  | 13.35  | 15.85  |       |                                                                      |  |

| t <sub>df1</sub>       | Output propagation delay fall time 1              | 11.35  | 13.85  | 16.35  |       |                                                                      |  |

| t <sub>dr2</sub>       | Output propagation delay rise time 2              | 11.25  | 13.75  | 16.25  |       | Notood                                                               |  |

| t <sub>df2</sub>       | Output propagation delay fall time 2              | 11.75  | 14.25  | 16.75  | ns    | No Load.                                                             |  |

| t <sub>dr3</sub>       | Output propagation delay rise time 3              | 11.35  | 13.85  | 16.35  |       |                                                                      |  |

| t <sub>df3</sub>       | Output propagation delay fall time 3              | 11.45  | 13.95  | 16.45  | -     |                                                                      |  |

| t <sub>dcwlh</sub>     | CW output propagation delay time from low to high | 10.45  | 12.95  | 15.45  |       | V <sub>PP</sub> = +5.0V, V <sub>NN</sub> = -5.0V,                    |  |

| t <sub>dcwhl</sub>     | CW output propagation delay time from high to low | 10.35  | 12.85  | 15.35  | ns    | No Load                                                              |  |

| $\Delta t_{\rm dcwhl}$ | Delay time matching                               | -      | ±0.7   | -      | ns    | P to N, channel-to-channel matching                                  |  |

| t <sub>JCW</sub>       | Delay jitter on rise or fall                      | -      | 13     | -      | ps    | $V_{_{\rm PP}}$ = +5.0V, $V_{_{\rm NN}}$ = -5.0V, Load = 50 $\Omega$ |  |

| LAT                    | Latency                                           | 3.5TCK | 3.5TCK | 3.5TCK | -     |                                                                      |  |

#### Output P-channel MOSFET to $V_{PP}$ , CW = 0

| I <sub>OUT</sub> | Output saturation current | 2.2 | 3.2 | - | Α  |                                                     |

|------------------|---------------------------|-----|-----|---|----|-----------------------------------------------------|

| $R_{ON}$         | Output ON-resistance      | -   | 4.2 | - | Ω  | I <sub>out</sub> = 100mA                            |

| C <sub>oss</sub> | Output capacitance        | -   | 62  | - | pF | V <sub>PP</sub> -V <sub>OUT</sub> = 25V, f = 1.0MHz |

#### Output N-channel MOSFET to $V_{NN}$ , CW = 0

| I <sub>OUT</sub> | Output saturation current | - | -3.2 | -2.2 | Α  |                                                       |

|------------------|---------------------------|---|------|------|----|-------------------------------------------------------|

| R <sub>on</sub>  | Output ON-resistance      | - | 2.4  | -    | Ω  | I <sub>out</sub> = -100mA                             |

| C <sub>oss</sub> | Output capacitance        | - | 50   | -    | pF | V <sub>NN</sub> - V <sub>OUT</sub> = -25V, f = 1.0MHz |

#### Output P-channel MOSFET to $V_{PP}$ , CW = 1

| I <sub>OUT</sub> | Output saturation current | 1.2 | 1.5 | - | Α  |                                                     |

|------------------|---------------------------|-----|-----|---|----|-----------------------------------------------------|

| R <sub>on</sub>  | Output ON-resistance      | -   | 8.0 | - | Ω  | I <sub>out</sub> = 100mA                            |

| C <sub>oss</sub> | Output capacitance        | -   | 62  | - | pF | V <sub>PP</sub> -V <sub>OUT</sub> = 25V, f = 1.0MHz |

#### Output N-channel MOSFET to $V_{NN}$ , CW = 1

| I | I <sub>OUT</sub> | Output saturation current | - | -1.5 | -1.2 | А  |                                                       |

|---|------------------|---------------------------|---|------|------|----|-------------------------------------------------------|

| F | R <sub>on</sub>  | Output ON-resistance      | - | 6.6  | -    | Ω  | I <sub>out</sub> = -100mA                             |

| C | C <sub>oss</sub> | Output capacitance        | - | 50   | -    | pF | V <sub>NN</sub> - V <sub>OUT</sub> = -25V, f = 1.0MHz |

#### AC Electrical Characteristics (cont.)

|                                                   | •                     | ,                      |                     |                     |                     |                          |                            |                            |

|---------------------------------------------------|-----------------------|------------------------|---------------------|---------------------|---------------------|--------------------------|----------------------------|----------------------------|

| (Operating conditions unless otherwise specified, | V <sub>LL</sub> =3.3V | $V, AV_{DD} = DV_{DD}$ | $_{DD} = PV_{DD} =$ | $V_{RP} = 5.0V, PV$ | $V_{SS} = V_{RN} =$ | -5.0V, V <sub>PP</sub> = | +70V, V <sub>NN</sub> = -7 | 0V, T <sub>J</sub> = 25°C) |

| Sym                | Parameter                        | Min                  | Тур  | Мах                | Units | Conditions                                                       |

|--------------------|----------------------------------|----------------------|------|--------------------|-------|------------------------------------------------------------------|

| Dam                | oing P-channel MOSFE             | T to PG              | ND   |                    |       |                                                                  |

| Ι <sub>ουτ</sub>   | Output saturation current        | 2.2                  | 3.2  | -                  | A     |                                                                  |

| $R_{ON}$           | Output ON-resistance             | -                    | 4.0  | -                  | Ω     | I <sub>out</sub> = 100mA                                         |

| C <sub>oss</sub>   | Output capacitance               | -                    | 62   | -                  | pF    | V <sub>PP</sub> -V <sub>OUT</sub> = 25V, f = 1.0MHz              |

|                    | oing N-channel MOSFE             | T to PG              | ND   |                    |       |                                                                  |

| I <sub>OUT</sub>   | Output saturation current        | -                    | -3.2 | -2.2               | A     |                                                                  |

| R <sub>on</sub>    | Output ON-resistance             | -                    | 2.3  | -                  | Ω     | I <sub>out</sub> = -100mA                                        |

| $C_{\mathrm{oss}}$ | Output capacitance               | -                    | 50   | -                  | pF    | V <sub>NN</sub> - V <sub>OUT</sub> = -25V, f = 1.0MHz            |

|                    | c Inputs                         |                      |      |                    |       |                                                                  |

| I <sub>тск</sub>   | Input current for TCK            | -                    | ±1.0 | -                  | μA    | $V_{\overline{TCK}} = 0$ to $V_{LL}$                             |

| $V_{\rm IH}$       | Input logic high voltage for TCK | TCK<br>+0.15         | TCK  | V <sub>LL</sub>    | V     | Only for $\overline{\text{TCK}}$ input, TCK = 0.5V <sub>LL</sub> |

| V <sub>IL</sub>    | Input logic low voltage for TCK  | 0                    | TCK  | TCK<br>-0.15       | V     | Only for $\overline{\text{TCK}}$ input, TCK = 0.5V <sub>LL</sub> |

| $V_{\rm IH}$       | Input logic high voltage         | $0.8V_{LL}$          | -    | V <sub>LL</sub>    | V     | For all logic inputs except TCK                                  |

| $V_{\rm IL}$       | Input logic low voltage          | 0                    | -    | 0.2V <sub>LL</sub> | V     | For all logic inputs except TCK                                  |

| I <sub>IH</sub>    | Input logic high current         | -                    | -    | 1.0                | μA    |                                                                  |

| I <sub>IL</sub>    | Input logic low current          | -1.0                 | -    | -                  | μA    |                                                                  |

| $V_{OL}$           | Output logic low voltage         | 0                    | -    | 0.7                | V     | I <sub>out</sub> = 0 to -10mA                                    |

| $V_{OH}$           | Output logic high voltage        | V <sub>LL</sub> -0.7 | -    | V <sub>LL</sub>    | V     | I <sub>out</sub> = 0 to 10mA                                     |

| C                  | Input logic capacitance          | -                    | -    | 5.0                | pF    |                                                                  |

#### Logic Truth Table

|                                                               |    |    | Input             | S   |     |     |                       | Outputs | 5                                                                                 |                                                                                                                                |  |

|---------------------------------------------------------------|----|----|-------------------|-----|-----|-----|-----------------------|---------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Mode                                                          | EN | cw | 10-bit<br>Counter | INV | NIN | PIN | N-ch                  | P-ch    | RTZ                                                                               | Comments                                                                                                                       |  |

|                                                               | 1  | 0  | х                 | х   | 0   | 0   | OFF                   | OFF     | ON                                                                                | RTZ (return-to-zero) is activat-<br>ed when NIN and PIN are both<br>low. Output is pulled to ground<br>through a series diode. |  |

| Non-CW mode.<br>Outputs not inverted.<br>Outputs are con-     | 1  | 0  | х                 | 0   | 0   | 1   | OFF                   | ON      | OFF                                                                               | Not inverted. Logic 1 in the<br>P-channel register turns on the<br>output P-channel MOSFET.                                    |  |

| trolled by data in the shift registers                        | 1  | 0  | х                 | 0   | 1   | 0   | ON                    | OFF     | OFF                                                                               | Not inverted. Logic 1 in the<br>N-channel register turns on the<br>output N-channel MOSFET.                                    |  |

|                                                               | 1  | 0  | х                 | х   | 1   | 1   | OFF                   | OFF     | OFF                                                                               | Avoids cross over current. A<br>logic 1 in both P- and N-chan-<br>nel registers will put the output<br>in a Hi-Z state.        |  |

| Non-CW mode.<br>Outputs are inverted.                         | 1  | 0  | х                 | 1   | 0   | 1   | ON                    | OFF     | OFF                                                                               | Inverted, for harmonic imaging                                                                                                 |  |

| Outputs are con-<br>trolled by data in the<br>shift registers | 1  | 0  | х                 | 1   | 1   | 0   | OFF                   | ON      | OFF                                                                               | Inverted, for harmonic imaging                                                                                                 |  |

| CW mode.                                                      | 1  | х  | All 1             | Х   | х   | х   | OFF                   | OFF     | OFF                                                                               | Off channels are the ones with all 1's in their respective 10-bit counters. Output follows the f <sub>cw</sub>                 |  |

| Output follows fcw                                            | 1  | 1  | Not all 1         | х   | х   | х   | signal. Shift registe |         | signal. Shift registers for NIN<br>and PIN should remain static to<br>save power. |                                                                                                                                |  |

| Device Disabled                                               | 0  | Х  | Х                 | Х   | Х   | Х   | OFF                   | OFF     | OFF                                                                               | Hi-Z state                                                                                                                     |  |

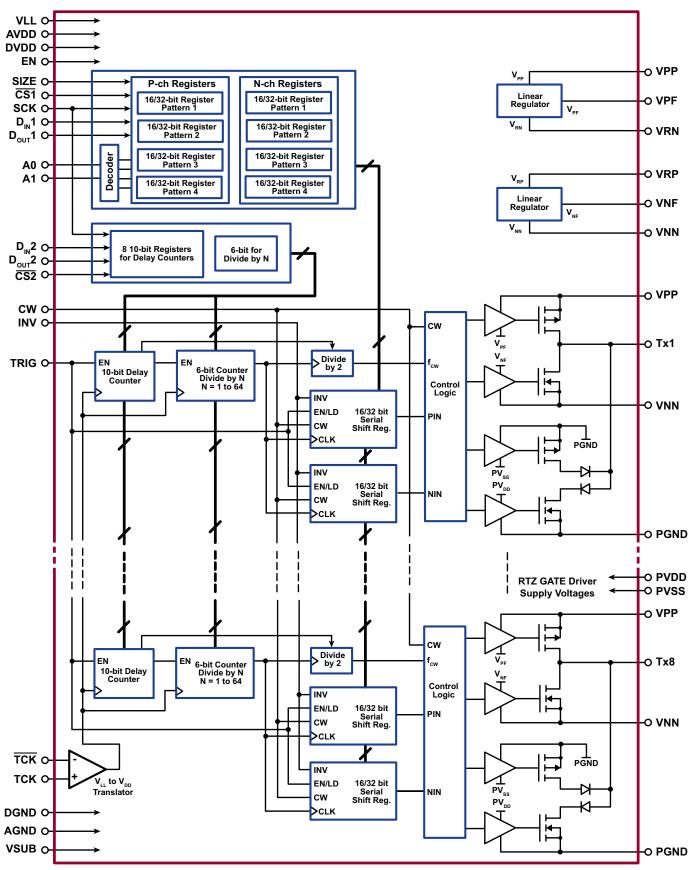

#### **Block Diagram**

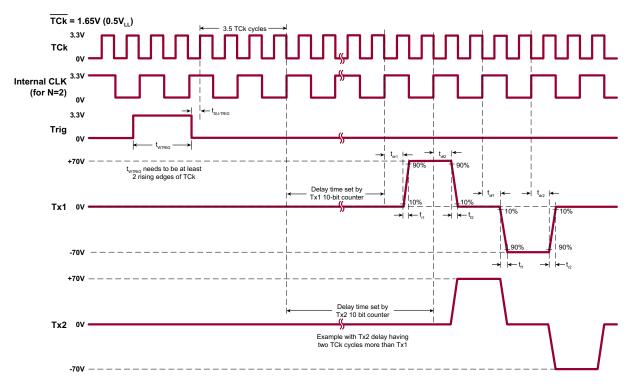

#### Timing Diagram 1

#### **Timing Diagram 2**

Doc.# DSFP-HV7351 A011314

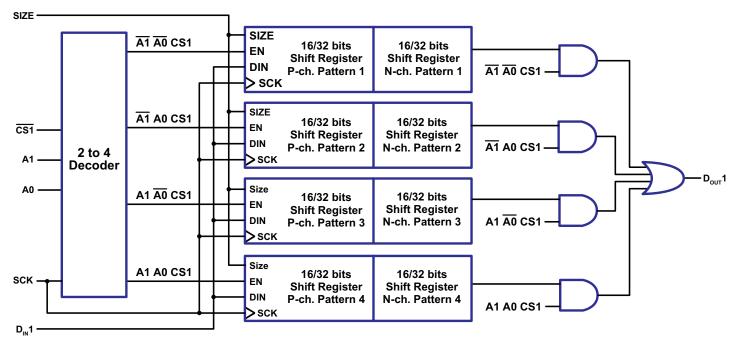

#### Pattern Register Circuit Diagram

#### Loading Data into the Four 16/32 bit Pattern Registers

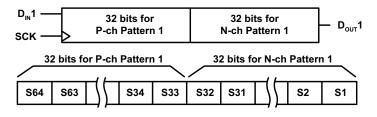

A detailed circuit diagram of the pattern registers is shown above. There are 4 programmable patterns that can be stored. One of four patterns can be selected via the two input logic decoder pins, A1 and A0. Data can be loaded on the selected pattern. Each pattern can be either 16 or 32 bits wide. The SIZE pin determines whether they are 16 or 32 bits wide. SIZE = H will set the pattern to be 32 bits wide while SIZE = L will set it to 16 bits wide. D<sub>IN</sub>1 is the input data for the register. When  $\overline{CS1}$  is high, data will not be shifted in. Data is shifted in only when  $\overline{CS1}$  is low.

With SIZE = H, the circuit is effectively a 64-bit serial shift register. The data first enters into the P-channel register and continues to be shifted though to the N-channel register. Data is clocked in during the rising edge of the clock. There is no activity during the falling edge of the clock. The data,  $D_{IN}$ 1, enters from the P-channel register and exits from the N-channel register from  $D_{OUT}$ 1.

For size = High, 32 bits wide (size = Low, 16-bits wide) A1 = A0 = Low, Pattern 1 selected  $\overline{CS1} = Low$ , data can be shifted in 64-bit serial shift register: 32 bits for the P-channel and

**32 bits for the N-channel** Data is shifted in during the rising edge of the clock. S1 is the first bit shifted in entering the P-channel register. After

Data is shifted in during the rising edge of the clock. S1 is the first bit shifted in, entering the P-channel register. After 64 clock cycles, S1 will be located in the N-channel register as shown below. It will also be clocked out to  $D_{out}$ 1.

A 2-to-4 decoder is provided to select which of the four patterns is to be used for all of the outputs. Logic inputs A1 and A0 determine which patterns are selected per the decoder truth table shown below. Once A1 and A0 are set, a rising edge on the trigger logic input pin will automatically load the selected pattern to all of the outputs.

#### **Decoder Truth Table**

| Logic Dec | Pattern Selected |                 |

|-----------|------------------|-----------------|

| A1        | A0               | Pallem Selected |

| 0         | 0                | 1               |

| 0         | 1                | 2               |

| 1         | 0                | 3               |

| 1         | 1                | 4               |

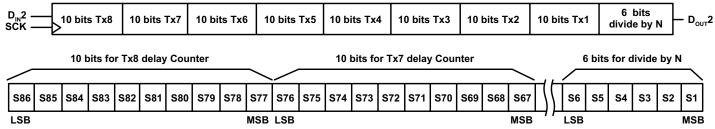

# Loading Data into the Delay Counters and the Divide-by-N Counter

Each output channel, TX, has its own programmable 10-bit delay counter. For 8 channels, 80 bits are needed. A 6-bit divide-by-N counter is also provided to program the desired TX frequency. To program all the individual delay counters and the divide-by-N counter, an 86-bit serial shift register is provided. It uses the same clock input that the pattern registers uses. DIN2 is the input data for this register. When  $\overline{CS2}$  is high, data will not be shifted in. Data is shifted in only when  $\overline{CS2}$  is low.

As shown below, the data first enters into the 10-bit register for the TX8 delay counter and continues to be shifted though to the 6-bit register for the divide by N counter. Data is clocked in during the rising edge of the clock. There is no activity during the falling edge of the clock. The MSB bit in the 6-bit divide-by-N register is clocked out into DOUT2 for cascading multiple devices if desired.

#### **10-Bit Delay Counter**

The input clock for the 10-bit delay counter is the TCK pin. The TCK pin is the only pin that is capable of high frequency, 200MHz. This helps maximum delay time resolution. The counter counts upward. Please refer to the table below.

86-bit Serial Shift Register: 80 bits for the delay counters and 6 bits for the divide by N

#### **Delay Counter Table**

| MSB |   |   |   |   |   |   | _ |   | LSB | Delay Time      |

|-----|---|---|---|---|---|---|---|---|-----|-----------------|

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   | 1023 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1   | 1022 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0   | 1021 TCK cycles |

| 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1   | 1020 TCK cycles |

| I   | I | I | I | I | I | I | I | I | I   | I               |

| I   | I | 1 | I | I | 1 | 1 | 1 | 1 | I   | 1               |

| 1   | I | I | I | I | I | I | 1 | I | I   | I               |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0   | 3 TCK cycles    |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1   | 2 TCK cycles    |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0   | 1 TCK cycle     |

| 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1   | No trigger      |

#### 6-Bit Divide-by-N Counter

The input clock for the 6-bit divide-by-N counter is the TCK pin. It generates the clock frequency for the 16/32 bit serial shift register for the output P- and N-channel patterns. Each

clock cycle will set the TX output to be either at  $V_{_{\rm PP}},\,V_{_{\rm NN}},\,$  ground, or high impedance depending on what was preprogrammed in their corresponding registers.

| MSB |   |   |   |   | LSB | Output Shift Register<br>Clock Frequency |

|-----|---|---|---|---|-----|------------------------------------------|

| 0   | 0 | 0 | 0 | 0 | 0   | f <sub>тск</sub> ÷64                     |

| 0   | 0 | 0 | 0 | 0 | 1   | f <sub>тск</sub> ÷ 63                    |

| 0   | 0 | 0 | 0 | 1 | 0   | f <sub>тск</sub> ÷ 62                    |

| 0   | 0 | 0 | 0 | 1 | 1   | f <sub>тск</sub> ÷ 61                    |

| I   | I | I | I | I | I   | I                                        |

| 1   | 1 | I | I | 1 | I I | I                                        |

| I   | I | I | I | I | I   | I                                        |

| 1   | 1 | 1 | 1 | 0 | 0   | f <sub>тск</sub> ÷4                      |

| 1   | 1 | 1 | 1 | 0 | 1   | f <sub>тск</sub> ÷3                      |

| 1   | 1 | 1 | 1 | 1 | 0   | f <sub>тск</sub> ÷2                      |

| 1   | 1 | 1 | 1 | 1 | 1   | f <sub>тск</sub> ÷1                      |

#### **Pin Description**

| Pin | Name  | Description                                                                                                                                                                                                                  |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AVDD  | Positive analog supply voltage (+5.0V).                                                                                                                                                                                      |

| 2   | DIN2  | Serial data in for delay counters and frequency divider.                                                                                                                                                                     |

| 3   | CS2   | Activates DIN2. Input logic high = off, input logic low = on.                                                                                                                                                                |

| 4   | SIZE  | Sets pattern width to either 16-bits or 32-bits. Logic low = 16-bits, logic high = 32-bits.                                                                                                                                  |

| 5   | INV   | Inverts the TX output waveform. See logic truth table for details.                                                                                                                                                           |

| 6   | CW    | Activates CW mode. Logic low = non-CW mode, logic high = CW mode. See logic truth table for details.                                                                                                                         |

| 7   | DOUT2 | Data out for delay counters and frequency divider.                                                                                                                                                                           |

| 8   | EN    | Enables and disables device. Logic low = off, logic high = on.                                                                                                                                                               |

| 9   | SCK   | Serial clock input for serial shift registers.                                                                                                                                                                               |

| 10  | DVDD  | Positive digital supply voltage (+5.0V).                                                                                                                                                                                     |

| 11  | DGND  | Digital ground.                                                                                                                                                                                                              |

| 12  | TRIG  | Toggles all TX outputs to transmit. Needs to be high for 2 rising edges of TCK. Delay counters will start on the rising edge of the TCK pin right after the falling edge of the TRIG signal. See timing diagram for details. |

| 13  | тск   | Transmitter clock for the delay counters and input frequency for the divide by N. Can be CMOS, LVDS, or SSTL.                                                                                                                |

| 14  | TCK   | Logic trip point TCK. Can be set to a DC value from $0.4V_{LL}$ to $0.6V_{LL}$ or driven differentially with TCK.                                                                                                            |

| 15  | VLL   | Logic interface supply voltage (3.0V or 3.3V).                                                                                                                                                                               |

| 16  | CS1   | Activates DIN1. Input logic high = off, input logic low = on.                                                                                                                                                                |

| 17  | DOUT1 | Data out for P-channel and N-channel pattern registers.                                                                                                                                                                      |

### Pin Description (cont.)

| Pin | Name | Description                                                                                                                                                                                         |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | A0   |                                                                                                                                                                                                     |

| 19  | A1   | Decoded to select 1 of 4 patterns to be loaded.                                                                                                                                                     |

| 20  | DIN1 | Serial data in for P-channel and N-channel pattern registers.                                                                                                                                       |

| 21  | VRN  | Negative supply for VPF regulator (-5.0V).                                                                                                                                                          |

| 22  | PVDD | Positive gate drive supply voltage for RTZ output transistors (+5.0V).                                                                                                                              |

| 23  | PGND | Dower ground path for PTZ output transistore                                                                                                                                                        |

| 24  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                       |

| 25  | PVSS | Negative gate drive supply voltage for RTZ output transistors (-5.0V).                                                                                                                              |

| 26  | VPF  | Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total. |

| 27  | NC   | No connection.                                                                                                                                                                                      |

| 28  | VNF  | Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total. |

| 29  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                       |

| 30  | TX1  | Transmit pulser outputs for channel 1.                                                                                                                                                              |

| 31  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                       |

| 32  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                       |

| 33  | TX2  | Transmit pulser outputs for channel 2.                                                                                                                                                              |

| 34  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                       |

| 35  | VNN  |                                                                                                                                                                                                     |

| 36  | TX3  | Transmit pulser outputs for channel 3.                                                                                                                                                              |

| 37  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                       |

| 38  | VPP  |                                                                                                                                                                                                     |

| 39  | TX4  | Transmit pulser outputs for channel 4.                                                                                                                                                              |

| 40  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                       |

| 41  | VNN  |                                                                                                                                                                                                     |

| 42  | VNF  | Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total. |

| 43  | DGND | Digital ground.                                                                                                                                                                                     |

| 44  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                       |

| 45  | VPF  | Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total. |

| 46  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                       |

| 47  | PVSS | Negative gate drive supply voltage for RTZ output transistors (-5.0V).                                                                                                                              |

| 48  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                       |

| 49  | PVDD | Positive gate drive supply voltage for RTZ output transistors (+5.0V).                                                                                                                              |

#### Pin Description (cont.)

| Pin | Name | Description                                                                                                                                                                                              |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 50  | DVDD | Positive digital supply voltage (+5.0V).                                                                                                                                                                 |

| 51  | DGND | Digital ground.                                                                                                                                                                                          |

| 52  | PVDD | Positive gate drive supply voltage for RTZ output transistors (+5.0V).                                                                                                                                   |

| 53  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                            |

| 54  | PVSS | Negative gate drive supply voltage for RTZ output transistors (-5.0V).                                                                                                                                   |

| 55  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                            |

| 56  | VPF  | Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage $1.0\mu F$ ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total. |

| 57  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                            |

| 58  | DGND | Digital ground.                                                                                                                                                                                          |

| 59  | VNF  | Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage $1.0\mu$ F ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total. |

| 60  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                            |

| 61  | VNN  |                                                                                                                                                                                                          |

| 62  | TX5  | Transmit pulser outputs for channel 5.                                                                                                                                                                   |

| 63  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                            |

| 64  | VPP  |                                                                                                                                                                                                          |

| 65  | TX6  | Transmit pulser outputs for channel 6.                                                                                                                                                                   |

| 66  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                            |

| 67  | VNN  |                                                                                                                                                                                                          |

| 68  | TX7  | Transmit pulser outputs for channel 7.                                                                                                                                                                   |

| 69  | VPP  | Positive high voltage supply (+3.0V to +70V).                                                                                                                                                            |

| 70  | VPP  |                                                                                                                                                                                                          |

| 71  | TX8  | Transmit pulser outputs for channel 8.                                                                                                                                                                   |

| 72  | VNN  | Negative high voltage supply (-3.0V to -70V).                                                                                                                                                            |

| 73  | VNF  | Linear regulator output gate drive voltage for the N-channel output transistors. A low voltage 1.0µF ceramic capacitor needs to be connected across every VNF to VNN pins. There are four in total.      |

| 74  | NC   | No connection.                                                                                                                                                                                           |

| 75  | VPF  | Linear regulator output gate drive voltage for the P-channel output transistors. A low voltage $1.0\mu$ F ceramic capacitor needs to be connected across every VPF and VPP pin. There are four in total. |

| 76  | PVSS | Negative gate drive supply voltage for RTZ output transistors (-5.0V).                                                                                                                                   |

| 77  | PGND | Power ground path for PTZ output transietors                                                                                                                                                             |

| 78  | PGND | Power ground path for RTZ output transistors.                                                                                                                                                            |

| 79  | PVDD | Positive gate drive supply voltage for RTZ output transistors (+5.0V).                                                                                                                                   |

| 80  | VRP  | Positive supply for VNF regulator (+5.0V).                                                                                                                                                               |

| V   | SUB  | Exposed center pad. Needs to be externally connected to digital ground, DGND.                                                                                                                            |

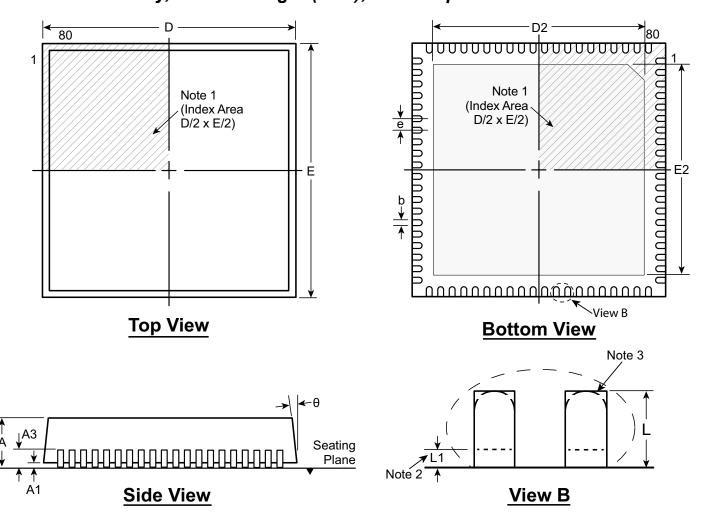

#### 80-Lead QFN Package Outline (K6) 11.00x11.00mm body, 1.00mm height (max), 0.50mm pitch

#### Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Depending on the method of manufacturing, a maximum of 0.15mm pullback (L1) may be present.

- 3. The inner tip of the lead may be either rounded or square.

| Symbol            |     | Α    | A1   | A3          | b    | D     | D2   | E     | E2   | е           | L    | L1   | θ               |

|-------------------|-----|------|------|-------------|------|-------|------|-------|------|-------------|------|------|-----------------|

| Dimension<br>(mm) | MIN | 0.80 | 0.00 | 0.20<br>REF | 0.18 | 10.90 | 9.50 | 10.90 | 9.50 | 0.50<br>BSC | 0.30 | 0.00 | <b>0</b> 0      |

|                   | NOM | 0.90 | 0.02 |             | 0.25 | 11.00 | 9.65 | 11.00 | 9.65 |             | 0.40 | -    | -               |

|                   | MAX | 1.00 | 0.05 |             | 0.30 | 11.10 | 9.75 | 11.10 | 9.75 |             | 0.50 | 0.15 | 14 <sup>0</sup> |

Drawings are not to scale.

Supertex Doc.#: DSPD-80QFNK611X11P050, Version A111511

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2014 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.