### **MDB1900ZB**

Zero Delay Buffer for PCIe (Gen1/Gen2/Gen3), SAS, SATA, ESI, and QPI

## **General Description**

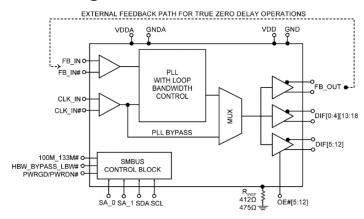

The MDB1900ZB is a true zero delay buffer with a fully-integrated, high-performance, low-power, and low-phase noise programmable PLL.

The MDB1900ZB is capable of distributing the reference clocks for PCIe (Gen1/Gen2/Gen3), SATA, ESI, SAS, SMI and Intel® Quickpath Interconnect (QPI). The MDB1900ZB works in conjunction with a CK410B+, CK509B or CK420BQ clock synthesizer to provide reference clocks to multiple agents.

The MDB1900ZB is designed for Intel's DB1900Z specification. The Intel part designation for the MDB1900ZB is identified as G20746-002.

Datasheets and support documentation are available on Micrel's web site at: www.micrel.com.

### **Block Diagram**

#### **Features**

- Supports zero delay (0ps) buffer mode for 100MHz and 133MHz clock frequencies.

- External feedback path for true zero delay operations

- Zero delay (PLL) mode can filter jitter in incoming clock

- Selectable PLL bandwidth for PLL mode

- Supports fanout buffer mode for clock frequencies between 0 and 250MHz

- Differential input reference with HCSL logic (0~0.7V)

- Nineteen differential HCSL-compatible clock output pairs

- Eight dedicated OE# pins to control their assigned output. Glitch free assertion/de-assertion.

- Spread spectrum modulation tolerant for EMI reduction

- SMBus interface for controlling output properties (enable/disable and delay tuning)

- Disabled outputs in power-down mode for maximum power savings

- Nine selectable SMBus addresses so multiple devices can share the same SMBus

- 3.3V or 2.5V operation

- Commercial temperature range (0°C to +70°C)

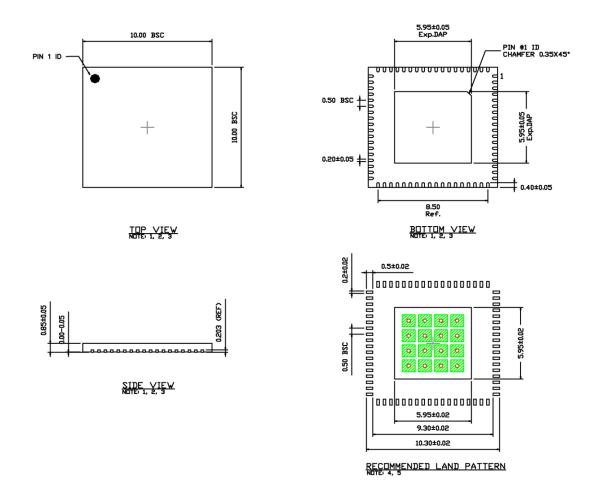

- 72-pin 10mm x 10mm QFN package

- · GREEN, RoHS, and PFOS compliant

## **Applications**

- PCI Express timing (Gen1/2/3) in Intel platforms, specifically the Romley platform

- SATA / SAS timing (storage)

- ESI and SMI systems (storage)

- Intel Quickpath Interconnect

## **Key Specifications**

- Cycle-to-cycle jitter (PLL mode): <35ps

- Output-to-output skew: <35ps

- Input-to-output delay (PLL mode): Fixed at Ops

- Input-to-output delay variation (PLL mode): 13ps

- Phase Jitter, PCIe Gen3: 0.25ps

- Accumulated Jitter, QPI 9.6Gb/s: <0.15ps</li>

Intel is a registered trademark of Intel Corporation.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Part Number    | Marking    | Shipping      | Ambient Temperature Range | Package <sup>(1)</sup> |

|----------------|------------|---------------|---------------------------|------------------------|

| MDB1900ZBQY TR | MDB1900ZBQ | Tape and Reel | -40°C to +85°C            | 72-Pin 10mm × 10mm QFN |

| MDB1900ZBQZ TR | MDB1900ZBQ | Tape and Reel | 0°C to +70°C              | 72-Pin 10mm × 10mm QFN |

#### Note:

1. Device is GREEN, RoHS, and PFOS compliant. Lead finish is 100% matte tin.

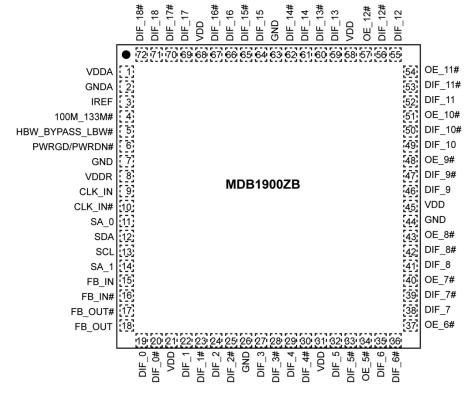

## **Pin Configuration**

72-Pin 10mm × 10mm QFN

## **Pin Description**

| Pin Number | Pin Name        | Type <sup>(2)</sup> | Pin Function                                                                                                                                                                                                                                                 |

|------------|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VDDA            | PWR                 | 3.3V or 2.5V Core Power Supply.                                                                                                                                                                                                                              |

| 2          | GNDA            | GND                 | Core Ground.                                                                                                                                                                                                                                                 |

| 3          | IREF            | I                   | $I_{REF}$ = (1.1V)/( $R_{IREF}$ ). A precision resistor ( $R_{IREF}$ ) is attached to this pin and to ground to set the reference current for the differential current mode output pairs. $R_{IREF}$ = 475Ω for 100Ω trace, $R_{IREF}$ = 412Ω for 85Ω trace. |

| 4          | 100M_133M#      | I, SE               | 3.3V LVTTL Input. Input/output frequency select. Logic 1 = 100MHz output (default, $50K\Omega$ pull-up resistor) Logic 0 = 133.33MHz output                                                                                                                  |

| 5          | HBW_BYPASS_LBW# | I, SE               | Tri-level input for selecting bypass or PLL bandwidth mode.  High = High PLL bandwidth mode  Mid = Bypass mode  Low = Low PLL bandwidth mode                                                                                                                 |

| 6          | PWRGD/PWRDN#    | I, SE               | $3.3\text{V}$ LVTTL Input for power good and power-down control. $50\text{K}\Omega$ pull-down resistor.                                                                                                                                                      |

| 7          | GND             | GND                 | Ground.                                                                                                                                                                                                                                                      |

| 8          | VDDR            | PWR                 | 3.3V or 2.5V power supply for differential clock input.                                                                                                                                                                                                      |

| 9          | CLK_IN          | I, DIF              | 0.7V HCSL differential clock input reference. True input pin.                                                                                                                                                                                                |

| 10         | CLK_IN#         | I, DIF              | 0.7V HCSL differential clock input reference. Complementary input pin.                                                                                                                                                                                       |

| 11         | SA_0            | I, SE               | Tri-level input to set SMBus address for this device. Works together with SA_1.                                                                                                                                                                              |

| 12         | SDA             | I/O                 | Open Collector SMBus Data I/O Pin (SDATA). 5V tolerant.                                                                                                                                                                                                      |

| 13         | SCL             | I, SE               | SMBus Slave Clock Input (SCLK). 5V tolerant.                                                                                                                                                                                                                 |

| 14         | SA_1            | I, SE               | Tri-level input to set SMBus address for this device. Works together with SA_0.                                                                                                                                                                              |

| 15         | FB_IN           | I, DIF              | ZDB Feedback, 0.7V differential clock input, true input pin.                                                                                                                                                                                                 |

| 16         | FB_IN#          | I, DIF              | ZDB Feedback, 0.7V differential clock input, complementary input pin.                                                                                                                                                                                        |

| 17         | FB_OUT          | O, DIF              | ZDB Feedback, 0.7V differential clock output (HCSL-compatible), true output pin.                                                                                                                                                                             |

| 18         | FB_OUT#         | O, DIF              | ZDB Feedback, 0.7V differential clock output (HCSL-compatible), complementary output pin.                                                                                                                                                                    |

| 19         | DIF_0           | O, DIF              | 0.7V Differential Clock Output 0 (HCSL-compatible), true output pin.                                                                                                                                                                                         |

| 20         | DIF_0#          | O, DIF              | 0.7V Differential Clock Output 0 (HCSL-compatible), complementary output pin.                                                                                                                                                                                |

| 21         | VDD             | PWR                 | 3.3V or 2.5V Power Supply.                                                                                                                                                                                                                                   |

| 22         | DIF_1           | O, DIF              | 0.7V Differential Clock Output 1 (HCSL-compatible), true output pin.                                                                                                                                                                                         |

| 23         | DIF_1#          | O, DIF              | 0.7V Differential Clock Output 1 (HCSL-compatible), complementary output pin.                                                                                                                                                                                |

| 24         | DIF_2           | O, DIF              | 0.7V Differential Clock Output 2 (HCSL-compatible), true output pin.                                                                                                                                                                                         |

#### Note:

2. I = Input O = Output

V = Output

I/O = Bi-directional

SE = Single-ended

DIF = Differential

PWR = 3.3V or 2.5V power

GND = Ground

# **Pin Description (Continued)**

| Pin Number | Pin Name | Type <sup>(2)</sup> | Pin Function                                                                                |

|------------|----------|---------------------|---------------------------------------------------------------------------------------------|

| 25         | DIF_2#   | O, DIF              | 0.7V Differential Clock Output 2 (HCSL-compatible), complementary output pin.               |

| 26         | GND      | GND                 | Ground.                                                                                     |

| 27         | DIF_3    | O, DIF              | 0.7V Differential Clock Output 3 (HCSL-compatible), true output pin.                        |

| 28         | DIF_3#   | O, DIF              | 0.7V Differential Clock Output 3 (HCSL-compatible), complementary output pin.               |

| 29         | DIF_4    | O, DIF              | 0.7V Differential Clock Output 4 (HCSL-compatible), true output pin.                        |

| 30         | DIF_4#   | O, DIF              | 0.7V Differential Clock Output 4 (HCSL-compatible), complementary output pin.               |

| 31         | VDD      | PWR                 | 3.3V or 2.5V power supply.                                                                  |

| 32         | DIF_5    | O, DIF              | 0.7V Differential Clock Output 5 (HCSL-compatible), true output pin.                        |

| 33         | DIF_5#   | O, DIF              | 0.7V Differential Clock Output 5 (HCSL-compatible), complementary output pin.               |

| 34         | OE_5#    | I, SE               | $3.3V\ LVTTL$ active-low input for enabling Differential Output 5 (50k $\Omega$ pull-down). |

| 35         | DIF_6    | O, DIF              | 0.7V Differential Clock Output 6 (HCSL-compatible), true output pin.                        |

| 36         | DIF_6#   | O, DIF              | 0.7V Differential Clock Output 6 (HCSL-compatible), complementary output pin.               |

| 37         | OE_6#    | I, SE               | $3.3V\ LVTTL$ active-low input for enabling Differential Output 6 (50k $\Omega$ pull-down). |

| 38         | DIF_7    | O, DIF              | 0.7V Differential Clock Output 7 (HCSL-compatible), true output pin.                        |

| 39         | DIF_7#   | O, DIF              | 0.7V Differential Clock Output 7 (HCSL-compatible), complementary output pin.               |

| 40         | OE_7#    | I, SE               | 3.3V LVTTL active-low input for enabling Differential Output 7 (50k $\Omega$ pulldown).     |

| 41         | DIF_8    | O, DIF              | 0.7V Differential Clock Output 8 (HCSL-compatible), true output pin.                        |

| 42         | DIF_8#   | O, DIF              | 0.7V Differential Clock Output 8 (HCSL-compatible), complementary output pin.               |

| 43         | OE_8#    | I, SE               | 3.3V LVTTL active-low input for enabling Differential Output 8 (50k $\Omega$ pulldown).     |

| 44         | GND      | GND                 | Ground                                                                                      |

| 45         | VDD      | PWR                 | 3.3V or 2.5V power supply.                                                                  |

| 46         | DIF_9    | O, DIF              | 0.7V Differential Clock Output 9 (HCSL-compatible), true output pin.                        |

| 47         | DIF_9#   | O, DIF              | 0.7V Differential Clock Output 9 (HCSL-compatible), complementary output pin.               |

| 48         | OE_9#    | I, SE               | 3.3V LVTTL active-low input for enabling Differential Output 9 (50k $\Omega$ pull-down).    |

| 49         | DIF_10   | O, DIF              | 0.7V Differential Clock Output 10 (HCSL-compatible), true output pin.                       |

| 50         | DIF_10#  | O, DIF              | 0.7V Differential Clock Output 10 (HCSL-compatible), complementary output pin.              |

# **Pin Description (Continued)**

| Pin Number | Pin Name    | Type <sup>(2)</sup> | Pin Function                                                                                        |

|------------|-------------|---------------------|-----------------------------------------------------------------------------------------------------|

| 51         | OE_10#      | I, SE               | $3.3V\ LVTTL$ active-low input for enabling Differential Output 10 (50k $\Omega$ pull-down).        |

| 52         | DIF_11      | O, DIF              | 0.7V Differential Clock Output 11 (HCSL-compatible), true output pin.                               |

| 53         | DIF_11#     | O, DIF              | 0.7V Differential Clock Output 11 (HCSL-compatible), complementary output pin.                      |

| 54         | OE_11#      | I, SE               | $3.3V\ LVTTL$ active-low input for enabling Differential Output 11 (50k $\Omega$ pull-down).        |

| 55         | DIF_12      | O, DIF              | 0.7V Differential Clock Output 12 (HCSL-compatible), true output pin.                               |

| 56         | DIF_12#     | O, DIF              | 0.7V Differential Clock Output 12 (HCSL-compatible), complementary output pin.                      |

| 57         | OE_12#      | I, SE               | 3.3V LVTTL active-low input for enabling Differential Output 12 (50K $\Omega$ pulldown).            |

| 58         | VDD         | PWR                 | 3.3V or 2.5V Power Supply.                                                                          |

| 59         | DIF_13      | O, DIF              | 0.7V Differential Clock Output 13 (HCSL-compatible), true output pin.                               |

| 60         | DIF_13#     | O, DIF              | 0.7V Differential Clock Output 13 (HCSL-compatible), complementary output pin.                      |

| 61         | DIF_14      | O, DIF              | 0.7V Differential Clock Output 14 (HCSL-compatible), true output pin.                               |

| 62         | DIF_14#     | O, DIF              | 0.7V Differential Clock Output 14 (HCSL-compatible), complementary output pin.                      |

| 63         | GND         | GND                 | Ground.                                                                                             |

| 64         | DIF_15      | O, DIF              | 0.7V Differential Clock Output 15 (HCSL-compatible), true output pin.                               |

| 65         | DIF_15#     | O, DIF              | 0.7V Differential Clock Output 15 (HCSL-compatible), complementary output pin.                      |

| 66         | DIF_16      | O, DIF              | 0.7V Differential Clock Output 16 (HCSL-compatible), true output pin.                               |

| 67         | DIF_16#     | O, DIF              | 0.7V Differential Clock Output 16 (HCSL-compatible), complementary output pin.                      |

| 68         | VDD         | PWR                 | 3.3V or 2.5V Power Supply.                                                                          |

| 69         | DIF_17      | O, DIF              | 0.7V Differential Clock Output 17 (HCSL-compatible), true output pin.                               |

| 70         | DIF_17#     | O, DIF              | 0.7V Differential Clock Output 17 (HCSL-compatible), complementary output pin.                      |

| 71         | DIF_18      | O, DIF              | 0.7V Differential Clock Output 18 (HCSL-compatible), true output pin.                               |

| 72         | DIF_18#     | O, DIF              | 0.7V Differential Clock Output 18 (HCSL-compatible), complementary output pin.                      |

| ePad       | Exposed Pad | GND                 | The center pad must be connected to the ground plane both for electrical ground and thermal relief. |

# Absolute Maximum Ratings<sup>(3)</sup>

| Analog Supply Voltage (V <sub>DDA</sub> )                          | +4.6V          |

|--------------------------------------------------------------------|----------------|

| I/O Supply Voltage (V <sub>DD</sub> )                              | +4.6V          |

| Input Low Voltage (V <sub>IL</sub> )                               | 0.5V           |

| Input High Voltage (V <sub>IH</sub> )                              | +4.6V          |

| Storage Temperature (T <sub>S</sub> )                              | 65°C to +150°C |

| Storage Temperature (T <sub>S</sub> )<br>ESD Rating <sup>(5)</sup> | 2kV            |

# Operating Ratings<sup>(4)</sup>

| Supply Voltage $(V_{DD}, V_{DDA})$ .   | +2.375V to +3.465V               |

|----------------------------------------|----------------------------------|

| Ambient Temperature (T <sub>A</sub> )  | 0°C to +70°C                     |

| Junction Temperature (T <sub>J</sub> ) | +125°C                           |

| Case Temperature (T <sub>C</sub> )     | +110°C                           |

| Thermal Resistance, Junction           | on-to-Ambient (T <sub>JA</sub> ) |

| Still Air                              | 26°C/W                           |

## DC Electrical Characteristics<sup>(6)</sup>

$V_{DDA} = V_{DD} = 3.3 V$  or 2.5 ±5%,  $T_A = 0$ °C to +70°C.

| Symbol                | Parameter                                                      | Condition                                                                       | Min.      | Тур. | Max.                  | Units |

|-----------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------|-----------|------|-----------------------|-------|

| $V_{DDA}, V_{DD}$     | 3.3V or 2.5V Operating Range                                   | 3.3V or 2.5V ±5%                                                                | 2.375     |      | 3.465                 | V     |

| V <sub>IH</sub>       | Input High Voltage                                             | V <sub>DD</sub> = 3.3V. Single-ended inputs, except SMBus and tri-level inputs. | 2         |      | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>       | Input Low Voltage                                              | V <sub>DD</sub> = 3.3V. Single-ended inputs, except SMBus and tri-level inputs. | GND - 0.3 |      | 0.8                   | V     |

| I <sub>IL</sub>       | Input Leakage Current <sup>(7)</sup>                           | $0 < V_{IN} < V_{DD}$                                                           | -5        |      | 5                     | μA    |

| $V_{IL\_TRI}$         | Input Low Voltage<br>(Tri-Level Input)                         | V <sub>DD</sub> = 3.3V                                                          | 0         |      | 0.9                   | V     |

| V <sub>IM_TRI</sub>   | Input Mid Voltage<br>(Tri-Level Input)                         | V <sub>DD</sub> = 3.3V                                                          | 1.3       |      | 1.8                   | V     |

| $V_{\text{IH\_TRI}}$  | Input High Voltage<br>(Tri-Level Input)                        | V <sub>DD</sub> = 3.3V                                                          | 2.4       |      | $V_{DD}$              | V     |

| C <sub>IN</sub>       | Input Capacitance <sup>(8)</sup>                               |                                                                                 | 1         |      | 4.5                   | pF    |

| C <sub>OUT</sub>      | Output Capacitance <sup>(8)</sup>                              |                                                                                 | 1         |      | 4.5                   | pF    |

| L <sub>PIN</sub>      | Pin Inductance                                                 |                                                                                 |           |      | 7                     | nΗ    |

| I <sub>DD_3.3V</sub>  | Operating Supply Current (I <sub>DDA</sub> + I <sub>DD</sub> ) | All outputs driven.                                                             |           |      | 450                   | mA    |

| I <sub>DD_3.3PD</sub> | Power-Down Current                                             | V <sub>DD</sub> = 3.3V. All differential pairs tristated.                       |           |      | 43                    | mA    |

| V <sub>DDSMB</sub>    | Nominal SMBus Voltage                                          |                                                                                 | 2.7       |      | 5.5                   | V     |

| V <sub>OLSMB</sub>    | SMBus Output Low Voltage                                       | @ IPULLUP                                                                       |           |      | 0.4                   | V     |

| V <sub>IHSMB</sub>    | SMBus input High Voltage                                       |                                                                                 | 2.1       |      | V <sub>DDSMB</sub>    | V     |

| V <sub>ILSMB</sub>    | SMBus input Low Voltage                                        |                                                                                 |           |      | 0.8                   | V     |

- 3. Exceeding the absolute maximum ratings may damage the device.

- 4. The device is not guaranteed to function outside its operating ratings.

- 5. Devices are ESD sensitive. Handling precautions are recommended. Human Body Model.

- 6. Specification for packaged product only.

- 7. Input leakage current. Does not include inputs with pull-up or pull-down resistors.

- 8. Capacitance value does not include pin capacitance.

# DC Electrical Characteristics<sup>(6)</sup> (Continued)

$V_{DDA} = V_{DD} = 3.3V$  or 2.5 ±5%,  $T_A = 0$ °C to +70°C.

| Symbol                      | Parameter                                               | Condition                                        | Min. | Тур. | Max. | Units |

|-----------------------------|---------------------------------------------------------|--------------------------------------------------|------|------|------|-------|

| I <sub>PULLUP</sub> (SMBUS) | Current-Through Pull-Up<br>Resistance or Current Source |                                                  | 100  |      | 470  | μA    |

| R <sub>PULLUP</sub> (SMBUS) | Pull-Up Resistance Value                                | $V_{DD} = 3.3V \pm 5\%$                          | 4.7  |      | 27   | ΚΩ    |

| T <sub>R(SMBUS)</sub>       | Rise Time for SDA and SCL                               | $(V_{IL(MAX)} - 0.15)$ to $(V_{IH(MIN)} + 0.15)$ |      |      | 1000 | ns    |

| T <sub>F(SMBUS)</sub>       | Fall Time for SDA and SCL                               | $(V_{IH(MIN)} + 0.15)$ to $(V_{IL(MAX)} - 0.15)$ |      |      | 300  | ns    |

## AC Electrical Characteristics - (CLK\_IN, CLK\_IN#) Clock Input Parameters

$V_{DDA} = V_{DD} = 3.3 V$  or 2.5V ±5%,  $T_A = 0$ °C to +70°C.

| Symbol                                       | Parameter                                                  | Condition                                                                                                 | Min. | Тур. | Max. | Units |

|----------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>IH</sub><br>(CLK_IN),<br>(CLK_IN#)    | Differential Input High Voltage                            | Statistical measurement on single-<br>ended signal using oscilloscope<br>V <sub>HIGH</sub> math function. | 660  |      | 850  | mV    |

| V <sub>IL</sub><br>(CLK_IN),<br>(CLK_IN#)    | Differential Input Low Voltage                             | Statistical measurement on single-<br>ended signal using oscilloscope<br>V <sub>LOW</sub> math function.  | -150 |      |      | mV    |

| V <sub>IHMAX</sub><br>(CLK_IN),<br>(CLK_IN#) | Differential Input Maximum<br>Voltage (include overshoot)  | Statistical measurement on single-<br>ended signal using absolute value.                                  |      |      | 1150 | mV    |

| V <sub>ILMIN</sub><br>(CLK_IN),<br>(CLK_IN#) | Differential Input Minimum<br>Voltage (include undershoot) | Statistical measurement on single-<br>ended signal using absolute value.                                  | -300 |      |      | mV    |

| V <sub>SWING</sub> (CLK_IN), (CLK_IN#)       | Differential Input Swing (include over / undershoot)       | Differential input (peak-to-peak).                                                                        | 300  |      | 1450 | mV    |

| V <sub>OX</sub><br>(CLK_IN),<br>(CLK_IN#)    | Crossing Point Input Voltage (absolute)                    |                                                                                                           | 250  |      | 550  | mV    |

| V <sub>OXV</sub><br>(CLK_IN),<br>(CLK_IN#)   | Crossing Point Input Voltage (variation)                   | Variation of crossing over all edges.                                                                     |      |      | 140  | mV    |

| Edge Rate<br>(CLK_IN),<br>(CLK_IN#)          | Minimum (CLK_IN)/(CLK_IN#)<br>Edge Rate <sup>(9)</sup>     | Based on single-ended measurement.                                                                        | 0.35 |      |      | V/ns  |

| Slew Rise<br>(CLK_IN),<br>(CLK_IN#)          | Input Rising Slew Rate <sup>(10)</sup>                     | Differential measurement                                                                                  | 0.70 |      | 4    | V/ns  |

<sup>9.</sup> The minimum input edge rate is 0.35V/ns single-ended or 0.7V/ns differential for both 100MHz and 133.33MHz.

<sup>10.</sup> The slew rate (0.70V/ns to 4V/ns) measurement on differential waveform for both 100MHz and 133.33MHz.

## AC Electrical Characteristics – (CLK\_IN, CLK\_IN#) Clock Input Parameters (Continued)

$V_{DDA} = V_{DD} = 3.3 V$  or 2.5V  $\pm 5\%$ ,  $T_A = 0$ °C to +70°C.

| Symbol                                 | Parameter                               | Condition                 | Min. | Тур. | Max. | Units |

|----------------------------------------|-----------------------------------------|---------------------------|------|------|------|-------|

| Slew Fall<br>(CLK_IN),<br>(CLK_IN#)    | Input Falling Slew Rate <sup>(10)</sup> | Differential measurement. | 0.70 |      | 4    | V/ns  |

| DC<br>(CLK_IN),<br>(CLK_IN#)           | Input Duty Cycle                        | Differential measurement. | 45   |      | 55   | %     |

| CY-CY Jitter<br>(CLK_IN),<br>(CLK_IN#) | Cycle-to-cycle Input Jitter             |                           |      |      | 50   | ps    |

## Spread Spectrum (SSC) Specification for Clock Input (CLK\_IN, CLK\_IN#)

| Symbol               | Parameter             | Value           |

|----------------------|-----------------------|-----------------|

| Modulation           | Down Spread           | (-0.5%) Maximum |

| Modulation Frequency | Modulation Frequency  | 30kHz to 33kHz  |

| Modulation Profile   | Triangular or Lexmark | (-0.5%) Maximum |

## **AC Electrical Characteristics – HCSL Outputs**

$V_{DDA} = V_{DD} = 3.3V$  or 2.5V  $\pm 5\%$ ,  $T_A = 0$ °C to +70°C.

| Symbol              | Parameter                                                   | Condition<br>(100MHz, 133.33MHz)                                             | Min.                  | Тур. | Max. | Units |

|---------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------|------|------|-------|

| T <sub>STAB</sub>   | Clock Stabilization Time <sup>(11)</sup>                    |                                                                              |                       | 160  | 300  | μs    |

| LACCURACY           | Long Accuracy <sup>(12, 13, 14, 15, 16)</sup>               |                                                                              |                       |      | 100  | ppm   |

| T <sub>ABSMIN</sub> | Absolute Minimum Host CLK<br>Period <sup>(12, 16, 17)</sup> | When (–0.5%) spread spectrum clock input (SSC <sub>ON</sub> ).               | (Period –<br>0.125ns) |      |      | ns    |

| T <sub>ABSMIN</sub> | Absolute Minimum Host CLK<br>Period <sup>(12, 16, 17)</sup> | When non-spread spectrum SSC clock input (SSC <sub>OFF</sub> ).              | -2.5%                 |      |      | ns    |

| Edge Rate           | Edge Rate <sup>(18)</sup>                                   | Measurement from differential waveform.                                      | 1.0                   | 2.5  | 4.0  | V/ns  |

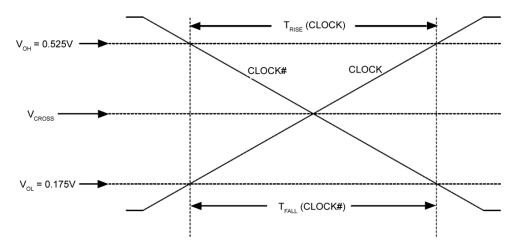

| T <sub>R</sub>      | Rise Time <sup>(19, 20)</sup> (see Figure 2)                | Single-ended measurement V <sub>OL</sub> = 0.175V, V <sub>OH</sub> = 0.525V. | 175                   | 225  | 700  | ps    |

| T <sub>F</sub>      | Fall Time <sup>(19, 20)</sup> (see Figure 2)                | Single-ended measurement $V_{OH} = 0.525V$ , $V_{OL} = 0.175V$ .             | 175                   | 225  | 700  | ps    |

- 11. This is the time from ramping the power supply, or assertion the PWRGD and when valid CLK\_IN input until the time that stable clocks are output from the device (PLL locked).

- All long-time accuracy and clock period specifications are guaranteed assuming that the input reference (CLK\_IN, CLK\_IN#) meets the CK410B+ or CK420BQ clock period specifications.

- 13. The long accuracy is 0ppm, when average only over any integer number of SSC periods.

- When (SSC<sub>OFF</sub>), using the frequency counter with the measurement interval equal to or greater than 0.15s, target frequencies are 100,000,000Hz, 133,333,333Hz.

- 15. When (SSC<sub>oN</sub>), using the frequency counter with the measurement interval equal to or greater than 0.15s, target frequencies are 99,750,000Hz, 133,000,000Hz.

- 16. Measurement taken from differential waveform.

- 17. The average period over any 1µs period of time must be greater than the minimum and less than the maximum specified period.

- 18. Measure taken from differential waveform on a component test board. The edge (slew) rate is measured from (–150mV) to (+150mV) on the differential waveform. Scope is set to average. Signal must be monotonic through the V<sub>OL</sub> to V<sub>OH</sub> region for T<sub>R</sub> and T<sub>F</sub>.

- 19. Measured from V<sub>OL</sub> = 0.175V and V<sub>OH</sub> = 0.525V. Only valid for rising clock and falling CLK#. Signal must be monotonic through V<sub>OL</sub> to V<sub>OH</sub> region for T<sub>R</sub> and T<sub>F</sub>. Measurement taken from single-ended waveform. The translation will be (0.5V/ns minimum to 2V/ns maximum) for single-ended edge rate. Refer to Figure 2.

- 20. Measurement taken from single-ended waveform.

## **AC Electrical Characteristics – HCSL Outputs (Continued)**

$V_{DDA} = V_{DD} = 3.3V$  or 2.5V ±5%,  $T_A = 0$ °C to +70°C.

| Symbol                        | Parameter                                                                     | Condition<br>(100MHz, 133.33MHz)                                                                            | Min.                | Тур. | Max.                     | Units |

|-------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|------|--------------------------|-------|

| $\Delta T_R$                  | Rise Time Variation <sup>(20, 21)</sup>                                       |                                                                                                             |                     |      | 125                      | ps    |

| $\Delta T_F$                  | Fall Time Variation (20, 21)                                                  |                                                                                                             |                     |      | 125                      | ps    |

| $T_RFM$                       | Rise and Fall Time<br>Matching <sup>(20, 21, 22)</sup>                        | Determined as fraction of $2 \times (T_R - T_F) / (T_R + T_F)$ .                                            |                     |      | 20                       | %     |

| V <sub>HIGH</sub>             | Differential Output High Voltage (typically 0.7V) (20, 23)                    | Statistical measurement on single-ended signal using oscilloscope math function.                            | 660                 | 700  | 850                      | mV    |

| $V_{LOW}$                     | Differential Output Low Voltage (typically 0.0V) (20, 24)                     | Statistical measurement on single-ended signal using -150 oscilloscope math function.                       |                     | 8    | 50                       | mV    |

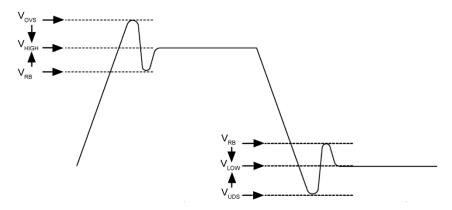

| Vovs                          | Differential Output Maximum<br>Voltage (include overshoot)<br>(see Figure 3)  | Statistical measurement on single-ended signal using absolute value.                                        |                     |      | V <sub>HIGH</sub> + 0.3V | V     |

| V <sub>UDS</sub>              | Differential Output Minimum<br>Voltage (include undershoot)<br>(see Figure 3) | Statistical measurement on single-ended signal using absolute value.                                        |                     |      | V <sub>LOW</sub> – 0.3V  | V     |

| $V_{RB}$                      | Ringback Voltage<br>(see Figure 3)                                            | Statistical measurement on single-ended signal using absolute value (-0.5%) SSC input (SSC <sub>ON</sub> ). | 0.2                 |      |                          | V     |

| $V_{RB}$                      | Ringback Voltage (see Figure 3)                                               | Statistical measurement on single-ended signal using absolute value non-SSC input (SSC <sub>OFF</sub> ).    | V <sub>X</sub> ±0.2 |      |                          | V     |

| V <sub>OX</sub><br>(Absolute) | Absolute Crossing Point Voltages <sup>(20, 25)</sup>                          | Statistical measurement on single-ended signal using absolute value.                                        | 250                 |      | 550                      | mV    |

| Total ∆V <sub>OX</sub>        | Total Variation of V <sub>OX</sub> Over All Edges <sup>(20, 26)</sup>         | Statistical measurement on single-ended signal using absolute value.                                        |                     |      | 140                      | mV    |

- 21. Measured with oscilloscope, averaging off, and using minimum/maximum statistics. Variation is the delta between minimum and maximum.

- 22. Measured with oscilloscope, averaging on, the difference between the rising edge rate (average) of clock versus the falling edge rate (average) of clock#.

- 23. A statistical average high value for  $V_{\text{HIGH}}$  obtained by using the oscilloscope  $V_{\text{HIGH}}$  math function.

- 24. A statistical average low value for  $V_{\text{LOW}}$  obtained by using the  $V_{\text{LOW}}$  math function.

- 25. The crossing point should meet the absolute and relative crossing point specifications simultaneously.

- 26.  $\Delta V_{OX}$  is defined as the total variation of all crossing voltages of rising CLOCK and falling CLOCK#.

## AC Electrical Characteristics – HCSL Outputs (Continued)

$V_{DDA} = V_{DD} = 3.3V$  or 2.5V  $\pm 5\%$ ,  $T_A = 0$ °C to +70°C.

| Symbol                                        | Parameter                                                                                                  | Condition<br>(100MHz, 133.33MHz)                                                             | Min. | Тур. | Max. | Units |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|-------|

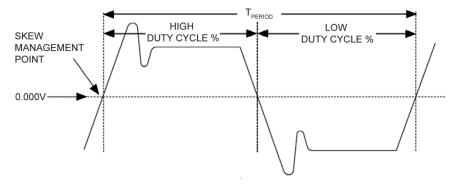

| Duty Cycle                                    | Differential Output Duty<br>Cycle <sup>(16)</sup> (see Figure 4)                                           | Measurement from differential waveform (measured at V <sub>OX</sub> ). PLL Mode              | 45   | 50   | 55   | %     |

| Duty Cycle<br>Distortion                      | Differential Output Duty Cycle Distortion <sup>(16, 31)</sup> (see Figure 4)                               | Measurement from differential waveform (measured at V <sub>OX</sub> ). Bypass mode at 100MHz | -2   | 0    | +2   | %     |

| T <sub>SKEW</sub>                             | Output-to-Output Delay <sup>(27, 28)</sup> (see Figure 4)                                                  | Measured at V <sub>OX</sub> (common to PLL and bypass mode).                                 |      | 18   | 35   | ps    |

| T <sub>PD</sub><br>(CLK_IN) to<br>DIF [18:0]  | Input-to-Output Delay <sup>(27, 28)</sup>                                                                  | Measured at V <sub>OX</sub> (PLL mode).                                                      | -35  | ±15  | 35   | ps    |

| ΔT <sub>PD</sub><br>(CLK_IN) to<br>DIF_[18:0] | Input-to-Output Delay<br>Variation <sup>(27)</sup>                                                         | Measured at V <sub>OX</sub> (PLL mode).                                                      |      | 13   | 75   | ps    |

| CY-CY Jitter<br>DIF_[18:0]<br>DIF#_[18:0]     | Cycle-to-Cycle Jitter <sup>(16)</sup>                                                                      | PLL mode.                                                                                    |      | 25   | 35   | ps    |

| T <sub>PD</sub><br>(CLK_IN) to<br>DIF_[18:0]  | Input-to-Output Delay <sup>(27)</sup>                                                                      | Measured at V <sub>OX</sub> (bypass mode).                                                   | 0.7  |      | 4.5  | ns    |

| ΔT <sub>PD</sub><br>(CLK_IN) to<br>DIF_[18:0] | Input-to-Output Delay<br>Variation <sup>(27)</sup>                                                         | Measured at V <sub>OX</sub> (bypass mode) absolute.                                          |      |      | 225  | ps    |

| T <sub>DTE</sub>                              | Random Differential Tracking<br>Error between two devices in<br>Hi BW mode <sup>(29)</sup>                 | PLL (HBW) mode, no spread spectrum.                                                          |      |      | 3.5  | ps    |

| T <sub>DSSTE</sub>                            | P2P Differential Spread<br>Spectrum Tracking Error<br>between two devices in Hi BW<br>mode <sup>(30)</sup> | PLL (HBW) mode, SSCON.                                                                       |      |      | 50   | ps    |

<sup>27.</sup> Measured from differential crossing point  $(V_{OX})$  to differential crossing point  $(V_{OX})$  with scope averaging on to find mean value.  $V_{OX}$  (relative) minimum and maximum are derived using the following:  $V_{OX}$  (relative) minimum = 0.250 + 0.5  $V_{HAVG}$  – 0.7V) and  $V_{OX}$  (relative) maximum = 0.550 – 0.5  $(0.7V - V_{HAVG})$ .

<sup>28.</sup> Measured into fixed 2pF load capacitor. Input to output skew is measured at the first output edge following the corresponding input.

<sup>29.</sup> This parameter is measured at the outputs of two MDB1900ZB devices in the HBW mode driven by a CK420BQ. The random differential tracking error is the differential phase jitter. It is the accumulated phase jitter, not including the effect of spread spectrum and not shared by the outputs. The jitter is measured into 2pF load cap and from differential cross-point to differential cross-point

<sup>30.</sup> This is the P2P difference in spread spectrum tracking error between two MDB1900ZB devices in Hi BW mode. The parameter is measured at the output of two MDB1900ZB devices driven by a CK420BQ with SSCON.

<sup>31.</sup> Duty Cycle Distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

## **Clock Period – SSC Disabled**

|                            | Measurement Window                                  |                                     |                                    |                |                                    |                                     |                                                     |       |

|----------------------------|-----------------------------------------------------|-------------------------------------|------------------------------------|----------------|------------------------------------|-------------------------------------|-----------------------------------------------------|-------|

| SSC <sub>OFF</sub>         | 1 Clock                                             | 1µs                                 | 0.1s                               | 0.1s           | 0.1s                               | 1µs                                 | 1 Clock                                             |       |

| Center<br>Frequency<br>MHz | –JITTER <sub>C – C</sub><br>Absolute per<br>Minimum | -SSC<br>Short<br>Average<br>Minimum | –ppm<br>Long<br>Average<br>Minimum | 0ppm<br>Period | +ppm<br>Long<br>Average<br>Maximum | +SSC<br>Short<br>Average<br>Maximum | +JITTER <sub>C - C</sub><br>Absolute per<br>Maximum | Units |

| 100                        | 9.94900                                             |                                     | 9.99900                            | 10.00000       | 10.00100                           |                                     | 10.05100                                            | ns    |

| 133.0                      | 7.44925                                             |                                     | 7.49925                            | 7.50000        | 7.50075                            |                                     | 7.55075                                             | ns    |

## **Clock Period – SSC Enabled**

| SSCON                      | 1 Clock                                             | 1µs                                 | 0.1s                               | 0.1s           | 0.1s                               | 1µs                                 | 1 Clock                                             |       |

|----------------------------|-----------------------------------------------------|-------------------------------------|------------------------------------|----------------|------------------------------------|-------------------------------------|-----------------------------------------------------|-------|

| Center<br>Frequency<br>MHz | –JITTER <sub>C – C</sub><br>Absolute per<br>Minimum | -SSC<br>Short<br>Average<br>Minimum | –ppm<br>Long<br>Average<br>Minimum | 0ppm<br>Period | +ppm<br>Long<br>Average<br>Maximum | +SSC<br>Short<br>Average<br>Maximum | +JITTER <sub>C – C</sub><br>Absolute per<br>Maximum | Units |

| 99.75                      | 9.94906                                             | 9.99906                             | 10.02406                           | 10.02506       | 10.02607                           | 10.05107                            | 10.10107                                            | ns    |

| 133.0                      | 7.44930                                             | 7.44930                             | 7.51805                            | 7.51880        | 7.51955                            | 7.5830                              | 7.58830                                             | ns    |

## PLL Bandwidth – Peaking and Phase Jitter (SSC<sub>OFF</sub>)

$V_{DDA} = V_{DD} = 3.3V$  or 2.5V ±5%,  $T_A = 0$ °C to +70°C.

| Symbol                                                   | Condition (100MHz, 133.33MHz)                                                                                                                     | Min. | Тур. | Max. | Units             |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|

| DLL litter Dealing(32)                                   | HBW_BYPASS_LBW# = 0 (low bandwidth)                                                                                                               |      |      | 1.0  | 40                |

| PLL Jitter Peaking <sup>(32)</sup>                       | HBW_BYPASS_LBW# = 1 (high bandwidth)                                                                                                              |      |      | 1.0  | dB                |

| PLL Bandwidth <sup>(33)</sup>                            | HBW_BYPASS_LBW# = 0 (low bandwidth)                                                                                                               | 0.70 | 1.0  | 1.4  | NAL 1-            |

| PLL Bandwidth                                            | HBW_BYPASS_LBW# = 1 (high bandwidth)                                                                                                              | 2    | 3.0  | 4    | MHz               |

| Phase Jitter<br>(PCIe Gen1) <sup>(34, 36, 37)</sup>      | PCIe Gen1<br>(including PLL BW 1.5MHz – 22MHz,<br>damping factor = 0.54, T <sub>D</sub> = 10ns, F <sub>TRK</sub> = 1.5MHz)                        |      | 16   | 50   | PS(Pk-Pk)         |

| Phase Jitter                                             | PCIe Gen2 (including PLL BW 8MHz $-$ 16MHz, jitter peaking = 3dB, damping factor = 0.54, $T_D$ = 10ns) (low band, F < 1.5MHz)                     |      | 0.9  | 1.75 |                   |

| (PCIe Gen2) <sup>(36, 37, 39)</sup>                      | PCIe Gen2 (including PLL BW 8MHz – 16MHz, jitter peaking = 3dB, damping factor = 0.54, T <sub>D</sub> = 10ns) (high band, [1.5MHz < F < Nyquist]) |      | 1.1  | 2.0  | PS <sub>RMS</sub> |

| Phase Jitter                                             | PCIe Gen3<br>(including PLL BW 2MHz – 4MHz, CDR = 10MHz)<br>(low band)                                                                            |      | 1.9  | 2.5  |                   |

| (PCle Gen3) <sup>(35, 36, 37, 39)</sup>                  | PCIe Gen3<br>(including PLL BW 2MHz – 4MHz, CDR = 10MHz)<br>(high band)                                                                           |      | 0.25 | 1.0  | PS <sub>RMS</sub> |

| Accumulated Jitter (4.8Gbps QPI) <sup>(37, 38, 40)</sup> | QPI, accumulated jitter (4.8Gbps or 6.4Gbps, 100MHz or 133MHz, 12 UI)                                                                             |      | 0.12 | 0.25 | ps <sub>RMS</sub> |

| Accumulated Jitter (6.4Gbps QPI) <sup>(37, 38, 40)</sup> | QPI, accumulated jitter (4.8Gbps or 6.4Gbps, 100MHz or 133MHz, 12 UI)                                                                             |      | 0.14 | 0.25 | ps <sub>RMS</sub> |

| Accumulated Jitter (8Gbps QPI_SMI) <sup>(37, 38)</sup>   | QPI, accumulated jitter (8Gbps, 100MHz, 12 UI)                                                                                                    |      | 0.08 | 0.20 | ps <sub>RMS</sub> |

| Accumulated Jitter (9.6Gbps QPI_SMI) <sup>(37, 38)</sup> | QPI, accumulated jitter (9.6Gbps, 100MHz, 12 UI)                                                                                                  |      | 0.06 | 0.15 | ps <sub>RMS</sub> |

| Accumulated Jitter (4MHz SMI)                            | SMI, 4MHz accumulated jitter                                                                                                                      |      | 0.06 | 0.2  | ps <sub>RMS</sub> |

| Accumulated Jitter (16MHz SMI)                           | SMI, 16MHz accumulated jitter                                                                                                                     |      | 0.12 | 0.5  | ps <sub>RMS</sub> |

- 32. Measured as maximum pass band gain. At frequencies with the loop BW, highest point-of-magnification is called PLL jitter peaking.

- 33. Measured at 3dB down or half-power point.

- 34. These jitter numbers are defined for a BER of 1E-12. Measured numbers at a smaller sample size have to be extrapolated to this BER target.

- 35. PCIe Gen3 filter characteristics are subject to final ratification by PCI-SIG. Check with PCI-SIG for latest specification.

- 36. The damping factor damping factor = 0.54 is implying a jitter peaking of 3dB.

- 37. Post processed evaluation through Intel-supplied Matlab scripts.

- 38. Measuring on 100MHz output using the template file in the clock jitter tool.

- 39. Measuring on 100MHz PCIe SRC output using the template file in the clock jitter tool.

- 40. Measuring on 100MHz, 133.33MHz output using the template file in the clock jitter tool.

## PLL Bandwidth – Peaking and Phase Jitter (SSC<sub>ON</sub>)

$V_{DDA}$  =  $V_{DD}$  = 3.3V or 2.5V ±5%,  $T_A$  = 0°C to +70°C.

| Symbol                                                   | Condition (100MHz, 133.33MHz)                                                                                                              | Min. | Тур. | Max. | Units                 |

|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----------------------|

| PLL Jitter Peaking <sup>(32)</sup>                       | HBW_BYPASS_LBW# = 0 (low bandwidth)                                                                                                        |      |      | 1.0  | dB                    |

| PLL Jiller Peaking                                       | HBW_BYPASS_LBW# = 1 (high bandwidth)                                                                                                       |      |      | 1.0  | αь                    |

| DL D                                                     | HBW_BYPASS_LBW# = 0 (low bandwidth)                                                                                                        | 0.70 | 1.0  | 1.4  |                       |

| PLL Bandwidth <sup>(33)</sup>                            | HBW_BYPASS_LBW# = 1 (high bandwidth)                                                                                                       | 2    | 3.0  | 4    | MHz                   |

| Phase Jitter<br>(PCle Gen1) <sup>(34, 36, 37)</sup>      | PCIe Gen1<br>(including PLL BW 1.5MHz – 22MHz,<br>damping factor = 0.54, T <sub>D</sub> = 10ns, F <sub>TRK</sub> = 1.5MHz)                 |      | 16   | 50   | ps <sub>(Pk-Pk)</sub> |

| Phase Jitter                                             | PCIe Gen2 (including PLL BW 8MHz – 16MHz, Jitter Peaking = 3dB, damping factor = 0.54, T <sub>D</sub> = 10ns) (low band, F < 1.5MHz)       |      | 1.0  | 1.75 |                       |

| (PCIe Gen2) <sup>(36, 37, 39)</sup>                      | PCIe Gen2 (including PLL BW 8MHz $-$ 16MHz, Jitter Peaking = 3dB, damping factor = 0.54, $T_D$ = 10ns) (high band, [1.5MHz < F < Nyquist]) |      | 1.0  | 2.0  | <b>PS</b> RMS         |

| Phase Jitter                                             | PCIe Gen3 (including PLL BW 2MHz – 4MHz, CDR = 10MHz) (low band)                                                                           |      | 2.7  | 3.0  | 20                    |

| (PCle Gen3) (35, 36, 37, 39)                             | PCIe Gen3 (including PLL BW 2MHz – 4MHz, CDR = 10MHz) (high band)                                                                          |      | 0.28 | 1.0  | PS <sub>RMS</sub>     |

| Accumulated Jitter (4.8Gbps QPI) <sup>(37, 38, 40)</sup> | QPI, accumulated jitter (4.8Gbps or 6.4Gbps, 100MHz or 133MHz, 12 UI)                                                                      |      | 0.18 | 0.25 | ps <sub>RMS</sub>     |

| Accumulated Jitter (6.4Gbps QPI) <sup>(37, 38, 40)</sup> | QPI, accumulated jitter (4.8Gbps or 6.4Gbps, 100MHz or 133MHz, 12 UI)                                                                      |      | 0.20 | 0.25 | ps <sub>RMS</sub>     |

| Accumulated Jitter (8Gbps QPI_SMI) <sup>(37, 38)</sup>   | QPI, accumulated jitter (8Gbps, 100MHz, 12 UI)                                                                                             |      | 0.09 | 0.20 | ps <sub>RMS</sub>     |

| Accumulated Jitter (9.6Gbps QPI_SMI) <sup>(37, 38)</sup> | QPI, accumulated jitter (9.6Gbps, 100MHz, 12 UI)                                                                                           |      | 0.08 | 0.15 | ps <sub>RMS</sub>     |

| Accumulated Jitter (4MHz SMI)                            | SMI, 4MHz accumulated jitter                                                                                                               |      | 0.12 | 0.2  | ps <sub>RMS</sub>     |

| Accumulated Jitter (16MHz SMI)                           | SMI, 16MHz accumulated jitter                                                                                                              |      | 0.06 | 0.5  | ps <sub>RMS</sub>     |

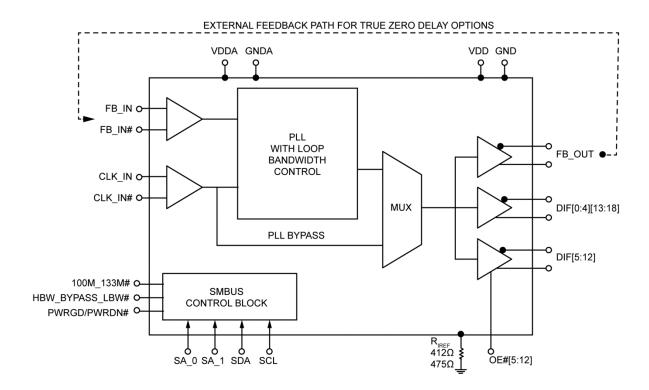

## **Functional Diagram**

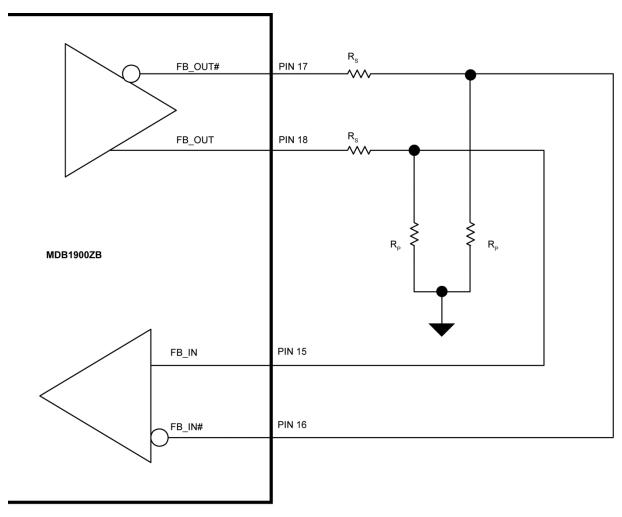

## External Feedback (FB\_OUT, FB\_OUT#) and (FB\_IN, FB\_IN#) Topology

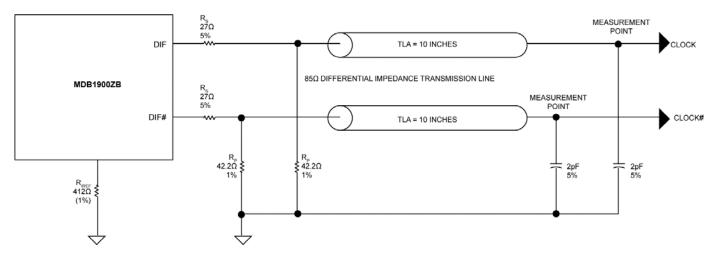

The MDB1900ZB utilizes external feedback topology to achieve low input-to-output delay variation. Place the shunt and series resistors as close to the (FB\_OUT, FB\_OUT#) (Pins 18 and 17) as possible (refer to Figure 1).

NOTE:

RESISTORS MUST BE LOCATED CLOSE TO FB\_OUT AND FB\_OUT# PINS.

Figure 1. External Feedback

**Table 1. Feedback Series and Shunt Resistors**

| E | Board Table Impedance R <sub>S</sub> |         | R <sub>P</sub> | Units |

|---|--------------------------------------|---------|----------------|-------|

|   | 100                                  | 33 (5%) | 49.9 (1%)      | Ω     |

|   | 85                                   | 27 (5%) | 42.2 (1%)      | Ω     |

## **Measurements Points for Differential**

Figure 2. Single-Ended Measurement Points for  $T_{\text{RISE}}$  and  $T_{\text{FALL}}$

Figure 3. Single-Ended Measurement Points for  $V_{\text{OVS}},\,V_{\text{UDS}},\,\text{and}\,\,V_{\text{RB}}$

Figure 4. Differential (Clock/Clock#) Measurement Points for T<sub>PERIOD</sub>, Duty Cycle, and Jitter

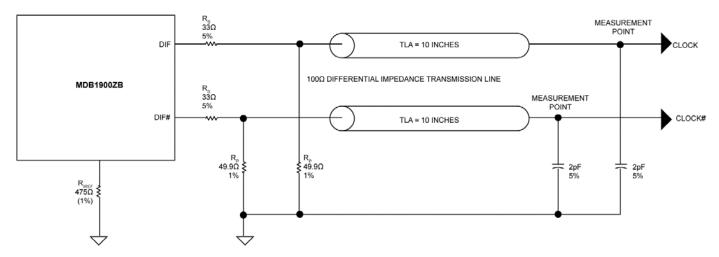

## Termination of HCSL [DIF, DIF# (18:0)] Output Buffers for Testing Conditions

All differential output parameters are measured while driving 10in  $100\Omega$  or  $85\Omega$  differential impedance transmission line segments with 2pF load capacitors at the end of each segment. Measurements are taken across the 2pF load capacitor associated with Clock and Clock# as shown in Figure 5 and Figure 6. For resistive lumped load, board trace impedance and trace length refer to Table 3.

Table 2. I<sub>REF</sub> and DIF Clock (HCSL) Output Current

| Board Trace Impedance Z | Reference R <sub>IREF</sub><br>I <sub>REF</sub> = (1.1V) / (R <sub>IREF</sub> ) | Output Current (mA)             | V <sub>OH</sub> at Z |

|-------------------------|---------------------------------------------------------------------------------|---------------------------------|----------------------|

| 100Ω                    | $R_{IREF} = 475\Omega (1\%)$ $I_{REF} = 2.32mA$                                 | $I_{OH} = (6mA \times I_{REF})$ | 0.7V @ 50Ω           |

| 85Ω                     | $R_{IREF} = 412\Omega (1\%)$ $I_{REF} = 2.67mA$                                 | $I_{OH} = (6mA \times I_{REF})$ | 0.7V @ 42.2Ω         |

Table 3. Resistive Lumped Test Loads for HCSL Differential Clocks

| Clock                                                        | Board Trace Impedance    | Rs      | R <sub>P</sub> | R <sub>IREF</sub> | Units | Notes                                                           |

|--------------------------------------------------------------|--------------------------|---------|----------------|-------------------|-------|-----------------------------------------------------------------|

| Clocks<br>(100MHz and 133.33MHz)<br>with 50Ω configuration   | 100                      | 33 (5%) | 49.9 (1%)      | 475 (1%)          | Ω     | 10in. (maximum) into 2pF load with 100Ω differential impedance. |

| Clocks<br>(100MHz and 133.33MHz)<br>with 42.5Ω configuration | 100MHz and 133.33MHz) 85 |         | 42.2 (1%)      | 412 (1%)          | Ω     | 10in. (maximum) into 2pF load with 85Ω differential impedance.  |

Figure 5. 0.7V Configuration Test Load Board Termination with  $100\Omega$  Differential Impedance Transmission Line

Figure 6. 0.7V Configuration Test Load Board Termination with  $85\Omega$  Differential Impedance Transmission Line

### **Functional Description**

#### CLK IN, CLK IN# Input Reference

The reference clock (CLK\_IN, CLK\_IN#) is an HCSL (0.7V) differential input with 100MHz or 133.33MHz frequency from CK410B+, CK509B or CK420BQ clock Synthesizer. The input (CLK\_IN, CLK\_IN#) has the option to have spread spectrum ON or spread spectrum OFF. The spread spectrum clocking (SSC) has modulation frequency value of 30kHz – 33kHz, with modulation of –0.5% down-spread (maximum). The modulation profile is Triangular or Lexmark.

#### **OE# and Output Enables (Control Registers)**

OE# pins are dedicated control pins for DIF [12:5] outputs and are asynchronous asserted-low signals. Each output can be individually enabled or disabled by SMBus control register bits. The output enable bits in the SMBus registers are active high and by default are set to enable.

#### **OE# Assertion (Transition from Logic 1 to Logic 0)**

All differential outputs that were tri-stated are to resume normal operation in a glitch free manner. The latency from the assertion to active outputs is 4-12 DIF clock periods.

#### **OE# De-Assertion (Transition from Logic 0 to Logic 1)**

The impact of de-asserting OE# is each corresponding differential output will transition from normal operation to tri-state in a glitch free manner. A minimum of four valid clocks will be provided after OE# de-assertion. The maximum latency from the de-assertion to tri-stated outputs is twelve DIF clock periods.

**Table 4. OE Functionality**

| Inj              | outs               | OE# Hardware Pins and Control Register Bits Outputs |     |                     |                             |                    |           |

|------------------|--------------------|-----------------------------------------------------|-----|---------------------|-----------------------------|--------------------|-----------|

| PWRGD/<br>PWRGD# | CLK_IN/<br>CLK_IN# | SMBus<br>Enable Bit                                 | OE# | DIF/DIF#_<br>[12:5] | DIF/DIF#_<br>[18:13], [4:0] | FB_OUT/<br>FB_OUT# | PLL State |

| 0                | Х                  | X                                                   | Х   | Hi-Z                | Hi-Z                        | Hi-Z               | ON        |

|                  |                    | 0                                                   | Х   | Hi-Z                | Hi-Z                        | Running            | ON        |

| 1                | Running            | 1                                                   | 0   | Running             | Running                     | Running            | ON        |

|                  |                    | 1                                                   | 1   | Hi-Z                | Running                     | Running            | ON        |

#### 100M 133M# (Frequency Selection)

The 100M 133M# is a hardware pin which programs the appropriate output frequency. The MDB1900ZB is operated in the 1:1 mode only; therefore the CLK IN frequency is equal to DIF [18:0] frequency. The frequency selection can be enabled by 100M\_133M# pin or by SMBus control register bit.

Note: The default frequency at power-up is 100MHz.

**Table 5. Frequency Program**

| 100M_133M# | Optimized Frequency<br>(CLK_IN = DIF_[18:0]} |

|------------|----------------------------------------------|

| 0          | 133.33MHz                                    |

| 1          | 100.00MHz (Default)                          |

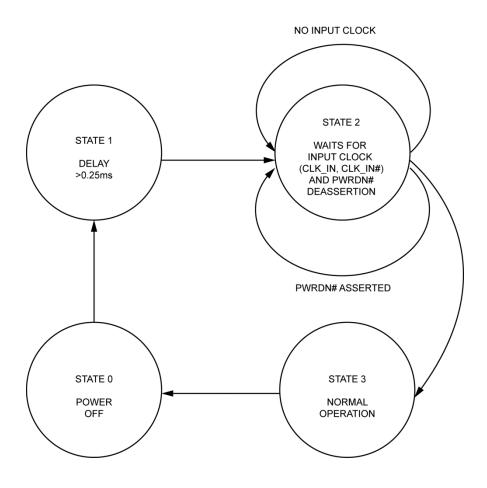

#### **PWRGD / PWRDN#**

De-assertion of PWRGD (Logic 0) which becomes PWRDN# indicates a power-down mode, which will shut off all clocks cleanly. PWRDN# is asynchronous active low input, and instructs the device to enter power saving mode. PWRDN# should be asserted low prior to shutting off the input clock or power to ensure all clocks shut down in a glitch-free manner, and all outputs will be tristated.

Table 6. PWRGD/PWRGDN# Functionality

| PWRGD/<br>PWRGDN# | DIF_/DIF#<br>[18.0] | Notes           |

|-------------------|---------------------|-----------------|

| 0                 | Tri-State           | Power-Down Mode |

| 1                 | Normal              | Active Mode     |

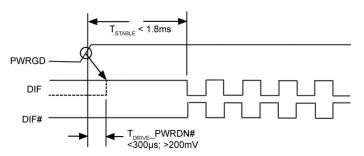

#### **PWRGD Assertion**

The power-up latency is less than 1.8ms. This is the time from the assertion of the PWRGD pin or the ramping of the power supply and the time from valid CLK IN input clock until the time that stable clocks are output from the buffer chip (PLL locked).

The assertion and de-assertion of PWRDN# is absolutely asynchronous

Note: It is not recommended to disable (CLK\_IN, CLK\_IN#) input prior to assertion of PWRDN# and operation in this mode can result in glitches and excessive frequency shifting.

Figure 7. PWRGD Assertion (Power-Down De-Assertion)

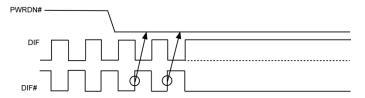

#### **PWRDN# Assertion**

When PWRDN# is sampled as being asserted by two consecutive rising edges of DIF#, all differential outputs must be tri-stated on the next DIF# high-to-low transition.

Figure 8. PWRDN# Assertion

#### **HBW BYPASS LBW#**

The HBW BYPASS LBW# is a tri-level function input pin. It is used to select between PLL high-bandwidth, bypass mode and PLL low bandwidth. The PLL HBW, BYPASS and PLL LBW mode may be selected via writing **SMBus** register asserting or by HBW\_BYPASS\_LBW input pin to the appropriate level per Table 7.

Table 7. PLL Bandwidth and Readback

| HBW_BYPASS_LBW# | Byte 0,<br>Bit 7               | Byte 0,<br>Bit 6 |   |

|-----------------|--------------------------------|------------------|---|

| L (Low)         | LBW<br>(Low PLL<br>Bandwidth)  | 0                | 0 |

| M (Mid)         | BYPASS<br>(Bypass PLL)         | 0                | 1 |

| H (High)        | HBW<br>(High PLL<br>Bandwidth) | 1                | 1 |

## SA\_0, SA\_1 (Address Selection)

Downloaded from Arrow.com.

SA\_0 and SA\_1 are tri-level hardware pins that can configure the MDB1900ZB to nine different addresses.

Table 8. SA\_0, SA\_1, and SMBus Address

| SA_1 | SA_0 | SMBus Address |

|------|------|---------------|

| L    | L    | D8            |

| L    | M    | DA            |

| L    | Н    | DE            |

| М    | L    | C2            |

| M    | M    | C4            |

| М    | Н    | C6            |

| Н    | L    | CA            |

| Н    | M    | CC            |

| Н    | Н    | CE            |

## **MDB1900ZB Control Registers**

#### **SDA, SCL (Pins 12, 13)**

The serial data (SDA) and serial clock (SCL) are dedicated for SMBus application and designed for 400Kb/s (maximum).

The SDA and SCL pins do not have internal pull-up resistors. When the device is in power-down mode, the SDA and SCL inputs are tri-stated and all programming information is retained.

All electrical characteristics meet the standard mode specifications of the SMBus 2.0 specification. For SDA and SCL input specs, refer to the *DC Electrical Characteristics*.

Table 9. Byte 0: Frequency Select, Output Enable, PLL-Mode Control Register

| Bit | Description                    | If Bit = 0 | If Bit = 1 | Type | Default             | Pin(s) |

|-----|--------------------------------|------------|------------|------|---------------------|--------|

| 7   | HBW_BYPASS_LBW#<br>Mode 1      | Refer to   | Toble 4    | R    | Latched at Power-Up | 5      |

| 6   | HBW_BYPASS_LBW#<br>Mode 0      | Relei to   | Table 4    | R    | Latched at Power-Up | 5      |

| 5   | Output Enable<br>DIF, DIF#_18  | Hi-Z       | Enable     | RW   | 1                   | 71, 72 |

| 4   | Output Enable<br>DIF, DIF#_17  | Hi-Z       | Enable     | RW   | 1                   | 69, 70 |

| 3   | Output Enable<br>DIF, DIF#_16  | Hi-Z       | Enable     | RW   | 1                   | 66, 67 |

| 2   | Reserved                       | _          | _          | _    | _                   | _      |

| 1   | Reserved                       |            |            | _    | _                   | _      |

| 0   | 100M_133M#<br>Frequency Select | 133.33MHz  | 100MHz     | R    | Latched at Power-Up | 4      |

Table 10. Byte 1: Output Enable Control Register

| Bit | Description                    | If Bit = 0 | If Bit = 1 | Туре | Default | Pin(s) |

|-----|--------------------------------|------------|------------|------|---------|--------|

| 7   | Output Enable<br>DIF, DIF#_[7] | Hi-Z       | Enabled    | RW   | 1       | 38, 39 |

| 6   | Output Enable<br>DIF, DIF#_[6] | Hi-Z       | Enabled    | RW   | 1       | 35, 36 |

| 5   | Output Enable<br>DIF, DIF#_[5] | Hi-Z       | Enabled    | RW   | 1       | 32, 33 |

| 4   | Output Enable<br>DIF, DIF#_[4] | Hi-Z       | Enabled    | RW   | 1       | 29, 30 |

| 3   | Output Enable<br>DIF, DIF#_[3] | Hi-Z       | Enabled    | RW   | 1       | 27, 28 |

| 2   | Output Enable<br>DIF, DIF#_[2] | Hi-Z       | Enabled    | RW   | 1       | 24, 25 |

| 1   | Output Enable<br>DIF, DIF#_[1] | Hi-Z       | Enabled    | RW   | 1       | 22, 23 |

| 0   | Output Enable<br>DIF, DIF#_[0] | Hi-Z       | Enabled    | RW   | 1       | 19, 20 |

Table 11. Byte 2: Output Enable Control Register

| Bit | Description                     | If Bit = 0 | If Bit = 1 | Туре | Default | Pin(s) |

|-----|---------------------------------|------------|------------|------|---------|--------|

| 7   | Output Enable<br>DIF, DIF#_[15] | Hi-Z       | Enabled    | RW   | 1       | 64, 65 |

| 6   | Output Enable<br>DIF, DIF#_[14] | Hi-Z       | Enabled    | RW   | 1       | 61, 62 |

| 5   | Output Enable<br>DIF, DIF#_[13] | Hi-Z       | Enabled    | RW   | 1       | 59, 60 |

| 4   | Output Enable<br>DIF, DIF#_[12] | Hi-Z       | Enabled    | RW   | 1       | 55, 56 |

| 3   | Output Enable<br>DIF, DIF#_[11] | Hi-Z       | Enabled    | RW   | 1       | 52, 53 |

| 2   | Output Enable<br>DIF, DIF#_[10] | Hi-Z       | Enabled    | RW   | 1       | 49, 50 |

| 1   | Output Enable<br>DIF, DIF#_[9]  | Hi-Z       | Enabled    | RW   | 1       | 46, 47 |

| 0   | Output Enable<br>DIF, DIF#_[8]  | Hi-Z       | Enabled    | RW   | 1       | 41, 42 |

Table 12. Byte 3: OE# Pin Real-time Readback Control Register

| Bit | Description                     | If Bit = 0 | If Bit = 1  | Туре | Default   | Pin(s) |

|-----|---------------------------------|------------|-------------|------|-----------|--------|

| 7   | Real-Time Readback<br>of OE_12# | OE_5# Low  | OE_5# High  | R    | Real-Time | 57     |

| 6   | Real-Time Readback<br>of OE_11# | OE_6# Low  | OE_6# High  | R    | Real-Time | 54     |

| 5   | Real-Time Readback<br>of OE_10# | OE_7# Low  | OE_7# High  | R    | Real-Time | 51     |

| 4   | Real-Time Readback of OE_9#     | OE_8# Low  | OE_8# High  | R    | Real-Time | 48     |

| 3   | Real-Time Readback<br>of OE_8#  | OE_9# Low  | OE_9# High  | R    | Real-Time | 43     |

| 2   | Real-Time Readback of OE_7#     | OE_10# Low | OE_10# High | R    | Real-Time | 40     |

| 1   | Real-Time Readback<br>of OE_6#  | OE_11# Low | OE_11# High | R    | Real-Time | 37     |

| 0   | Real-Time Readback<br>of OE_5#  | OE_12# Low | OE_12# High | R    | Real-Time | 34     |

#### Table 13. Byte 4: Reserved Control Register

| Bit | Description | If Bit = 0 | If Bit = 1 | Туре | Default | Pin(s) |

|-----|-------------|------------|------------|------|---------|--------|

| 7   | Reserved    | _          | _          | _    | -       | _      |

| 6   | Reserved    | _          | _          | -    | -       | _      |

| 5   | Reserved    | _          | _          | -    | -       | _      |

| 4   | Reserved    | _          | _          | -    | -       | _      |

| 3   | Reserved    | _          | _          | -    | -       | _      |

| 2   | Reserved    | _          | _          | -    | -       | _      |

| 1   | Reserved    | _          | _          | _    | -       | _      |

| 0   | Reserved    | _          | _          | _    | -       | _      |

### Table 14. Byte 5: Vendor/Revision Identification Control Register

| Bit | Description         | If Bit = 0 | If Bit = 1 | Туре | Default                       | Pin(s) |

|-----|---------------------|------------|------------|------|-------------------------------|--------|

| 7   | Revision Code Bit 3 | _          | _          | R    |                               | _      |

| 6   | Revision Code Bit 2 | _          | _          | R    | Vendor Specific               | _      |

| 5   | Revision Code Bit 1 | _          | _          | R    | (contact factory for details) | _      |

| 4   | Revision Code Bit 0 | _          | _          | R    | ,                             | _      |

| 3   | Vendor ID Bit 3     | _          | _          | R    | 0                             | -      |

| 2   | Vendor ID Bit 2     | _          | _          | R    | 0                             | -      |

| 1   | Vendor ID Bit 1     | _          | _          | R    | 1                             | -      |

| 0   | Vendor ID Bit 0     | -          | _          | R    | 1                             | _      |

#### Table 15. Byte 6: Device ID Control Register

| Bit | Description       | If Bit = 0       | If Bit = 1       | Туре | Default | Pin(s) |

|-----|-------------------|------------------|------------------|------|---------|--------|

| 7   | Device ID 7 (MSB) |                  |                  | R    | 1       | _      |

| 6   | Device ID 6       |                  |                  | R    | 1       | _      |

| 5   | Device ID 5       |                  |                  | R    | 0       | _      |

| 4   | Device ID 4       | Device ID is 0x0 | DB (Hex), or 219 | R    | 1       | _      |

| 3   | Device ID 3       |                  | imal)            | R    | 1       | _      |

| 2   | Device ID 2       |                  |                  |      | 0       | _      |

| 1   | Device ID 1       |                  |                  | R    | 1       | _      |

| 0   | Device ID 0       |                  |                  | R    | 1       | _      |

#### Byte 7: Byte Count Register

Writing to bits [0:4] of Byte 7 configures how many bytes will be read back.

Table 16. Byte 7: Byte Count Register

| Bit | Description | If Bit = 0 | If Bit = 1 | Туре | Default | Pin(s) |

|-----|-------------|------------|------------|------|---------|--------|

| 7   | Reserved    | _          | _          | -    | _       | _      |

| 6   | Reserved    | _          | _          | -    | -       | _      |

| 5   | Reserved    | _          | _          | -    | -       | _      |

| 4   | BC4         | _          | _          | RW   | 0       | _      |

| 3   | BC3         | _          | _          | RW   | 1       | _      |

| 2   | BC2.        | _          | _          | RW   | 0       | _      |

| 1   | BC1         | _          | _          | RW   | 0       | _      |

| 0   | BC0         | -          | _          | RW   | 0       | -      |

#### Byte 8, 9, 10: Access and Controls for Optional Advanced Features

Registers 8, 9, and 10 are additional Micrel-defined registers to allow access to and control of optional advanced features. For optional features details, please see the *Optional Features* section.

Optional advanced features use a two level read or write access, wherein the first step is to enter an access code in Byte 8, followed by entering a feature's bit address in Byte 9, and then reading or writing control information in Byte 10.

### Byte 8: Advanced Features Access Register

This is a write-only register which defines the access to Register 9 and 10. When value 0xBB('1011'1011) is written to Register 8, then Registers 9 and 10 become accessible. Otherwise, Registers 9 and 10 cannot be either read or written.

Table 17. Byte 8: Advanced Features Access Register

| Bit | Description | If Bit = 0 | If Bit = 1 | Туре | Default | Pin(s) |

|-----|-------------|------------|------------|------|---------|--------|

| 7   | access[7]   | _          | _          | W    | -       | -      |

| 6   | access[6]   | -          | _          | W    | -       | -      |

| 5   | access[5]   | -          | _          | W    | -       | -      |

| 4   | access[4]   | -          | _          | W    | -       | _      |

| 3   | access[3]   | -          | _          | W    | -       | _      |

| 2   | access[2]   | -          | _          | W    | -       | -      |

| 1   | access[1]   | _          | _          | W    | _       | _      |

| 0   | access[0]   | _          | _          | W    | _       | _      |

#### Byte 9: Features Bits Address Register

Each optional feature has an associate set of bits and each bit has a unique address. For details of optional features and their associated bit addresses, please see the *Optional Features* section. In order to access a bit, its address has to be written to Register 9.

Table 18. Byte 9. Features Bits Address Register