## **MIC1832**

#### μP Supervisory Circuit

### **General Description**

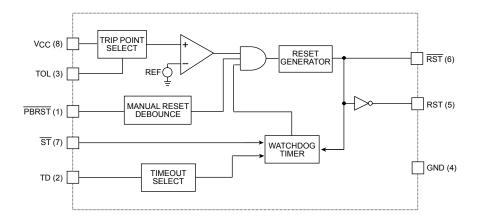

The MIC1832 is a multifunction circuit which monitors microprocessor activity, external reset and power supplies in microprocessor based systems. The circuit functions include a watchdog time, power supply monitor, microprocessor reset, and manual pushbutton reset input.

The power supply line is monitored with a comparator and an internal voltage reference. /RST is forced low when an out-of-tolerance condition exists and remains asserted for at least 250ms after  $V_{CC}$  rises above the threshold voltage (2.55V or 2.88V). The /RST pin will remain logic low with  $V_{CC}$  as low as 1.4V.

The Watchdog input (/ST) monitors  $\mu P$  activity and will assert /RST if no  $\mu P$  activity has occurred with in the watchdog timeout period. The watchdog timeout period is selectable with nominal period of 150, 600, 1200 milliseconds.

#### **Features**

- Power OK/Resettime delay, 250ms min.

- · Watchdog timer, 150ms, 600ms, or 1.2s typical

- Precision supply voltage monitor, select between 5% or 10% of supply voltage

- Avaiable in 8-pin surface mount (SO)

- Debounced External reset input

- Low supply current, <18μA typical</li>

### **Applications**

- · Autimotive systems

- · Intelligent systems

- · Critical microprocessor power monitoring

- Battery powered computers

- Controllers

### **Ordering Information**

| Part Number |           | Tomporatura Banga | Dookogo    |  |

|-------------|-----------|-------------------|------------|--|

| Standard    | Pb-Free   | Temperature Range | Package    |  |

| MIC1832N    | MIC1832NY | –40°C to +85°C    | 8-Pin PDIP |  |

| MIC1832M    | MIC1832MY | –40°C to +85°C    | 8-Pin SOIC |  |

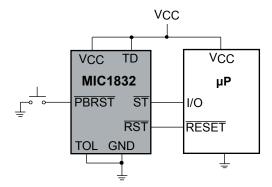

## **Typical Application**

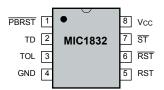

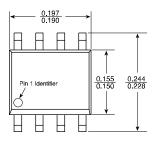

# **Pin Configuration**

8-Pin PDIP Package 8-Pin SOIC Package

**Pin Description**

| Pin Number | Pin Name        | Pin Function                                                                                                                                                                                                                                                                                                              |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | /PBRST          | Pushbutton Reset Input: This input is debounced and can be driven with external logic signals or by means of a mechanical pushbutton to actively force a reset. All pulses less than 1ms in duration on the /PBRST pin are ignored, whereas, any pulse with a duration of 20ms or greater is guaranteed to cause a reset. |

| 2          | TD              | Time Delay input: This input selects the timebase used by the watchdog timer. When TD = 0V, the watchdog timeout period is set to a normal value of 150ms, when TD = open, the watchdog timeout period is et to a nominal value of 600ms and when TD = $V_{CC}$ , the watchdog period is 1.2s nominally.                  |

| 3          | TOL             | Tolerance Select Input: Selects whether 5% or 10% of VCC is used as the reset threshold voltage. When TOL = 0V, the 5% tolerance level is selected and when TOL = $V_{CC}$ , a 10% tolerance level is selected.                                                                                                           |

| 4          | GND             | IC ground pin, 0V reference                                                                                                                                                                                                                                                                                               |

| 5          | RST             | RST is asserted high if either $V_{CC}$ goes below the reset threshold, the watchdog times out or /PBRST is pulled low for a minimum of 20ms. RST remains asserted for one reset timeout period after VCC exceeds the reset threshold or after the watch times out or after /PBRST goes high.                             |

| 6          | /RST            | /RST is asserted low if either $V_{CC}$ goes below the reset threshold, the watchdog times out or /PBRST is pulled low for a minimum of 20ms. /RST remains asserted for one reset timeout period after $V_{CC}$ exceeds the reset threshold or after the watch times out or after /PBRST goes high. Open-drain output     |

| 7          | /ST             | Input to watchdog timer. If /ST does not see a transition from high to low within the watchdog timeout period, RST and /RST will be asserted.                                                                                                                                                                             |

| 8          | V <sub>CC</sub> | Primary supply input, +5V                                                                                                                                                                                                                                                                                                 |

## **Absolute Maximum Ratings (Note 1)**

###

## **Operating Ratings (Note 2)**

| Operating Temperature Range |              |

|-----------------------------|--------------|

| MIC1832M/N                  | 40°C to 85°C |

| MIC1832D                    | 40°C to 85°C |

| Power Dissapation           | 700mW        |

#### **Electrical Characteristics**

$V_{IN}$  = xx;  $R_L$  = xx;  $T_A$  = Operating Temperature Range, **bold** values indicate -40°C ≤  $T_A$  ≤ +85°C; unless noted

| Parameter                                                   | Condition                                         | Min                  | Тур  | Max                  | Units |

|-------------------------------------------------------------|---------------------------------------------------|----------------------|------|----------------------|-------|

| Supply Voltage Range                                        | V <sub>CC</sub>                                   |                      |      | 5.5                  | V     |

| Supply Current                                              | I <sub>CC</sub> @ V <sub>CC</sub> = 5V (Note 4)   |                      | 18   | 30                   | μA    |

|                                                             | I <sub>CC</sub> @ V <sub>CC</sub> = 3.3V (Note 4) |                      | 15   | 25                   | μA    |

| /ST and /PBRST Input Levels                                 | V <sub>IH</sub> (Note 5)                          | 2                    |      | V <sub>CC</sub> +0.3 | V     |

|                                                             | V <sub>IH</sub> (Note 6)                          | V <sub>CC</sub> -0.4 |      | V <sub>CC</sub> +0.3 | V     |

|                                                             | V <sub>IL</sub>                                   | -0.3                 |      | 0.5                  | V     |

| Input Leakage, /ST (Note 7)                                 | I <sub>IL</sub>                                   |                      |      | ±1                   | μA    |

| Output Voltage, /RST, RST                                   | $I_{SOURCE} = 350 \mu A, V_{CC} = 3.3 V$          | 2.4                  |      |                      | V     |

| Output Voltage, /RST, RST                                   | I <sub>SINK</sub> = 10mA, V <sub>CC</sub> = 3.3V  |                      |      | 0.4                  | V     |

| Output Voltage                                              | V <sub>CC</sub> = 1.4V, I <sub>SINK</sub> = 50μA  |                      |      | 0.3                  | V     |

| V <sub>CC</sub> 5% Trip Point (Reset<br>Threshold Voltage)  | TOL = Gnd                                         | 2.8                  | 2.88 | 2.97                 | V     |

| V <sub>CC</sub> 10% Trip Point (Reset<br>Threshold Voltage) | TOL = V <sub>CC</sub>                             | 2.47                 | 2.55 | 2.64                 | V     |

| Input Capacitance, /ST, TOL                                 | C <sub>IN</sub> (Note 8)                          |                      |      | 5                    | pF    |

| Output Capacitance, /RST, RST                               | C <sub>OUT</sub> (Note 8)                         |                      |      | 7                    | pF    |

#### **AC Electrical Characteristics**

$V_{CC}$  = 4.5V to 5.5V;  $T_A$  = Operating Temperature Range, **bold** values indicate –40°C ≤  $T_A$  ≤ +85°C; unless noted

| 70 7                                                              |                                   | / \ |       |      |    |

|-------------------------------------------------------------------|-----------------------------------|-----|-------|------|----|

| /PBRST Min. Pulse Width, t <sub>PB</sub>                          | /PBRST = V <sub>IL</sub> (Note 9) | 20  |       |      | ms |

| /PBRST Delay, t <sub>PBD</sub>                                    |                                   | 1   | 4     | 20   | ms |

| Reset Active Time, t <sub>RST</sub>                               |                                   | 250 | 610   | 1000 | ms |

| /ST Pulse Width, t <sub>ST</sub>                                  |                                   | 20  |       |      | ms |

| /ST Timeout Period, t <sub>TD</sub>                               | TD = 0V                           | 62. | 5 150 | 250  | ms |

|                                                                   | TD = Open                         | 250 | 600   | 1000 | ms |

|                                                                   | TD = V <sub>CC</sub>              | 500 | 1200  | 2000 | ms |

| V <sub>CC</sub> Fall Time, t <sub>F</sub>                         |                                   | 40  |       |      | μs |

| V <sub>CC</sub> Rise Time, t <sub>R</sub>                         |                                   | 0   |       |      | ns |

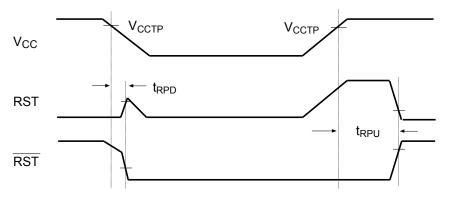

| V <sub>CC</sub> Detect to /RST Low and RST High, t <sub>RPD</sub> | V <sub>CC</sub> Falling (Note 10) |     | 5     | 8    | μs |

| V <sub>CC</sub> Detect to /RST Low and RST Low, t <sub>RPD</sub>  | V <sub>CC</sub> Falling (Note 9)  | 250 | 610   | 1000 | μs |

- Note 1. Exceeding the absolute maximum rating may damage the device.

- Note 2. The device is not guaranteed to function outside its operating rating.

- Note 3. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5k in series with 100pF.

- $\textbf{Note 4.} \quad I_{CC} \text{ is measured with /PBRST and all outputs open and inputs within 0.5V of supply rails}$

- **Note 5.** Measured with  $V_{CC} \ge 2.7V$

- **Note 6.** Measured with  $V_{CC} < 2.7V$

- Note 7. /PBRST has an internal pull-up resistor to  $\rm V_{CC}$  (typ.  $40k\Omega)$

- **Note 8.** Guaranteed by design at  $T_A = 25^{\circ}C$

- Note 9. /PBRST must be held low for a minimum of 20ms to guarantee a reset

- Note 10.  $V_{CC}$  falling a 8.5mV/ $\mu$ s

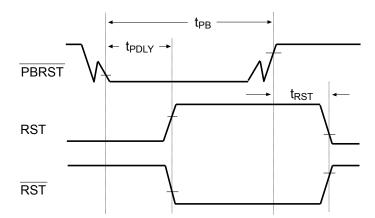

# **Timing Diagrams**

Figure 1. Power-Up/Power-Down Sequence

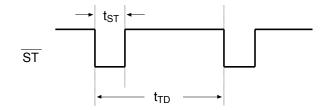

Figure 2. Watchdog Input

Figure 3. Pushbutton Reset

#### **Applications Information**

#### **Power Monitor**

The /RST and RST pins are asserted whenever  $V_{CC}$  falls below the reset threshold voltage as determined by the TOL pin. A 5% tolerance level (4.62V reset threshold voltage) can be selected by connecting the TOL pin to ground and a 10% tolerance can be selected by connecting the TOL pin to  $V_{CC}$ . The reset pins will remain asserted for a period of 250ms after  $V_{CC}$  has risen above the reset threshold voltage. The reset function ensures the microprocessor is properly reset and powers up into a known condition after a power failure. /RST will remain valid with  $V_{CC}$  as low as 1.4V.

#### **Watchdog Timer**

The microprocessor can be mounted by connecting the /ST pin (watchdog input) to a bus line or I/O line. If a high-to-low does not occur on the/ST pin within the watchdog timeout

period (determined by the TD pin, see Table 1.), the /RST and the RST will remain asserted for 250ms when this occurs. A minimum pulse of 75ns or any transition high-to-low on the /ST pin will reset the watchdog timer. The watchdog timer will be reset if /ST sees a valid transition within the watchdog timeout period.

#### **Pushbutton Reset Input**

The /PBRST input can be driven with a manual pushbutton switch or with external logic signals. the input is internally debounced and requires an active low signal to force the reset outputs into their active states. The /PBRST input will recognize any pulse that is 20ms in duration or greater and will ignore all pulses that are less than 1ms in duration.

### **Block Diagram**

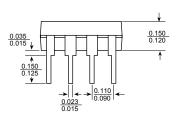

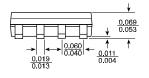

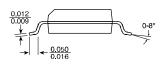

### **Package Information**

8-Pin PDIP (N)

8-Pin SOIC (M)

#### MICREL INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

This information furnished by Micrel in this data sheet is believed to be accurate and reliable. However no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2000 Micrel, Inc.