# VSC7984 Datasheet

12.5 Gbps Electroabsorption Modulator Driver

## **FEATURES**

- 5 V or -5.2 V power supply operation

- Selectable data retiming

- AC-coupled inputs

- Internally-stabilized modulation and bias outputs

- Excellent output return loss

- 300 mV differential input sensitivity

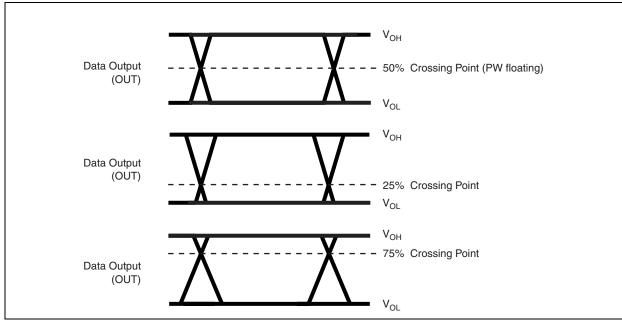

- Programmable output data eye crossing point

- 2.5 V on-chip voltage reference

- On-chip temperature monitor

- Output Enable

# **GENERAL DESCRIPTION**

## **APPLICATIONS**

- SONET OC-192 and SDH STM-64 transmission systems up to 12.5 Gbps

- 10 Gigabit Ethernet (GbE) modules

- Very Short Reach (VSR) modules

- Fiber optic transponder and transceiver modules

- SONET/SDH test equipment

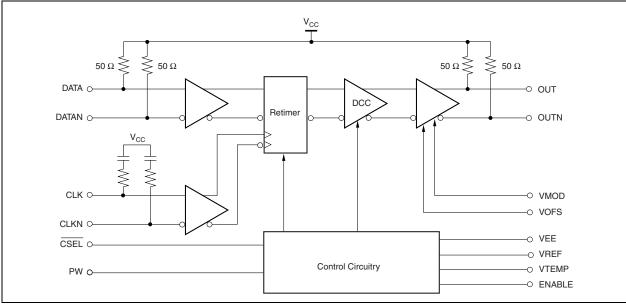

The VSC7984 is a 12.5 Gbps electroabsorption modulator (EAM) driver for SONET/SDH and 10 GbE applications. It provides selectable data retiming to improve jitter performance and controls for output bias voltage, modulation voltage, and duty cycle. Internal operational amplifiers and an on-chip voltage reference preclude the need for additional off-chip circuitry to stabilize modulation and offset voltages. A temperature-monitor output reflects the internal device temperature to simplify testing and to verify that the device is not being operated beyond its recommended maximum temperature.

The VSC7984 is available in a 24-pin, plastic quad flat no-lead (QFN) package. The device is also available in a lead(Pb)-free package, VSC7984XYF.

# **REVISION HISTORY**

This section describes the changes that were implemented in this document. The changes are listed by revision, starting with the most current publication.

## **Revision 4.1**

Revision 4.1 of this datasheet was published on January 19, 2007. The following is a summary of the changes implemented in the datasheet:

- The VSC7984 device is now available in a lead(Pb)-free package.

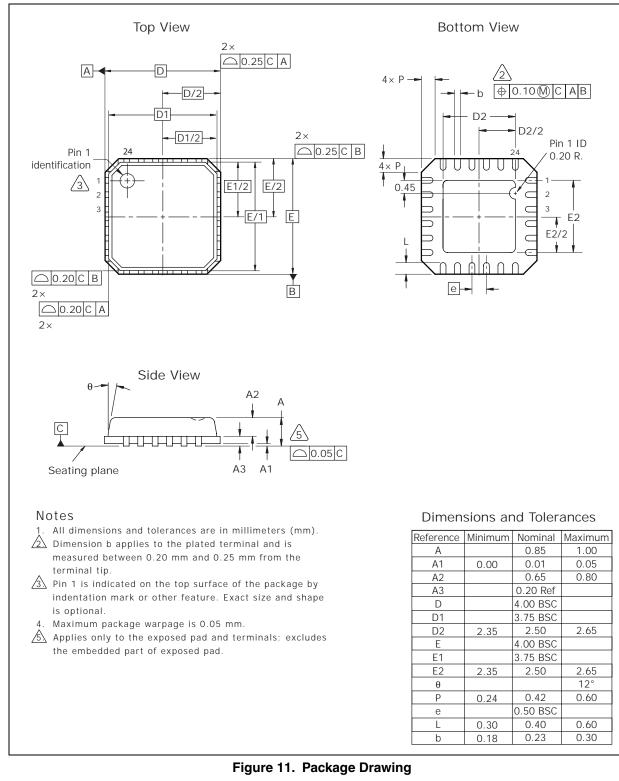

- The package drawing was updated to display the correct number of pins. For more information, see Figure 11, page 14.

#### **Revision 4.0**

Revision 4.0 of this datasheet was published on November 17, 2004. This was the first production-level publication of the document.

## **FUNCTIONAL DESCRIPTION**

The advantages of the VSC7984 device are its excellent output match, data retiming, internal stabilization of bias and modulation, and small package size. The VSC7984 provides up to 2.7 V of output modulation swing and up to 1.4 V of voltage offset (or bias). The output compliance (the lowest achievable peak level of output swing) is –3.5 V. Data retiming provides a means of reducing source jitter, as well as an Output Enable feature that disables modulation for low power modes. An on-chip reference provides a 2.5 V output relative to the most negative rail, which can be used to stabilize modulation and bias voltages over temperature and supply. An on-chip temperature monitor output is also provided for monitoring the internal thermal status.

The VSC7984 inputs are to be AC-coupled and the outputs DC-coupled. For assistance with other configurations, contact your local Vitesse sales representative.

#### ENABLE

When connected to the most negative rail or left floating, the ENABLE input shuts down the output modulation and bias voltages. Connect to the most positive rail for normal operation.

### Voltage Reference

The voltage reference provides a 2.5 V output for stabilizing modulation and bias set points. The modulation and bias control voltages should be relative to the most negative rail. For -5.2 V applications, the control voltages must track power supply variations.

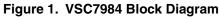

#### **Temperature Monitor Output**

The temperature monitor output (VTEMP) output provides a voltage proportional to the die temperature. This is useful for correlating die temperature in various environments. The temperature monitor may then be used to verify thermal designs in the user application.

Figure 2. VTEMP vs. Junction Temperature

#### **Power Consumption**

The VSC7984 consumes 300 mA typical from a -5.2 V supply and 315 mA maximum with a 2.5 V output swing. The following equations provide the typical current consumption for a given modulation and offset setting:

$$P_D = 5.5 \text{ V} \times I_{EE} = 5.5 \text{ V} \times [165 \text{ mA} + (V_{OM}/25) + 35 \text{ mA}] \text{ for } V_{OM} < 1.4 \text{ V}$$

(EQ 1)

$$P_D = 5.5 \text{ V} \times I_{EE} = 5.5 \text{ V} \times [165 \text{ mA} + (V_{OM}/25) + (-0.024 \times (V_{OM}) + 0.07)] \text{ for } V_{OM} > 1.4 \text{ V}$$

(EQ 2)

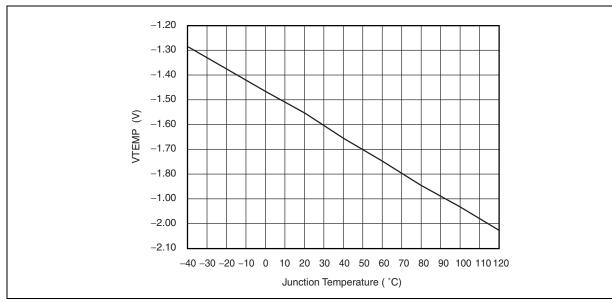

Figure 3. Output Voltage Range Specifications

## Modulation, Bias, and Data Eye Crossing Point

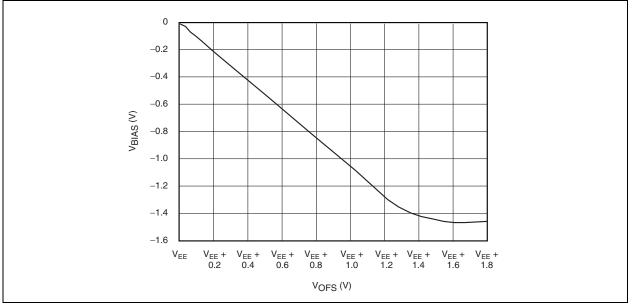

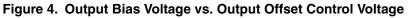

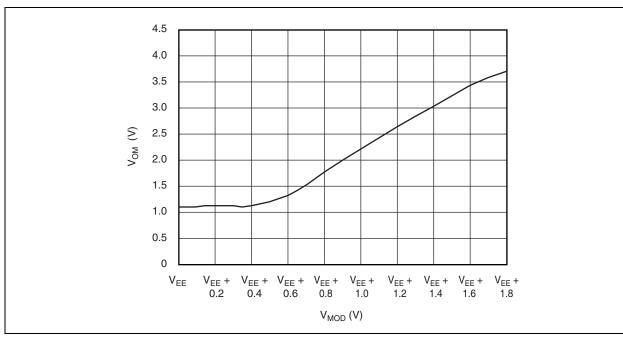

Internal feedback stabilizes the VSC7984 modulation and offset voltages so no external operational amplifiers are required to stabilize modulation and bias currents. For optimal stability, it is recommended that a reference voltage relative to the most negative rail be used to set the VMOD and VOFS control voltages. The graphs in Figure 4, page 5, Figure 5, page 5, and Figure 6, page 6 depict bias voltage, modulation voltage, and data eye crossing point range versus their control voltage.

Figure 5. Output Modulation Voltage vs. Output Modulation Control Voltage

5 of 16

VMDS-10029 Revision 4.1

January 19, 2007

Figure 6. Data Eye Crossing vs. Pulse Width Control Voltage

Downloaded by YASSER\_MOHAMMAD@SILICONEXPERT.COM on July 9, 2008 from Vitesse.com

# **ELECTRICAL SPECIFICATIONS**

This section provides the DC characteristics, AC characteristics, recommended operating conditions, and stress ratings for the VSC7984 device.

## **DC Characteristics**

Specifications are guaranteed over the recommended operating conditions listed in Table 3, page 10. Data input pattern at PRBS  $2^{31}$ -1 and 11.3 Gbps, unless otherwise noted.

| Symbol                | Parameter                                                            | Minimum                | Typical                | Maximum                | Unit | Condition                                         |

|-----------------------|----------------------------------------------------------------------|------------------------|------------------------|------------------------|------|---------------------------------------------------|

| $V_{CC} - V_{EE}$     | Power supply voltage                                                 | 4.75                   | 5.0                    | 5.5                    | V    |                                                   |

| I <sub>EE</sub>       | Power supply current (nominal bias and modulation current)           |                        | 300                    | 315                    | mA   | V <sub>OM</sub> = 2.5 V, V <sub>BIAS</sub> = 1 V. |

| P <sub>DNOMINAL</sub> | Power dissipation (nominal bias and modulation current)              |                        | 1510                   | 1735                   | mW   | $V_{OM} = 2.5 \text{ V}, V_{BIAS} = 1 \text{ V}.$ |

| IQ                    | Quiescent power supply current                                       |                        | 150                    | 160                    | mA   | ENABLE = LOW.                                     |

| P <sub>DQ</sub>       | Quiescent power dissipation                                          |                        | 780                    | 880                    | mW   | ENABLE = LOW.                                     |

| V <sub>MOD</sub>      | Output modulation control voltage                                    | V <sub>EE</sub>        |                        | V <sub>EE</sub> + 2.0  | V    | See Figure 5.                                     |

| V <sub>OFS</sub>      | Output offset control voltage for<br>output bias                     | V <sub>EE</sub>        |                        | V <sub>EE</sub> + 2.0  | V    | See Figure 4.                                     |

| V <sub>BIAS_MAX</sub> | Maximum output bias voltage                                          |                        | V <sub>CC</sub> – 1.40 | V <sub>CC</sub> – 1.15 | V    | $R_L = 50 \Omega.$<br>See Figure 4.               |

| V <sub>IH</sub>       | Input HIGH voltage (ENABLE)                                          | V <sub>CC</sub> – 3.0  |                        |                        | V    |                                                   |

| V <sub>IL</sub>       | Input LOW voltage (ENABLE)                                           |                        |                        | V <sub>CC</sub> - 4.0  | V    |                                                   |

| V <sub>REF</sub>      | Reference voltage output                                             | V <sub>EE</sub> + 2.4  | V <sub>EE</sub> + 2.5  | V <sub>EE</sub> + 2.7  | V    | C <sub>LOAD</sub> < 100 pF.                       |

| I <sub>VREF</sub>     | Reference voltage current output                                     |                        |                        | 4                      | mA   | Sourcing.                                         |

| V <sub>TEMP</sub>     | Temperature monitor output voltage<br>(±6 °C part-to-part variation) | V <sub>CC</sub> – 1.58 |                        | V <sub>CC</sub> – 1.51 | V    | T <sub>J</sub> = 20 °C.<br>See Figure 2.          |

|                       |                                                                      | V <sub>CC</sub> – 2.05 |                        | V <sub>CC</sub> – 1.99 | V    | T <sub>J</sub> = 120 °C.<br>See Figure 2.         |

#### Table 1. DC Characteristics

### **AC Characteristics**

Specifications are guaranteed over the recommended operating conditions listed in Table 3, page 10. Data input pattern at PRBS  $2^{31}$ -1 and 11.3 Gbps, unless otherwise noted.

#### Table 2. AC Characteristics

| Symbol                          | Parameter                                    | Minlmum               | Typical  | Maximum               | Unit | Condition                                                                                                                                                                                                                  |

|---------------------------------|----------------------------------------------|-----------------------|----------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f <sub>DATA</sub>               | Data rate                                    |                       | 11.3     | 12.5                  | Gbps | NRZ.                                                                                                                                                                                                                       |

| f <sub>CLK</sub>                | Clock rate                                   | 1                     | 11.3     | 12.5                  | GHz  |                                                                                                                                                                                                                            |

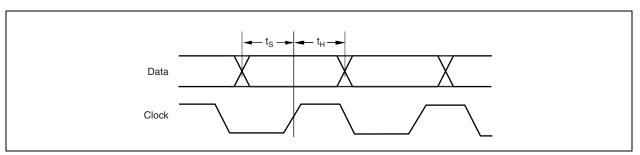

| V <sub>IN</sub>                 | Single-ended data input voltage amplitude    | 0.3                   |          | 1.0                   | V    | AC-coupled, measured peak-<br>to-peak. See Figure 9.                                                                                                                                                                       |

|                                 | Differential data input voltage<br>amplitude | 0.3                   |          | 1.0                   | V    | AC-coupled, measured peak-<br>to-peak (150 mV per side).<br>See Figure 9.                                                                                                                                                  |

| V <sub>CLK</sub>                | Single-ended clock input voltage amplitude   | 0.4                   |          | 1.0                   | V    | AC-coupled, measured peak-<br>to-peak.<br>See Figure 9.                                                                                                                                                                    |

|                                 | Differential clock input voltage amplitude   | 0.4                   |          | 1.0                   | V    | AC-coupled, measured peak-<br>to-peak (200 mV per side).<br>See Figure 9.                                                                                                                                                  |

| V <sub>OC</sub>                 | Output compliance voltage                    |                       |          | V <sub>CC</sub> – 3.5 | V    | $ \begin{array}{l} R_{L} = 50 \; \Omega, \; V_{CC} - V_{EE} \geq 4.9 \; V \\ V_{OM} \leq 2.7 \; V. \; See \ Figure \ 3. \end{array} $                                                                                      |

|                                 |                                              |                       |          | V <sub>CC</sub> – 3.3 | V    | $\label{eq:RL} \begin{split} \text{R}_{\text{L}} &= 50 \ \Omega \text{, } \text{V}_{\text{CC}} - \text{V}_{\text{EE}} \geq 4.75 \ \text{V} \\ \text{V}_{\text{OM}} \leq 2.7 \ \text{V} \text{. See Figure 3.} \end{split}$ |

| V <sub>OM</sub>                 | Output modulation voltage                    | 1.4                   |          | 2.7                   | V    | R <sub>L</sub> = 50 Ω.                                                                                                                                                                                                     |

| I <sub>OM_DIS</sub>             | Disabled output current                      |                       |          | 5                     | mA   | ENABLE = LOW.                                                                                                                                                                                                              |

| t <sub>R</sub> , t <sub>F</sub> | Output rise time and fall time               |                       | 25       | 35                    | ps   | 20% to 80%, $R_L = 50 \Omega$ .                                                                                                                                                                                            |

| DCC                             | Data eye crossing point range                | 25                    |          | 85                    | %    | See Figure 6 and Figure 7.                                                                                                                                                                                                 |

| DCC <sub>STAB</sub>             | Data eye crossing point stability            | -7                    |          | 7                     | %    |                                                                                                                                                                                                                            |

| V <sub>PW</sub>                 | Pulse width control input <sup>(1)</sup>     | V <sub>EE</sub> + 0.5 |          | V <sub>EE</sub> + 2.5 | V    | For 50% crossing point at OUT, set $V_{PW} = V_{EE} + 1.1 V$ . See Figure 6.                                                                                                                                               |

| –OVS<br>+OVS                    | Output undershoot /overshoot                 | -12                   |          | 10                    | %    | V <sub>OM</sub> > 1.4 V.                                                                                                                                                                                                   |

| CSEL                            | Clock select                                 |                       | Floating |                       | V    | Unclocked mode.                                                                                                                                                                                                            |

|                                 |                                              | V <sub>EE</sub>       |          | V <sub>EE</sub> + 0.3 | V    | Clocked mode.                                                                                                                                                                                                              |

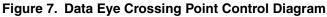

| t <sub>S</sub>                  | Setup time                                   | 0                     | -11      |                       | ps   | See Figure 8.                                                                                                                                                                                                              |

| t <sub>H</sub>                  | Hold time                                    | 30                    | 25       |                       | ps   | See Figure 8.                                                                                                                                                                                                              |

| J <sub>TOT_rms</sub>            | Total jitter, rms                            |                       | 2.1      | 4                     | ps   | Clocked mode.                                                                                                                                                                                                              |

|                                 |                                              |                       | 2.2      | 6                     | ps   | Unclocked mode.                                                                                                                                                                                                            |

| J <sub>TOT_p-p</sub>            | Total jitter, peak-to-peak                   |                       | 12       | 16                    | ps   | Clocked mode.                                                                                                                                                                                                              |

|                                 |                                              |                       | 14       | 18                    | ps   | Unclocked mode.                                                                                                                                                                                                            |

| S <sub>11</sub>                 | Clock input return loss                      |                       | -11      |                       | dB   | 1 GHz to 10 GHz.                                                                                                                                                                                                           |

|                                 |                                              |                       | -9       | Ī                     | dB   | 10 GHz to 15 GHz.                                                                                                                                                                                                          |

| S <sub>11</sub>                 | Data input return loss                       |                       | -11      |                       | dB   | 50 MHz to 10 GHz.                                                                                                                                                                                                          |

|                                 |                                              |                       | -10      | T                     | dB   | 10 GHz to 15 GHz.                                                                                                                                                                                                          |

| S <sub>22</sub>                 | Data output return loss                      |                       | -11      | T                     |      | 50 MHz to 7.5 GHz.                                                                                                                                                                                                         |

|                                 |                                              |                       | -9       |                       |      | 7.5 GHz to 10 GHz.                                                                                                                                                                                                         |

1. The VSC7984 is capable of moving the data eye crossing point to the very top and bottom of the eye diagram.

Figure 8. Setup and Hold Timing Diagram

Figure 9. Input Voltage Swing Diagram

VMDS-10029 Revision 4.1 January 19, 2007

### **Operating Conditions**

The following table shows the recommended operating conditions for the VSC7984 device.

Table 3. Recommended Operating Conditions

| Symbol          | Parameter                                          | Minimum | Typical | Maximum | Unit | Condition             |

|-----------------|----------------------------------------------------|---------|---------|---------|------|-----------------------|

| V <sub>CC</sub> | Power supply voltage for positive supply operation |         | 5.0     |         | V    | V <sub>EE</sub> = GND |

| V <sub>EE</sub> | Power supply voltage for negative supply operation |         | -5.2    |         | V    | V <sub>CC</sub> = GND |

| Т               | Operating temperature <sup>(1)</sup>               | -20     |         | 95      | °C   |                       |

1. Lower limit of specification is ambient temperature, and upper limit is case temperature.

### **Stress Ratings**

Stresses listed in the following table may be applied to devices one at a time without causing permanent damage. Functionality at or exceeding the values listed is not implied. Exposure to these values for extended periods may affect device reliability.

Table 4. Stress Ratings

| Symbol            | Parameter                                         | Minimum             | Maximum             | Unit |

|-------------------|---------------------------------------------------|---------------------|---------------------|------|

| $V_{CC} - V_{EE}$ | Power supply voltage                              | 0                   | 6                   | V    |

| I <sub>EE</sub>   | Supply current                                    |                     | 500                 | mA   |

| $V_{IN}, V_{CLK}$ | Input voltage                                     | V <sub>CC</sub> – 2 | V <sub>CC</sub> + 1 | V    |

| V <sub>OUT</sub>  | Output voltage                                    |                     | $V_{CC} - 4$        | V    |

| V <sub>MOD</sub>  | Output voltage modulation control voltage         | $V_{EE} - 0.5$      | V <sub>CC</sub>     | V    |

| V <sub>OFS</sub>  | Output voltage offset control voltage             | $V_{EE} - 0.5$      | V <sub>CC</sub>     | V    |

| V <sub>PW</sub>   | Pulse width control voltage                       | $V_{EE}$            | V <sub>CC</sub>     | V    |

| Τ <sub>S</sub>    | Storage temperature                               | -55                 | 140                 | °C   |

| V <sub>ESD</sub>  | Electrostatic discharge voltage, human body model | -250                | 250                 | V    |

#### ELECTROSTATIC DISCHARGE

This device can be damaged by ESD. Vitesse recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures may adversely affect reliability of the device.

## **PIN DESCRIPTIONS**

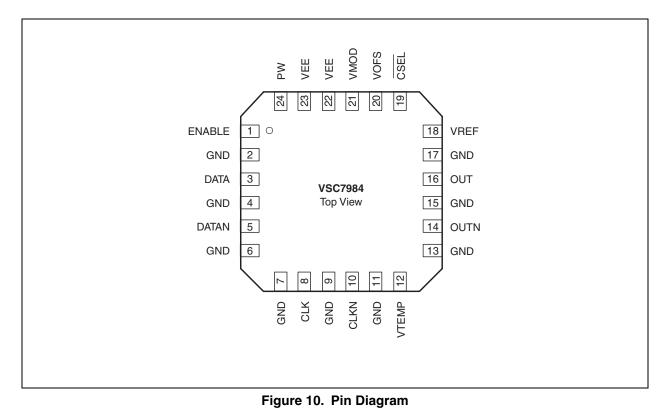

The VSC7984 device has 24-pins, which are described in this section.

### Pin Diagram

#### **Pin Identifications**

This section contains the pin descriptions for the VSC7984 device.

#### Table 5. Pin Identifications

| Pin | Signal Name | I/O   | Description                                                                                   |

|-----|-------------|-------|-----------------------------------------------------------------------------------------------|

| 1   | ENABLE      | I     | Enables output modulation and bias voltage.                                                   |

| 2   | GND         | Power | Ground.                                                                                       |

| 3   | DATA        | I     | Data input, true.                                                                             |

| 4   | GND         | Power | Ground.                                                                                       |

| 5   | DATAN       | I     | Data input, complement.                                                                       |

| 6   | GND         | Power | Ground.                                                                                       |

| 7   | GND         | Power | Ground.                                                                                       |

| 8   | CLK         | I     | Clock input, true.                                                                            |

| 9   | GND         | Power | Ground.                                                                                       |

| 10  | CLKN        | I     | Clock input, complement.                                                                      |

| 11  | GND         | Power | Ground.                                                                                       |

| 12  | VTEMP       | 0     | Device temperature monitor output.                                                            |

| 13  | GND         | Power | Ground.                                                                                       |

| 14  | OUTN        | 0     | Data output, complement.                                                                      |

| 15  | GND         | Power | Ground.                                                                                       |

| 16  | OUT         | 0     | Data output, true.                                                                            |

| 17  | GND         | Power | Ground.                                                                                       |

| 18  | VREF        | 0     | Reference voltage.                                                                            |

| 19  | CSEL        | Ι     | Clock enable. For clock mode, connect to V <sub>EE</sub> ; leave floating for unclocked mode. |

| 20  | VOFS        | I     | Output bias control. See Figure 4, page 5.                                                    |

| 21  | VMOD        | I     | Output modulation control. See Figure 5, page 5.                                              |

| 22  | VEE         | Power | Negative power supply.                                                                        |

| 23  | VEE         | Power | Negative power supply.                                                                        |

| 24  | PW          | I     | Pulse width control for data eye crossing point, true.                                        |

1. A voltage HIGH on the data input (pin 3) corresponds to a voltage HIGH on the data output (pin 16).

## **PACKAGE INFORMATION**

A significant advantage of the VSC7984 device is its small plastic package. VSC7984YF is a 24-pin, plastic quad flat no-lead (QFN) package with an exposed pad, 4 mm  $\times$  4 mm body size, 0.65 mm body thickness, 0.5 mm pin pitch, and 1 mm maximum height. The device is also available in a lead(Pb)-free package, VSC7984XYF.

Lead(Pb)-free products from Vitesse comply with the temperatures and profiles defined in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

The backside of the die is mounted directly to a heat spreader with conductive epoxy. The exposed heat spreader must be connected to the most negative power supply (typically -5 V) or must be left floating.

The primary heat path is through the exposed heat spreader on the bottom of the package. Some heat can be removed through the top of the package; however, it is recommended to thermally connect the exposed heat spreader to the PCB. Contact your local Vitesse sales representative for detailed information about the PCB design.

#### **Package Drawing**

Downloaded by YASSER\_MOHAMMAD@SILICONEXPERT.COM on July 9, 2008 from Vitesse.com

#### **Moisture Sensitivity**

This device is rated moisture sensitivity level 3 or better as specified in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

## **ORDERING INFORMATION**

The VSC7984 device is available in two package types. VSC7984YF is a 24-pin, plastic quad flat no-lead (QFN) package with an exposed pad, 4 mm × 4 mm body size, 0.65 mm body thickness, 0.5 mm pin pitch, and 1 mm maximum height. The device is also available in a lead(Pb)-free package, VSC7984XYF.

Lead(Pb)-free products from Vitesse comply with the temperatures and profiles defined in the joint IPC and JEDEC standard IPC/JEDEC J-STD-020. For more information, see the IPC and JEDEC standard.

The following table lists the ordering information for the VSC7984 device.

| VSC7984 | 12.5 Gbps Clocked Modulator Driver |

|---------|------------------------------------|

|---------|------------------------------------|

| Part Number | Description                                                                                                                                             |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSC7984YF   | 24-pin, plastic QFN with an exposed pad, 4 mm $\times$ 4 mm body size, 0.65 mm body thickness, 0.5 mm pin pitch, and 1 mm maximum height                |

| VSC7984XYF  | Lead(Pb)-free, 24-pin, plastic QFN with an exposed pad, 4 mm $\times$ 4 mm body size, 0.65 mm body thickness, 0.5 mm pin pitch, and 1 mm maximum height |

#### CORPORATE HEADQUARTERS

Vitesse Semiconductor Corporation 741 Calle Plano Camarillo, CA 93012 Tel: 1-800-VITESSE • FAX:1-(805) 987-5896

For application support, latest technical literature, and locations of sales offices, please visit our web site at **www.vitesse.com**

Copyright © 2003–2004, 2007 by Vitesse Semiconductor Corporation

PRINTED IN THE U.S.A

Vitesse Semiconductor Corporation ("Vitesse") retains the right to make changes to its products or specifications to improve performance, reliability or manufacturability. All information in this document, including descriptions of features, functions, performance, technical specifications and availability, is subject to change without notice at any time. While the information furnished herein is held to be accurate and reliable, no responsibility will be assumed by Vitesse for its use. Furthermore, the information contained herein does not convey to the purchaser of microelectronic devices any license under the patent right of any manufacturer.

Vitesse products are not intended for use in life support products where failure of a Vitesse product could reasonably be expected to result in death or personal injury. Anyone using a Vitesse product in such an application without express written consent of an officer of Vitesse does so at their own risk, and agrees to fully indemnify Vitesse for any damages that may result from such use or sale.

Vitesse Semiconductor Corporation is a registered trademark. All other products or service names used in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other trademarks or registered trademarks mentioned herein are the property of their respective holders.

VMDS-10029 Revision 4.1 January 19, 2007