# **SSC7150**

# **Motion Coprocessor**

#### **Product Features**

- · High Performance 32-bit Embedded Controller

- · Low power 7.65mA (typ) in active mode

- System in deep sleep consumes 70μA (typ)

- 3.3-Volt I/O

- Package

- 6mm x 6mm, 28-pin QFN

#### **Sensor Firmware**

- · Sensor fusion firmware features include:

- Self-contained 9-axis sensor fusion

- Sensor data pass-through

- Fast in-use background calibration of all sensors and calibration monitor

- Magnetic immunity: Enhanced magnetic distortion detection and suppression

- Gyroscope drift cancellation

- Easy to implement complete turnkey sensor fusion solution

- Sensor power management

- · Sensors Supported

- Bosch BMC150 Geomagnetic Sensor/Accelerometer

- Bosch BMG160 Gyroscope

#### **Hardware Features**

The hardware features in the SSC7150 motion coprocessor include the following:

- Two I<sup>2</sup>C Controllers

- Supports I<sup>2</sup>C bus speeds to 400kHz

- Host Interface Supports Slave Operation

- Sensor Interface Supports Master Operation

- · Low Power Modes

#### **Target Markets**

- · Remote Controls, Gaming

- · Fitness Monitoring

- · Internet of Things Applications

#### **Description**

The SSC7150 motion coprocessor is a low-power, flexible, turnkey solution. SSC7150 makes implementing sensor fusion easy for motion-based embedded applications. Microchip created this solution, enabling faster time to market without the need for sensor-fusion expertise. The SSC7150 is extremely efficient. Low average current while running complex sensor-fusion algorithms results in lower power consumption for multiple applications.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# SSC7150

#### **Table of Contents**

| 1.0 Pin Configuration                | 4  |

|--------------------------------------|----|

| 2.0 System Block Diagram             | 10 |

| 3.0 Guidelines for Getting Started   |    |

| 4.0 Electrical Characteristics       |    |

| Appendix A: Revision History         | 25 |

| The Microchip Web Site               | 26 |

| Customer Change Notification Service | 26 |

| Customer Support                     | 26 |

| Product Identification System        | 27 |

#### 1.0 PIN CONFIGURATION

#### 1.1 Description

The Pin Configuration chapter includes a Pin Diagram, Pin List, Pin Description and Package Details.

#### 1.2 Terminology and Symbols for Pins/Buffers

| Term | Definition                                                               |

|------|--------------------------------------------------------------------------|

| #    | The '#' sign at the end of a signal name indicates an active-low signal. |

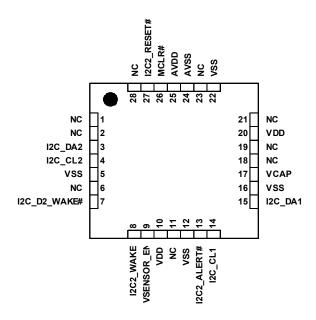

# 1.3 Pin Diagram

#### FIGURE 1-1: 28 PIN QFN PIN DIAGRAM

**Note:** The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to VSS externally.

#### 1.4 Pin List

The Pin List is shown in Table 1-1.

TABLE 1-1: SSC7150 28 QFN PIN CONFIGURATION

| 28 QFN | Din Name     |

|--------|--------------|

| Number | Pin Name     |

| 1      | NC           |

| 2      | NC           |

| 3      | I2C_DA2      |

| 4      | I2C_CL2      |

| 5      | VSS          |

| 6      | NC           |

| 7      | I2C_D2_WAKE# |

| 8      | I2C2_WAKE    |

| 9      | VSENSOR_EN   |

| 10     | VDD          |

| 11     | NC           |

| 12     | VSS          |

| 13     | I2C2_ALERT#  |

| 14     | I2C_CL1      |

| 15     | I2C_DA1      |

| 16     | VSS          |

| 17     | VCAP         |

| 18     | NC           |

| 19     | NC           |

| 20     | VDD          |

| 21     | NC           |

| 22     | VSS          |

| 23     | NC           |

| 24     | AVSS         |

| 25     | AVDD         |

| 26     | MCLR#        |

| 27     | I2C2_RESET#  |

| 28     | NC           |

#### 1.4.1 FIVE VOLT TOLERANT PINS

Table 1-2 lists the 5 Volt tolerant pins in the SSC7150. All other pins in the device are 3.3V only.

TABLE 1-2: 5V-TOLERANT PINS

| Pin Number | Pin Name    |

|------------|-------------|

| 13         | I2C2_ALERT# |

| 14         | I2C_CL1     |

| 15         | I2C_DA1     |

| 26         | MCLR#       |

#### 1.5 Pin Description

#### 1.5.1 OVERVIEW

The following tables describe the signal functions in the SSC7150 pin configuration. See Section 1.6, "Notes for Tables in this Chapter," on page 7 for notes that are referenced in the Pin Description tables.

#### 1.5.2 HOST INTERFACE

The SSC7150 can be used with an  $I^2$ C host interface. The pins required for each interface are shown in Table 1-3 and Table 1-4. See the associated Notes for board connection information for the unused interface.

TABLE 1-3: I<sup>2</sup>C HOST INTERFACE

| I2C Interface Signals         | s            |                                                 |       |

|-------------------------------|--------------|-------------------------------------------------|-------|

| Pin Ref. Number   Signal Name |              | Description                                     | Notes |

| 4                             | I2C_CL2      | I2C Controller Clock to Host Interface          |       |

| 3                             | I2C_DA2      | I2C Controller Data to Host Interface           |       |

|                               |              | Alert Interrupt signal from motion coprocessor  |       |

| 13                            | I2C2 ALERT#  | to Host. Used to tell Host data from motion     |       |

| 13                            | IZCZ_ALERI#  | coprocessor is ready to be sent out. Active low |       |

|                               |              | output.                                         |       |

|                               | I2C_D2_WAKE# | Used to wake the motion coprocessor from a      |       |

| 7                             |              | low power state due to host I2C                 |       |

| ,                             |              | communication. Active low input. Connect to     |       |

|                               |              | I2C_DA2.                                        |       |

|                               |              | Used to wake motion coprocessor from a Sleep    |       |

| 8                             | I2C2_WAKE    | state. This signal must be driven high at least |       |

| O                             |              | 11ms prior to sending any I2C traffic to the    |       |

|                               |              | motion coprocessor. Active high input.          |       |

| 27                            | I2C2 RESET#  | Reset input. Used to reset the host I2C         | •     |

| 21                            | IZUZ_NESEI#  | interface.                                      |       |

#### 1.5.3 I<sup>2</sup>C SENSOR INTERFACE

#### TABLE 1-4: I<sup>2</sup>C SENSOR INTERFACE

| I2C Sensor Interface |             |                                          |       |

|----------------------|-------------|------------------------------------------|-------|

| Pin Ref. Number      | Signal Name | Description                              | Notes |

| 14                   | I2C_CL1     | I2C Controller Clock to Sensor Interface |       |

| 15                   | I2C_DA1     | I2C Controller Data to Sensor Interface  |       |

#### 1.5.4 MISCELLANEOUS FUNCTIONS

#### TABLE 1-5: MISCELLANEOUS FUNCTIONS

| Miscellaneous Functions  |             |                                                |        |

|--------------------------|-------------|------------------------------------------------|--------|

| Pin Ref. Number          | Signal Name | Description                                    | Notes  |

| 26                       | MCLR#       | Master Clear (Reset) Input                     | Note 1 |

| 9 VSENSOR_EN             |             | Sensor voltage switch control output.          |        |

| 1, 2, 6, 11, 18, 19, 21, | NC          | Pins labelled NC should be left unconnected on |        |

| 23, 28                   | NC          | the board                                      |        |

#### 1.5.5 POWER INTERFACE

#### TABLE 1-6: POWER INTERFACE

| Power Interface |             |                                      |        |

|-----------------|-------------|--------------------------------------|--------|

| Pin Ref. Number | Signal Name | Description                          | Notes  |

| 17              | VCAP        | Internal Voltage Regulator Capacitor | Note 2 |

| 10, 20          | VDD         | VDD supply                           |        |

| 5, 12, 16, 22   | VSS         | VDD associated ground                |        |

| 25              | AVDD        | AVDD supply                          |        |

| 24              | AVSS        | AVDD associated ground               |        |

# 1.6 Notes for Tables in this Chapter

| Note 1 | A pull-up to VDD is required on the MCLR# pin. Use a 10K ohm pull-up resistor.                           |  |  |  |  |

|--------|----------------------------------------------------------------------------------------------------------|--|--|--|--|

| Note 2 | A low-ESR (1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage |  |  |  |  |

|        | regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at     |  |  |  |  |

|        | least a 6V rating, connected to ground. The type can be ceramic or tantalum.                             |  |  |  |  |

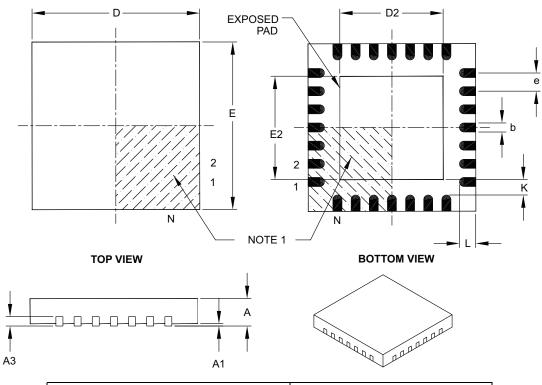

#### 1.7 Package Details

This section provides the technical details of the packages.

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |                  | MILLIMETERS    |                | 3    |  |

|------------------------|------------------|----------------|----------------|------|--|

|                        | Dimension Limits | MIN            | NOM            | MAX  |  |

| Number of Pins         | N                |                | 28             |      |  |

| Pitch                  | е                |                | 0.65 BSC       |      |  |

| Overall Height         | A                | 0.80           | 0.90           | 1.00 |  |

| Standoff               | A1               | 0.00           | 0.00 0.02 0.05 |      |  |

| Contact Thickness      | A3               | 0.20 REF       |                |      |  |

| Overall Width          | E                | 6.00 BSC       |                |      |  |

| Exposed Pad Width      | E2               | 3.65 3.70 4.20 |                | 4.20 |  |

| Overall Length         | D                | 6.00 BSC       |                |      |  |

| Exposed Pad Length     | D2               | 3.65 3.70 4.20 |                |      |  |

| Contact Width          | b                | 0.23 0.30 0.35 |                | 0.35 |  |

| Contact Length         | L                | 0.50 0.55 0.70 |                |      |  |

| Contact-to-Exposed Pad | K                | 0.20 – –       |                |      |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

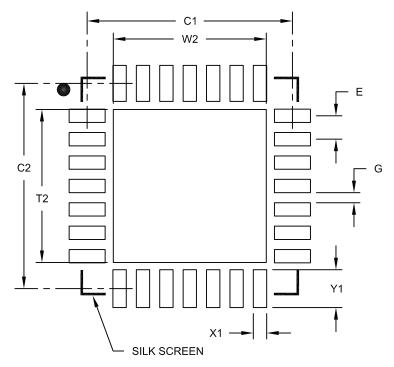

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

| Units                         |    | MILLIMETERS |      |      |

|-------------------------------|----|-------------|------|------|

| Dimension Limits              |    | MIN         | NOM  | MAX  |

| Contact Pitch E               |    | 0.65 BSC    |      |      |

| Optional Center Pad Width     | W2 |             |      | 4.25 |

| Optional Center Pad Length T2 |    |             |      | 4.25 |

| Contact Pad Spacing           | C1 |             | 5.70 |      |

| Contact Pad Spacing           | C2 |             | 5.70 |      |

| Contact Pad Width (X28)       | X1 |             |      | 0.37 |

| Contact Pad Length (X28)      | Y1 |             | ·    | 1.00 |

| Distance Between Pads G       |    | 0.20        |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

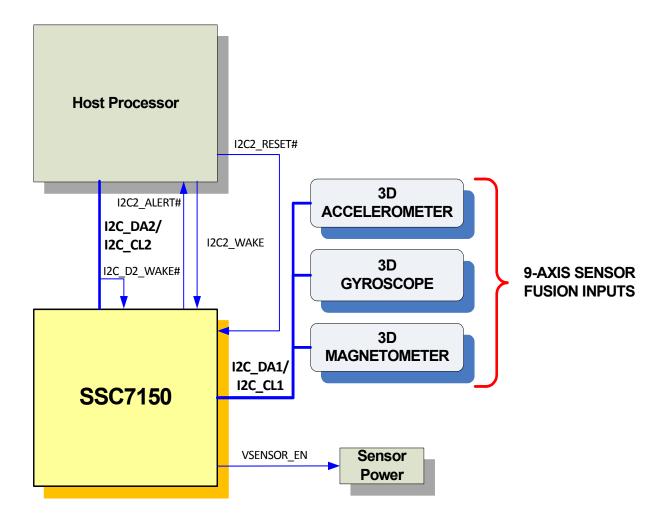

#### 2.0 SYSTEM BLOCK DIAGRAM

The SSC7150 system block diagram is shown in Figure 2-1.

FIGURE 2-1: SSC7150 SYSTEM BLOCK DIAGRAM

#### 3.0 GUIDELINES FOR GETTING STARTED

#### 3.1 Basic Connection Requirements

Getting started with the SSC7150 requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and VSS pins (see Section 3.2 "Decoupling Capacitors")

- All AVDD and AVSs pins, even if the ADC module is not used (see Section 3.2 "Decoupling Capacitors"). Note

that there is no ADC support in this device. See Note below.

- VCAP pin (see Section 3.3 "Capacitor on Internal Voltage Regulator (Vcap)")

- MCLR# pin (see Section 3.4 "Master Clear (MCLR#) Pin")

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

Refer to the following schematic for connection information:

SSC7150 Sensor Hub Module, Assy. 6753, Schematic Revision 1.4.

#### 3.2 Decoupling Capacitors

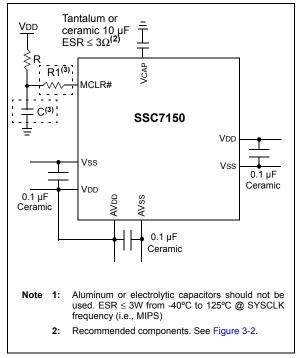

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 3-1. Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1 µF (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a

second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second

capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling

capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the

power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to

the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in

the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

#### FIGURE 3-1: RECOMMENDED MINIMUM CONNECTION

#### 3.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

#### 3.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 3.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 4.0 "Electrical Characteristics"** for additional information on CEFC specifications.

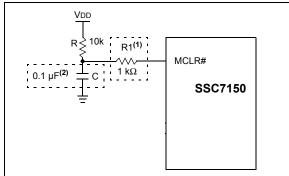

## 3.4 Master Clear (MCLR#) Pin

The MCLR# pin is the Device Reset pin. Pulling the MCLR# pin low generates a device Reset. Figure 3-2 illustrates a typical MCLR# circuit.

#### FIGURE 3-2: MCLR# PIN CONNECTIONS

#### **Recommended Components:**

- Note 1:  $470\Omega \le R1 \le 1\Omega$  will limit any current flowing into MCLR# from the external capacitor C, in the event of MCLR# pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

#### 4.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the SSC7150 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the SSC7150 devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                              | 40°C to +85°C        |

|-----------------------------------------------------------------------------|----------------------|

| Storage temperature                                                         | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                          | 0.3V to +4.0V        |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)    | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD ≥ 2.3V (Note 3) | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3) | 0.3V to +3.6V        |

| Maximum current out of Vss pin(s)                                           | 300 mA               |

| Maximum current into VDD pin(s) (Note 2)                                    | 300 mA               |

| Maximum output current sunk by any I/O pin                                  | 15 mA                |

| Maximum output current sourced by any I/O pin                               | 15 mA                |

| Maximum current sunk by all ports                                           | 200 mA               |

| Maximum current sourced by all ports (Note 2)                               | 200 mA               |

- **Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 4-1).

- 3: See the "Pin List" section for the 5V tolerant pins.

#### 4.1 DC Characteristics

TABLE 4-1: THERMAL OPERATING CONDITIONS

| Rating                                                                         | Symbol | Min. | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Industrial Temperature Devices                                                 |        |      |             |      |      |

| Operating Junction Temperature Range                                           | TJ     | -40  | _           | +125 | °C   |

| Operating Ambient Temperature Range                                            | TA     | -40  | _           | +85  | °C   |

| Power Dissipation: Internal Chip Power Dissipation: PINT = VDD x (IDD – S IOH) | PD     | ı    | PINT + PI/C | )    | W    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD - VOH} x IOH) + S (VOL x IOL))    |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                              | PDMAX  | (    | TJ – TA)/θJ | Α    | W    |

#### TABLE 4-2: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                        | Symbol | Typical | Max. | Unit | Notes |

|----------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 28-pin QFN | θЈА    | 35      | _    | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA (θJA) numbers are achieved by package simulations.

TABLE 4-3: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |         |                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |      |       |       |            |  |

|--------------------|---------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics                                                  | Min.                                                                                                                                                    | Тур. | Max.  | Units | Conditions |  |

| Operating          | Voltage |                                                                  | •                                                                                                                                                       | I    | 1     |       | 1          |  |

| DC10               | VDD     | Supply Voltage (Note 2)                                          | 2.3                                                                                                                                                     |      | 3.6   | V     | _          |  |

| DC12               | VDR     | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                    | _    | _     | V     | _          |  |

| DC16               | VPOR    | VDD Start Voltage<br>to Ensure Internal Power-on Reset<br>Signal | 1.75                                                                                                                                                    | _    | 2.1   | V     | _          |  |

| DC17               | SVDD    | VDD Rise Rate<br>to Ensure Internal Power-on Reset<br>Signal     | 0.00005                                                                                                                                                 | _    | 0.115 | V/μs  | _          |  |

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

<sup>2:</sup> Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. Refer to parameter BO10 in Table 4-7 for BOR values.

#### TABLE 4-4: DC CHARACTERISTICS: OPERATING/POWER-DOWN CURRENT

| DC CHARA      | CTERIST  | ICS                    |           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |            |  |  |  |  |

|---------------|----------|------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Parameter No. | Symbol   | Typical <sup>(3)</sup> | Max.      | Units                                                                                                                                                   | Conditions |  |  |  |  |

| Operating/P   | ower-Dow | n Current (No          | ote 1, 2) |                                                                                                                                                         |            |  |  |  |  |

| DC20          | IPEAK    | 19.5                   | 20.0      | mA                                                                                                                                                      | _          |  |  |  |  |

| DC30          | IACTIVE  | 7.65                   | 7.90      | mA                                                                                                                                                      | _          |  |  |  |  |

| DC40          | IDLE     | 1.77                   | 1.95      | mA                                                                                                                                                      | _          |  |  |  |  |

| DC50          | IPD      | 70                     | 150       | μΑ                                                                                                                                                      | _          |  |  |  |  |

- **Note 1:** A device's supply current is mainly a function of the operating voltage and frequency, as well as temperature.

- 2: The current measurements are as follows:

- Peak current (IPEAK):

This is the peak active current value when a sensor is actively providing environmental changes.

Active current (IACTIVE):

This is the average operating current value when a sensor is actively providing environmental changes.

• Idle current (IIDLE):

This is the average idle current value when no sensor is actively providing environmental changes (and the device is not in power-down mode).

• Power-Down current (IPD):

This is the current value when the device is in power-down mode. This is the state entered when the Host issues the SET\_POWER (Sleep) Command.

Wakeup from power-down mode requires the I2C2\_WAKE pin.

**3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE 4-5: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

| DC CHA        | RACTERI | STICS                          | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature-40°C $\leq$ TA $\leq$ +85°C |                        |            |       |                                                                       |  |  |  |

|---------------|---------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------|------------|-------|-----------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics                | Min.                                                                                                                       | Typical <sup>(1)</sup> | Max.       | Units | Conditions                                                            |  |  |  |

|               | VIL     | Input Low Voltage              |                                                                                                                            |                        |            |       |                                                                       |  |  |  |

| DI10          |         | I/O Pins                       | Vss                                                                                                                        | _                      | 0.2 VDD    | V     |                                                                       |  |  |  |

| DI18          |         | I2C_DAx, I2C_CLx               | Vss                                                                                                                        | _                      | 0.3 VDD    | V     | I <sup>2</sup> C disabled (Note 4)                                    |  |  |  |

| DI19          |         | I2C_DAx, I2C_CLx               | Vss                                                                                                                        | _                      | 0.8        | V     | I <sup>2</sup> C enabled (Note 4)                                     |  |  |  |

|               | VIH     | Input High Voltage             |                                                                                                                            |                        |            |       |                                                                       |  |  |  |

| DI20          |         | I/O Pins not 5V-tolerant (5)   | 0.65 VDD                                                                                                                   | _                      | Vdd        | V     | (Note 4,6)                                                            |  |  |  |

|               |         | I/O Pins 5V-tolerant (5)       | 0.65 VDD                                                                                                                   | _                      | 5.5        | V     |                                                                       |  |  |  |

| DI28          |         | I2C_DAx, I2C_CLx               | 0.65 VDD                                                                                                                   | _                      | 5.5        | V     | I <sup>2</sup> C disabled (Note 4,6)                                  |  |  |  |

| DI29          |         | I2C_DAx, I2C_CLx               | 2.1                                                                                                                        | _                      | 5.5        | V     | I <sup>2</sup> C enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>( <b>Note 4,6</b> ) |  |  |  |

|               | lıL     | Input Leakage Current (Note 3) |                                                                                                                            |                        |            |       |                                                                       |  |  |  |

| DI50          |         | I/O Ports                      | _                                                                                                                          | _                      | <u>+</u> 1 | μΑ    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-imped-<br>ance                       |  |  |  |

| DI55          |         | MCLR# <sup>(2)</sup>           | _                                                                                                                          | _                      | <u>+</u> 1 | μΑ    | VSS ≤ VPIN ≤ VDD                                                      |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR# pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Pin List" section for the 5V-tolerant pins.

- **6:** The VIH specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the device are provided to be recognized only as a logic "high" internally to the device. For External "input" logic inputs that require a pull-up source, to ensure the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the device.

TABLE 4-6: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

| DC CHA | RACTERI | STICS               | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ |      |      |       |                                      |

|--------|---------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--------------------------------------|

| Param. | Symbol  | Characteristic      | Min.                                                                                                                                                    | Тур. | Max. | Units | Conditions                           |

| DO10   | Vol     | Output Low Voltage  | _                                                                                                                                                       | _    | 0.4  | V     | IOL ≤ 10 mA, VDD = 3.3V              |

|        |         | I/O Pins            |                                                                                                                                                         |      |      |       |                                      |

| DO20   | Vон     | Output High Voltage | 1.5 <sup>(1)</sup>                                                                                                                                      | _    | _    | ٧     | $IOH \ge -14 \text{ mA}, VDD = 3.3V$ |

|        |         | I/O Pins            | 2.0 <sup>(1)</sup>                                                                                                                                      | _    | _    |       | $IOH \ge -12 \text{ mA}, VDD = 3.3V$ |

|        |         |                     | 2.4                                                                                                                                                     | _    | _    |       | $IOH \ge -10 \text{ mA}, VDD = 3.3V$ |

|        |         |                     | 3.0 (1)                                                                                                                                                 | _    | _    |       | IOH ≥ -7 mA, VDD = 3.3V              |

Note 1: Parameters are characterized, but not tested.

### TABLE 4-7: ELECTRICAL CHARACTERISTICS: BROWN-OUT RESET (BOR)

| DC CHAF       | RACTERIS | STICS                                                  | (unless otherwis                                  |   |     | rating Conditions: 2.3V to 3.6V wise stated) perature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |            |  |

|---------------|----------|--------------------------------------------------------|---------------------------------------------------|---|-----|-------------------------------------------------------------------------------------------------------------------|------------|--|

| Param.<br>No. | Symbol   | Characteristics                                        | Min. <sup>(1)</sup> Typical Max. Units Conditions |   |     |                                                                                                                   | Conditions |  |

| BO10          | Vbor     | BOR Event on VDD transition high-to-low <sup>(2)</sup> | 2.0                                               | _ | 2.3 | V                                                                                                                 | _          |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

#### TABLE 4-8: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |    |   |    |                                                                                           |

|--------------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|---|----|-------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min. Typical Max. Units Commen                                                                                                                          |    |   |    |                                                                                           |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                       | 10 | _ | μF | Capacitor must be low series resistance (1 ohm). Typical voltage on the VCAP pin is 1.8V. |

**<sup>2:</sup>** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized.

#### 4.2 AC Characteristics and Timing Parameters

The information contained in this section defines SSC7150 AC characteristics and timing parameters.

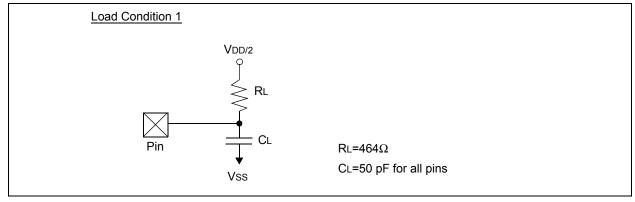

FIGURE 4-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 4-9: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                  |      | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |                               |    |                           |  |

|--------------------|--------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----|---------------------------|--|

| Param.<br>No.      | Symbol | Characteristics  | Min. | Typical <sup>(1)</sup>                                                                                                                                  | cal <sup>(1)</sup> Max. Units |    | Conditions                |  |

| DO56               | Сю     | All I/O pins     | _    | _                                                                                                                                                       | 50                            | pF |                           |  |

| DO58               | Св     | I2C_DAx, I2C_CLx | _    | _                                                                                                                                                       | 400                           | pF | In I <sup>2</sup> C™ mode |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

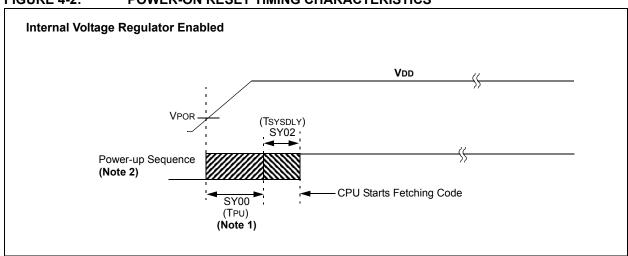

#### FIGURE 4-2: POWER-ON RESET TIMING CHARACTERISTICS

- **Note 1:** The power-up period will be extended if the power-up sequence completes before the device exits from BOR (VDD < VDDMIN).

- 2: Includes interval voltage regulator stabilization delay.

MCLR#

TMCLR

(SY20)

BOR

TBOR

(SY30)

TSysply)

(SY30)

SY02

CPU Starts Fetching Code

FIGURE 4-3: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 4-10: RESET TIMING**

| AC CHA        | RACTERI | STICS                                                                                                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ |                              |      |       |            |  |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|------------|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                                                                                                | Min.                                                                                                                                                    | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |

| SY00          | TPU     | Power-up Period<br>Internal Voltage Regulator<br>Enabled                                                                                      | _                                                                                                                                                       | 400                          | 600  | μs    | _          |  |

| SY02          | Tsysdly | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK <sup>(3)</sup> Delay before First instruction is Fetched. | _                                                                                                                                                       | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |

| SY20          | Tmclr   | MCLR# Pulse Width (low)                                                                                                                       | 2                                                                                                                                                       | _                            | _    | μs    |            |  |

| SY30          | TBOR    | BOR Pulse Width (low)                                                                                                                         | _                                                                                                                                                       | 1                            |      | μs    |            |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

3: SYSCLK is 48MHz

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

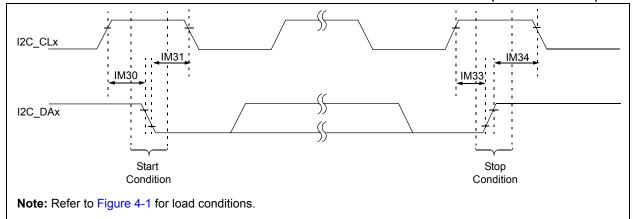

# FIGURE 4-4: I<sup>2</sup>Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

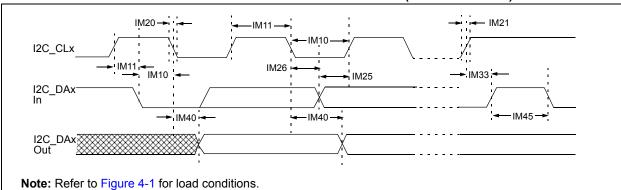

# FIGURE 4-5: I<sup>2</sup>Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

# SSC7150

TABLE 4-11: I<sup>2</sup>C BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        | RACTERI | STICS                |              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C |      |       |                                                                |  |  |

|---------------|---------|----------------------|--------------|-----------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol  | Charact              | eristics     | Min. <sup>(1)</sup>                                                                                             | Max. | Units | Conditions                                                     |  |  |

| IM10          | TLO:SCL | Clock Low Time       | 100 kHz mode | Трв * (BRG + 2)                                                                                                 | _    | μs    | _                                                              |  |  |

|               |         |                      | 400 kHz mode | TPB * (BRG + 2)                                                                                                 | _    | μs    |                                                                |  |  |

| IM11          | THI:SCL | Clock High Time      | 100 kHz mode | TPB * (BRG + 2)                                                                                                 | _    | μs    | _                                                              |  |  |

|               |         |                      | 400 kHz mode | TPB * (BRG + 2)                                                                                                 | _    | μs    |                                                                |  |  |

| IM20          | TF:SCL  | I2C_DAx and          | 100 kHz mode | _                                                                                                               | 300  | ns    | CB is specified to be                                          |  |  |

|               |         | I2C_CLx<br>Fall Time | 400 kHz mode | 20 + 0.1 CB                                                                                                     | 300  | ns    | from 10 to 400 pF                                              |  |  |

| IM21          | TR:SCL  | I2C_DAx and          | 100 kHz mode |                                                                                                                 | 1000 | ns    | CB is specified to be                                          |  |  |

|               |         | I2C_CLx<br>Rise Time | 400 kHz mode | 20 + 0.1 CB                                                                                                     | 300  | ns    | from 10 to 400 pF                                              |  |  |

| IM25          | Tsu:dat | Data Input           | 100 kHz mode | 250                                                                                                             |      | ns    | _                                                              |  |  |

|               |         | Setup Time           | 400 kHz mode | 100                                                                                                             | _    | ns    |                                                                |  |  |

| IM26          | THD:DAT | Data Input           | 100 kHz mode | 0                                                                                                               |      | μs    | _                                                              |  |  |

|               |         | Hold Time            | 400 kHz mode | 0                                                                                                               | 0.9  | μs    |                                                                |  |  |

| IM30          | Tsu:sta | Start Condition      | 100 kHz mode | Трв * (BRG + 2)                                                                                                 |      | μs    | Only relevant for                                              |  |  |

|               |         | Setup Time           | 400 kHz mode | ТРВ * (BRG + 2)                                                                                                 | I    | μs    | Repeated Start condition                                       |  |  |

| IM31          | THD:STA | Start Condition      | 100 kHz mode | Трв * (BRG + 2)                                                                                                 | 1    | μs    | After this period, the                                         |  |  |

|               |         | Hold Time            | 400 kHz mode | ТРВ * (BRG + 2)                                                                                                 | I    | μs    | first clock pulse is generated                                 |  |  |

| IM33          | Tsu:sto | Stop Condition       | 100 kHz mode | Трв * (BRG + 2)                                                                                                 |      | μs    | _                                                              |  |  |

|               |         | Setup Time           | 400 kHz mode | Трв * (BRG + 2)                                                                                                 | _    | μs    |                                                                |  |  |

| IM34          | THD:STO | Stop Condition       | 100 kHz mode | Трв * (BRG + 2)                                                                                                 | _    | ns    | _                                                              |  |  |

|               |         | Hold Time            | 400 kHz mode | Трв * (BRG + 2)                                                                                                 |      | ns    |                                                                |  |  |

| IM40          | TAA:SCL | Output Valid         | 100 kHz mode | _                                                                                                               | 3500 | ns    | _                                                              |  |  |

|               |         | from Clock           | 400 kHz mode | _                                                                                                               | 1000 | ns    |                                                                |  |  |

| IM45          | TBF:SDA | Bus Free Time        | 100 kHz mode | 4.7                                                                                                             |      | μs    | The amount of time                                             |  |  |

|               |         |                      | 400 kHz mode | 1.3                                                                                                             | _    | μs    | the bus must be free<br>before a new<br>transmission can start |  |  |

| IM50          | Св      | Bus Capacitive L     | oading       | _                                                                                                               | 400  | pF    | _                                                              |  |  |

| IM51          | TPGD    | Pulse Gobbler De     | elay         | 52                                                                                                              | 312  | ns    | See Note 2                                                     |  |  |

**Note 1:** BRG is the value of the  $I^2C^{TM}$  Baud Rate Generator.

<sup>2:</sup> The typical value for this parameter is 104 ns.

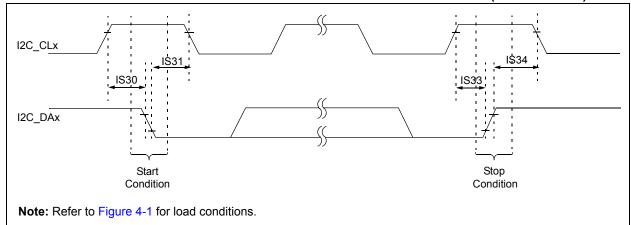

# FIGURE 4-6: I<sup>2</sup>Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

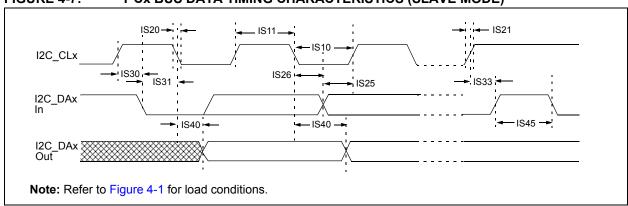

## FIGURE 4-7: I<sup>2</sup>Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 4-12: I<sup>2</sup>Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

|               | AC (    | CHARACTERISTIC       | es .         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C |      |       |                                                  |  |

|---------------|---------|----------------------|--------------|-----------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------------|--|

| Param.<br>No. | Symbol  | Characte             | eristics     | Min.                                                                                                            | Max. | Units | Conditions                                       |  |

| IS10          | TLO:SCL | Clock Low Time       | 100 kHz mode | 4.7                                                                                                             | _    | μs    | _                                                |  |

|               |         |                      | 400 kHz mode | 1.3                                                                                                             | _    | μs    | _                                                |  |

| IS11          | THI:SCL | Clock High Time      | 100 kHz mode | 4.0                                                                                                             | _    | μs    | _                                                |  |

|               |         |                      | 400 kHz mode | 0.6                                                                                                             | _    | μs    | _                                                |  |

| IS20          | TF:SCL  | I2C_DAx and          | 100 kHz mode | _                                                                                                               | 300  | ns    | CB is specified to be from                       |  |

|               |         | I2C_CLx<br>Fall Time | 400 kHz mode | 20 + 0.1 CB                                                                                                     | 300  | ns    | 10 to 400 pF                                     |  |

| IS21          | TR:SCL  | I2C_DAx and          | 100 kHz mode | _                                                                                                               | 1000 | ns    | CB is specified to be from                       |  |

|               |         | I2C_CLx<br>Rise Time | 400 kHz mode | 20 + 0.1 CB                                                                                                     | 300  | ns    | 10 to 400 pF                                     |  |

| IS25          | TSU:DAT | Data Input           | 100 kHz mode | 250                                                                                                             | _    | ns    | _                                                |  |

|               |         | Setup Time           | 400 kHz mode | 100                                                                                                             | _    | ns    |                                                  |  |

| IS26          | THD:DAT | Data Input           | 100 kHz mode | 0                                                                                                               | _    | ns    | _                                                |  |

|               |         | Hold Time            | 400 kHz mode | 0                                                                                                               | 0.9  | μs    |                                                  |  |

| IS30          | Tsu:sta | Start Condition      | 100 kHz mode | 4700                                                                                                            |      | ns    | Only relevant for Repeated                       |  |

|               |         | Setup Time           | 400 kHz mode | 600                                                                                                             | _    | ns    | Start condition                                  |  |

| IS31          | THD:STA | Start Condition      | 100 kHz mode | 4000                                                                                                            |      | ns    | After this period, the first                     |  |

|               |         | Hold Time            | 400 kHz mode | 600                                                                                                             | _    | ns    | clock pulse is generated                         |  |

| IS33          | Tsu:sto | Stop Condition       | 100 kHz mode | 4000                                                                                                            | —    | ns    | _                                                |  |

|               |         | Setup Time           | 400 kHz mode | 600                                                                                                             |      | ns    |                                                  |  |

| IS34          | THD:STO | Stop Condition       | 100 kHz mode | 4000                                                                                                            |      | ns    | _                                                |  |

|               |         | Hold Time            | 400 kHz mode | 600                                                                                                             |      | ns    |                                                  |  |

| IS40          | TAA:SCL | Output Valid from    | 100 kHz mode | 0                                                                                                               | 3500 | ns    | _                                                |  |

|               |         | Clock                | 400 kHz mode | 0                                                                                                               | 1000 | ns    |                                                  |  |

| IS45          | TBF:SDA | Bus Free Time        | 100 kHz mode | 4.7                                                                                                             | _    | μs    | The amount of time the bus                       |  |

|               |         |                      | 400 kHz mode | 1.3                                                                                                             | _    | μs    | must be free before a new transmission can start |  |

| IS50          | Св      | Bus Capacitive Lo    | ading        | _                                                                                                               | 400  | pF    | _                                                |  |

## **APPENDIX A: REVISION HISTORY**

#### TABLE A-1: REVISION HISTORY

| Revision               | Section/Figure/Entry | Correction |

|------------------------|----------------------|------------|

| DS00001885A (01-30-15) | Document Release     |            |

# SSC7150

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at <a href="www.microchip.com">www.microchip.com</a>. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO. <sup>(1)</sup> Device Series | - XXX <sup>(2)</sup> - XXX - [X] <sup>(3)</sup> Package Sensor Tape and Reel Fusion Option Firmware | Example:  SSC7150-ML-AB0 = 28-QFN, Bosch 9-axis sensor fusion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                               | SSC7150 <sup>(1)</sup>                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Package:                              | ML = 28 pin QFN <sup>(2)</sup>                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Sensor Fusion Firmware:               | AB0 = Bosch 9-axis Sensor Fusion                                                                    | Note 1: These products meet the halogen maximum concentration values per IEC61249-2-21.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Tape and Reel<br>Option:              | Blank = Tray packaging TR = Tape and Reel (3)                                                       | Note 2: All package options are RoHS compliant. For RoHS compliance and environmental information, please visit <a href="http://www.micro-chip.com/pagehandler/en-us/aboutus/ehs.html">http://www.micro-chip.com/pagehandler/en-us/aboutus/ehs.html</a> Note 3: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option. |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELoQ, Iogo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 9781632770073

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX

Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300

Fax: 86-27-5980-5118 **China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870

Fax: 65-6334-8850 Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828

Fax: 45-4450-2828

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf** Tel: 49-2129-3766400

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340

**Poland - Warsaw** Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15