# SM802140

ClockWorks<sup>™</sup> 644.53125MHz LVDS Ultra-Low Jitter, Frequency Synthesizer

#### **General Description**

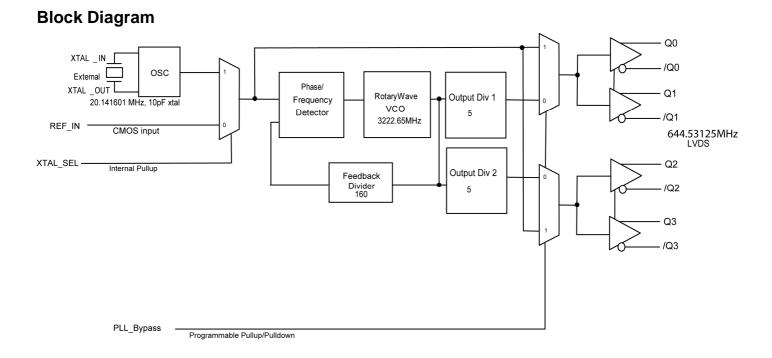

The SM802140 is a member of the ClockWorks<sup>™</sup> family of devices from Micrel and provides an extremely low-noise timing solution for clock signals. It is based upon a unique patented RotaryWave<sup>®</sup> architecture that provides very low phase noise.

The device operates from a 3.3V or 2.5V power supply and synthesizes four Differential LVDS clocks at 644.53125 MHz

The SM802140 accepts a 20.141601MHz crystal input.

Data sheets and support documentation can be found on Micrel's web site at: <u>www.micrel.com</u>.

#### **Features**

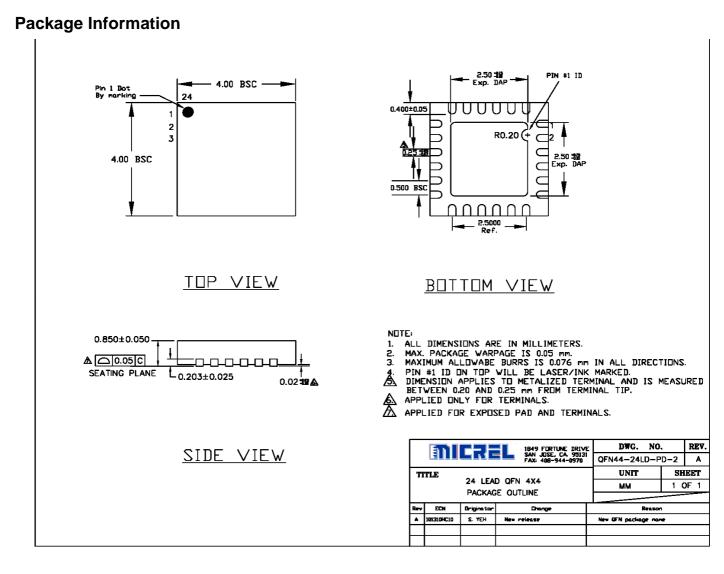

Generates four LVDS clocks output at 644.53125MHz 2.5V or 3.3V operating range Typical phase jitter @ 644MHz

(1.875MHz to 20MHz): 114 fs (typical) at 3.3V Industrial temperature range Green, RoHS, and PFOS compliant Available in 24-pin 4mm  $\times$  4mm QFN package

#### **Applications**

40GbE Serial PMD clock FPGA Transceiver clock

ClockWorks is a trademark of Micrel, Inc RotaryWave is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

November 2011

## **Ordering Information**

| Part Number   | Marking | Shipping      | Temperature Range | Package    |

|---------------|---------|---------------|-------------------|------------|

| SM802140UMG   | 802140  | Tube          | -40°C to +85°C    | 24-Pin QFN |

| SM802140UMGTR | 802140  | Tape and Reel | –40°C to +85°C    | 24-Pin QFN |

Note:

1. Devices are Green, RoHS, and PFOS compliant.

## **Pin Configuration**

# **Pin Description**

| Pin Number    | Pin Name   | Pin Type  | Pin Level                                                                       | Pin Function                                                                 |

|---------------|------------|-----------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 3, 4          | /Q3, Q3    |           |                                                                                 |                                                                              |

| 16, 17        | /Q0, Q0    |           |                                                                                 |                                                                              |

| 20, 21        | /Q1, Q1    | O, (DIFF) | LVDS Differential Clock Outputs at 644.                                         | Differential Clock Outputs at 644.53125MHz                                   |

| 23, 24        | /Q2, Q2    |           |                                                                                 |                                                                              |

|               |            |           |                                                                                 |                                                                              |

| 1             | VDDO2      | PWR       |                                                                                 | Power Supply for Outputs Q2 and Q3                                           |

| 2             | VSSO2      | PWR       |                                                                                 | Power Supply Ground for Outputs Q2 and Q3                                    |

|               |            |           |                                                                                 | Bypasses the PLL and Switches the REF_IN or<br>XTAL Frequency to all Outputs |

| 5             | PLL_BYPASS | I, (SE)   | LVCMOS                                                                          | 1 = Bypass PLL, output is XTAL or REF_IN                                     |

|               |            |           |                                                                                 | $0 = PLL Mode, 45K\Omega pull-down$                                          |

| 6             |            |           | LVCMOS                                                                          | Selects PLL Reference Input Mode                                             |

| σ             | XTAL_SEL   | I, (SE)   | $0 = \text{REF}_{\text{IN}}, 1 = \text{XTAL}, 45\text{K}\Omega \text{ pull-up}$ |                                                                              |

| 7, 12, 15, 19 | TEST       | I, (SE)   | LVCMOS                                                                          | Test Pins. Do Not Connect These Pins to Anything                             |

November 2011

| 8  | VDD                     | PWR     |         | Power Supply                                                                    |  |

|----|-------------------------|---------|---------|---------------------------------------------------------------------------------|--|

| 9  | REF_IN                  | I, (SE) | LVCMOS  | Reference Clock Input                                                           |  |

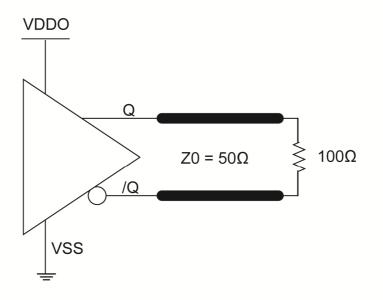

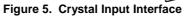

| 10 | XIN                     | I, (SE) | crystal | Crystal Input, no load caps needed.                                             |  |

| 10 |                         | I, (SE) | Crystar | See Fig. 6.                                                                     |  |

| 11 | хоит                    | O, (SE) | crystal | Crystal Output, no load caps needed.                                            |  |

|    | 2001                    | 0, (3E) | Crystar | See Fig. 6.                                                                     |  |

| 13 | VSS                     | I, (SE) |         | This Pin is not a Power Supply Ground, but MUST be Tied to VSS                  |  |

| 14 | VSS<br>(Exposed<br>Pad) | PWR     |         | Power Supply Ground. The exposed pad must be connected to the VSS ground plane. |  |

| 18 | VDDO1                   | PWR     |         | Power Supply for Outputs Q0 and Q1                                              |  |

| 22 | VSSO1                   | PWR     |         | Power Supply Ground for Outputs Q0 and Q1                                       |  |

## **Pin Description (Continued)**

## **Truth Table**

| PLL_BYPASS | XTAL_SEL | INPUT  | OUTPUT      |

|------------|----------|--------|-------------|

| 0          | -        | -      | PLL         |

| 1          | _        | -      | XTAL/REF_IN |

| _          | 0        | REF_IN | -           |

| _          | 1        | XTAL   | -           |

# **Application Information**

#### **Crystal Layout**

Keep the layers under the crystal as open as possible and do not place switching signals or noisy supplies under the crystal.

Crystal load capacitance is built inside the die so no external capacitance is needed. See the *Selecting a Quartz crystal for the Clockworks Flex I Family of Precision Synthesizers* application note for further details.

Contact Micrel's HBW applications group if you need assistance on selecting a suitable crystal for your application at <u>hbwhelp@micrel.com</u>

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>DD</sub> , V <sub>DDO1/2</sub> ) | +4.6V          |

|---------------------------------------------------------|----------------|

| Input Voltage (V <sub>IN</sub> )                        |                |

| Lead Temperature (soldering, 20sec.)                    |                |

| Case Temperature                                        | 115°C          |

| Storage Temperature (T <sub>s</sub> )                   | –65°C to +150° |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>DD</sub> , V <sub>DDO1/2</sub> ) | .+2.375V to +3.465V  |

|---------------------------------------------------------|----------------------|

| Ambient Temperature (T <sub>A</sub> )                   | –40°C to +85°C       |

| Junction Thermal Resistance <sup>(3)</sup>              |                      |

| QFN (θ <sub>JA</sub> )                                  |                      |

| Still-Air                                               | <mark>50</mark> °C/W |

| QFN (ψ <sub>JB</sub> )                                  |                      |

| Junction-to-Board                                       | <mark>32</mark> °C/W |

# DC Electrical Characteristics<sup>(4)</sup>

$V_{DD}$  =  $V_{DDO}$  = 3.3V  $\pm 5\%$  or 2.5V  $\pm 5\%$

$V_{\text{DD}}$  = 3.3V ±5%,  $V_{\text{DDO1/2}}$  = 3.3V ±5% or 2.5V ±5%

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .

| Symbol                             | Parameter                                                         | Condition                    | Min.  | Тур. | Max.  | Units |

|------------------------------------|-------------------------------------------------------------------|------------------------------|-------|------|-------|-------|

| V <sub>DD</sub> , V <sub>DDO</sub> | 2.5V Operating Voltage                                            |                              | 2.375 | 2.5  | 2.625 | V     |

| V <sub>DD</sub> , V <sub>DDO</sub> | 3.3V Operating Voltage                                            |                              | 3.135 | 3.3  | 3.465 | V     |

| I <sub>DD</sub>                    | Supply current V <sub>DD</sub> + V <sub>DDO</sub><br>Outputs open | 644MHz - 4 Diff LVDS outputs | -     | 204  | 240   | mA    |

## LVCMOS INPUT (XTAL\_SEL, PLL\_Bypass) DC Electrical Characteristics<sup>(4)</sup>

$V_{DD}$  = 3.3V ±5%, or 2.5V ±5%, T<sub>A</sub> = -40°C to +85°C.

| Symbol          | Parameter          | Condition                      | Min. | Тур. | Max.                  | Units |

|-----------------|--------------------|--------------------------------|------|------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |                                | 2    |      | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IN</sub> | Input Low Voltage  |                                | -0.3 |      | 0.8                   | V     |

| I <sub>IH</sub> | Input High Current | $V_{DD} = V_{IN} = 3.465V$     |      |      | 150                   | μΑ    |

| I <sub>IL</sub> | Input Low Current  | $V_{DD} = 3.465V, V_{IN} = 0V$ | -150 |      |                       | μA    |

## LVDS OUTPUT DC Electrical Characteristics<sup>(4)</sup>

$V_{DD} = V_{DDO1/2} = 3.3V \pm 5\%$  or 2.5V  $\pm 5\%$

$V_{DD}$  = 3.3V ±5%,  $V_{DDO1/2}$  = 3.3V ±5% or 2.5V ±5%

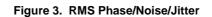

$T_A$  =  $-40^\circ C$  to  $+85^\circ C.~R_L$  =  $100\Omega$  across Q and /Q.

| Symbol          | Parameter                        | Condition | Min  | Тур  | Max  | Units |

|-----------------|----------------------------------|-----------|------|------|------|-------|

| V <sub>OD</sub> | Differential Output Voltage      | Figure 1  | 275  | 350  | 475  | mV    |

| $\Delta V_{OD}$ | V <sub>OD</sub> Magnitude Change |           |      |      | 40   | mV    |

| V <sub>OS</sub> | Offset Voltage                   |           | 1.15 | 1.25 | 1.50 | V     |

| $\Delta V_{OS}$ | V <sub>os</sub> Magnitude Change |           |      |      | 50   | mV    |

#### **Crystal Characteristics**

| Parameter                          | Condition                | Min. | Тур.                           | Max. | Units |  |  |

|------------------------------------|--------------------------|------|--------------------------------|------|-------|--|--|

| Mode of Oscillation                | 10pF Load <sup>(6)</sup> | F    | Fundamental, Parallel Resonant |      |       |  |  |

| Frequency                          |                          |      | 20.141601                      |      | MHz   |  |  |

| Equivalent Series Resistance (ESR) |                          |      |                                | 50   | Ω     |  |  |

| Shunt Capacitor, C0                |                          |      | 1                              | 5    | pF    |  |  |

| Correlation Drive Level            |                          |      | 10                             | 100  | uW    |  |  |

# AC Electrical Characteristics<sup>(4, 5, 6)</sup>

$V_{DD} = V_{DDO1/2} = 3.3V \pm 5\%$  or 2.5V  $\pm 5\%$

$V_{DD}$  = 3.3V ±5%,  $V_{DDO1/2}$  = 3.3V ±5% or 2.5V ±5%

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .  $R_L = 100\Omega$  across Q and /Q

| Symbol               | Parameter                  | Condition                                                                                       | Min. | Тур.              | Max. | Units |

|----------------------|----------------------------|-------------------------------------------------------------------------------------------------|------|-------------------|------|-------|

| FOUT                 | Output Frequency           |                                                                                                 |      | 644.53125         |      | MHz   |

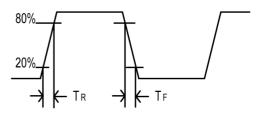

| $T_R/T_F$            | LVDS Output Rise/Fall Time | 20% - 80%                                                                                       | 80   | 175               | 350  | ps    |

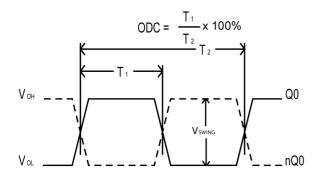

| ODC                  | Output Duty Cycle          |                                                                                                 | 48   | 50                | 52   | %     |

| TLOCK                | PLL Lock Time              |                                                                                                 |      |                   | 20   | ms    |

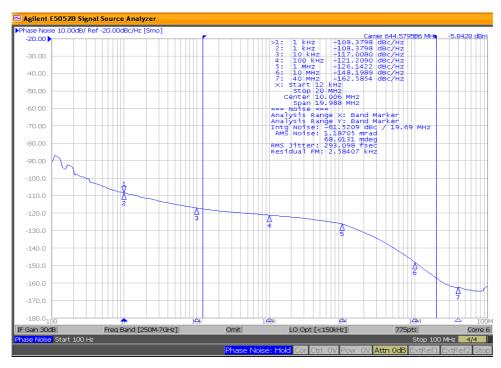

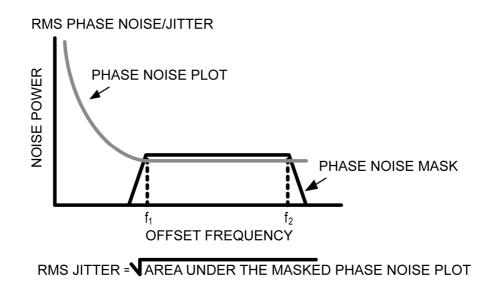

| T <sub>jit</sub> (∅) | RMS Phase Jitter           | Integration Range (1.875MHz – 20MHz)<br>Integration Range (12kHz – 20MHz)                       |      | 114<br>293        |      | fs    |

|                      | Spurious Noise Components  | 20.141MHz reference<br>Reference 2 <sup>nd</sup> harmonic<br>Reference 3 <sup>rd</sup> harmonic |      | -82<br>-78<br>-85 |      | dBc   |

#### Note:

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- 3. Package thermal resistance assumes exposed pad is soldered (or equivalent) to the devices most negative potential on the PCB.

- 4. The circuit is designed to meet the AC and DC specifications shown in the above table(s) after thermal equilibrium has been established.

- 5. All phase noise measurements were taken with an Agilent 5052B phase noise system.

- 6. See Application note, "Selecting a Quartz crystal for the Clockworks Flex I Family of Precision Synthesizers" for further details.

- 7. Measured using 20.141MHz crystal as the input reference source. If using an external reference input, use a low phase noise source. With an external reference, the phase noise will follow the input source phase noise up to about 1MHz.

5

#### **Phase Noise Plots**

Phase Noise Plot: 644.53125MHz, 12KHz - 20MHz 293 Fs

Phase Noise Plot: 644.53125MHz, 1.875MHz - 20MHz 114 Fs

Figure 1. Duty Cycle Timing

Figure 4. LVDS Output Load and Test Circuit

9

November 2011

24-Pin QFN

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

. . . . . . . . . . . . . . . .