Single-FET, Constant Power-Limit Hot Swap Controller

### **General Description**

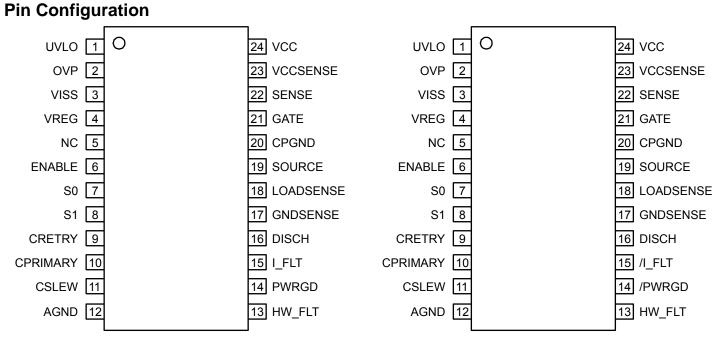

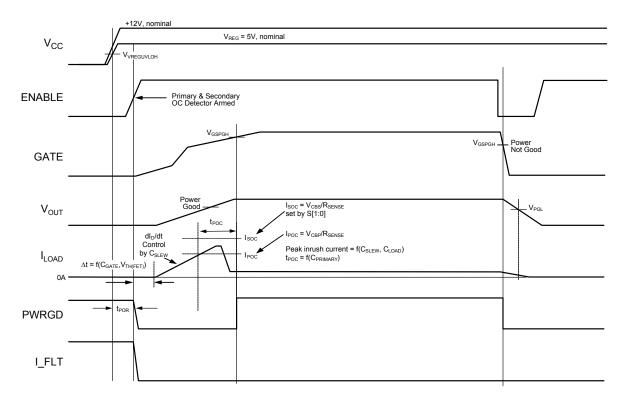

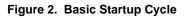

The MIC2310 is a single-channel, positive voltage, constant power-limit hot swap controller designed to provide for the safe insertion and removal of pc boards into fixed, rack, and pedestal mid- or back-planes using few external components. In addition, the MIC2310 employs a patent-pending, output load power-limiting technique where the current limit is inversely proportional to the output load voltage, such that the power product will not exceed the programmed power limit any longer than the externally programmed primary overcurrent period. The MIC2310 is ideally suited to address the power-limiting and timing requirements per the UL60950 specification for 240-VA applications. The MIC2310 incorporates high-side controller circuitry for an external N-channel MOSFET for which the MOSFET drain current rate of change is userprogrammable via an external capacitor. The MIC2310 dual-speed, dual-level overcurrent fault employs protection. The primary overcurrent detector response time is programmable via an external current sense resistor and the secondary overcurrent detector is 2-bit userprogrammable and exhibits a very fast (default) response to faults to ensure that the system power supplies are protected against catastrophic load current and shortcircuit faults. Additionally, an analog output (voltage) signal is provided that is proportional to the steady-state load current to allow monitoring of the system's power. A PWRGD signal is provided to indicate a valid output voltage that can be used to enable a DC-DC power module.

Data sheets and support documentation can be found on Micrel's web site at www.micrel.com.

#### Features

- Provides safe PCB insertion and removal from live +12V backplanes

- Patent-pending, adaptive circuit breaker threshold control

- Maintains constant power product at output

- Power-limit product (VA) is externally programmable for various power applications

- Dual-level, dual-speed overcurrent detection/protection

- Programmable primary detector response time

- Fast (< 1 μs) secondary detector response time to short circuit conditions

- User-programmable threshold settings via (2) digital inputs

- Steady-state load current monitoring

- Programmable inrush current slew-rate control

- Electronic circuit breaker functions after fault

- Latch off

- Automatic retry

- Programmable input undervoltage lockout and overvoltage protection

- Fault reporting:

- Open-drain 'Power-is-Good' output

- Open-drain 'I\_FLT' output signaling for all current faults

- Shorted R<sub>SENSE</sub> and Damaged MOSFET detection (D-G and D-S shorts)

### **Applications**

- UL60950, EN60950, and CSA1950 systems (240-VA)

- General Power-limiting Applications

- Base stations

- Enterprise servers

- High-reliability servers

- Enterprise switch networks

- +12V backplanes

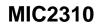

## **Typical Application**

### **Ordering Information**

| Part Number  | PWRGD State | I_FLT State | Fault Condition Status | Package      | Lead Finish |

|--------------|-------------|-------------|------------------------|--------------|-------------|

| MIC2310-1ZTS | Active-HIGH | Active-HIGH | Latched/Auto-retry     | 24-pin TSSOP | Pb-Free     |

| MIC2310-2ZTS | Active-LOW  | Active-LOW  | Latched/Auto-retry     | 24-pin TSSOP | Pb-Free     |

Note:

1. Other Voltage available. Contact Micrel for details.

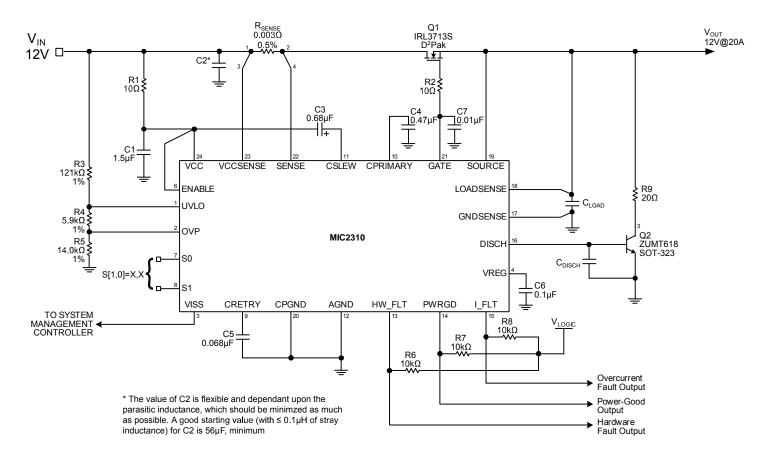

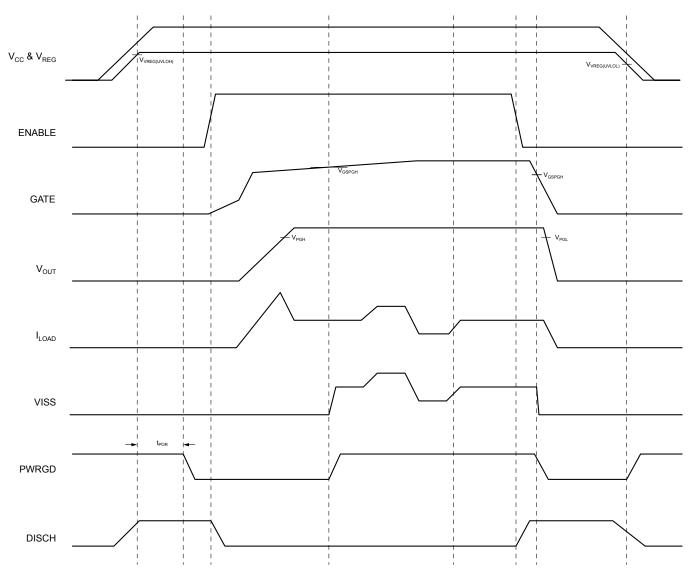

### 24-pin TSSOP (TS) MIC2310-1ZTS

24-pin TSSOP (TS) MIC2310-2ZTS

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | UVLO     | Undervoltage Lockout Input. When the applied voltage at the UVLO pin is higher than the controller's $V_{UVLOH}$ threshold voltage, the GATE drive circuits are active when ENABLE= HIGH. If the applied voltage at the UVLO pin falls below the controller's $V_{UVLOL}$ threshold voltage, the GATE drive circuits are disabled to turn the external MOSFET OFF. In addition, the DISCH circuit is activated to drive an optional, external discharge transistor alone (illustrated in the Typical Application circuit) or in combination with an SCR for a very fast discharge circuit configuration.                                                                                           |

| 2          | OVP      | Overvoltage Protection Input. When the applied voltage at the OVP pin is higher than the controller's $V_{OVPH}$ threshold voltage, the GATE drive circuit is disabled to turn the external MOSFET OFF. In addition, the DISCH circuit is activated to drive an optional, external discharge transistor alone (illustrated in the Typical Application circuit) or in combination with an SCR for a very fast discharge circuit configuration. Using an external resistor divider, the UVLO and the OVP pins form a window comparator that defines the supply voltage range within which the load may be safely powered.                                                                            |

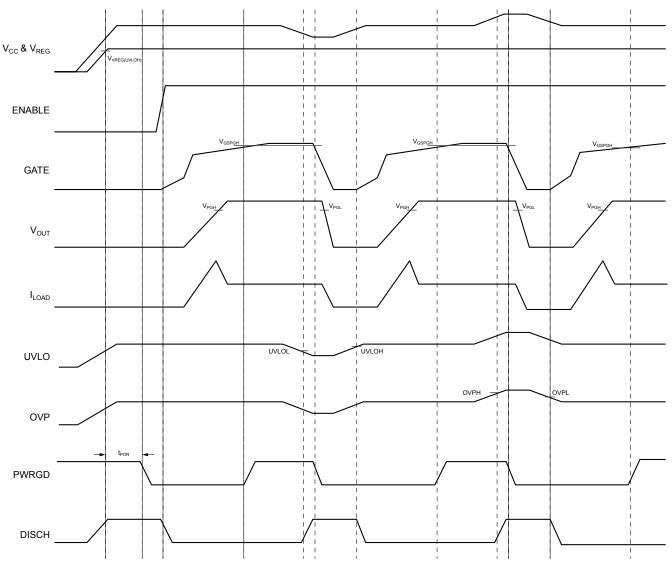

| 3          | VISS     | Steady-state Output Current Monitor. This output signal provides an analog voltage that is proportional to the steady-state load current. This signal is provided as an input to the system supervisor/processor to monitor the dc current/power level of the application circuit.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4          | VREG     | Internal +5V Regulator Bypass. Connect a 0.1- $\mu$ F, 16V ceramic capacitor from this pin to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5          | NC       | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

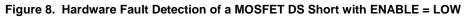

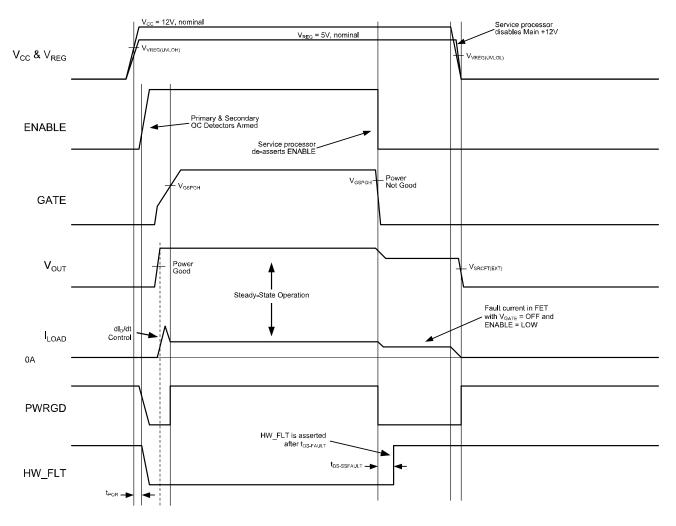

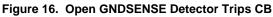

| 6          | ENABLE   | ENABLE Input. An active asserted-HIGH digital input that controls the operation of the MIC2310. Activated after the internal POR timer has terminated, a LOW-to-HIGH transition on this pin commences a start-up sequence if the applied V <sub>CC</sub> is above the V <sub>UVLOH</sub> and below the V <sub>OVPH</sub> threshold voltages. While ENABLE = LOW, the GATE pin is held to 0V and the DISCH output is activated. The ENABLE input can be used to reset the internal circuit breaker by applying a HIGH-to-LOW-to-HIGH transition as defined by t <sub>ENLPW</sub> following either a load current fault, an open LOADSENSE fault, an open GNDSENSE fault, or a shorted RSENSE fault. |

| 7          | S0       | Secondary OC Detector Current Threshold Digital Inputs – S1 is the MSB and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

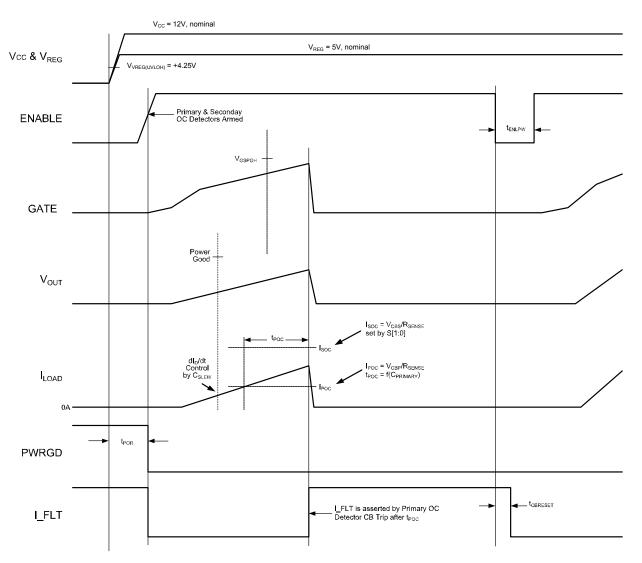

| 8          | S1       | S0 is the LSB. When used together, S[1:0] sets the overcurrent threshold for the secondary overcurrent detection circuit to one of four levels relative to the primary overcurrent detector nominal threshold. For example, S[1:0] = L, L sets the secondary overcurrent threshold at 1.3X; S[1:0] = L, H sets a 1.5X threshold; S[1:0] = H, L sets a 2X threshold, and S[1:0] = H, H sets a 1.75X threshold. If the S[1:0] pins are not connected or left NC, the default setting is S[1:0] = L, L or 1.3X. The permissible voltage range on these inputs is AGND $\leq$ S[1:0] $\leq$ V <sub>CC</sub> .                                                                                          |

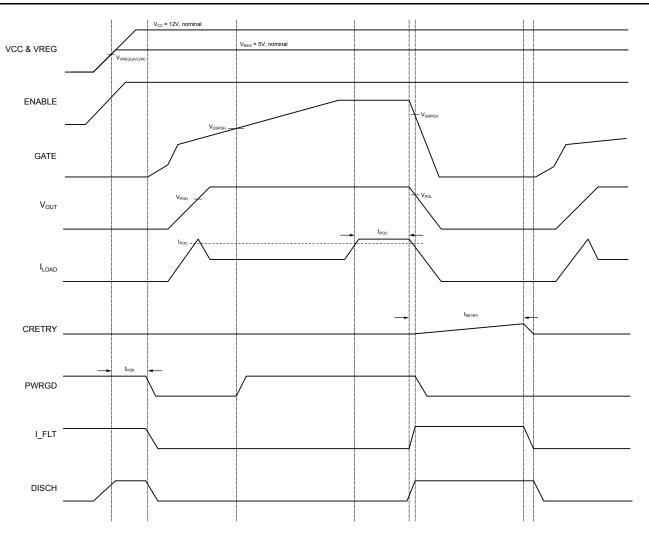

| 9          | CRETRY   | Auto-retry Timing Capacitor. A capacitor connected from the CRETRY pin to AGND configures the MIC2310 to re-start automatically with ENABLE = HIGH after the circuit breaker trips and latches off. It also sets the "cool-off" time delay before a new load current start-up sequence is initiated. To configure the MIC2310's circuit breaker to latch off after fault, connect this pin to AGND. The circuit breaker latches OFF and remains latched OFF unless the ENABLE input is toggled HIGH-to-LOW-to-HIGH as defined by $t_{ENLPW}$ or the V <sub>CC</sub> supply voltage is turned OFF then ON.                                                                                          |

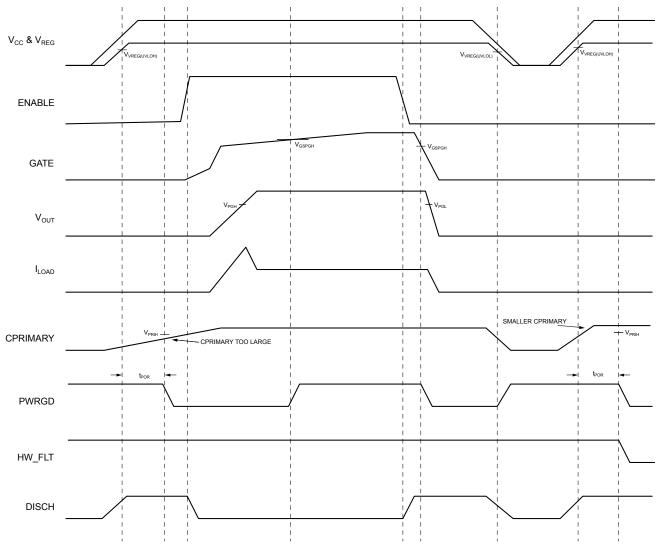

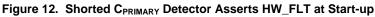

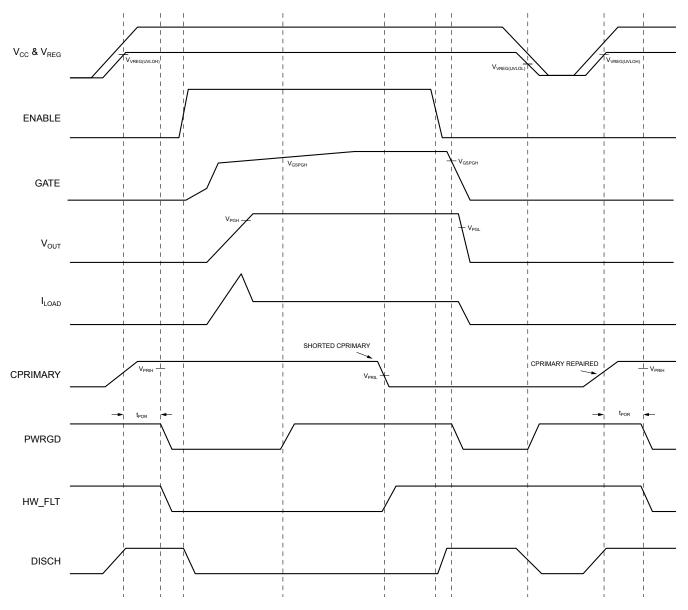

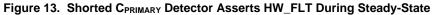

| 10         | CPRIMARY | Primary Overcurrent Detector Timing Capacitor. Connecting a capacitor from the CPRIMARY pin to AGND sets the response time of the controller's primary overcurrent detection circuit to GATE OFF in the event of an overcurrent condition. If the CPRIMARY pin is not connected, the primary overcurrent detection response time defaults to t <sub>POCSENSE</sub> , typically 250µs as specified in the Electrical Characteristics Table. The controller incorporates a patent-pending built-in test for a faulty CPRIMARY capacitor.                                                                                                                                                             |

## Pin Description (continued)

| Pin Number | Pin Name        | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | CSLEW           | Inrush Current Slew Rate Control Input. To adjust the inrush load current profile (controlled $dI_{DRAIN}/dt$ ), connect a capacitor from this pin to VCC. To adjust the MOSFET GATE voltage profile (controlled $dV_{GATE}/dt$ ), leave this pin OPEN (floating) and connect a capacitor from GATE to AGND. For additional information on the operation of this function, please refer to the Functional Description section.                                                                                                                                                                                                                                                                                              |

| 12         | AGND            | Analog Ground. Connect this pin to the system analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

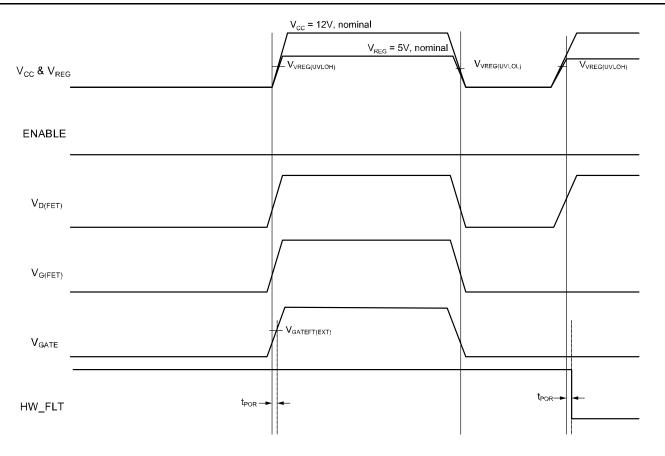

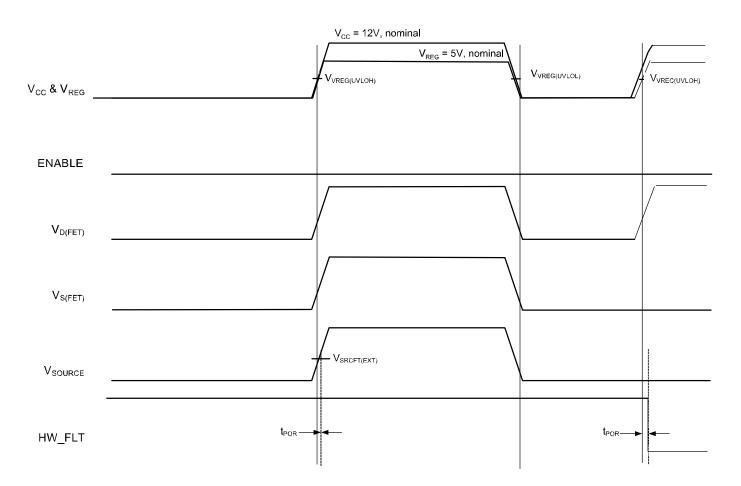

| 13         | HW_FLT          | External MOSFET Hardware Fault Digital Output. This output is an open-drain, active-HIGH signal that should be connected to a +3.3V logic supply by a 10k $\Omega$ resistor. This digital output is active after the internal POR timer has terminated and becomes asserted (HIGH) due to a fault under the following conditions: a) a shorted DG MOSFET with ENABLE = LOW; b) a shorted DS MOSFET with ENABLE = LOW; c) a shorted R <sub>SENSE</sub> ; d) a shorted DS MOSFET after steady-state operation with ENABLE = HIGH-to-LOW; or e) a shorted DG or DS while EN = HIGH and DISCH = HIGH; or f) a shorted C <sub>PRIMARY</sub> to AGND. The HW_FLT output is latched and is reset when VCC is brought low such that |

|            |                 | $V_{\text{REG}} < V_{\text{VREG}(UVLO)}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14         | PWRGD<br>/PWRGD | Power Good Digital Output. This output is an open-drain, active-HIGH (PWRGD) or active-LOW (/PWRGD) signal that should be connected to a +3.3-V logic supply by a 10k $\Omega$ resistor. This digital output is active after the internal POR timer has terminated and becomes asserted when the voltage between the LOADSENSE and the GNDSENSE pins is higher than the controller's V <sub>PGH</sub> threshold voltage. It is de-asserted when the voltage between the LOADSENSE pins is less than the controller's V <sub>PGL</sub> threshold voltage.                                                                                                                                                                    |

| 15         | I_FLT<br>/I_FLT | Load Current Fault Digital Output. This output is an open-drain, active-HIGH (I_FLT) or active-LOW (/I_FLT) signal that should be connected to a +3.3V logic supply by a 10k $\Omega$ resistor. This digital output is active after the internal POR timer has terminated and becomes asserted whenever the primary or secondary overcurrent detection circuits cause the internal circuit breaker to latch OFF. The digital output remains asserted unless the ENABLE input is toggled HIGH-to-LOW-to-HIGH as defined by t <sub>ENLPW</sub> or the V <sub>CC</sub> supply voltage is turned OFF then ON or if the auto-retry mode is enabled.                                                                              |

| 16         | DISCH           | Discharge External Transistor Drive Output. When ENABLE = LOW or after a fault condition (either an overcurrent fault or hardware fault such as a shorted MOSFET) that causes either the primary and secondary overcurrent detectors to trip the internal circuit breaker, the DISCH circuit is activated to provide gate drive to optional, external transistors (and SCR, for very fast load discharge). These transistors serve as auxiliary gate pull-down or load voltage pull-down switches. A load voltage pull-down is illustrated in the Typical Application circuit.                                                                                                                                              |

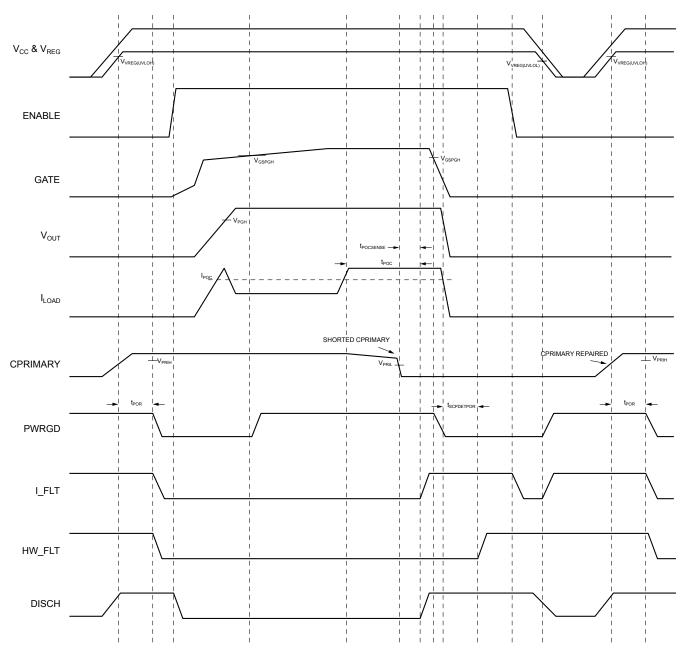

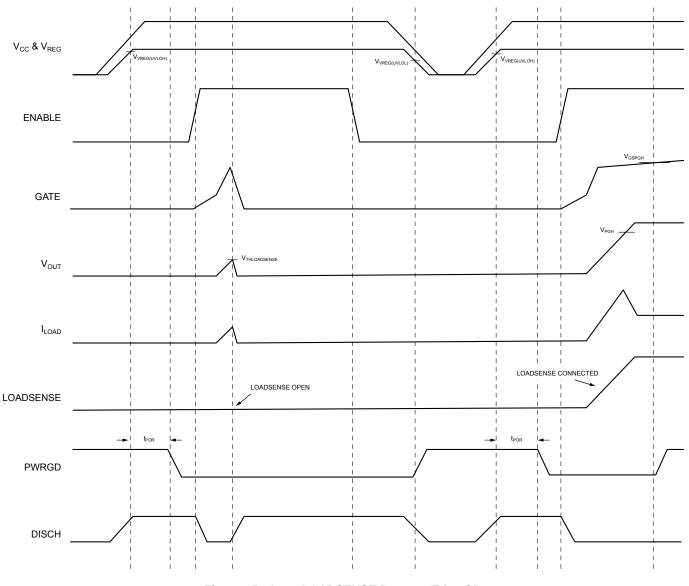

| 17         | GNDSENSE        | These input pins (when used together) sense the load voltage and provide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18         | LOADSENSE       | feedback to the controller's adaptive VA limit and Power-Good circuits. The voltage across these two pins also sets the controller's Power-Is-Good status output as defined by the specified $V_{PGH}$ or the $V_{PGL}$ threshold voltages. Internal circuit monitors are included if either or both LOADSENSE and GNDSENSE connections are severed or not connected to the load.                                                                                                                                                                                                                                                                                                                                           |

| 19         | SOURCE          | External Power MOSFET Source Pin Monitor. To protect external circuits downstream of the controller, internal monitor circuits are included to sense a shorted drain-source condition of the external power MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20         | CPGND           | Internal charge pump power ground. Connect this pin directly to the system's analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 21         | GATE            | External N-channel MOSFET GATE Drive Output. The GATE output signal uses an internal charge pump to charge the gate of an external N-channel MOSFET pass transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

## Pin Description (continued)

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22         | SENSE    | By connecting a very low value (m $\Omega$ ) current sense resistor between these two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23         | VCCSENSE | pins, the MIC2310's internal primary and secondary overcurrent detection circuits monitor the load current. The VCCSENSE pin is the positive (+) input terminal and the SENSE pin is the negative (-) input terminal of the overcurrent detection circuits. If the voltage across the sense resistor exceeds either the primary overcurrent threshold for a time ( $t_{POC}$ ) or the secondary primary overcurrent threshold for any duration, the MIC2310 electronic circuit breaker is tripped, the GATE is turned OFF, the DISCH circuit is activated, and the I_FLT digital output is asserted. The controller also incorporates a patent-pending built-in test for shorted current-sense resistors. Because of this built-in self test, the MIC2310's electronic circuit breaker cannot be disabled by connecting together the VCCSENSE and SENSE pins. |

| 24         | VCC      | Positive supply input to the MIC2310. The MIC2310 is specified to operate from $+10.8V \le V_{CC} \le +13.2V$ and the supply current with ENABLE = HIGH is less than 10mA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCC, VCCSENSE, SENSE, LOADSENSE, ENABLE,<br>CSLEW, S1, S0, SOURCE |  |

|-------------------------------------------------------------------|--|

| GATE–0.3V to +30V                                                 |  |

| UVLO, OVP, VISS, CRETRY, CPRIMARY, HW_FLT,                        |  |

| PWRGD, I FLT, DISCH, GNDSENSE –0.3V to +6V                        |  |

| Output Current                                                    |  |

| HW_FLT, PWRGD, I_FLT pins10mA                                     |  |

| ESD Rating (All pins)                                             |  |

| Human Body Model 2kV <sup>(3)</sup>                               |  |

| Machine Model                                                     |  |

| Lead Temperature (Soldering) Pb-free package                      |  |

| IR Reflow+260°C +0°C/-5°C                                         |  |

| Storage Temperature65°C to +150°C                                 |  |

|                                                                   |  |

## **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )            | +10.8V to +13.2V |

|----------------------------------------------|------------------|

| Ambient Temperature Range (T <sub>A</sub> )  | 0 °C to +70 °C   |

| Junction Temperature (T <sub>J</sub> )       | +125 °C          |

| Package Thermal Resistance ( $\theta_{JA}$ ) |                  |

| 24-pin TSSOP                                 | 83.8 °C/W        |

## DC Electrical Characteristics<sup>(4)</sup>

$V_{CC}$  = +12V,  $C_{REG}$  = 0.1µF,  $T_A$  = +25 °C unless otherwise noted. **Bold** indicates specification applies over the full operating temperature range of 0 °C to +70 °C. All voltages are measured with respect to AGND unless otherwise noted.

| Symbol                          | Parameter                                                                              | Condition                                                                                                                              | Min   | Тур   | Max   | Units |

|---------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>CC</sub>                 | Operating Supply Voltage<br>(Constant Output Power)                                    |                                                                                                                                        | 10.8  |       | 13.2  | V     |

| I <sub>CC</sub>                 | Supply Current                                                                         | ENABLE = LOW,HIGH                                                                                                                      |       |       | 10    | mA    |

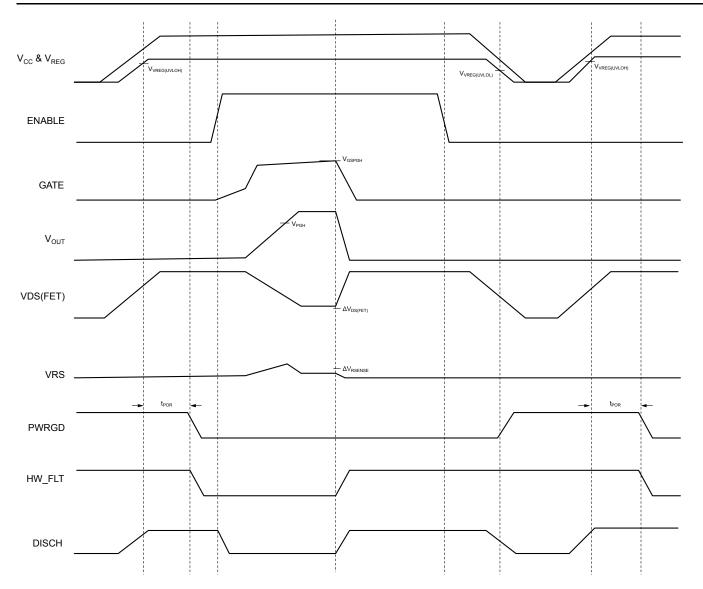

| $V_{\text{VREG}(\text{UVLOH})}$ | Internal VREG Undervoltage<br>Lockout High Threshold<br>Voltage                        | V <sub>REG</sub> Low-to-High Transition                                                                                                | 3.95  | 4.25  | 4.5   | V     |

| $V_{\text{VREG}(\text{UVLOL})}$ | Internal V <sub>REG</sub> Undervoltage<br>Lockout Low Threshold<br>Voltage             |                                                                                                                                        | 3.70  |       | 4.25  | V     |

| V <sub>UVLOH</sub>              | UVLO High Threshold<br>Voltage                                                         | Low-to-High Transition                                                                                                                 | 0.96  | 1.00  | 1.04  | V     |

| V <sub>UVLOL</sub>              | UVLO Low Threshold<br>Voltage                                                          | High-to-Low Transition                                                                                                                 | 0.91  | 0.941 | 0.97  | V     |

| I <sub>UVLO</sub>               | UVLO Pin Input Current                                                                 | UVLO = 6V                                                                                                                              |       |       | 5     | μA    |

| V <sub>OVPH</sub>               | OVP High Threshold Voltage                                                             | Low-to-High Transition                                                                                                                 | 1.35  | 1.407 | 1.45  | V     |

| V <sub>OVPL</sub>               | OVP Low Threshold Voltage                                                              | High-to-Low Transition                                                                                                                 | 1.295 | 1.339 | 1.395 | V     |

| I <sub>OVP</sub>                | OVP Pin Input Current                                                                  | OVP = 6V                                                                                                                               |       |       | 5     | μA    |

| V <sub>GSPGH</sub>              | "Power-is-Good" GATE-<br>SOURCE Threshold                                              | (V <sub>GATE</sub> – V <sub>SOURCE</sub> )                                                                                             | 4.25  | 5     |       | V     |

| V <sub>PGH</sub>                | "Power-is-Good" High<br>Threshold<br>(V <sub>LOADSENSE</sub> – V <sub>GNDSENSE</sub> ) | Low-to-High Transition,<br>$(V_{GATE} - V_{SOURCE}) \ge V_{GSPGH}$<br>Measured with respect to<br>GNDSENSE = AGND                      | 9.3   | 9.7   | 10.1  | V     |

| V <sub>PGL</sub>                | "Power-not-Good" Low<br>Threshold<br>(V <sub>LOADSENSE</sub> – V <sub>GNDSENSE</sub> ) | High-to-Low Transition,<br>(V <sub>GATE</sub> – V <sub>SOURCE</sub> ) ≥ V <sub>GSPGH</sub> Measured<br>with respect to GNDSENSE = AGND | 8.4   | 9     | 9.6   | V     |

| V <sub>REG</sub>                | V <sub>REG</sub> Output Voltage                                                        | R <sub>REG</sub> > 1 MΩ                                                                                                                | 4.5   | 5     | 5.5   | V     |

| Symbol              | Parameter                                            | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                              | Min   | Тур   | Max                                                                                                | Units |

|---------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|----------------------------------------------------------------------------------------------------|-------|

| V <sub>CBP</sub>    | Primary OC Circuit Breaker                           | (V <sub>LOADSENSE</sub> – V <sub>G</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <sub>NDSENSE</sub> ) = +12V                                                  | 54.7  | 57.2  | 59.7                                                                                               | mV    |

|                     | Threshold Voltage                                    | (V <sub>LOADSENSE</sub> – V <sub>GI</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <sub>NDSENSE</sub> ) = +10.8V                                                | 60.7  | 63.5  | 66.3                                                                                               | mV    |

|                     | $V_{VCCSENSE} - V_{SENSE}$                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <sub>NDSENSE</sub> ) = +13.2V                                                | 49.6  | 51.9  | 54.2                                                                                               | mV    |

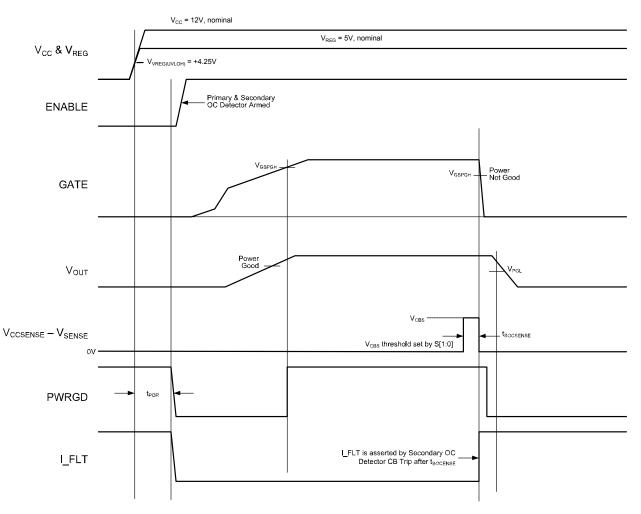

| V <sub>CBS</sub>    | Secondary OC SENSE                                   | Secondary OC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | S[1:0] = L, L                                                                | 64    | 75.5  | 87                                                                                                 | mV    |

|                     | Voltage                                              | Detector Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | S[1:0] = L, H                                                                | 75    | 87.5  | 99                                                                                                 | mV    |

|                     | $V_{VCCSENSE}$ - $V_{SENSE}$                         | Breaker Trips,<br>V <sub>LOADSENSE</sub> –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S[1:0] = H, L                                                                | 100   | 116.6 | 59.7   66.3   54.2   87   99   130   116   1   3   1.28   0.35   -1.65   -1.2   -1.2   -1.2   -1.5 | mV    |

|                     |                                                      | V <sub>GNDSENSE</sub> =<br>10.8V to 13.2V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S[1:0] = H,H                                                                 | 85    | 102   |                                                                                                    | mV    |

| IVCCSENSE           | VCCSENSE Pin Input<br>Current                        | $V_{VCCSENSE} = V_{CC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |       |       | 1                                                                                                  | μA    |

| I <sub>SENSE</sub>  | SENSE Pin Input Current                              | $V_{\text{SENSE}} = V_{\text{CC}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                              |       |       | 3                                                                                                  | μA    |

| V <sub>RETRYH</sub> | CRETRY Pin High<br>Threshold Voltage                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              | 1.21  | 1.25  | 1.28                                                                                               | V     |

| V <sub>RETRYL</sub> | CRETRY Pin Low Threshold<br>Voltage                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                              | 0.25  | 0.3   | 0.35                                                                                               | V     |

| IRETRYUP            | CRETRY Pin Charging<br>Current                       | TIMER ON,<br>V <sub>RETRY</sub> = 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                              | -4.25 | -3    | -1.65                                                                                              | μA    |

| RETRYDN             | CRETRY Pin Pull-down<br>Current                      | TIMER OFF,<br>V <sub>RETRY</sub> = 1.5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              |       | 3     |                                                                                                    | mA    |

| V <sub>PRIL</sub>   | CPRIMARY Pin Low<br>Threshold Voltage                | During OC responses of the second se | I;<br><sub>SE</sub> > V <sub>CBP</sub>                                       | -1.3  | -1.25 | -1.2                                                                                               | V     |

| V <sub>PRIL</sub>   | CPRIMARY Pin Low<br>Threshold Voltage                | During shorted<br>C <sub>PRIMARY</sub><br>detection;<br>Measured<br>relative to V <sub>REG</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ENABLE = HIGH;<br>$V_{CC(SENSE)} - V_{SENSE}$<br>$< V_{CBP}$<br>ENABLE = LOW | -1.3  | -1.25 | -1.2                                                                                               | V     |

| I <sub>PRI</sub>    | CPRIMARY Pin Charging<br>Current                     | During Primary C<br>$V_{CPRIMARY} = V_{REG}$<br>ENABLE = HIGH<br>$V_{CC(SENSE)} - V_{SEN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ;<br>I                                                                       | 2.4   | 3     | 3.6                                                                                                | μA    |

|                     |                                                      | During nominal a<br>$V_{PRIMARY} = V_{REG} - ENABLE = HIGH$<br>$V_{CC(SENSE)} - V_{SEN}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ł                                                                            | -4.5  | -3    | -1.5                                                                                               | mA    |

|                     |                                                      | During disable;<br>V <sub>CPRIMARY</sub> = V <sub>REG</sub><br>ENABLE = LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                              | -4.5  | -3    | -1.5                                                                                               | mA    |