# VSC8489-10 and VSC8489-13

# Dual Channel WAN/LAN/Backplane RXAUI/XAUI to SFP+/KR 10 GbE SerDes PHY with VeriTime<sup>™</sup>

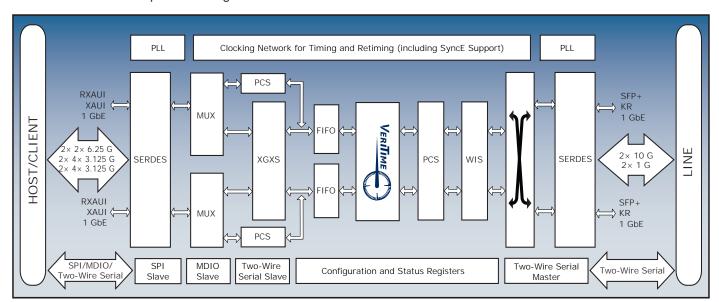

Vitesse's dual channel SerDes PHY provides fully IEEE 1588v2-compliant devices and hardware-based KR support for timing-critical applications, including all industry-standard protocol encapsulations.

VeriTime<sup>™</sup> is Vitesse's patent-pending distributed timing technology that delivers the industry's most accurate IEEE 1588v2 timing implementation. IEEE 1588v2 timing integrated in the PHY is the quickest, lowest cost method of implementing the timing accuracy that is critical to maintaining existing timing-critical capabilities during the migration from TDM to packet-based architectures.

The VSC8489-10 and VSC8489-13 devices support 1-step and 2-step PTP frames for ordinary clock, boundary clock, and transparent clock applications, along with complete Y.1731 OAM performance monitoring capabilities.

The devices meet the SFP+ SR/LR/ER/220MMF host requirements in accordance with the SFF-8431 specifications. They also compensate for optical impairments in SFP+ applications, along with degradations of the PCB.

#### **Highlights**

- IEEE 1588v2 compliant

- Failover switching and lane ordering

- Simultaneous LAN and WAN support

- RXAUI/XAUI support

- SFP+ I/O with KR support

- 1 GbE support

#### **Applications**

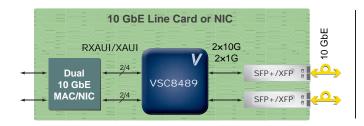

- Multiple-port RXAUI/XAUI to SFI/ SFP+ line cards or NICs

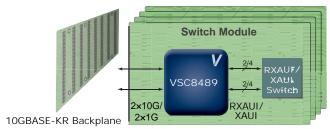

- 10GBASE-KR compliant backplane transceivers

- Carrier Ethernet networks requiring IEEE 1588v2 timing

- Secure data center to data center interconnects

- 10 GbE switch cards and router cards

The devices provide full KR support, including KR state machine, for autonegotiation and link optimization. The transmit path incorporates a multitap output driver to provide flexibility to meet the demanding 10GBASE-KR (IEEE 802.3ap) Tx output launch requirements.

Highly flexible clocking options enable Layer 1 support for Synchronous Ethernet. The devices use a single 156.25 MHz reference clock for LAN/WAN operation. They include a failover switching capability for protection routing, along with selectable lane ordering. A complete suite of BIST functionality includes line and client loopbacks along with pattern generation and error detection.

www.vitesse.com

Making next-generation networks a reality.

## VSC8489-10 and VSC8489-13

## **Range of Support**

- IEEE 1588v2/Y.1731 OAM precision timing support at 1.25 Gbps and 10.3 Gbps

- Compliant to IEEE 802.3ae and SFF-8431 electrical (SFI) specifications

- 9.95 Gbps WAN and 10.3 Gbps LAN operation, as well as 1.25 Gbps Ethernet support

- Supports all standard SFP+ applications

- Support for 10GBASE-KR (IEEE 802.3ap) for 10G backplanes, including 1.25 Gbps and 10.3 Gbps autonegotiation

- Adaptive equalization receiver and programmable, multitap transmitter pre-emphasis

- · Synchronous Ethernet support

- MDIO/SPI and two-wire serial slave management interfaces

## **Key Specifications**

- · 900 mW typical for each bidirectional channel

- 1.2 V and 1.0 V core power supplies (2.5 V TTL supply)

- 0 °C to 95 °C temperature range for VSC8489-10

- -40 °C to 110 °C temperature range for VSC8489-13

## **Flexibility**

- · Failover switching and lane ordering

- VScope input signal monitoring integrated circuit

- · Host-side and line-side loopbacks with BIST functions

- I/O programmability for lane swap, invert, amplitude, slew, pre-emphasis, and equalization

- Optional forward error correction (FEC)

- Synchronous Ethernet support with flexible clocking

- Passive copper cable support for minimum transmission cost

- Pin-compatible with VSC8489, VSC8490, and VSC8491

### **Related Vitesse Products**

Visit www.vitesse.com for information about these related Vitesse products:

- VSC8490-10

- VSC8491-10

- VSC8572

- VSC8574

- VSC8584

©2014 by Vitesse Semiconductor Corporation. All Rights Reserved. Products and specifications may change at any time without notice and Vitesse assumes no responsibility for the information provided herein. VPPD-03466. Revision 1.0.