DSC8103 DSC8123

# Programmable Low-Jitter Precision LVDS Oscillator

# **General Description**

The DSC8103 & DSC8123 series of high performance field-programmable oscillators utilizes a proven silicon MEMS technology to provide excellent jitter and stability over a supply wide range of voltages and temperatures. Using the TIMEFLASH programmer, the end user can easily program the oscillators' frequency in the field for immediate testing or use in advance prototype development or production.

DSC8103 has a standby feature allowing it to completely power-down when EN pin is pulled low; whereas for DSC8123, only the outputs are disabled when EN is low. Both oscillators are available in industry standard packages, including the small 3.2x2.5 mm<sup>2</sup>, and are "drop-in" replacement for standard 6-pin LVDS guartz oscillators.

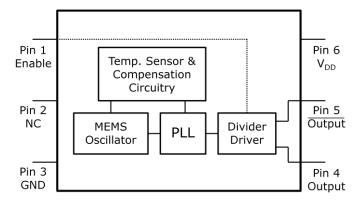

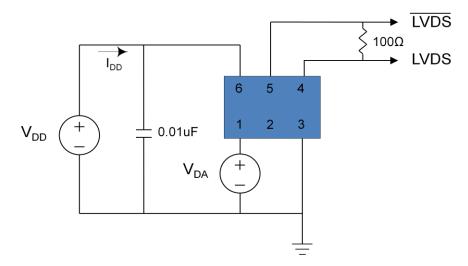

# **Block Diagram**

# **Output Enable Modes**

| EN Pin | DSC8103        | DSC8123          |

|--------|----------------|------------------|

| High   | Outputs Active | Outputs Active   |

| NC     | Outputs Active | Outputs Active   |

| Low    | Standby        | Outputs Disabled |

## **Features**

- Low RMS Phase Jitter: <1 ps (typ)

- High Stability: ±10, ±25, ±50 ppm

- Wide Temperature Range Industrial: -40° to 85° C Ext. commercial: -20° to 70° C

- High Supply Noise Rejection: -50 dBc

- Short Lead Time: 2 Weeks

- Wide Freq. Range: 10 to 460 MHz

- Small Industry Standard Footprints o 2.5x2.0, 3.2x2.5, 5.0x3.2, & 7.0x5.0 mm

- Excellent Shock & Vibration Immunity Qualified to MIL-STD-883

- High Reliability 20x better MTF than guartz oscillators

- Low Current Consumption

- Supply Range of 2.25 to 3.6 V

- Standby & Output Enable Function

- Lead Free & RoHS Compliant

- LVPECL & HCSL Versions Available

# **Applications**

- Storage Area Networks SATA, SAS, Fibre Channel

- Passive Optical Networks o EPON, 10G-EPON, GPON, 10G-PON

- Ethernet 1G, 10GBASE-T/KR/LR/SR, and FCoE

- HD/SD/SDI Video & Surveillance

- PCI Express: Gen 1 & Gen 2

- DisplayPort

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 1 |

#### **Absolute Maximum Ratings**

| Item           | Min  | Мах                  | Unit | Condition  |

|----------------|------|----------------------|------|------------|

| Supply Voltage | -0.3 | +4.0                 | V    |            |

| Input Voltage  | -0.3 | V <sub>DD</sub> +0.3 | V    |            |

| Junction Temp  | -    | +150                 | °C   |            |

| Storage Temp   | -55  | +150                 | °C   |            |

| Soldering Temp | -    | +260                 | °C   | 40sec max. |

| ESD            | -    |                      | V    |            |

| HBM            |      | 4000                 |      |            |

| MM             |      | 400                  |      |            |

| CDM            |      | 1500                 |      |            |

Note: 1000+ years of data retention on internal memory

#### **Specifications**

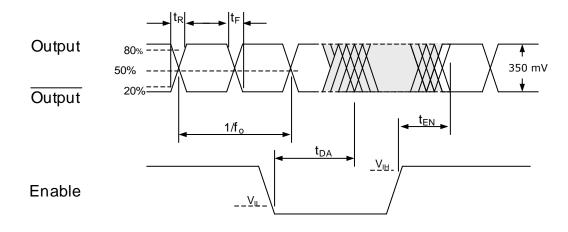

#### Parameter Condition Min. Unit Typ. Max. Supply Voltage<sup>1</sup> 2.25 3.6 V $V_{DD}$ EN pin low - outputs are disabled Supply Current DSC8103 0.095 mΑ $I_{DD}$ DSC8123 20 22 Includes frequency variations due $\pm 10$ **Frequency Stability** Δf to initial tolerance, temp. and ppm ±25 power supply voltage ±50 1 year @25°C Aging Δf ±5 ppm Startup Time<sup>2</sup> T=25°C 5 t<sub>su</sub> ms Input Logic Levels Input logic high V $0.75 \times V_{DD}$ $V_{IH}$ Input logic low $0.25 x V_{DD}$ $V_{IL}$ Output Disable Time<sup>3</sup> 5 $t_{DA}$ ns DSC8103 5 ms **Output Enable Time** t<sub>EN</sub> 20 DSC8123 ns Enable Pull-Up Resistor<sup>4</sup> Pull-up resistor exist 40 kΩ **LVDS Outputs** Supply Current Output Enabled, $R_1 = 50\Omega$ 29 32 mΑ $I_{DD}$ Output offset Voltage $R=100\Omega$ Differential 1.125 1.4 V Vos Delta Offset Voltage 50 $\Delta V_{\text{OS}}$ mV Pk to Pk Output Swing $V_{PP}$ Single-Ended 350 mV Output Transition time<sup>3</sup> 20% to 80% Rise Time 200 ps t<sub>R</sub> $R_1 = 50\Omega, C_1 = 2pF$ Fall Time t<sub>F</sub> 10 460 Frequency $f_0$ Single Frequency MHz SYM 48 52 **Output Duty Cycle** Differential % Period Jitter $\mathbf{J}_{\mathsf{PER}}$ 2.5 ps<sub>RMS</sub> 0.28 200kHz to 20MHz @156.25MHz **Integrated Phase Noise** J<sub>PH</sub> 100kHz to 20MHz @156.25MHz 0.4 $\mathsf{ps}_{\mathsf{RMS}}$ 12kHz to 20MHz @156.25MHz 1.7 2

Notes: 1.

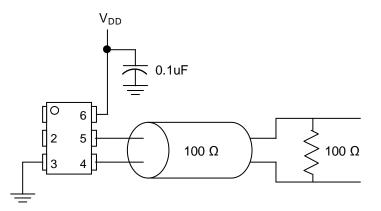

Pin 6  $V_{DD}$  should be filtered with 0.1uf capacitor.

$t_{su}$  is time to 100ppm of output frequency after V<sub>DD</sub> is applied and outputs are enabled. 2.

3. Output Waveform and Test Circuit figures below define the parameters.

Output is enabled if pad is floated or not connected. 4.

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 2 |

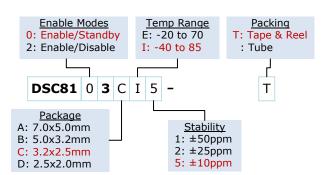

# **Ordering Code**

📰 discera

800

1000

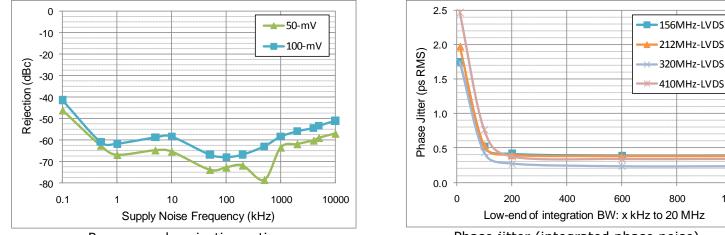

# Nominal Performance Parameters (Unless specified otherwise: T=25° C, V<sub>DD</sub>=3.3 V)

Power supply rejection ratio

Phase jitter (integrated phase noise)

#### **Output Waveform**

# **Typical Termination Scheme**

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 3 |

### **Test Circuit**

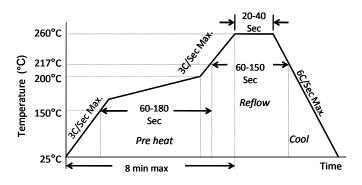

#### **Solder Reflow Profile**

| MSL 1 @ 260°C refer to JSTD-020C  |              |  |  |  |

|-----------------------------------|--------------|--|--|--|

| Ramp-Up Rate (200°C to Peak Temp) | 3°C/Sec Max. |  |  |  |

| Preheat Time 150°C to 200°C       | 60-180 Sec   |  |  |  |

| Time maintained above 217°C       | 60-150 Sec   |  |  |  |

| Peak Temperature                  | 255-260°C    |  |  |  |

| Time within 5°C of actual Peak    | 20-40 Sec    |  |  |  |

| Ramp-Down Rate                    | 6°C/Sec Max. |  |  |  |

| Time 25°C to Peak Temperature     | 8 min Max.   |  |  |  |

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 4 |

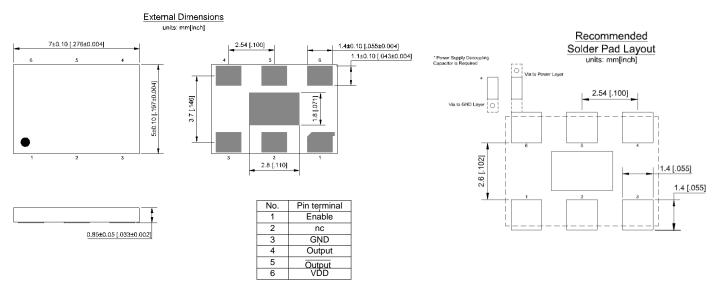

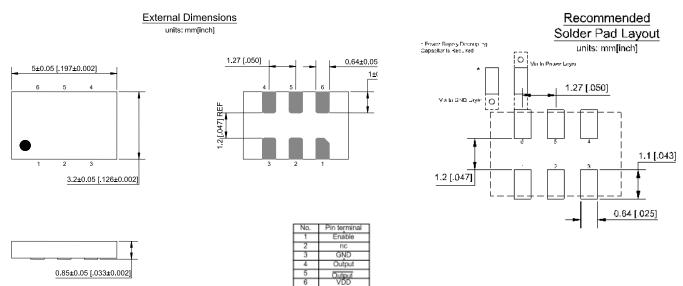

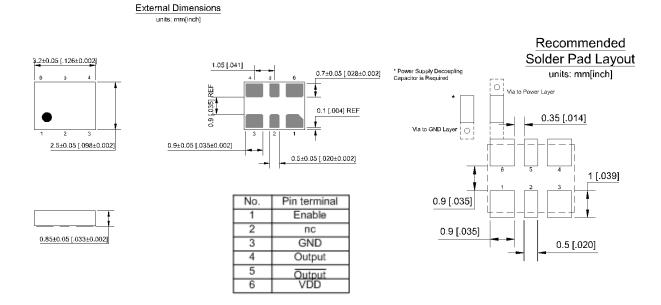

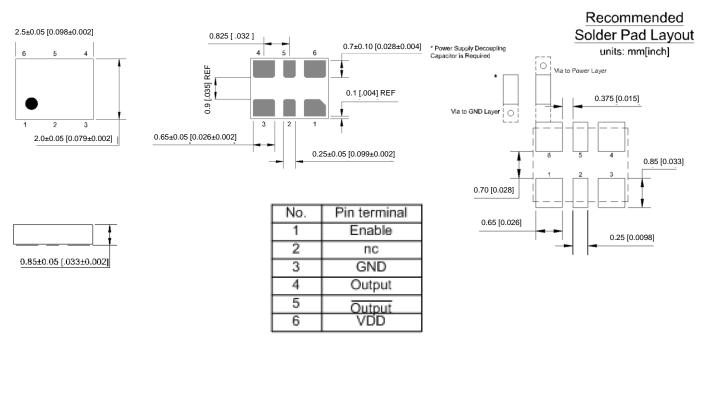

#### **Package Dimensions**

#### 7.0 x 5.0 mm Plastic Package

#### 5.0 x 3.2 mm Plastic Package

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 5 |

Programmable Low-Jitter Precision LVDS Oscillator

# **i**discera

#### 3.2 x 2.5 mm Plastic Package

#### 2.5 x 2.0 mm Plastic Package

| DISCERA, Inc. •          | 1961 Concourse Drive, San Jose, California 95131    | •   | USA             |

|--------------------------|-----------------------------------------------------|-----|-----------------|

| Phone: +1 (408) 432-8600 | • Fax: +1 (408) 432-8609 • Email: sales@discera.com | n • | www.discera.com |

All Rights Reserved. No part of this document may be copied or reproduced in any form without the prior written permission of Discera, Inc. Discera Inc. may update or make changes to the contents, products, programs or services described at any time without notice. This document neither states nor implies any kind of warranty, including, but not limited to implied warranties of merchantability or fitness for a particular use. Page 6 |