# **Regulating Pulse Width Modulator**

## Description

This monolithic integrated circuit contains all the control circuitry for a regulating power supply inverter or switching regulator. Included in a 16-pin dual-in-line package is the voltage reference, error amplifier, oscillator, pulse width modulator, pulse steering flip-flop, dual alternating output switches and current limiting and shut-down circuitry. This device can be used for switching regulators of either polarity, transformer coupled DC to DC converters, transformerless voltage doublers and polarity converters, as well as other power applications. The SG1524 is specified for operation over the full military ambient temperature range of -55°C to +125°C, the SG2524 for -25°C to +85°C, and the SG3524 is designed for commercial applications of 0°C to +70°C.

### **Features**

- 8V to 40V Operation

- 5V Reference

- Reference Line and Load Regulation of 0.4%

- 100Hz to 300kHz Oscillator Range

- Excellent External Sync Capability

- Dual 50mA Output Transistors

- Current Limit Circuitry

- Complete PWM Power Control Circuitry

- Single Ended or Push-Pull Outputs

- Total Supply Current less than 10mA

## **High Reliability Features**

Following are the high reliability features of SG1524:

- Available to MIL-STD-883, ¶ 1.2.1

- MIL-M38510/12601BEA SG1524J-JAN

- MSC-AMS Level "S" Processing Available

- Available to DSCC Standard Microcircuit Drawing (SMD)

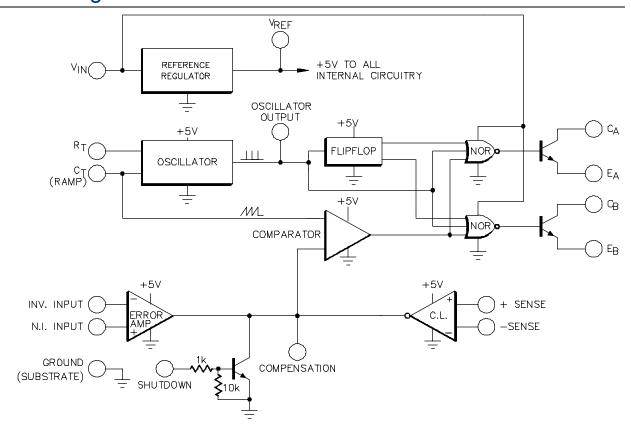

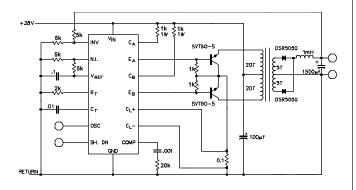

## **Block Diagram**

Figure 1 · Block Diagram

### Absolute Maximum Ratings (Note 1)

| Input Voltage (+V <sub>IN</sub> ) | 42V          |

|-----------------------------------|--------------|

| Collector Voltage                 | 40V          |

| Logic Inputs                      |              |

| Current Limit Sense Inputs        | 0.3V to 0.3V |

| Output Current (each transistor)  |              |

| Reference Load Current            | 50mA         |

Note 1: Values beyond which damage may occur.

| Oscillator Charging Current5mA                                                        |

|---------------------------------------------------------------------------------------|

| Operating Junction Temperature                                                        |

| Hermetic (J, L Packages) 150°C                                                        |

| Plastic (N, D Packages)150°C                                                          |

| Storage Temperature Range65°C to 150°C                                                |

| Lead Temperature (Soldering, 10 seconds)300°C                                         |

| Pb-free / RoHS Peak Package Solder Reflow Temp (40 sec. max. exposure) 260°C (+0, -5) |

### **Thermal Data**

Note A. Junction Temperature Calculation:  $T_J = T_A + (P_D \times \theta_{JA})$ . Note B. The above numbers for  $\theta_{JC}$  are maximums for the limiting thermal resistance of the package in a standard mounting configuration. The  $\theta_{JA}$  numbers are meant to be guidelines for the thermal performance of the device/pc-board system. All of the above assume no ambient airflow.

## Recommended Operating Conditions (Note 2)

| Input Voltage (+V <sub>IN</sub> )     | 8V to 40V    | Os |

|---------------------------------------|--------------|----|

| Collector Voltage                     |              | Os |

| Error Amp Common Mode Range           | 1.8V to 3.4V | Os |

| Current Limit Sense Common Mode Range | 0.3V to 0.3V | Op |

| Output Current (each transistor)      | 0 to 50mA    | ;  |

| Reference Load Current                | 0 to 20mA    | ,  |

| Oscillator Charging Current           | 30μA to 2mA  | ;  |

|                                       |              |    |

Note 2: Range over which the device is functional and parameter limits are guaranteed.

### **Electrical Characteristics**

(Unless otherwise specified, these specifications apply over the operating ambient temperatures for SG1524 with -55°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, SG2524 with -25°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, SG3524 with 0°C  $\leq$  T<sub>A</sub>  $\leq$  70°C, and +V<sub>IN</sub> = 20V. Low duty cycle pulse testing techniques are used which maintains junction and case temperatures equal to the ambient temperature.)

| Parameter                            | Test Conditions                  |      | SG1524/SG2524 |      |      | SG3524 |      |       |

|--------------------------------------|----------------------------------|------|---------------|------|------|--------|------|-------|

| Farameter                            |                                  |      | Тур.          | Max. | Min. | Тур.   | Max. | Units |

| Reference Section (Note 3)           |                                  |      |               |      |      |        |      |       |

| Output Voltage                       | T <sub>1</sub> = 25°C            | 4.80 | 5.00          | 5.20 | 4.60 | 5.00   | 5.40 | V     |

| Line Regulation                      | $V_{IN} = 8V \text{ to } 40V$    |      |               | 20   |      |        | 30   | mV    |

| Load Regulation                      | I <sub>1</sub> = 0 to 20mA       |      |               | 50   |      |        | 50   | mV    |

| Temperature Stability (Note 7) Total | Över Operating Temperature Range |      |               | 50   |      |        | 50   | mV    |

| Output Voltage Range (Note 7)        | Over Line, Load and Temperature  | 4.80 |               | 5.20 | 4.60 |        | 5.40 | V     |

| Short Circuit Current                | $V_{REF} = 0V$                   | 25   | 50            | 150  | 25   | 50     | 150  | mA    |

Note 3.  $I_1 = 0mA$

# Electrical Characteristics (Continued)

| Parameter                         | Test Conditions                                           |     | SG1524/SG2524 |          |      | 4 SG3524 |      |       |

|-----------------------------------|-----------------------------------------------------------|-----|---------------|----------|------|----------|------|-------|

| Farameter                         |                                                           |     | Тур.          | Max.     | Min. | Тур.     | Max. | Units |

| Oscillator Section (Note 4)       |                                                           |     |               |          |      |          |      |       |

| Initial Accuracy                  | T <sub>1</sub> = 25°C                                     | 36  | 40            | 44       | 36   | 40       | 44   | kHz   |

|                                   | $MIN \leq T_1 \leq MAX$                                   | 34  |               | 46       | 34   |          | 46   | kHz   |

| Voltage Stability                 | $V_{IN} = 8V^{3} to 40V$                                  |     | 0.1           | 1        |      | 0.1      | 1    | %     |

| Maximum Frequency                 | $R_{\tau}^{"} = 2k\Omega, C_{\tau} = 1nF$                 | 200 | 400           |          | 200  | 400      |      | kHz   |

| Sawtooth Peak Voltage             | $V_{IN} = 40V$                                            | 3   |               | 3.8      | 3    |          | 3.8  | V     |

| Sawtooth Valley Voltage           | $V_{IN}^{IN} = 8V$                                        | 0.6 | 1             | 1.2      | 0.6  | 1        | 1.2  | V     |

| Clock Amplitude                   | IIV                                                       | 3.2 |               |          | 3.2  |          |      | V     |

| Clock Pulse Width                 |                                                           | 0.3 |               | 1.5      | 0.3  |          | 1.5  | μs    |

| Error Amplifier Section (Note 5)  |                                                           | l   |               | <u> </u> |      |          |      |       |

| Input Offset Voltage              | $R_s \le 2k\Omega$                                        |     | 0.5           | 5        |      | 2        | 10   | mV    |

| Input Bias Current                | 5                                                         |     | 1             | 10       |      | 1        | 10   | μA    |

| Input Offset Current              |                                                           |     |               | 1        |      |          | 2    | μΑ    |

| DC Open Loop Gain                 | $R_{\perp} \ge 10M\Omega$ , $T_{\perp} = 25^{\circ}C$     | 72  |               |          | 60   |          |      | dB    |

| Output Low Level                  | $V_{PIN1}^L - V_{PIN2} \ge 150 \text{mV}$                 |     | 0.2           | 0.5      |      | 0.2      | 0.5  | V     |

| Output High Level                 | $V_{PIN 2}^{PIN 1} - V_{PIN 1}^{PIN 2} \ge 150 \text{mV}$ | 3.8 | 4.2           |          | 3.8  | 4.2      |      | V     |

| Common Mode Rejection             | $V_{CM} = 1.8V \text{ to } 3.4V$                          | 70  |               |          |      |          |      | dB    |

| Supply Voltage Rejection          | $V_{IN}^{CM} = 8V \text{ to } 40V$                        | 55  |               |          |      |          |      | dB    |

| Gain-Bandwidth Product (Note 7)   | T <sub>1</sub> = 25°C                                     | 1   | 2             |          | 1    | 2        |      | MHz   |

| P.W.M. Comparator (Note 4)        |                                                           |     |               |          |      |          | -    |       |

| Minimum Duty Cycle                | $V_{COMP} = 0.5V$                                         |     |               | 0        |      |          | 0    | %     |

| Maximum Duty Cycle                | $V_{COMP} = 3.6V$                                         | 45  | 49            |          | 45   | 49       |      | %     |

| Current Limit Amplifier Section ( |                                                           |     |               |          |      | l        |      |       |

| Sense Voltage                     | T <sub>1</sub> = 25°C                                     | 190 | 200           | 210      | 180  | 200      | 220  | mV    |

| Input Bias Current                | J                                                         |     |               | 200      |      |          | 200  | μΑ    |

| Shutdown Section                  |                                                           |     |               |          |      |          |      |       |

| Threshold Voltage                 | T <sub>1</sub> = 25°C                                     | 0.5 | 0.8           | 1.2      | 0.5  | 0.8      | 1.2  | V     |

|                                   | $MIN \leq T_{J} \leq MAX$                                 | 0.2 |               | 1.8      | 0.2  |          | 1.8  | V     |

| Output Section (each transistor)  |                                                           |     |               |          |      |          |      |       |

| Collector Leakage Current         | $V_{CE} = 40V$                                            |     |               | 50       |      |          | 50   | μΑ    |

| Collector Saturation Voltage      | I <sub>C</sub> = 50mA                                     |     |               | 2        |      |          | 2    | ·V    |

| Emitter Output Voltage            | $I_{\rm F}^{\rm C} = 50 \mathrm{mA}$                      | 17  |               |          | 17   |          |      | V     |

| Collector Voltage Rise Time       | $R_c = 2k\Omega$                                          |     |               | 0.4      |      |          | 0.4  | μs    |

| Collector Voltage Fall Time       | $R_c = 2k\Omega$                                          |     |               | 0.2      |      |          | 0.2  | μs    |

| Power Consumption                 |                                                           |     |               |          |      |          |      |       |

| Standby Current                   | V <sub>IN</sub> = 40V                                     |     | 7             | 10       |      | 7        | 10   | mA    |

Note 4.  $F_{OSC} = 40 \text{kHz} \ (R_T = 2.9 \text{k}\Omega, \ C_T = .01 \mu\text{F})$ Note 5.  $V_{CM} = 2.5 \text{V}$ Note 6.  $V_{CM} = 0 \text{V}$ Note 7. These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production.

## **Application Notes**

#### **OSCILLATOR**

The oscillator in the SG1524 uses an external resistor  $R_T$  to establish a constant charging current into an external capacitor  $C_T$ . While this uses more current than a series-connected RC, it provides a linear ramp voltage at  $C_T$  which is used as a time-dependent reference for the PWM comparator. The charging current is equal to  $3.6 \text{V/R}_T$ , and should be restricted to between  $30\mu\text{A}$  and 2mA. The equivalent range for  $R_T$  is 100k to 1.8k.

The range of values for C<sub>T</sub> also has limits, as the discharge time of  $C_T$  determines the pulse width of the oscillator output pulse. The pulse is used (among other things) as a blanking pulse to both outputs to insure that there is no possibility of having both outputs on simultaneously during transitions. This output deadtime relationship is shown in Figure 2. A pulse width below 0.35 microseconds may cause failure of the internal flip-flop to toggle. This restricts the minimum value of C<sub>T</sub> to 1000pF. (Note: Although the oscillator output is a convenient oscilloscope sync input, the probe capacitance will increase the pulse width and decrease the oscillator frequency slightly.) Obviously, the upper limit to the pulse width is determined by the modulation range required in the power supply at the chosen switching frequency. Practical values of C<sub>T</sub> fall between 1000pF and 0.1µF, although successful 120 Hz oscillators have been implemented with values up to 5µF and a series surge limit resistor of 100 ohms.

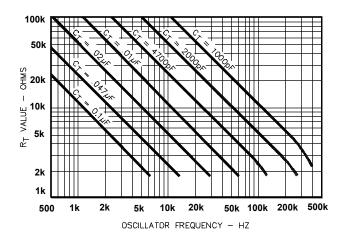

The oscillator frequency is approximately  $1/R_T \cdot C_T$ ; where R is in ohms, C is in microfarads, and the frequency is in Megahertz. For greater accuracy, the chart in Figure 3 may be used for a wide range of operating frequencies.

20 10 1 **QUTPUT DEADTIME** 2 1 0.5 0.2 .001 .002 .005 .01 .02 .05 0.1  $C_T$  VALUE  $-\mu F$

Figure 2 · Output Stage Deadtime vs. C<sub>T</sub>

Note that for buck regulator topologies, the two outputs can be wire-ORed for an effective 0-90% duty cycle range. With this connection, the output frequency is the same as the oscillator frequency. For push-pull applications, the outputs are used separately; the flip-flop limits the duty cycle range at each output to 0-45%, and the effective switching frequency at the transformer is 1/2 the oscillator frequency.

If it is desired to synchronize the SG1524 to an external clock, a positive pulse may be applied to the clock pin. The oscillator should be programmed with  $R_{\rm T}$  and  $C_{\rm T}$  values that cause it to free-run at 90% of the external sync frequency. A sync pulse with a maximum logic 0 of +0.3 volts and a minimum logic 1 of +2.4 volts applied to Pin 3 will lock the oscillator to the external source. The minimum sync pulsewidth should be 200 nanoseconds, and the maximum is determined by the required deadtime. The clock pin should never be driven more negative than -0.3 volts, nor more positive than +5.0 volts. The nominal resistance to ground is 3.2k at the clock pin,  $\pm 25\%$  over temperature.

If two or more SG1524's must be synchronized together, program one master unit with  $R_T$  and  $C_T$  for the desired frequency. Leave the  $R_T$  pins on the slaves open, connect the  $C_T$  pins to the  $C_T$  of the master, and connect the clock pins to the clock pin of the master. Since  $C_T$  is a high-impedance node, this sync technique works best when all devices are close together.

Figure 3 · Oscillator Frequency vs. R<sub>T</sub> and C<sub>T</sub>

### Application Notes (Continued)

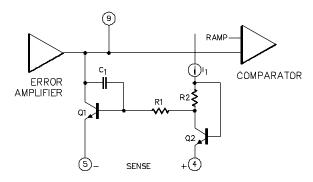

#### **CURRENT LIMITING**

The current limiting circuitry of the SG1524 is shown in Figure 4. By matching the base-emitter voltages of Q1 and Q2, and assuming a negligible voltage drop across R1:

C.L. Threshold =

$$V_{BE}(Q1) + I_1 \cdot R_2 - V_{BE}(Q2) = I_1 \cdot R_2$$

~ 200 mV

Although this circuit provides a relatively small threshold with a negligible temperature coefficient, there are some limitations to its use because of its simplicity.

The most important of these is the limited common-mode voltage range:  $\pm 0.3$  volts around ground. This requires sensing in the ground or return line of the power supply. Also precautions should be taken to not turn on the parasitic substrate diode of the integrated circuit, even under transient conditions. A Schottky clamp diode at Pin 5 may be required in some configurations to achieve this.

A second factor to consider is that the response time is relatively slow. The current limit amplifier is internally compensated by  $R_{_1},\,C_{_1},$  and Q1, resulting in a roll-off pole at approximately 300 Hz. A third factor to consider is the bias current of the C.L. sense pins. A constant current of approximately 150 $\mu$ A flows out of Pin 4, and a variable current with a range of 0-150 $\mu$ A flows out of Pin 5. As a result, the equivalent source impedance seen by the current sense pins should be less than 50 ohms to keep the threshold error less than 5%.

Since the gain of this circuit is relatively low (42 dB), there is a transition region as the current limit amplifier takes over pulse width control from the error amplifier. For testing purposes, threshold is defined as the input voltage required to get 25% duty cycle (+2 volts at the error amplifier output) with the error amplifier signaling maximum duty cycle.

APPLICATION NOTE: If the current limit function is not used on the SG1524, the common-mode voltage range restriction requires both current sense pins to be grounded.

Figure 4 · Current Limiting Circuitry of the SG1524

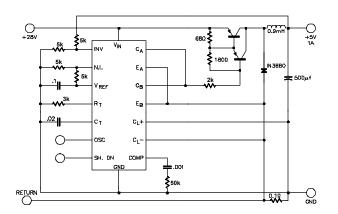

In this conventional single-ended regulator circuit, the two outputs of the SG1524 are connected in parallel for effective 0 - 90% duty-cycle modulation. The use of an output inductor requires and R-C phase compensation network for loop stability.

Push-pull outputs are used in this transformer-coupled DC-DC regulating converter. Note that the oscillator must be set at twice the desired output frequency as the SG1524's internal flip-flop divides the frequency by 2 as it switches the PWM signal from one output to the other. Current limiting is done here in the primary so that the pulse width will be reduced should transformer saturation occur.

# Connection Diagrams and Ordering Information (See Notes Below)

| Package                                               | Part No.                                                                     | Ambient<br>Temperature Range                                                                         | Connection Diagram                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-PIN CERAMIC DIP<br>J - PACKAGE                     | SG1524J-883B<br>SG1524J-JAN<br>SG1524J-DESC<br>SG1524J<br>SG2524J<br>SG3524J | -55°C to 125°C<br>-55°C to 125°C<br>-55°C to 125°C<br>-55°C to 125°C<br>-25°C to 85°C<br>0°C to 70°C | INV. INPUT                                                                                                                                                                                                                                                                                                                                                               |

| 16-PIN PLASTIC DIP<br>N - PACKAGE                     | SG2524N<br>SG3524N                                                           | -25°C to 85°C<br>0°C to 70°C                                                                         | N Package: RoHS / Pb-free Transition DC: 0503*. 100% Matte Tin Lead Finish                                                                                                                                                                                                                                                                                               |

| 16-PIN NARROW BODY<br>PLASTIC SOIC<br>D - PACKAGE     | SG2524D<br>SG3524D                                                           | -25°C to 85°C<br>0°C to 70°C                                                                         | INV. INPUT ☐ 1 16 ☐ V <sub>REF</sub> N.I. INPUT ☐ 2 15 ☐ +V <sub>N</sub> OSC. OUTPUT ☐ 3 14 ☐ E <sub>B</sub> +C.L. SENSE ☐ 4 13 ☐ C <sub>B</sub> -C.L. SENSE ☐ 5 12 ☐ C <sub>A</sub> R <sub>T</sub> ☐ 6 11 ☐ E <sub>A</sub> C <sub>T</sub> ☐ 7 10 ☐ SHUTDOWN  GROUND ☐ 8 9 ☐ COMPENSATION  RoHS / Pb-free transition DC:0440  Pb-free / RoHS 100% Matte Tin Lead Finish* |

| 20-PIN CERAMIC<br>LEADLESS CHIP CARRIER<br>L- PACKAGE | SG1524L-883B<br>SG1524L                                                      | -55°C to 125°C<br>-55°C to 125°C                                                                     | 1. N.C. 2. V <sub>REF</sub> 3. INV. INPUT 4 4. N.I. INPUT 5 5. OSC. OUTPUT 6 6. + C.L. SENSE 7 7 C.L. SENSE 7 8. R <sub>T</sub> 8 9. C <sub>T</sub> 10. GROUND 9 10 11 12 13 11. COMP 12. SHUTDOWN 11. COMP 12. SHUTDOWN 12. SHUTDOWN 15. 15. C <sub>A</sub> 16. N.C. 15. 17. C <sub>B</sub> 14. 18. E <sub>B</sub> 19. N.C. 20. +V <sub>IN</sub>                        |

### \*RoHS compliant

Note 1. Contact factory for JAN product availablity.

- 2. All packages are viewed from the top.

- 3. Hermetic Packages J & L use Pb37/Sn63 hot solder lead finish, contact factory for availability of RoHS versions.

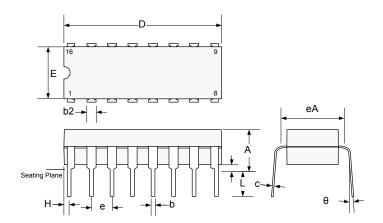

# Package Outline Dimensions

Controlling dimensions are in inches, metric equivalents are shown for general information.

| DIM | MILLIM | ETERS | INC       | HES   |  |

|-----|--------|-------|-----------|-------|--|

| DIN | MIN    | MAX   | MIN       | MAX   |  |

| Α   | -      | 5.08  | -         | 0.200 |  |

| b   | 0.38   | 0.51  | 0.015     | 0.020 |  |

| b2  | 1.04   | 1.65  | 0.045     | 0.065 |  |

| С   | 0.20   | 0.38  | 0.008     | 0.015 |  |

| D   | 19.30  | 19.94 | 0.760     | 0.785 |  |

| Е   | 5.59   | 7.11  | 0.220     | 0.280 |  |

| е   | 2.54   | BSC   | 0.100 BSC |       |  |

| eA  | 7.37   | 7.87  | 0.290     | 0.310 |  |

| Н   | 0.63   | 1.78  | 0.025     | 0.070 |  |

| L   | 3.18   | 5.08  | 0.125     | 0.200 |  |

| θ   | -      | 15°   | -         | 15°   |  |

| Q   | 0.51   | 1.02  | 0.020     | 0.040 |  |

#### Note:

Dimensions do not include protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

Figure 5 · J 16-Pin Ceramic Dip

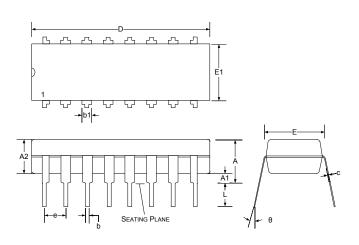

| DIM | MILLIM   | MILLIMETERS INCHES |       | HES    |

|-----|----------|--------------------|-------|--------|

| DIN | MIN      | MAX                | MIN   | MAX    |

| Α   | -        | 5.33               | -     | 0.210  |

| A1  | 0.38     | -                  | 0.015 | -      |

| A2  | 3.30     | Тур.               | 0.13  | 0 Тур. |

| b   | 0.36     | 0.56               | 0.014 | 0.022  |

| b1  | 1.14     | 1.78               | 0.045 | 0.070  |

| С   | 0.20     | 0.36               | 0.008 | 0.014  |

| D   | 18.67    | 19.69              | 0.735 | 0.775  |

| е   | 2.54 BSC |                    | 0.100 | ) BSC  |

| E   | 7.62     | 8.26               | 0.300 | 0.325  |

| E1  | 6.10     | 7.11               | 0.240 | 0.280  |

| L   | 2.92     | 0.381              | 0.115 | 0.150  |

| θ   | -        | 15°                | -     | 15°    |

#### Note:

Dimensions do not include protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

Figure 6 · N 16-Pin Plastic Dual Inline Package Dimensions

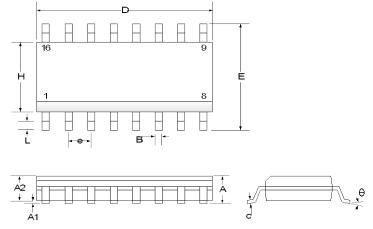

# Package Outline Dimensions(continued)

|     | MILL     | IMETERS | Inc   | CHES  |

|-----|----------|---------|-------|-------|

| DIM | MIN      | MAX     | MIN   | MAX   |

| Α   | 1.35     | 1.75    | 0.053 | 0.069 |

| A1  | 0.10     | 0.25    | 0.004 | 0.010 |

| A2  | 1.25     | 1.52    | 0.049 | 0.060 |

| b   | 0.33     | 0.51    | 0.013 | 0.020 |

| С   | 0.19     | 0.25    | 0.007 | 0.010 |

| D   | 9.78     | 10.01   | 0.385 | 0.394 |

| Е   | 5.79     | 6.20    | 0.228 | 0.244 |

| е   | 1.27 BSC |         | 0.050 | BSC   |

| Н   | 3.81     | 4.01    | 0.150 | 0.158 |

| L   | 0.40     | 1.27    | 0.016 | 0.050 |

| Θ   | 0        | 8       | 0     | 8     |

| *LC | -        | 0.10    | -     | 0.004 |

<sup>\*</sup>Lead Coplanarity

#### Note:

Dimensions do not include mold flash or protrusions; these shall not exceed 0.155mm (.006") on any side. Lead dimension shall not include solder coverage.

Figure 7 · D 16-Pin Plastic SOIC

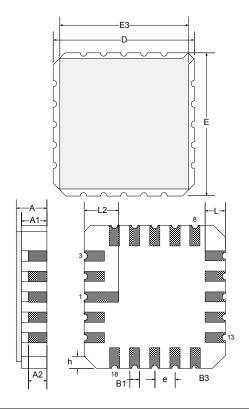

| DIM | MILLIME   | ETERS | INC       | HES   |  |

|-----|-----------|-------|-----------|-------|--|

| DIN | MIN       | MAX   | MIN       | MAX   |  |

| D/E | 8.64      | 9.14  | 0.340     | 0.360 |  |

| E3  | -         | 8.128 | -         | 0.320 |  |

| е   | 1.270     | BSC   | 0.050     | ) BSC |  |

| B1  | 0.635     | TYP   | 0.025 TYP |       |  |

| L   | 1.02      | 1.52  | 0.040     | 0.060 |  |

| Α   | 1.626     | 2.286 | 0.064     | 0.090 |  |

| h   | 1.016 TYP |       | 0.04      | 0 TYP |  |

| A1  | 1.372     | 1.68  | 0.054     | 0.066 |  |

| A2  | -         | 1.168 | -         | 0.046 |  |

| L2  | 1.91      | 2.41  | 0.075     | 0.95  |  |

| В3  | 0.20      | 3R    | 0.008R    |       |  |

#### Note:

All exposed metalized area shall be gold plated 60 microinch minimum thickness over nickel plated unless otherwise specified in purchase order.

Figure 8 · L 20-Pin Ceramic LCC Package Outline Dimensions

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdag: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at www.microsemi.com.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.