# In-System Programming (ISP) of Microsemi's Low Power Flash Devices Using FlashPro4/3/3X

#### **Table of Contents**

| Introduction                                    |

|-------------------------------------------------|

| JTAG 1532                                       |

| ISP Support in Flash-Based Devices              |

| Programming Voltage (VPUMP) and VJTAG           |

| Nonvolatile Memory (NVM) Programming Voltage    |

| IEEE 1532 (JTAG) Interface                      |

| Security                                        |

| Security in ARM-Enabled Low Power Flash Devices |

| Cortex-M1 and Cortex-M3 Device Security         |

| FlashROM and Programming Files                  |

| Programming Solution                            |

| ISP Programming Header Information              |

| Board-Level Considerations                      |

| Troubleshooting Signal Integrity                |

| Conclusion                                      |

| Related Documents                               |

| User's Guides                                   |

| List of Changes                                 |

#### Introduction

Microsemi's low power flash devices are all in-system programmable. This document describes the general requirements for programming a device and specific requirements for the FlashPro4/3/3X programmers<sup>1</sup>.

IGLOO,® ProASIC®3, SmartFusion,® and Fusion devices offer a low power, single-chip, live-at-power-up solution with the ASIC advantages of security and low unit cost through nonvolatile flash technology. Each device contains 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications such as Internet Protocol (IP) addressing, user system preference storage, device serialization, or subscription-based business models. IGLOO, ProASIC3, SmartFusion, and Fusion devices offer the best in-system programming (ISP) solution, FlashLock® security features, and AES-decryption-based ISP.

# **ISP Architecture**

Low power flash devices support ISP via JTAG and require a single VPUMP voltage of 3.3 V during programming. In addition, programming via a microcontroller in a target system is also supported.

<sup>1.</sup> FlashPro4 replaced FlashPro3/3X in 2010 and is backward compatible with FlashPro3/3X as long as there is no connection to pin 4 on the JTAG header on the board. On FlashPro3/3X, there is no connection to pin 4 on the JTAG header; however, pin 4 is used for programming mode (Prog\_Mode) on FlashPro4. When converting from FlashPro3/3X to FlashPro4, users should make sure that JTAG connectors on system boards do not have any connection to pin 4. FlashPro3X supports discrete TCK toggling that is needed to support non-JTAG compliant devices in the chain. This feature is included in FlashPro4.

Refer to the "Microprocessor Programming of Microsemi's Low Power Flash Devices" chapter of an appropriate FPGA fabric user's guide.

Family-specific support:

- ProASIC3, ProASIC3E, SmartFusion, and Fusion devices support ISP.

- ProASIC3L devices operate using a 1.2 V core voltage; however, programming can be done only at 1.5 V. Voltage switching is required in-system to switch from a 1.2 V core to 1.5 V core for programming.

- IGLOO and IGLOOe V5 devices can be programmed in-system when the device is using a 1.5 V supply voltage to the FPGA core.

- IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only) or 1.5 V. IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

- IGLOO V2 devices can operate at VCC 1.2 V or 1,5 V, but must be programmed at 1.5 V VCC. Voltage switching is required in-system to switch from 1.2 V supply (VCC, VCCI, VJTAG) to 1.5 V for programming.

IGLOO devices cannot be programmed in-system when the device is in Flash\*Freeze mode. The device should exit Flash\*Freeze mode and be in normal operation for programming to start. Programming operations in IGLOO devices can be achieved when the device is in normal operating mode and a 1.5 V core voltage is used.

#### **JTAG 1532**

IGLOO, ProASIC3, SmartFusion, and Fusion devices support the JTAG-based IEEE 1532 standard for ISP. To start JTAG operations, the IGLOO device must exit Flash\*Freeze mode and be in normal operation before starting to send JTAG commands to the device. As part of this support, when a device is in an unprogrammed state, all user I/O pins are disabled. This is achieved by keeping the global IO\_EN signal deactivated, which also has the effect of disabling the input buffers. The SAMPLE/PRELOAD instruction captures the status of pads in parallel and shifts them out as new data is shifted in for loading into the Boundary Scan Register (BSR). When the device is in an unprogrammed state, the OE and output BSR will be undefined; however, the input BSR will be defined as long as it is connected and being used. For JTAG timing information on setup, hold, and fall times, refer to the *FlashPro User's Guide*.

# **ISP Support in Flash-Based Devices**

The flash FPGAs listed in Table 1 support the ISP feature and the functions described in this document.

Table 1 • Flash-Based FPGAs Supporting ISP

| Series   | Family*       | Description                                                              |

|----------|---------------|--------------------------------------------------------------------------|

| IGLOO    | IGL00         | Ultra-low power 1.2 V to 1.5 V FPGAs with Flash*Freeze technology        |

|          | IGLO0e        | Higher density IGLOO FPGAs with six PLLs and additional I/O standards    |

|          | IGLOO nano    | The industry's lowest-power, smallest-size solution                      |

|          | IGLOO PLUS    | IGLOO FPGAs with enhanced I/O capabilities                               |

| ProASIC3 | ProASIC3      | Low power, high-performance 1.5 V FPGAs                                  |

|          | ProASIC3E     | Higher density ProASIC3 FPGAs with six PLLs and additional I/O standards |

|          | ProASIC3 nano | Lowest-cost solution with enhanced I/O capabilities                      |

|          | ProASIC3L     | ProASIC3 FPGAs supporting 1.2 V to 1.5 V with Flash*Freeze technology    |

|          | RT ProASIC3   | Radiation-tolerant RT3PE600L and RT3PE3000L                              |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

Table 1 • Flash-Based FPGAs Supporting ISP

|             | Military ProASIC3/EL | Military temperature A3PE600L, A3P1000, and A3PE3000L                                                                                                                                                             |

|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | Automotive ProASIC3  | ProASIC3 FPGAs qualified for automotive applications                                                                                                                                                              |

| SmartFusion | SmartFusion          | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable microcontroller subsystem (MSS) which includes programmable analog and an ARM® Cortex™-M3 hard processor and flash memory in a monolithic device |

| Fusion      | Fusion               | Mixed signal FPGA integrating ProASIC3 FPGA fabric, programmable analog block, support for ARM <sup>®</sup> Cortex <sup>™</sup> -M1 soft processors, and flash memory into a monolithic device                    |

| ProASIC     | ProASIC              | First generation ProASIC devices                                                                                                                                                                                  |

|             | ProASICPLUS          | Second generation ProASIC devices                                                                                                                                                                                 |

Note: \*The device names link to the appropriate datasheet, including product brief, DC and switching characteristics, and packaging information.

#### IGLOO Terminology

In documentation, the terms IGLOO series and IGLOO devices refer to all of the IGLOO devices as listed in Table 1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

#### ProASIC3 Terminology

In documentation, the terms ProASIC3 series and ProASIC3 devices refer to all of the ProASIC3 devices as listed in Table 1. Where the information applies to only one product line or limited devices, these exclusions will be explicitly stated.

To further understand the differences between the IGLOO and ProASIC3 devices, refer to the *Industry's Lowest Power FPGAs Portfolio*.

# Programming Voltage (VPUMP) and VJTAG

Low-power flash devices support on-chip charge pumps, and therefore require only a single 3.3 V programming voltage for the VPUMP pin during programming. When the device is not being programmed, the VPUMP pin can be left floating or can be tied (pulled up) to any voltage between 0 V and 3.6 V<sup>2</sup>. During programming, the target board or the FlashPro4/3/3X programmer can provide VPUMP. FlashPro4/3/3X is capable of supplying VPUMP to a single device. If more than one device is to be programmed using FlashPro4/3/3X on a given board, FlashPro4/3/3X should not be relied on to supply the VPUMP voltage. A FlashPro4/3/3X programmer is not capable of providing reliable VJTAG voltage. The board must supply VJTAG voltage to the device and the VJTAG pin of the programmer header must be connected to the device VJTAG pin. Microsemi recommends that VPUMP<sup>3</sup> and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail. Refer to the "Board-Level Considerations" section on page 11 for capacitor requirements.

Low power flash device I/Os support a bank-based, voltage-supply architecture that simultaneously supports multiple I/O voltage standards (Table 2). By isolating the JTAG power supply in a separate bank from the user I/Os, low power flash devices provide greater flexibility with supply selection and simplify power supply and printed circuit board (PCB) design. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Microsemi recommends that TCK be tied to GND through a 200 ohm to 1 Kohm resistor. This prevents a possible totempole current on the input buffer stage. For TDI, TMS, and TRST pins, the devices provide an internal nominal 10 Kohm pull-up resistor. During programming, all I/O pins, except for JTAG interface pins, are tristated and weakly pulled up to VCCI. This isolates the part and

<sup>2.</sup> During sleep mode in IGLOO devices connect VPUMP to GND.

VPUMP has to be quiet for successful programming. Therefore VPUMP must be separate and required capacitors must be installed close to the FPGA VPUMP pin.

prevents the signals from floating. The JTAG interface pins are driven by the FlashPro4/3/3X during programming, including the TRST pin, which is driven HIGH.

Table 2 • Power Supplies

| Power Supply | Programming Mode                                        | Current during<br>Programming |

|--------------|---------------------------------------------------------|-------------------------------|

| VCC          | 1.2 V / 1.5 V                                           | < 70 mA                       |

| VCCI         | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V (bank-selectable) | I/Os are weakly pulled up.    |

| VJTAG        | 1.2 V / 1.5 V / 1.8 V / 2.5 V / 3.3 V                   | < 20 mA                       |

| VPUMP        | 3.15 V to 3.45 V                                        | < 80 mA                       |

Note: All supply voltages should be at 1.5 V or higher, regardless of the setting during normal operation, except for IGLOO nano, where 1.2 V VCC and VJTAG programming is allowed.

# **Nonvolatile Memory (NVM) Programming Voltage**

SmartFusion and Fusion devices need stable VCCNVM/VCCENVM $^3$  (1.5 V power supply to the embedded nonvolatile memory blocks) and VCCOSC/VCCROSC $^4$  (3.3 V power supply to the integrated RC oscillator). The tolerance of VCCNVM/VCCENVM is  $\pm$  5% and VCCOSC/VCCROSC is  $\pm$  5%.

Unstable supply voltage on these pins can cause an NVM programming failure due to NVM page corruption. The NVM page can also be corrupted if the NVM reset pin has noise. This signal must be tied off properly.

Microsemi recommends installing the following capacitors<sup>5</sup> on the VCCNVM/VCCENVM and VCCOSC/VCCROSC pins:

- Add one bypass capacitor of 10 μF for each power supply plane followed by an array of decoupling capacitors of 0.1 μF.

- Add one 0.1 µF capacitor near each pin.

# IEEE 1532 (JTAG) Interface

The supported industry-standard IEEE 1532 programming interface builds on the IEEE 1149.1 (JTAG) standard. IEEE 1532 defines the standardized process and methodology for ISP. Both silicon and software issues are addressed in IEEE 1532 to create a simplified ISP environment. Any IEEE 1532 compliant programmer can be used to program low power flash devices. Device serialization is not supported when using the IEEE1532 standard. Refer to the standard for detailed information about IEEE 1532.

# **Security**

Unlike SRAM-based FPGAs that require loading at power-up from an external source such as a microcontroller or boot PROM, Microsemi nonvolatile devices are live at power-up, and there is no bitstream required to load the device when power is applied. The unique flash-based architecture prevents reverse engineering of the programmed code on the device, because the programmed data is stored in nonvolatile memory cells. Each nonvolatile memory cell is made up of small capacitors and any physical deconstruction of the device will disrupt stored electrical charges.

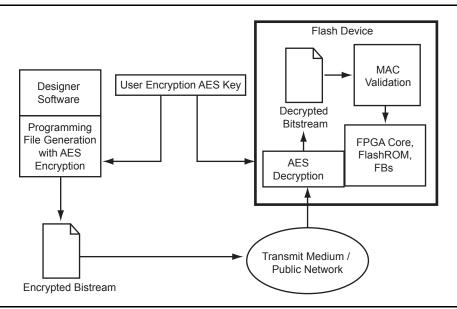

Each low power flash device has a built-in 128-bit Advanced Encryption Standard (AES) decryption core, except for the 30 k gate devices and smaller. Any FPGA core or FlashROM content loaded into the device can optionally be sent as encrypted bitstream and decrypted as it is loaded. This is particularly suitable for applications where device updates must be transmitted over an unsecured network such as

<sup>4.</sup> VCCROSC is for SmartFusion.

<sup>5.</sup> The capacitors cannot guarantee reliable operation of the device if the board layout is not done properly.

the Internet. The embedded AES decryption core can prevent sensitive data from being intercepted (Figure 1 on page 5). A single 128-bit AES Key (32 hex characters) is used to encrypt FPGA core programming data and/or FlashROM programming data in the Microsemi tools. The low power flash devices also decrypt with a single 128-bit AES Key. In addition, low power flash devices support a Message Authentication Code (MAC) for authentication of the encrypted bitstream on-chip. This allows the encrypted bitstream to be authenticated and prevents erroneous data from being programmed into the device. The FPGA core, FlashROM, and Flash Memory Blocks (FBs), in Fusion only, can be updated independently using a programming file that is AES-encrypted (cipher text) or uses plain text.

# Security in ARM-Enabled Low Power Flash Devices

There are slight differences between the regular flash device and the ARM-enabled flash devices, which have the M1 prefix.

The AES key is used by Microsemi and preprogrammed into the device to protect the ARM IP. As a result, the design will be encrypted along with the ARM IP, according to the details below.

#### Cortex-M1 and Cortex-M3 Device Security

Cortex-M1-enabled and Cortex-M3 devices are shipped with the following security features:

- FPGA array enabled for AES-encrypted programming and verification

- FlashROM enabled for AES-encrypted write and verify

- Embedded Flash Memory enabled for AES encrypted write

Figure 1 • AES-128 Security Features

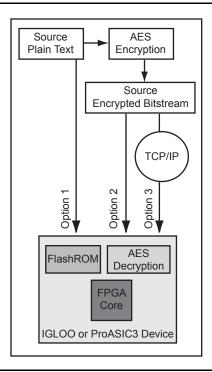

Figure 2 shows different applications for ISP programming.

- 1. In a trusted programming environment, you can program the device using the unencrypted (plaintext) programming file.

- You can program the AES Key in a trusted programming environment and finish the final programming in an untrusted environment using the AES-encrypted (cipher text) programming file

- 3. For the remote ISP updating/reprogramming, the AES Key stored in the device enables the encrypted programming bitstream to be transmitted through the untrusted network connection.

Microsemi low power flash devices also provide the unique Microsemi FlashLock feature, which protects the Pass Key and AES Key. Unless the original FlashLock Pass Key is used to unlock the device, security settings cannot be modified. Microsemi does not support read-back of FPGA core-programmed data; however, the FlashROM contents can selectively be read back (or disabled) via the JTAG port based on the security settings established by the Microsemi Designer software. Refer to the "Security in Low Power Flash Devices" section of the Fusion and Extended Temperature Fusion FPGA Fabric User's Guide for more information.

Figure 2 • Different ISP Use Models

# FlashROM and Programming Files

Each low power flash device has 1 kbit of on-chip, nonvolatile flash memory that can be accessed from the FPGA core. This nonvolatile FlashROM is arranged in eight pages of 128 bits (Figure 3). Each page can be programmed independently, with or without the 128-bit AES encryption. The FlashROM can only be programmed via the IEEE 1532 JTAG port and cannot be programmed from the FPGA core. In addition, during programming of the FlashROM, the FPGA core is powered down automatically by the on-chip programming control logic.

|          |   |    |    |    |    | Ву | /te Nu | umbe | r in F | age |   |   |   |   |   |   |   |

|----------|---|----|----|----|----|----|--------|------|--------|-----|---|---|---|---|---|---|---|

|          |   | 15 | 14 | 13 | 12 | 11 | 10     | 9    | 8      | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|          | 7 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| _        | 6 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| be       | 5 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| e Number | 4 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

|          | 3 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Page     | 2 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

| Δ.       | 1 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

|          | 0 |    |    |    |    |    |        |      |        |     |   |   |   |   |   |   |   |

Figure 3 • FlashROM Architecture

When using FlashROM combined with AES, many subscription-based applications or device serialization applications are possible. The FROM configurator found in the Libero SoC Catalog supports easy management of the FlashROM contents, even over large numbers of devices. The FROM configurator can support FlashROM contents that contain the following:

- Static values

- Random numbers

- · Values read from a file

- · Independent updates of each page

In addition, auto-incrementing of fields is possible. In applications where the FlashROM content is different for each device, you have the option to generate a single STAPL file for all the devices or individual serialization files for each device. For more information on how to generate the FlashROM content for device serialization, refer to the "FlashROM in Microsemi's Low Power Flash Devices" section of the Fusion and Extended Temperature Fusion FPGA Fabric User's Guide for more information.

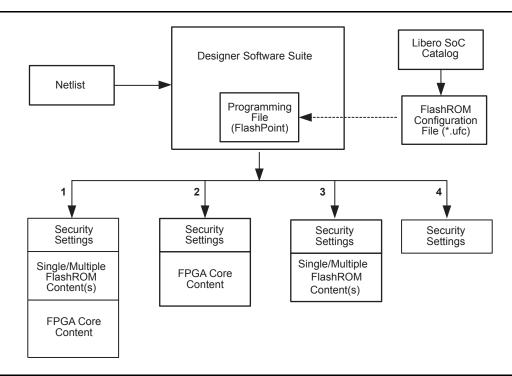

Libero SoC includes a unique tool to support the generation and management of FlashROM and FPGA programming files. This tool is called FlashPoint.

Depending on the applications, designers can use the FlashPoint software to generate a STAPL file with different contents. In each case, optional AES encryption and/or different security settings can be set.

In Designer, when you click the Programming File icon, FlashPoint launches, and you can generate STAPL file(s) with four different cases (Figure 4 on page 8). When the serialization feature is used during the configuration of FlashROM, you can generate a single STAPL file that will program all the devices or an individual STAPL file for each device.

The following cases present the FPGA core and FlashROM programming file combinations that can be used for different applications. In each case, you can set the optional security settings (FlashLock Pass Key and/or AES Key) depending on the application.

- A single STAPL file or multiple STAPL files with multiple FlashROM contents and the FPGA core content. A single STAPL file will be generated if the device serialization feature is not used. You can program the whole FlashROM or selectively program individual pages.

- 2. A single STAPL file for the FPGA core content

- A single STAPL file or multiple STAPL files with multiple FlashROM contents. A single STAPL file

will be generated if the device serialization feature is not used. You can program the whole

FlashROM or selectively program individual pages.

- A single STAPL file to configure the security settings for the device, such as the AES Key and/or Pass Key.

Figure 4 • Flexible Programming File Generation for Different Applications

#### **Programming Solution**

For device programming, any IEEE 1532–compliant programmer can be used; however, the FlashPro4/3/3X programmer must be used to control the low power flash device's rich security features and FlashROM programming options. The FlashPro4/3/3X programmer is a low-cost portable programmer for the Microsemi flash families. It can also be used with a powered USB hub for parallel programming. General specifications for the FlashPro4/3/3X programmer are as follows:

- Programming clock TCK is used with a maximum frequency of 20 MHz, and the default frequency is 4 MHz.

- Programming file STAPL

- Daisy chain Supported. You can use the ChainBuilder software to build the programming file for the chain.

- Parallel programming Supported. Multiple FlashPro4/3/3X programmers can be connected together using a powered USB hub or through the multiple USB ports on the PC.

- Power supply The target board must provide VCC, VCCI, VPUMP, and VJTAG during programming. However, if there is only one device on the target board, the FlashPro4/3/3X programmer can generate the required VPUMP voltage from the USB port.

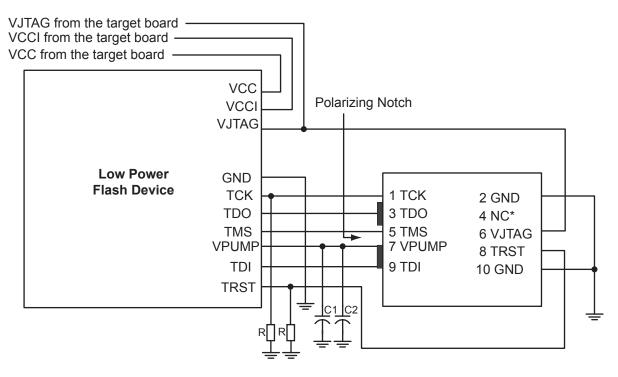

# **ISP Programming Header Information**

The FlashPro4/3/3X programming cable connector can be connected with a 10-pin, 0.1"-pitch programming header. The recommended programming headers are manufactured by AMP (103310-1) and 3M (2510-6002UB). If you have limited board space, you can use a compact programming header manufactured by Samtec (FTSH-105-01-L-D-K). Using this compact programming header, you are required to order an additional header adapter manufactured by Microsemi SoC Products Group (FP3-10PIN-ADAPTER-KIT).

Existing ProASICPLUS family customers who are using the Samtec Small Programming Header (FTSH-113-01-L-D-K) and are planning to migrate to IGLOO or ProASIC3 devices can also use FP3-10PIN-ADAPTER-KIT.

Table 3 • Programming Header Ordering Codes

| Manufacturer | Part Number           | Description                                                                                                                                                                                                                                                                                                                                        |

|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AMP          | 103310-1              | 10-pin, 0.1"-pitch cable header (right-angle PCB mount angle)                                                                                                                                                                                                                                                                                      |

| 3M           | 2510-6002UB           | 10-pin, 0.1"-pitch cable header (straight PCB mount angle)                                                                                                                                                                                                                                                                                         |

| Samtec       | FTSH-113-01-L-D-K     | Small programming header supported by FlashPro and Silicon Sculptor                                                                                                                                                                                                                                                                                |

| Samtec       | FTSH-105-01-L-D-K     | Compact programming header                                                                                                                                                                                                                                                                                                                         |

| Samtec       | FFSD-05-D-06.00-01-N  | 10-pin cable with 50 mil pitch sockets; included in FP3-10PIN-ADAPTER-KIT.                                                                                                                                                                                                                                                                         |

| Microsemi    | FP3-10PIN-ADAPTER-KIT | Transition adapter kit to allow FP3 to be connected to a micro 10-pin header (50 mil pitch). Includes a 6 inch Samtec FFSD-05-D-06.00-01-N cable in the kit. The transition adapter board was previously offered as FP3-26PIN-ADAPTER and includes a 26-pin adapter for design transitions from ProASICPLUS based boards to ProASIC3 based boards. |

**TCK GND** TDO 3 4 NC (FlashPro3/3X); Prog Mode\* (FlashPro4) 6 **VJTAG TMS** 5 **VPUMP** 8 **TRST** 9 10 TDI **GND**

Note: \*Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO nano, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 5 • Programming Header (top view)

Table 4 • Programming Header Pin Numbers and Description

| Pin | Signal           | Source       | Description      |  |  |  |  |  |

|-----|------------------|--------------|------------------|--|--|--|--|--|

| 1   | TCK              | Programmer   | JTAG Clock       |  |  |  |  |  |

| 2   | GND <sup>1</sup> | -            | Signal Reference |  |  |  |  |  |

| 3   | TDO              | Target Board | Test Data Output |  |  |  |  |  |

Table 4 • Programming Header Pin Numbers and Description

| Pin | Signal             | Source                  | Description                                                                                                                     |

|-----|--------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 4   | NC                 | -                       | No Connect (FlashPro3/3X); Prog_Mode (FlashPro4). See note associated with Figure 5 on page 9 regarding Prog_Mode on FlashPro4. |

| 5   | TMS                | Programmer              | Test Mode Select                                                                                                                |

| 6   | VJTAG              | Target Board            | JTAG Supply Voltage                                                                                                             |

| 7   | VPUMP <sup>2</sup> | Programmer/Target Board | Programming Supply Voltage                                                                                                      |

| 8   | nTRST              | Programmer              | JTAG Test Reset (Hi-Z with 10 k $\Omega$ pull-down, HIGH, LOW, or toggling)                                                     |

| 9   | TDI                | Programmer              | Test Data Input                                                                                                                 |

| 10  | GND <sup>1</sup>   | -                       | Signal Reference                                                                                                                |

#### Notes:

- 1. Both GND pins must be connected.

- 2. FlashPro4/3/3X can provide VPUMP if there is only one device on the target board.

#### **Board-Level Considerations**

A bypass capacitor is required from VPUMP to GND for all low power flash devices during programming. This bypass capacitor protects the devices from voltage spikes that may occur on the VPUMP supplies during the erase and programming cycles. Refer to the "Pin Descriptions and Packaging" chapter of the appropriate device datasheet for specific recommendations. For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible. The bypass capacitor must be placed within 2.5 cm of the device pins.

Note: \*NC (FlashPro3/3X); Prog\_Mode (FlashPro4). Prog\_Mode on FlashPro4 is an output signal that goes High during device programming and returns to Low when programming is complete. This signal can be used to drive a system to provide a 1.5 V programming signal to IGLOO V2, ProASIC3L, and RT ProASIC3 devices that can run with 1.2 V core voltage but require 1.5 V for programming. IGLOO nano V2 devices can be programmed at 1.2 V core voltage (when using FlashPro4 only), but IGLOO nano V5 devices are programmed with a VCC core voltage of 1.5 V.

Figure 6 • Board Layout and Programming Header Top View

# **Troubleshooting Signal Integrity**

#### Symptoms of a Signal Integrity Problem

A signal integrity problem can manifest itself in many ways. The problem may show up as extra or dropped bits during serial communication, changing the meaning of the communication. There is a normal variation of threshold voltage and frequency response between parts even from the same lot. Because of this, the effects of signal integrity may not always affect different devices on the same board in the same way. Sometimes, replacing a device appears to make signal integrity problems go away, but this is just masking the problem. Different parts on identical boards will exhibit the same problem sooner or later. It is important to fix signal integrity problems early. Unless the signal integrity problems are severe enough to completely block all communication between the device and the programmer, they may show up as subtle problems. Some of the FlashPro4/3/3X exit codes that are caused by signal integrity problems are listed below. Signal integrity problems are not the only possible cause of these

errors, but this list is intended to show where problems can occur. FlashPro4/3/3X allows TCK to be lowered from 6 MHz down to 1 MHz to allow you to address some signal integrity problems that may occur with impedance mismatching at higher frequencies. Customers are expected to troubleshoot board-level signal integrity issues by measuring voltages and taking scope plots.

#### Scan Chain Failure

Normally, the FlashPro4/3/3X Scan Chain command expects to see 0x1 on the TDO pin. If the command reports reading 0x0 or 0x3, it is seeing the TDO pin stuck at 0 or 1. The only time the TDO pin comes out of tristate is when the JTAG TAP state machine is in the Shift-IR or Shift-DR state. If noise or reflections on the TCK or TMS lines have disrupted the correct state transitions, the device's TAP state controller might not be in one of these two states when the programmer tries to read the device. When this happens, the output is floating when it is read and does not match the expected data value. This can also be caused by a broken TDO net. Only a small amount of data is read from the device during the Scan Chain command, so marginal problems may not always show up during this command. Occasionally a faulty programmer can cause intermittent scan chain failures.

#### Exit 11

This error occurs during the verify stage of programming a device. After programming the design into the device, the device is verified to ensure it is programmed correctly. The verification is done by shifting the programming data into the device. An internal comparison is performed within the device to verify that all switches are programmed correctly. Noise induced by poor signal integrity can disrupt the writes and reads or the verification process and produce a verification error. While technically a verification error, the root cause is often related to signal integrity.

Refer to the *FlashPro User's Guide* for other error messages and solutions. For the most up-to-date known issues and solutions, refer to http://www.microsemi.com/soc/support.

#### Conclusion

IGLOO, ProASIC3, SmartFusion, and Fusion devices offer a low-cost, single-chip solution that is live at power-up through nonvolatile flash technology. The FlashLock Pass Key and 128-bit AES Key security features enable secure ISP in an untrusted environment. On-chip FlashROM enables a host of new applications, including device serialization, subscription-based applications, and IP addressing. Additionally, as the FlashROM is nonvolatile, all of these services can be provided without battery backup.

#### **Related Documents**

#### **User's Guides**

FlashPro User's Guide

http://www.microsemi.com/soc/documents/flashpro\_ug.pdf

# **List of Changes**

The following table lists critical changes that were made in the current version of the document.

| Revision                      | Changes                                  | Page |

|-------------------------------|------------------------------------------|------|

| Revision 1<br>(February 2014) | Note below Figure 6 is updated.          | 11   |

|                               | The section ISP Architecture is updated. | 1    |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at www.microsemi.com.

© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.