# A Microchip Technology Company

# 2 Mbit SPI Serial Flash SST25VF020

Not Recommended for New Designs

SST's serial flash family features a four-wire. SPI-compatible interface that allows for a low pin-count package occupying less board space and ultimately lowering total system costs. SST25VF020 SPI serial flash memory is manufactured with SST proprietary, high performance CMOS SuperFlash Technology. The split-gate cell design and thick-oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches.

# **Features**

- Single 2.7-3.6V Read and Write Operations

- Serial Interface Architecture - SPI Compatible: Mode 0 and Mode 3

- 20 MHz Max Clock Frequency

#### Superior Reliability

- Endurance: 100,000 Cycles (typical)

Greater than 100 years Data Retention

#### Low Power Consumption:

- Active Read Current: 7 mA (typical)

- Standby Current: 8 µA (typical)

#### Flexible Erase Capability

- Uniform 4 KByte sectors

Uniform 32 KByte overlay blocks

#### • Fast Erase and Byte-Program:

- Chip-Erase Time: 70 ms (typical)

- Sector- or Block-Erase Time: 18 ms (typical)

- Byte-Program Time: 14 µs (typical)

#### Auto Address Increment (AAI) Programming

- Decrease total chip programming time over Byte-Program operations

- End-of-Write Detection

- Software Status

## Hold Pin (HOLD#)

- Suspends a serial sequence to the memory without deselecting the device

#### Write Protection (WP#)

- Enables/Disables the Lock-Down function of the status register

#### Software Write Protection

- Write protection through Block-Protection bits in status register

#### • Temperature Range

- Commercial: 0°C to +70°C

- Industrial: -40°C to +85°C

Extended: -20°C to +85°C

- Packages Available

- 8-lead SOIC 150 mil body width

8-contact WSON (5mm x 6mm)

- All non-Pb (lead-free) devices are RoHS compliant

Not Recommended for New Designs

# **Product Description**

The SST serial flash family features a four-wire, SPI-compatible interface that allows for a low pincount package occupying less board space and ultimately lowering total system costs. SST25VF020 SPI serial flash memories are manufactured with SST's proprietary, high performance CMOS Super-Flash Technology. The split-gate cell design and thick-oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches.

The SST25VF020 device significantly improves performance, while lowering power consumption. The total energy consumed is a function of the applied voltage, current, and time of application. Since for any given voltage range, the SuperFlash technology uses less current to program and has a shorter erase time, the total energy consumed during any Erase or Program operation is less than alternative flash memory technologies. The SST25VF020 device operates with a single 2.7-3.6V power supply.

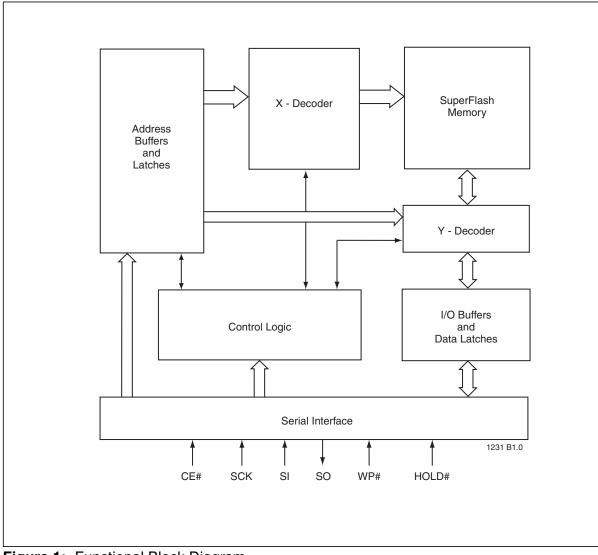

The SST25VF020 device is offered in an 8-lead SOIC 150 mil body width (SA) package, and in an 8-contact WSON package. See Figure 2 for the pin assignments.

Not Recommended for New Designs

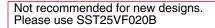

# **Block Diagram**

Figure 1: Functional Block Diagram

Not Recommended for New Designs

# **Pin Description**

#### Figure 2: Pin Assignments

#### Table 1: Pin Description

| Symbol          | Pin Name              | Functions                                                                                                                                                                                                           |

|-----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK             | Serial Clock          | To provide the timing of the serial interface.<br>Commands, addresses, or input data are latched on the rising edge of the clock input,<br>while output data is shifted out on the falling edge of the clock input. |

| SI              | Serial Data<br>Input  | To transfer commands, addresses, or data serially into the device.<br>Inputs are latched on the rising edge of the serial clock.                                                                                    |

| SO              | Serial Data<br>Output | To transfer data serially out of the device.<br>Data is shifted out on the falling edge of the serial clock.                                                                                                        |

| CE#             | Chip Enable           | The device is enabled by a high to low transition on CE#. CE# must remain low for the duration of any command sequence.                                                                                             |

| WP#             | Write Protect         | The Write Protect (WP#) pin is used to enable/disable BPL bit in the status register.                                                                                                                               |

| HOLD#           | Hold                  | To temporarily stop serial communication with SPI flash memory without resetting the device.                                                                                                                        |

| V <sub>DD</sub> | Power Supply          | To provide power supply (2.7-3.6V).                                                                                                                                                                                 |

| V <sub>SS</sub> | Ground                |                                                                                                                                                                                                                     |

T1.0 25078

# Memory Organization

The SST25VF020 SuperFlash memory array is organized in 4 KByte sectors with 32 KByte overlay blocks.

# **Device Operation**

The SST25VF020 is accessed through the SPI (Serial Peripheral Interface) bus compatible protocol. The SPI bus consist of four control lines; Chip Enable (CE#) is used to select the device, and data is accessed through the Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK).

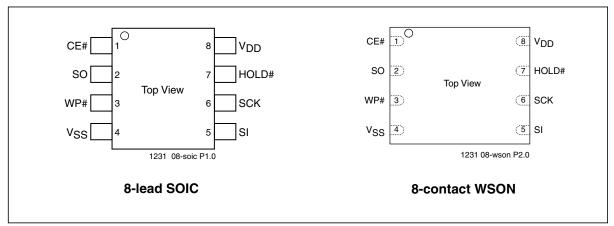

The SST25VF020 supports both Mode 0 (0,0) and Mode 3 (1,1) of SPI bus operations. The difference between the two modes, as shown in Figure 3, is the state of the SCK signal when the bus master is in Stand-by mode and no data is being transferred. The SCK signal is low for Mode 0 and SCK signal is high for Mode 3. For both modes, the Serial Data In (SI) is sampled at the rising edge of the SCK clock signal and the Serial Data Output (SO) is driven after the falling edge of the SCK clock signal.

Figure 3: SPI Protocol

Not Recommended for New Designs

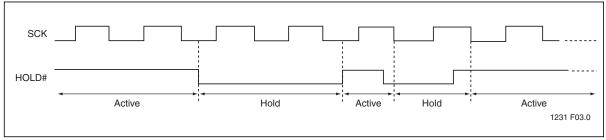

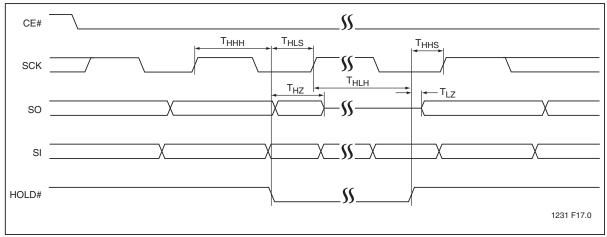

## Hold Operation

HOLD# pin is used to pause a serial sequence underway with the SPI flash memory without resetting the clocking sequence. To activate the HOLD# mode, CE# must be in active low state. The HOLD# mode begins when the SCK active low state coincides with the falling edge of the HOLD# signal. The HOLD mode ends when the HOLD# signal's rising edge coincides with the SCK active low state.

If the falling edge of the HOLD# signal does not coincide with the SCK active low state, then the device enters Hold mode when the SCK next reaches the active low state. Similarly, if the rising edge of the HOLD# signal does not coincide with the SCK active low state, then the device exits in Hold mode when the SCK next reaches the active low state. See Figure 4 for Hold Condition waveform.

Once the device enters Hold mode, SO will be in high-impedance state while SI and SCK can be  $V_{\text{IL}}$  or  $V_{\text{IH}}.$

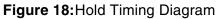

If CE# is driven active high during a Hold condition, it returns the device to standby mode. As long as HOLD# signal is low, the memory remains in the Hold condition. To resume communication with the device, HOLD# must be driven active high, and CE# must be driven active low. See Figure 18 for Hold timing.

Figure 4: Hold Condition Waveform

## **Write Protection**

SST25VF020 provides software Write protection. The Write Protect pin (WP#) enables or disables the lock-down function of the status register. The Block-Protection bits (BP1, BP0, and BPL) in the status register provide Write protection to the memory array and the status register. See Table 4 for Block-Protection description.

## Write Protect Pin (WP#)

The Write Protect (WP#) pin enables the lock-down function of the BPL bit (bit 7) in the status register. When WP# is driven low, the execution of the Write-Status-Register (WRSR) instruction is determined by the value of the BPL bit (see Table 2). When WP# is high, the lock-down function of the BPL bit is disabled.

| WP# | BPL | Execute WRSR Instruction |

|-----|-----|--------------------------|

| L   | 1   | Not Allowed              |

| L   | 0   | Allowed                  |

| Н   | Х   | Allowed                  |

T2.0 25078

## Status Register

The software status register provides status on whether the flash memory array is available for any Read or Write operation, whether the device is Write enabled, and the state of the memory Write protection. During an internal Erase or Program operation, the status register may be read only to determine the completion of an operation in progress. Table 3 describes the function of each bit in the software status register.

| Bit | Name | Function                                                                                                             | Default at<br>Power-up | Read/Write |

|-----|------|----------------------------------------------------------------------------------------------------------------------|------------------------|------------|

| 0   | BUSY | <ul><li>1 = Internal Write operation is in progress</li><li>0 = No internal Write operation is in progress</li></ul> | 0                      | R          |

| 1   | WEL  | <ul><li>1 = Device is memory Write enabled</li><li>0 = Device is not memory Write enabled</li></ul>                  | 0                      | R          |

| 2   | BP0  | Indicate current level of block write protection (See Table 4)                                                       | 1                      | R/W        |

| 3   | BP1  | Indicate current level of block write protection (See Table 4)                                                       | 1                      | R/W        |

| 4:5 | RES  | Reserved for future use                                                                                              | 0                      | N/A        |

| 6   | AAI  | Auto Address Increment Programming status<br>1 = AAI programming mode<br>0 = Byte-Program mode                       | 0                      | R          |

| 7   | BPL  | 1 = BP1, BP0 are read-only bits<br>0 = BP1, BP0 are read/writable                                                    | 0                      | R/W        |

#### Table 3: Software Status Register

T3.0 25078

#### Busy

The Busy bit determines whether there is an internal Erase or Program operation in progress. A "1" for the Busy bit indicates the device is busy with an operation in progress. A "0" indicates the device is ready for the next valid operation.

## Write Enable Latch (WEL)

The Write-Enable-Latch bit indicates the status of the internal memory Write Enable Latch. If the Write-Enable-Latch bit is set to "1", it indicates the device is Write enabled. If the bit is set to "0" (reset), it indicates the device is not Write enabled and does not accept any memory Write (Program/Erase) commands. The Write-Enable-Latch bit is automatically reset under the following conditions:

- Power-up

- Write-Disable (WRDI) instruction completion

- Byte-Program instruction completion

- Auto Address Increment (AAI) programming reached its highest memory address

- Sector-Erase instruction completion

- Block-Erase instruction completion

- Chip-Erase instruction completion

## Block Protection (BP1, BP0)

The Block-Protection (BP1, BP0) bits define the size of the memory area, as defined in Table 4, to be software protected against any memory Write (Program or Erase) operations. The Write-Status-Register (WRSR) instruction is used to program the BP1 and BP0 bits as long as WP# is high or the Block-Protect-Lock (BPL) bit is 0. Chip-Erase can only be executed if Block-Protection bits are both 0. After power-up, BP1 and BP0 are set to 1.

## **Block Protection Lock-Down (BPL)**

WP# pin driven low (V<sub>IL</sub>), enables the Block-Protection-Lock-Down (BPL) bit. When BPL is set to 1, it prevents any further alteration of the BPL, BP1, and BP0 bits. When the WP# pin is driven high (V<sub>IH</sub>), the BPL bit has no effect and its value is "Don't Care". After power-up, the BPL bit is reset to 0.

|                       | Status<br>Register<br>BitBP1BP0 |   | Protected Memory Area |

|-----------------------|---------------------------------|---|-----------------------|

| Protection Level      |                                 |   | 2 Mbit                |

| 0                     | 0                               | 0 | None                  |

| 1 (1/4 Memory Array)  | 0                               | 1 | 030000H-03FFFFH       |

| 2 (1/2 Memory Array)  | 1                               | 0 | 020000H-03FFFFH       |

| 3 (Full Memory Array) | 1                               | 1 | 000000H-03FFFFH       |

#### Table 4: Software Status Register Block Protection<sup>1</sup>

1. Default at power-up for BP1 and BP0 is '11'.

## T4.0 25078

## Auto Address Increment (AAI)

The Auto Address Increment Programming-Status bit provides status on whether the device is in AAI programming mode or Byte-Program mode. The default at power up is Byte-Program mode.

Not Recommended for New Designs

## Instructions

Instructions are used to Read, Write (Erase and Program), and configure the SST25VF020. The instruction bus cycles are 8 bits each for commands (Op Code), data, and addresses. Prior to executing any Byte-Program, Auto Address Increment (AAI) programming, Sector-Erase, Block-Erase, or Chip-Erase instructions, the Write-Enable (WREN) instruction must be executed first. The complete list of the instructions is provided in Table 5. All instructions are synchronized off a high to low transition of CE#. Inputs will be accepted on the rising edge of SCK starting with the most significant bit. CE# must be driven low before an instruction is entered and must be driven high after the last bit of the instruction has been shifted in (except for Read, Read-ID and Read-Status-Register instructions). Any low to high transition on CE#, before receiving the last bit of an instruction bus cycle, will terminate the instruction in progress and return the device to the standby mode. Instruction commands (Op Code), addresses, and data are all input from the most significant bit (MSB) first.

| Bus Cycle <sup>2</sup>                                 | 1               |      | 2                                    |                      | 3                                   | 3         | 4                              |           |                     | 5                 |

|--------------------------------------------------------|-----------------|------|--------------------------------------|----------------------|-------------------------------------|-----------|--------------------------------|-----------|---------------------|-------------------|

| Cycle Type/Operation <sup>3,4</sup>                    | S <sub>IN</sub> | SOUT | S <sub>IN</sub>                      | SOUT                 | S <sub>IN</sub>                     | SOUT      | S <sub>IN</sub>                | SOUT      | S <sub>IN</sub>     | SOUT              |

| Read                                                   | 03H             | Hi-Z | A <sub>23</sub> -<br>A <sub>16</sub> | Hi-Z                 | A <sub>15</sub> -<br>A <sub>8</sub> | Hi-Z      | A <sub>7</sub> -A <sub>0</sub> | Hi-Z      | Х                   | D <sub>OUT</sub>  |

| Sector-Erase <sup>5,6</sup>                            | 20H             | Hi-Z | A <sub>23</sub> -<br>A <sub>16</sub> | Hi-Z                 | A <sub>15</sub> -<br>A <sub>8</sub> | Hi-Z      | A <sub>7</sub> -A <sub>0</sub> | Hi-Z      | -                   | -                 |

| Block-Erase <sup>5,7</sup>                             | 52H             | Hi-Z | A <sub>23</sub> -<br>A <sub>16</sub> | Hi-Z                 | A <sub>15</sub> -<br>A <sub>8</sub> | Hi-Z      | A <sub>7</sub> -A <sub>0</sub> | Hi-Z      | -                   | -                 |

| Chip-Erase <sup>6</sup>                                | 60H             | Hi-Z | -                                    | -                    | -                                   | -         | -                              | -         | -                   | -                 |

| Byte-Program <sup>6</sup>                              | 02H             | Hi-Z | A <sub>23</sub> -<br>A <sub>16</sub> | Hi-Z                 | A <sub>15</sub> -<br>A <sub>8</sub> | Hi-Z      | A <sub>7</sub> -A <sub>0</sub> | Hi-Z      | Di<br>N             | Hi-Z              |

| Auto Address Increment (AAI)<br>Program <sup>6,8</sup> | AFH             | Hi-Z | A <sub>23</sub> -<br>A <sub>16</sub> | Hi-Z                 | A <sub>15</sub> -<br>A <sub>8</sub> | Hi-Z      | A <sub>7</sub> -A <sub>0</sub> | Hi-Z      | D <sub>I</sub><br>N | Hi-Z              |

| Read-Status-Register (RDSR)                            | 05H             | Hi-Z | Х                                    | D <sub>OU</sub><br>т | -                                   | Note<br>9 | -                              | Note<br>9 | -                   | Note <sup>9</sup> |

| Enable-Write-Status-Register (EWSR) <sup>10</sup>      | 50H             | Hi-Z | -                                    | -                    | -                                   | -         | -                              | -         | -                   | -                 |

| Write-Status-Register<br>(WRSR) <sup>10</sup>          | 01H             | Hi-Z | Data                                 | Hi-Z                 | -                                   | -         |                                | -         | -                   | -                 |

| Write-Enable (WREN)                                    | 06H             | Hi-Z | -                                    | -                    | -                                   | -         | -                              | -         | -                   | -                 |

| Write-Disable (WRDI)                                   | 04H             | Hi-Z | -                                    | -                    | -                                   | -         | -                              | -         | -                   | -                 |

| Read-ID                                                | 90H or<br>ABH   | Hi-Z | 00H                                  | Hi-Z                 | 00H                                 | Hi-Z      | ID<br>Addr <sup>11</sup>       | Hi-Z      | Х                   | D <sub>OUT</sub>  |

|                                                        | •               |      |                                      |                      |                                     | •         |                                | •         |                     | T5.0 25078        |

#### Table 5: Device Operation Instructions<sup>1</sup>

1. A<sub>MS</sub> = Most Significant Address

$A_{MS} = A_{17}$  for SST25VF020

Address bits above the most significant bit of each density can be  $V_{IL}$  or  $V_{IH}$

2. One bus cycle is eight clock periods.

3. Operation:  $S_{IN}$  = Serial In,  $S_{OUT}$  = Serial Out

4. X = Dummy Input Cycles (V<sub>IL</sub> or V<sub>IH</sub>); - = Non-Applicable Cycles (Cycles are not necessary)

5. Sector addresses: use  $A_{\text{MS}}\text{-}A_{12},$  remaining addresses can be  $V_{\text{IL}}$  or  $V_{\text{IH}}$

6. Prior to any Byte-Program, AAI-Program, Sector-Erase, Block-Erase, or Chip-Erase operation, the Write-Enable (WREN) instruction must be executed.

7. Block addresses for: use  $A_{\text{MS}}\text{-}A_{15},$  remaining addresses can be  $V_{\text{IL}}$  or  $V_{\text{IH}}$

- To continue programming to the next sequential address location, enter the 8-bit command, AFH, followed by the data to be programmed.

- 9. The Read-Status-Register is continuous with ongoing clock cycles until terminated by a low to high transition on CE#.

- 10. The Enable-Write-Status-Register (EWSR) instruction and the Write-Status-Register (WRSR) instruction must work in conjunction of each other. The WRSR instruction must be executed immediately (very next bus cycle) after the EWSR instruction to make both instructions effective.

- 11. Manufacturer's ID is read with  $A_0=0$ , and Device ID is read with  $A_0=1$ . All other address bits are 00H. The Manufacturer's and Device ID output stream is continuous until terminated by a low to high transition on CE#

- 12. Device ID = 43H for SST25VF020

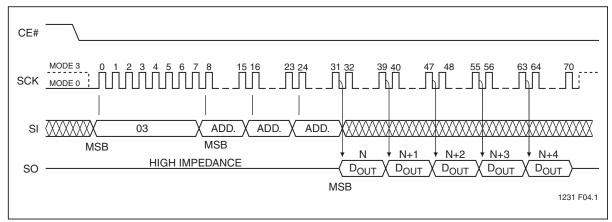

## Read

The Read instruction outputs the data starting from the specified address location. The data output stream is continuous through all addresses until terminated by a low to high transition on CE#. The internal address pointer will automatically increment until the highest memory address is reached. Once the highest memory address is reached, the address pointer will automatically increment to the beginning (wrap-around) of the address space, i.e. for 2 Mbit density, once the data from address location 3FFFFH had been read, the next output will be from address location 00000H.

The Read instruction is initiated by executing an 8-bit command, 03H, followed by address bits [ $A_{23}$ - $A_0$ ]. CE# must remain active low for the duration of the Read cycle. See Figure 5 for the Read sequence.

Figure 5: Read Sequence

Not Recommended for New Designs

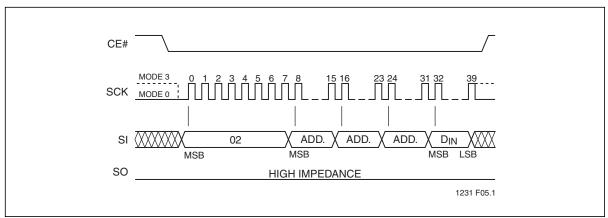

## Byte-Program

The Byte-Program instruction programs the bits in the selected byte to the desired data. The selected byte must be in the erased state (FFH) when initiating a Program operation. A Byte-Program instruction applied to a protected memory area will be ignored.

Prior to any Write operation, the Write-Enable (WREN) instruction must be executed. CE# must remain active low for the duration of the Byte-Program instruction. The Byte-Program instruction is initiated by executing an 8-bit command, 02H, followed by address bits  $[A_{23}-A_0]$ . Following the address, the data is input in order from MSB (bit 7) to LSB (bit 0). CE# must be driven high before the instruction is executed. The user may poll the Busy bit in the software status register or wait T<sub>BP</sub> for the completion of the internal self-timed Byte-Program operation. See Figure 6 for the Byte-Program sequence.

Figure 6: Byte-Program Sequence

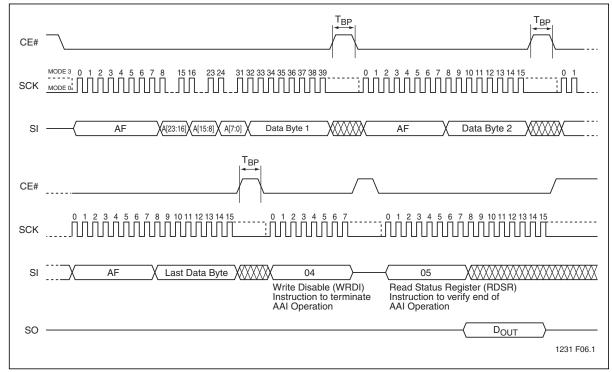

## Auto Address Increment (AAI) Program

The AAI program instruction allows multiple bytes of data to be programmed without re-issuing the next sequential address location. This feature decreases total programming time when the entire memory array is to be programmed. An AAI program instruction pointing to a protected memory area will be ignored. The selected address range must be in the erased state (FFH) when initiating an AAI program instruction.

Prior to any write operation, the Write-Enable (WREN) instruction must be executed. The AAI program instruction is initiated by executing an 8-bit command, AFH, followed by address bits  $[A_{23}-A_0]$ . Following the addresses, the data is input sequentially from MSB (bit 7) to LSB (bit 0). CE# must be driven high before the AAI program instruction is executed. The user must poll the BUSY bit in the software status register or wait T<sub>BP</sub> for the completion of each internal self-timed Byte-Program cycle. Once the device completes programming byte, the next sequential address may be program, enter the 8-bit command, AFH, followed by the data to be programmed. When the last desired byte had been programmed, execute the Write-Disable (WRDI) instruction, 04H, to terminate AAI. After execution of the WRDI command, the user must poll the Status register to ensure the device completes programming. See Figure 7 for AAI programming sequence.

There is no wrap mode during AAI programming; once the highest unprotected memory address is reached, the device will exit AAI operation and reset the Write-Enable-Latch bit (WEL = 0).

Figure 7: Auto Address Increment (AAI) Program Sequence

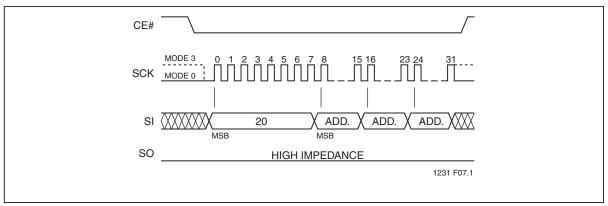

## Sector-Erase

The Sector-Erase instruction clears all bits in the selected 4 KByte sector to FFH. A Sector-Erase instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write-Enable (WREN) instruction must be executed. CE# must remain active low for the duration of the any command sequence. The Sector-Erase instruction is initiated by executing an 8-bit command, 20H, followed by address bits [A<sub>23</sub>-A<sub>0</sub>]. Address bits [A<sub>MS</sub>-A<sub>12</sub>] (A<sub>MS</sub> = Most Significant address) are used to determine the sector address (SA<sub>X</sub>), remaining address bits can be V<sub>IL</sub> or V<sub>IH.</sub> CE# must be driven high before the instruction is executed. The user may poll the Busy bit in the software status register or wait T<sub>SE</sub> for the completion of the internal self-timed Sector-Erase cycle. See Figure 8 for the Sector-Erase sequence.

Figure 8: Sector-Erase Sequence

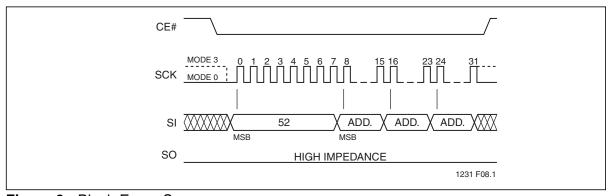

## **Block-Erase**

The Block-Erase instruction clears all bits in the selected 32 KByte block to FFH. A Block-Erase instruction applied to a protected memory area will be ignored. Prior to any Write operation, the Write-Enable (WREN) instruction must be executed. CE# must remain active low for the duration of any command sequence. The Block-Erase instruction is initiated by executing an 8-bit command, 52H, followed by address bits [A<sub>23</sub>-A<sub>0</sub>]. Address bits [A<sub>MS</sub>-A<sub>15</sub>] (A<sub>MS</sub> = Most significant address) are used to determine block address (BA<sub>X</sub>), remaining address bits can be V<sub>IL</sub> or V<sub>IH</sub>. CE# must be driven high before the instruction is executed. The user may poll the Busy bit in the software status register or wait T<sub>BE</sub> for the completion of the internal self-timed Block-Erase cycle. See Figure 9 for the Block-Erase sequence.

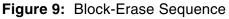

## Chip-Erase

The Chip-Erase instruction clears all bits in the device to FFH. A Chip-Erase instruction will be ignored if any of the memory area is protected. Prior to any Write operation, the Write-Enable (WREN) instruction must be executed. CE# must remain active low for the duration of the Chip-Erase instruction sequence. The Chip-Erase instruction is initiated by executing an 8-bit command, 60H. CE# must be driven high before the instruction is executed. The user may poll the Busy bit in the software status register or wait  $T_{CE}$  for the completion of the internal self-timed Chip-Erase cycle. See Figure 10 for the Chip-Erase sequence.

Figure 10: Chip-Erase Sequence

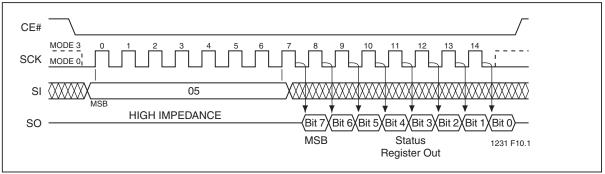

## **Read-Status-Register (RDSR)**

The Read-Status-Register (RDSR) instruction allows reading of the status register. The status register may be read at any time even during a Write (Program/Erase) operation. When a Write operation is in progress, the Busy bit may be checked before sending any new commands to assure that the new commands are properly received by the device. CE# must be driven low before the RDSR instruction is entered and remain low until the status data is read. Read-Status-Register is continuous with ongoing clock cycles until it is terminated by a low to high transition of the CE#. See Figure 11 for the RDSR instruction sequence.

Figure 11: Read-Status-Register (RDSR) Sequence

## Write-Enable (WREN)

The Write-Enable (WREN) instruction sets the Write-Enable-Latch bit to 1 allowing Write operations to occur. The WREN instruction must be executed prior to any Write (Program/Erase) operation. CE# must be driven high before the WREN instruction is executed.

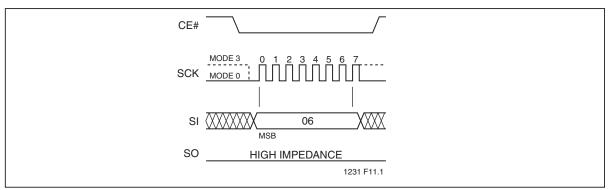

Figure 12: Write Enable (WREN) Sequence

## Write-Disable (WRDI)

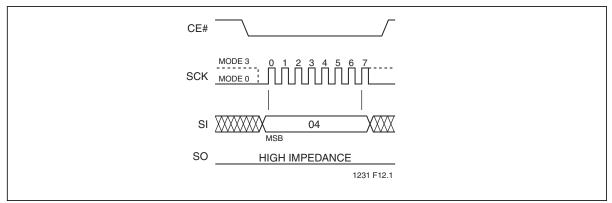

The Write-Disable (WRDI) instruction resets the Write-Enable-Latch bit and AAI bit to 0 disabling any new Write operations from occurring. CE# must be driven high before the WRDI instruction is executed.

Figure 13:Write Disable (WRDI) Sequence

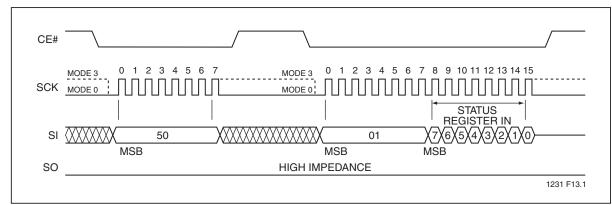

## Enable-Write-Status-Register (EWSR)

The Enable-Write-Status-Register (EWSR) instruction arms the Write-Status-Register (WRSR) instruction and opens the status register for alteration. The Enable-Write-Status-Register instruction does not have any effect and will be wasted, if it is not followed immediately by the Write-Status-Register (WRSR) instruction. CE# must be driven low before the EWSR instruction is entered and must be driven high before the EWSR instruction is executed.

Not Recommended for New Designs

## Write-Status-Register (WRSR)

The Write-Status-Register instruction works in conjunction with the Enable-Write-Status-Register (EWSR) instruction to write new values to the BP1, BP0, and BPL bits of the status register. The Write-Status-Register instruction must be executed immediately after the execution of the Enable-Write-Status-Register instruction (very next instruction bus cycle). This two-step instruction sequence of the EWSR instruction followed by the WRSR instruction works like SDP (software data protection) command structure which prevents any accidental alteration of the status register values. The Write-Status-Register instruction will be ignored when WP# is low and BPL bit is set to "1". When the WP# is low, the BPL bit can only be set from "0" to "1" to lock-down the status register, but cannot be reset from "1" to "0". When WP# is high, the lock-down function of the BPL bit is disabled and the BPL, BP0, and BP1 bits in the status register can all be changed. As long as BPL bit is set to 0 or WP# pin is driven high (VIH) prior to the low-to-high transition of the CE# pin at the end of the WRSR instruction, the BP0, BP1, and BPL bit in the status register can all be altered by the WRSR instruction. In this case, a single WRSR instruction can set the BPL bit to "1" to lock down the status register as well as altering the BP0 and BP1 bit at the same time. See Table 2 for a summary description of WP# and BPL functions. CE# must be driven low before the command sequence of the WRSR instruction is entered and driven high before the WRSR instruction is executed. See Figure 14 for EWSR and WRSR instruction sequences.

Figure 14: Enable-Write-Status-Register (EWSR) and Write-Status-Register (WRSR) Sequence

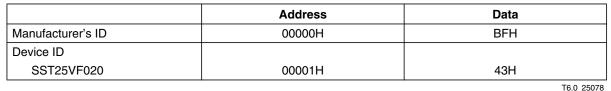

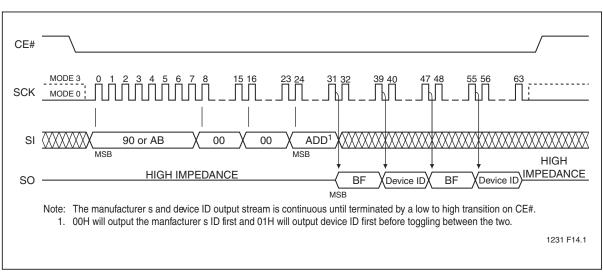

## Read-ID

The Read-ID instruction identifies the device as SST25VF020 and manufacturer as SST. The device information can be read from executing an 8-bit command, 90H or ABH, followed by address bits [ $A_{23}$ -  $A_0$ ]. Following the Read-ID instruction, the manufacturer's ID is located in address 00000H and the device ID is located in address 00001H. Once the device is in Read-ID mode, the manufacturer's and device ID output data toggles between address 00000H and 00001H until terminated by a low to high transition on CE#.

## Table 6: Product Identification

Figure 15:Read-ID Sequence

# **Electrical Specifications**

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Temperature Under Bias                                                           | 55°C to +125°C                               |

|----------------------------------------------------------------------------------|----------------------------------------------|

| Storage Temperature                                                              | 65°C to +150°C                               |

| D. C. Voltage on Any Pin to Ground Potential                                     | 0.5V to V <sub>DD</sub> +0.5V                |

| Transient Voltage (<20 ns) on Any Pin to Ground Potential                        | $\dots \dots$ -2.0V to V <sub>DD</sub> +2.0V |

| Package Power Dissipation Capability (Ta = 25°C)                                 | 1.0W                                         |

| Surface Mount Solder Reflow Temperature                                          | 260°C for 10 seconds                         |

| Output Short Circuit Current <sup>1</sup>                                        | 50 mA                                        |

| 1. Output shorted for no more than one second. No more than one output shorted a | t a time                                     |

1. Output shorted for no more than one second. No more than one output shorted at a time.

#### Table 7: Operating Range

| Range      | Ambient Temp   | V <sub>DD</sub> |

|------------|----------------|-----------------|

| Commercial | 0°C to +70°C   | 2.7-3.6V        |

| Industrial | -40°C to +85°C | 2.7-3.6V        |

| Extended   | -20°C to +85°C | 2.7-3.6V        |

T7.1 25078

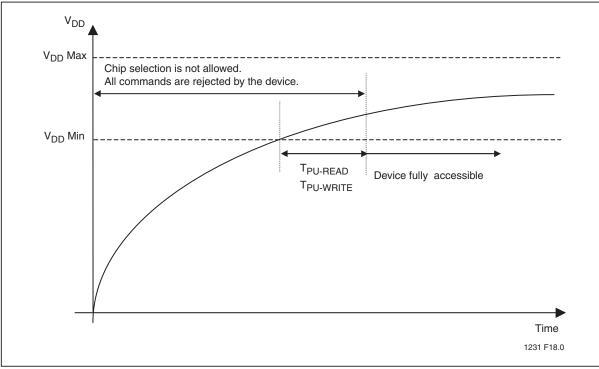

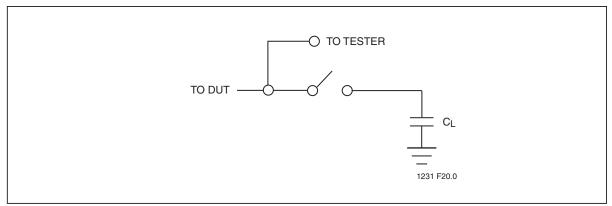

#### Table 8: AC Conditions of Test<sup>1</sup>

| Input Rise/Fall Time | Output Load            |

|----------------------|------------------------|

| 5ns                  | C <sub>L</sub> = 30 pF |

|                      | T8.1 25078             |

1. See Figures 20 and 21

#### **Table 9:** DC Operating Characteristics V<sub>DD</sub> = 2.7-3.6V

|                  |                           | Limits               |     |       |                                                                                |

|------------------|---------------------------|----------------------|-----|-------|--------------------------------------------------------------------------------|

| Symbol           | Parameter                 | Min                  | Max | Units | Test Conditions                                                                |

| I <sub>DDR</sub> | Read Current              |                      | 10  | mA    | CE#=0.1 V <sub>DD</sub> /0.9 V <sub>DD</sub> @20 MHz, SO=open                  |

| I <sub>DDW</sub> | Program and Erase Current |                      | 30  | mA    | CE#=V <sub>DD</sub>                                                            |

| I <sub>SB</sub>  | Standby Current           |                      | 15  | μA    | CE#=V <sub>DD</sub> , V <sub>IN</sub> =V <sub>DD</sub> or V <sub>SS</sub>      |

| ILI              | Input Leakage Current     |                      | 1   | μA    | V <sub>IN</sub> =GND to V <sub>DD</sub> , V <sub>DD</sub> =V <sub>DD</sub> Max |

| I <sub>LO</sub>  | Output Leakage Current    |                      | 1   | μA    | $V_{OUT}$ =GND to $V_{DD}$ , $V_{DD}$ = $V_{DD}$ Max                           |

| VIL              | Input Low Voltage         |                      | 0.8 | V     | V <sub>DD</sub> =V <sub>DD</sub> Min                                           |

| VIH              | Input High Voltage        | 0.7 V <sub>DD</sub>  |     | V     | V <sub>DD</sub> =V <sub>DD</sub> Max                                           |

| V <sub>OL</sub>  | Output Low Voltage        |                      | 0.2 | V     | $I_{OL}$ =100 µA, $V_{DD}$ = $V_{DD}$ Min                                      |

| V <sub>OH</sub>  | Output High Voltage       | V <sub>DD</sub> -0.2 |     | V     | I <sub>OH</sub> =-100 μA, V <sub>DD</sub> =V <sub>DD</sub> Min                 |

T9.0 25078

T11.0 25078

#### Table 10: Recommended System Power-up Timings

| Symbol                             | Parameter                              | Minimum | Units       |

|------------------------------------|----------------------------------------|---------|-------------|

| T <sub>PU-READ</sub> <sup>1</sup>  | V <sub>DD</sub> Min to Read Operation  | 10      | μs          |

| T <sub>PU-WRITE</sub> <sup>1</sup> | V <sub>DD</sub> Min to Write Operation | 10      | μs          |

|                                    |                                        |         | T10.0 25078 |

This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

#### Table 11:Capacitance (Ta = 25°C, f=1 Mhz, other pins open)

| Parameter                     | Description            | <b>Test Condition</b> | Maximum |

|-------------------------------|------------------------|-----------------------|---------|

| C <sub>OUT</sub> <sup>1</sup> | Output Pin Capacitance | $V_{OUT} = 0V$        | 12 pF   |

| C <sub>IN</sub> <sup>1</sup>  | Input Capacitance      | $V_{IN} = 0V$         | 6 pF    |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

#### Table 12: Reliability Characteristics

| Symbol                        | Parameter      | Minimum Specification | Units  | Test Method         |

|-------------------------------|----------------|-----------------------|--------|---------------------|

| N <sub>END</sub> <sup>1</sup> | Endurance      | 10,000                | Cycles | JEDEC Standard A117 |

| T <sub>DR</sub> <sup>1</sup>  | Data Retention | 100                   | Years  | JEDEC Standard A103 |

| ILTH <sup>1</sup>             | Latch Up       | 100 + I <sub>DD</sub> | mA     | JEDEC Standard 78   |

|                               | -              |                       |        | T12.0 25078         |

1. This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

©2011 Silicon Storage Technology, Inc.

Not Recommended for New Designs

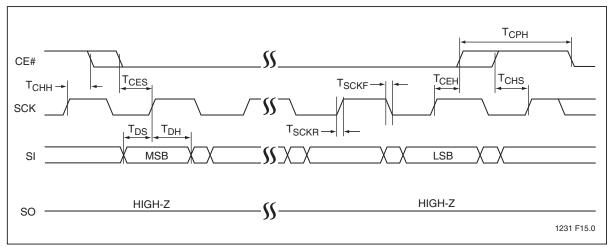

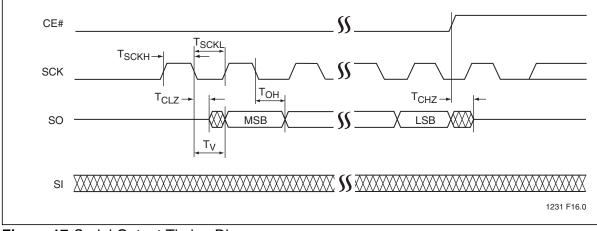

|                               |                             |     | Limits |       |

|-------------------------------|-----------------------------|-----|--------|-------|

| Symbol                        | Parameter                   | Min | Max    | Units |

| F <sub>CLK</sub>              | Serial Clock Frequency      |     | 20     | MHz   |

| Т <sub>SCKH</sub>             | Serial Clock High Time      | 20  |        | ns    |

| T <sub>SCKL</sub>             | Serial Clock Low Time       | 20  |        | ns    |

| T <sub>SCKR</sub>             | Serial Clock Rise Time      |     | 5      | ns    |

| T <sub>SCKF</sub>             | Serial Clock Fall Time      |     | 5      | ns    |

| T <sub>CES</sub> <sup>1</sup> | CE# Active Setup Time       | 20  |        | ns    |

| T <sub>CEH</sub> <sup>1</sup> | CE# Active Hold Time        | 20  |        | ns    |

| T <sub>CHS</sub> <sup>1</sup> | CE# Not Active Setup Time   | 10  |        | ns    |

| T <sub>CHH</sub> <sup>1</sup> | CE# Not Active Hold Time    | 10  |        | ns    |

| T <sub>CPH</sub>              | CE# High Time               | 100 |        | ns    |

| T <sub>CHZ</sub>              | CE# High to High-Z Output   |     | 20     | ns    |

| T <sub>CLZ</sub>              | SCK Low to Low-Z Output     | 0   |        | ns    |

| T <sub>DS</sub>               | Data In Setup Time          | 4   |        | ns    |

| T <sub>DH</sub>               | Data In Hold Time           | 5   |        | ns    |

| T <sub>HLS</sub>              | HOLD# Low Setup Time        | 10  |        | ns    |

| T <sub>HHS</sub>              | HOLD# High Setup Time       | 10  |        | ns    |

| T <sub>HLH</sub>              | HOLD# Low Hold Time         | 15  |        | ns    |

| Т <sub>ННН</sub>              | HOLD# High Hold Time        | 10  |        | ns    |

| T <sub>HZ</sub>               | HOLD# Low to High-Z Output  |     | 20     | ns    |

| T <sub>LZ</sub>               | HOLD# High to Low-Z Output  |     | 20     | ns    |

| Т <sub>ОН</sub>               | Output Hold from SCK Change | 0   |        | ns    |

| T <sub>V</sub>                | Output Valid from SCK       |     | 23     | ns    |

| T <sub>SE</sub>               | Sector-Erase                |     | 25     | ms    |

| T <sub>BE</sub>               | Block-Erase                 |     | 25     | ms    |

| T <sub>SCE</sub>              | Chip-Erase                  |     | 100    | ms    |

| T <sub>BP</sub>               | Byte-Program                |     | 20     | μs    |

# Table 13:AC Operating Characteristics $V_{DD} = 2.7-3.6V$

1. Relative to SCK.

T13.2 25078

Not Recommended for New Designs

Figure 16:Serial Input Timing Diagram

Figure 17:Serial Output Timing Diagram

Not Recommended for New Designs

Figure 19: Power-up Timing Diagram

Not Recommended for New Designs

Figure 21:A Test Load Example

Not Recommended for New Designs

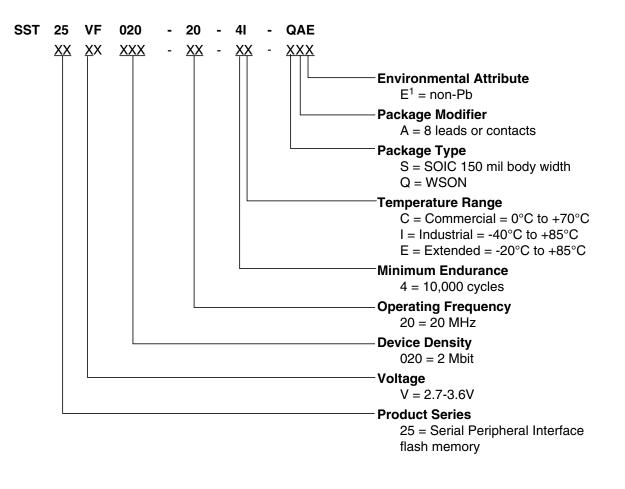

# **Product Ordering Information**

1. Environmental suffix "E" denotes non-Pb solder. SST non-Pb solder devices are "RoHS Compliant".

## Valid combinations for SST25VF020

SST25VF020-20-4C-SAE SST25VF020-20-4I-SAE SST25VF020-20-4E-SAE SST25VF020-20-4C-QAE SST25VF020-20-4I-QAE SST25VF020-20-4E-QAE

**Note:**Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

Not Recommended for New Designs

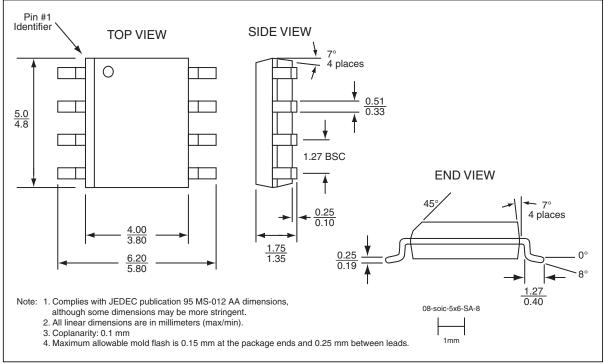

# **Packaging Diagrams**

Figure 22: 8-lead Small Outline Integrated Circuit (SOIC) 150 mil body width (4.9mm x 6mm) SST Package Code: SA

Not Recommended for New Designs

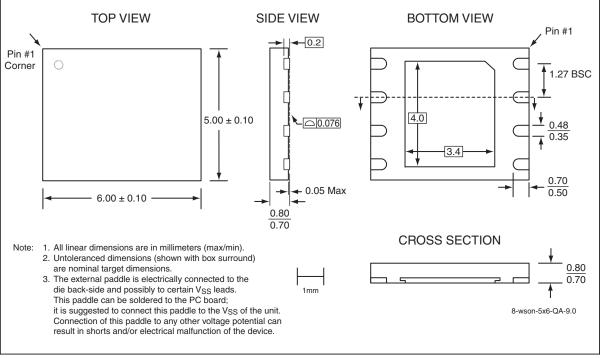

Figure 23:8-contact Very-very-thin Small Outline No-lead (WSON) SST Package Code: QA

#### Table 14: Revision History

| Revision | Description                                                                                                                                                                     | Date     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 00       | Initial release of S71231                                                                                                                                                       | Apr 2003 |

|          | (2 Mbit and 4 Mbit parts were originally described in data sheet S71192)                                                                                                        |          |

| 01       | • Updated Figures 3, 5 - 15: Aligned SI waveform with rising edge of clock                                                                                                      | Aug 2003 |

| 02       | Added new 8-SOIC (S2A) package and associated MPNs                                                                                                                              | Oct 2003 |

| 03       | 2004 Data Book                                                                                                                                                                  | Dec 2003 |

|          | Updated the Package Outline for S2A                                                                                                                                             |          |

| 04       | Added Extended temperature and associated MPNs                                                                                                                                  | Jun 2004 |

| 05       | Revised Absolute Max. Stress Ratings for Surface Mount Solder Reflow<br>Temp.                                                                                                   | Nov 2005 |

| 06       | Updated QA package drawing to revision 9.                                                                                                                                       | Jan 2006 |

|          | Removed leaded parts.                                                                                                                                                           |          |

|          | Added footnote to product ordering section.                                                                                                                                     |          |

| 07       | Removed all references to SST25VF040 due to end of life. New SST25VF040 EOL data sheet is S71231(04).                                                                           | Oct 2006 |

|          | <ul> <li>Revised Hold Operation, page 6 paragraph 4, to indicate that device<br/>returns to standby mode when CE# is driven active high during a Hold<br/>Condition.</li> </ul> |          |

| А        | Applied new document format                                                                                                                                                     | Nov 2011 |

|          | Released document under letter revision system                                                                                                                                  |          |

|          | Updated spec number from S71231 to DS25078                                                                                                                                      |          |

ISBN:978-1-61341-680-8

© 2011 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

#### Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com