# 512MB (2 x 64M x 32) / 1GB (4 x 64M x 32) NOR Flash MCP 3V Page Mode Memory

W7264M32V1-XSBX / W7464M32V1-XSBX

#### **FEATURES**

- Single power supply operation

- 3 Volt read, erase, and program operations

- I/O Control

- Wide I/O voltage range (Vio): 1.8V to Vcc

- All input levels (address, control, and DQ input levels) and outputs are determined by voltage on V<sub>IO</sub> input.

- Separate 1024-byte One Time Program (OTP) array with two lockable regions

- Uniform sector architecture

- · One thousand twenty four 128 Kbyte sectors

- 100,000 erase cycles per sector typical

- 20-year data retention typical

- Commercial, industrial and military temperature ranges

- Organized as 2 ranks of 64M x 32 (512MB), 4 ranks of 64M x 32 (1GB)

#### PERFORMANCE CHARACTERISTICS

- High Performance

- 110, 120 ns

- · 32-byte page read buffer

- · 15, 20 ns page read times

- 512-byte write buffer reduces overall programming time for multiple-word updates

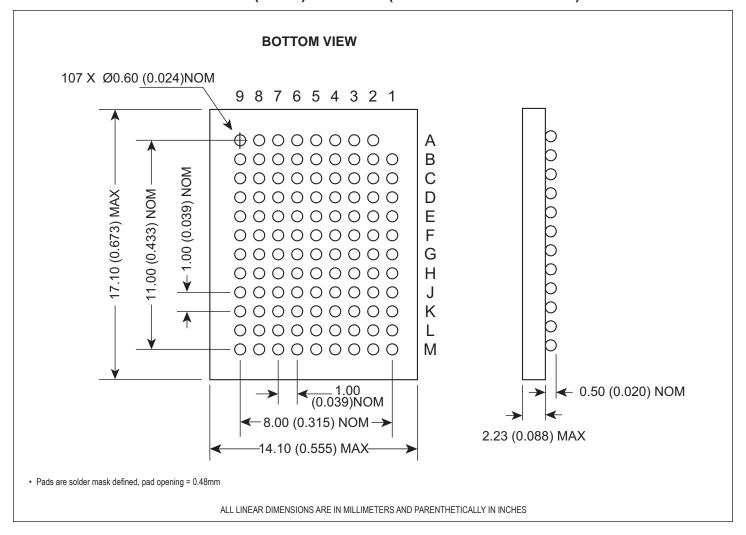

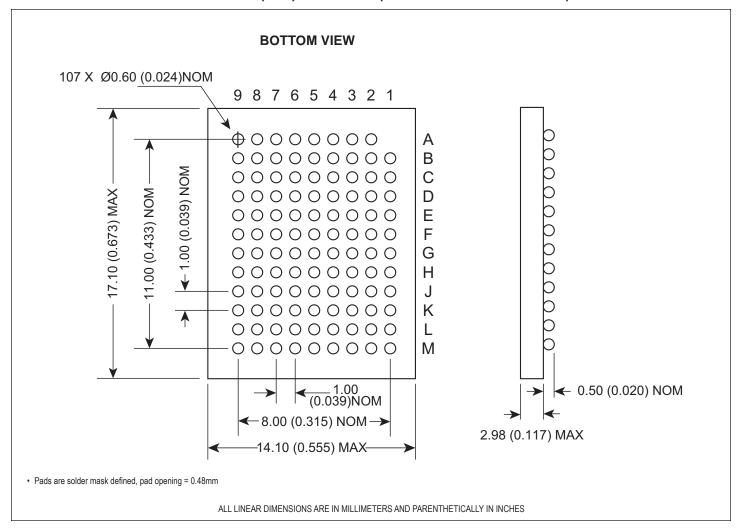

- Package option

- 107 BGA, 14mm x 17mm

- 1.0mm pitch

- Footprint compatible with W764M32V1-XBX

- Software features

- Suspend and resume commands for program and erase operations

- · Data# polling and toggle bits provide status

- CFI (Common Flash Interface) parameter table

- Hardware features

- Advanced Sector Protection (ASP)

- · Hardware reset input (RESET#) resets device

- Status Register, data polling, and ready/busy pin methods to determine device status.

#### **GENERAL DESCRIPTION**

The W7264M32V1-XSBX device is a 3V single power flash memory and utilizes four chips organized as 67,108,864 words. The W7464M32V1-XSBX device is a 3V single power flash memory and utilizes eight chips organized as 67,108,864 words. These devices have a 32-bit wide data bus. One write enable per 16-bit data word. Each device requires a single 3 volt power supply for both read and write functions.

<sup>\*</sup> This product is subject to change without notice.

# FIGURE 1 – PIN CONFIGURATION (TOP VIEW)

| A | 1      | 2      | 3      |        | _   | _     | 7        | 0       | 0     |

|---|--------|--------|--------|--------|-----|-------|----------|---------|-------|

| Α |        |        |        | 4      | 5   | 6     | 7        | 8       | 9     |

|   |        | Vcc    | DQ24   | DQ8    | GND | (A1)  | (A4)     | Vcc     | GND   |

| В | VIO    | DQ10   | DQ25   | DQ9    | GND | (A2)  | (A5)     | (A7)    | VIO   |

| С | DQ12   | DQ27   | (DQ11) | DQ26   | GND | OE#   | (A6)     | RY/BY#) | (A8)  |

| D | DQ13   | (DQ29) | (DQ28) | CS2#*  | GND | (A3)  | (RESET#) | WP#     | (A15) |

| Е | DQ14   | DQ30   | DQ31   | VIO    | GND | VIO   | CS0#     | WE1#    | (A16) |

| F | (DQ15) | GND    | VIO    | Vcc    | GND | Vcc   | VIO      | GND     | (A23) |

| G | (DQ0)  | GND    | VIO    | Vcc    | GND | Vcc   | VIO      | GND     | (A24) |

| Н | DQ1    | DQ17   | DQ16)  | VIO    | GND | VIO   | CS1#     | WE0#    | (A18) |

| J | (DQ18) | DQ2    | DQ3    | CS3#*  | GND | (A20) | (A21)    | (A22)   | (A19) |

| K | (DQ19) | DQ4    | DQ20   | (DQ21) | GND | (A0)  | (A11)    | (A10)   | (A9)  |

| L | VIO    | DQ5    | DQ6    | DQ23   | GND | (A17) | (A13)    | (A12)   | VIO   |

| М | GND    | Vcc    | (DQ22) | (DQ7)  | GND | (A25) | (A14)    | Vcc     | GND   |

|   | 1      | 2      | 3      |        | 5   | 6     |          |         |       |

\*Balls D4 (CS2#) and J4 (CS3#) are not connected in W7264M32V1 devices

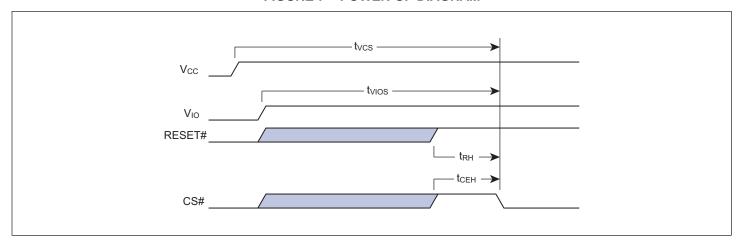

FIGURE 2 - W7264M32V1 (512MB) BLOCK DIAGRAM

WE0# WE1# CS0# -CS# WE# CS# WE# A0-25 A0-25 A0-25 OE# OE# OE# RESET# RESET# RESET# IC1 IC2 RY/BY# RY/BY# RY/BY# WP# WP# WP# I/O 0-15 I/O 0-15 **′16** 16 CS1# CS# WE# CS# WE# A0-25 A0-25 OE# OE# RESET# RESET# IC3 IC4 RY/BY# RY/BY# WP# WP# I/O 0-15 I/O 0-15 **′16** 16 CS2# CS# WE# CS# WE# A0-25 A0-25 OE# OE# RESET# RESET# IC5 IC6 RY/BY# RY/BY# WP# WP# I/O 0-15 I/O 0-15 ′16 ′16 CS3# CS# WE# CS# WE# A0-25 A0-25 **PIN DESCRIPTION** OE# OE# DQ0-31 Data Inputs/Outputs RESET# RESET# IC7 IC8 A0-25 Address Inputs RY/BY# RY/BY# WE#0-1 Write Enables WP# WP# CS#0-3 Chip Selects OE# Output Enable I/O 0-15 I/O 0-15 RESET# Hardware Reset 16 **′16** WP# Hardware Write Protection RY/BY# Ready/Busy Output Vcc Power Supply DQ 0-15 DQ 16-31 Vio I/O Power Supply **GND** Ground

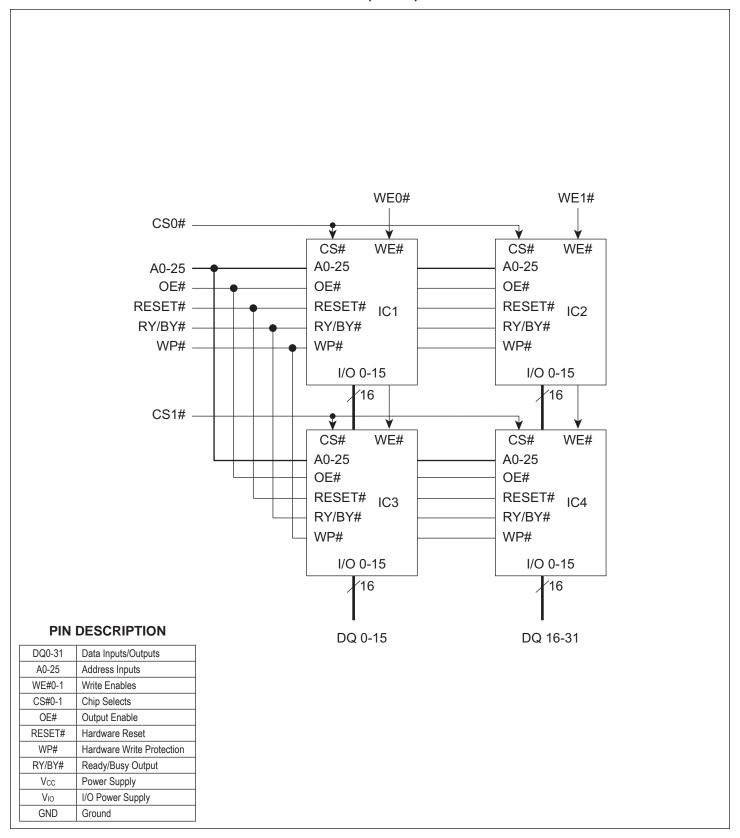

FIGURE 3 - W7464M32V1 (1GB) BLOCK DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                |                              | Unit |

|------------------------------------------|------------------------------|------|

| Supply Voltage Range (Vcc)               | -0.5 to +4.0                 | V    |

| Signal Voltage Range (other than RESET#) | -0.5 to V <sub>IO</sub> +0.5 | V    |

| I/O Voltage Range (Vio)                  | -0.5 to +4.0                 | V    |

| RESET#                                   | -0.5 to Vcc +0.5             | V    |

| Storage Temperature Range                | -55 to +125                  | °C   |

#### NOTES:

- 1. Minimum DC voltage on input or i/Os is -0.5V. During voltage transitions, input or I/Os pins may overshoot GND to -2.0V for periods of up to 20ns. Maximum DC voltage on input or I/Os pins is Vcc + 0.5V. During voltage transitions, input or I/O pins may overshoot to Vcc + 2.0V for periods up to 20ns

- 2. Stresses above those listed under Absolute Maxium Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of the data sheet is not implied. Exposure of the device to absolute maxium rating conditions for extended peroids may affect device reliability

#### RECOMMENDED OPERATING CONDITIONS

| Parameter      | Symbol          | Min | Max                   | Unit |

|----------------|-----------------|-----|-----------------------|------|

| Supply Voltage | Vcc             | 3.0 | 3.6                   | V    |

| I/O Voltage    | V <sub>IO</sub> | 1.7 | V <sub>CC</sub> + 0.2 | V    |

#### **AC TEST CONDITIONS**

| Parameter                        | Тур                              | Unit |

|----------------------------------|----------------------------------|------|

| Input Pulse Levels               | $V_{IL} = 0$ , $V_{IH} = V_{IO}$ | V    |

| Input Rise and Fall              | 1.5                              | ns   |

| Input and Output Reference Level | V <sub>IO</sub> x 0.5            | V    |

| Output Timing Reference Level    | V <sub>IO</sub> x 0.5            | V    |

#### NOTES:

IoL & IoH programmable from 0 to 16mA.

Tester Impedance  $Z0 = 50\Omega$ .

$V_Z$  is typically the midpoint of  $V_{\text{OH}}$  and  $V_{\text{OL}}.$

$I_{\text{OL}}$  &  $I_{\text{OH}}$  are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

# W7264M32V1 (512MB) BGA THERMAL RESISTANCE

| Description            | Symbol   | Typical | Units | Notes |

|------------------------|----------|---------|-------|-------|

| Junction to Board      | Theta JB | 16.3    | °C/W  | 1     |

| Junction to Case (Top) | Theta JC | 11.9    | °C/W  | 1     |

The JEDEC JESD51 specifications are used as the default modeling environment and boundary conditions. Using still air, horizontal mounting and the 2s2p board. Published material properties are used as input to derive the thermal characteristics of the module. Your application conditions will most likely differ from the JESD51 2s2p board definition specifications; therefore, Microsemi PMG recommends a customized evaluation of thermal resistances based on the actual conditions in thermally-challenged situations. Delphi models are available for most products upon request.

#### W7464M32V1 (1GB) BGA THERMAL RESISTANCE

| Description            | Symbol   | Typical | Units | Notes |

|------------------------|----------|---------|-------|-------|

| Junction to Board      | Theta JB | 20.4    | °C/W  | 1     |

| Junction to Case (Top) | Theta JC | 14.9    | °C/W  | 1     |

The JEDEC JESD51 specifications are used as the default modeling environment and boundary conditions. Using still air, horizontal mounting and the 2s2p board. Published material properties are used as input to derive the thermal characteristics of the module. Your application conditions will most likely differ from the JESD51 2s2p board definition specifications; therefore, Microsemi PMG recommends a customized evaluation of thermal resistances based on the actual conditions in thermally-challenged situations. Delphi models are available for most products upon request.

## W7264M32V1-XSBX / W7464M32V1-XSBX

#### **DC CHARACTERISTICS**

| Parameter                                           | Symbol           | Conditions                                                                                                                               | Min                    | Max                    | Unit |

|-----------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|------|

| Input Load Current (512MB)                          | ILI              | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub>                                            |                        | ±4.0                   | μA   |

| Output Leakage Current (512MB)                      | ILO              | Vout = Vss to Vcc, Vcc = Vcc(MAX)                                                                                                        |                        | ±2.0                   | μA   |

| Input Load Current (1GB)                            | ILI              | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub>                                            |                        | ±8.0                   | μA   |

| Output Leakage Current (1GB)                        | ILO              | Vout = Vss to Vcc, Vcc = Vcc(MAX)                                                                                                        |                        | ±4.0                   | μΑ   |

| V <sub>CC</sub> Active Current for Read (6)         | Icc1             | CS# = V <sub>IL</sub> , OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub> ; address switching at 5MHz                       |                        | 120                    | mA   |

| V <sub>CC</sub> Intra-Page Read Current (6)         | Icc2             | CS# = V <sub>IL</sub> #, OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub> ; f = 33MHz                                      |                        | 50                     | mA   |

| V <sub>CC</sub> Active Erase/Program Current (1, 6) | Іссз             | CS# = V <sub>IL</sub> #, OE# = V <sub>IH</sub> , V <sub>CC</sub> = V <sub>CC(MAX)</sub>                                                  |                        | 200                    | mA   |

| Vcc Standby Current (512MB) (7)                     | Icc4             | CS#, RESET#, OE# = Vih, Vih = Vio, Vil = Vss, Vcc = Vcc MAX                                                                              |                        | 800                    | μΑ   |

| Vcc Standby Current (1GB) (7)                       | Icc4             | CS#, RESET#, OE# = Vih, Vih = Vio, Vil = Vss, Vcc = Vcc MAX                                                                              |                        | 1.6                    | mA   |

| Vcc Reset Current (3, 5, 6)                         | Icc5             | CS# = Vih, RESET# = Vil, Vcc = Vcc MAX                                                                                                   |                        | 40                     | mA   |

| Automotic Close Mode (E12MP) (2 E 7)                | lasa             | V <sub>IH</sub> = V <sub>IO</sub> , V <sub>IL</sub> = V <sub>SS</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> , t <sub>ACC</sub> + 30 ns |                        | 12                     | mA   |

| Automatic Sleep Mode (512MB) (2, 5, 7)              | Icc6             | V <sub>IH</sub> = V <sub>IO</sub> , V <sub>IL</sub> = V <sub>SS</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> , tassb                    |                        | 800                    | μΑ   |

| Automotic Close Mode (1CD) (2 F 7)                  | lasa             | V <sub>IH</sub> = V <sub>IO</sub> , V <sub>IL</sub> = V <sub>SS</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> , t <sub>ACC</sub> + 30 ns |                        | 24                     | mA   |

| Automatic Sleep Mode (1GB) (2, 5, 7)                | Icc6             | V <sub>IH</sub> = V <sub>IO</sub> , V <sub>IL</sub> = V <sub>SS</sub> , V <sub>CC</sub> = V <sub>CC MAX</sub> , tassb                    |                        | 1.6                    | mA   |

| V <sub>CC</sub> current during power up (5, 6)      | Icc7             | RESET# = Vio, CS# = Vio, Vcc = Vcc MAX                                                                                                   |                        | 160                    | mA   |

| Input Low Voltage                                   | VIL              |                                                                                                                                          | -0.5                   | 0.3 x V <sub>IO</sub>  | V    |

| Input High Voltage                                  | ViH              |                                                                                                                                          | 0.7 x V <sub>IO</sub>  | V <sub>IO</sub> + 0.4  | V    |

| Output Low Voltage (4)                              | V <sub>OL</sub>  | $I_{OL}$ = 100 $\mu$ A for DQs, $I_{OL}$ = 2mA for RY/BY#                                                                                |                        | 0.15 x V <sub>IO</sub> | V    |

| Output High Voltage                                 | Voh              | I <sub>OH</sub> = 100 μA                                                                                                                 | 0.85 x V <sub>IO</sub> |                        | V    |

| Low V <sub>CC</sub> Lock-Out Voltage (5)            | V <sub>LKO</sub> |                                                                                                                                          | 2.25                   | 2.5                    | V    |

#### NOTES:

- 1. Icc active while Embedded Algorithm is in progress.

- 2. Automatic sleep mode enables the lower power mode when addresses remain stable for the specified designated time.

- 3. If an embedded operation is in progress at the start of reset, the current consumption will remain at the embedded operation specification until the embedded operation is stopped by the reset. If no embedded operation is in progress when reset is started, or following the stopping of an embedded operation, Icc7 will be drawn during the remainder of tRPH. After the end of tRPH the device will go to standby mode until the next read or write.

- 4. The recommended pull-up resistor for RY/BY# output is 5k to 10k Ohms.

- 5. Guaranteed by design, not tested

- 6. Current value is for 1-rank of 32-bit data flash only.

- 7. Max value when all chips of the device are in this low power mode

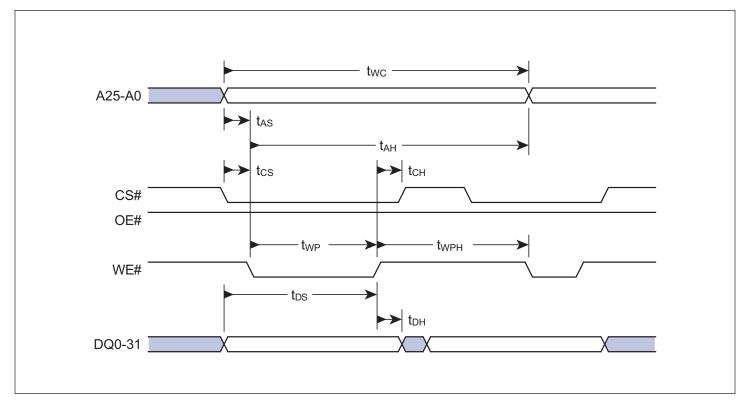

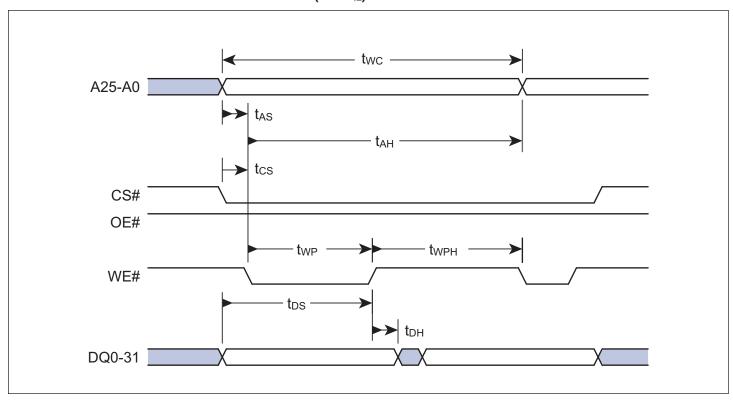

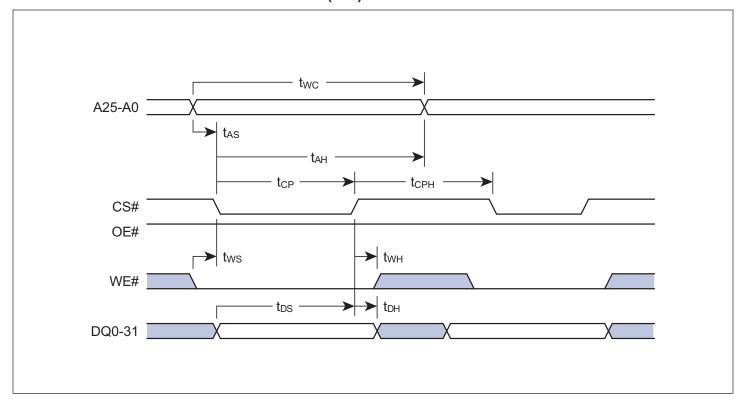

#### AC CHARACTERISTICS - WRITE/ERASE/PROGRAM OPERATIONS - WE# CONTROLLED

| Parameter                                               | Syr               | nbol            | Min | 110<br>Max | Min -1 | 20<br>Max | Unit |

|---------------------------------------------------------|-------------------|-----------------|-----|------------|--------|-----------|------|

| Write Cycle Time                                        | t <sub>AVAV</sub> | twc             | 60  |            | 60     |           | ns   |

| Chip Select Setup Time                                  | t <sub>ELWL</sub> | tcs             | 0   |            | 0      |           | ns   |

| Write Enable Pulse Width                                | twLWH             | twp             | 25  |            | 25     |           | ns   |

| Address Setup Time                                      | tavwl             | tas             | 0   |            | 0      |           | ns   |

| Data Setup Time                                         | tоvwн             | tos             | 30  |            | 30     |           | ns   |

| Data Hold Time                                          | twhox             | tон             | 0   |            | 0      |           | ns   |

| Address Hold Time                                       | twlax             | tah             | 45  |            | 45     |           | ns   |

| Write Enable Pulse Width High (3)                       | twnwL             | twpн            | 20  |            | 20     |           | ns   |

| Single Word Programming Time (1)                        | twnwh1            |                 |     | 400        |        | 400       | μs   |

| Buffer Programming Time                                 |                   |                 |     | 750        |        | 750       | μs   |

| Sector Erase (2)                                        | twhwh2            |                 |     | 1.1        |        | 1.1       | sec  |

| Read Recovery Time before Write (3)                     | tghwl             |                 | 0   |            | 0      |           | ns   |

| Address Setup Time to OE# low during toggle bit polling |                   | taso            | 15  |            | 15     |           | ns   |

| Write Recovery Time from RY/BY# (3)                     |                   | t <sub>RB</sub> | 0   |            | 0      |           | ns   |

| Program/Erase Valid to RY/BY# (3)                       |                   | tBUSY           |     | 80         |        | 80        | ns   |

#### NOTES:

- 1. Typical value for twhwh1 is 125  $\mu$ s.

- 2. Typical value for twhwh2 is 0.275 sec.

- 3. Guaranteed by design, not tested.

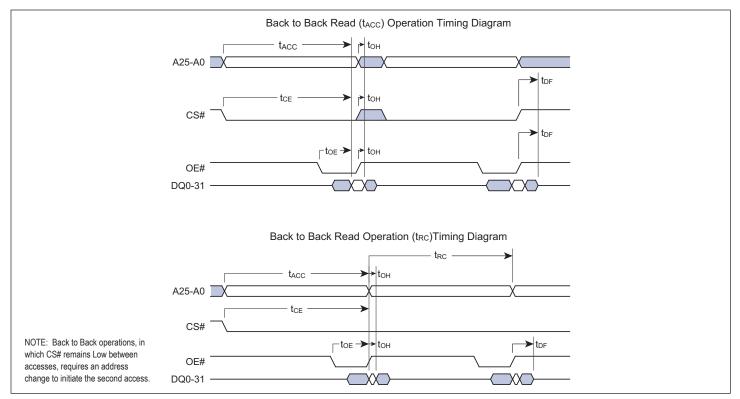

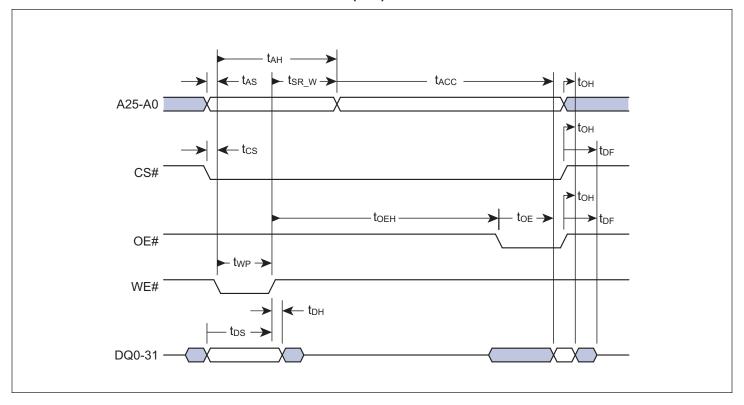

## **AC CHARACTERISTICS – READ-ONLY OPERATIONS**

| Parameter                                                             |                          | Symbol            |                  | -1<br>Min | 10<br>Max | -1<br>Min | 20<br>Max | Unit |

|-----------------------------------------------------------------------|--------------------------|-------------------|------------------|-----------|-----------|-----------|-----------|------|

| Read Cycle Time                                                       |                          | t <sub>AVAV</sub> | t <sub>RC</sub>  | 110       |           | 120       |           | ns   |

| Address Access Time                                                   |                          | tavqv             | tacc             |           | 110       |           | 120       | ns   |

| Chip Select Access Time                                               |                          | t <sub>ELQV</sub> | tce              |           | 110       |           | 120       | ns   |

| Page Access Time                                                      |                          |                   | tPACC            |           | 15        |           | 20        | ns   |

| Output Enable to Output Valid                                         |                          | tglqv             | toe              |           | 25        |           | 25        | ns   |

| Chip Select High to Output High Z                                     |                          | tehqz             | tor              |           | 15        |           | 15        | ns   |

| Output Enable High to Output High Z                                   |                          | tghqz             | tor              |           | 15        |           | 15        | ns   |

| Output Hold from Addresses, CS# or OE# Change, Whichever occurs first |                          | taxqx             | tон              | 0         |           | 0         |           | ns   |

| Output Enable Hold Time (1)                                           | Read                     |                   |                  | 0         |           | 0         |           | ns   |

| Output Enable Hold Time (1)                                           | Toggle and Data# Polling |                   | t <sub>OEH</sub> | 10        |           | 10        |           | ns   |

<sup>1.</sup> Guaranteed by design, not tested.

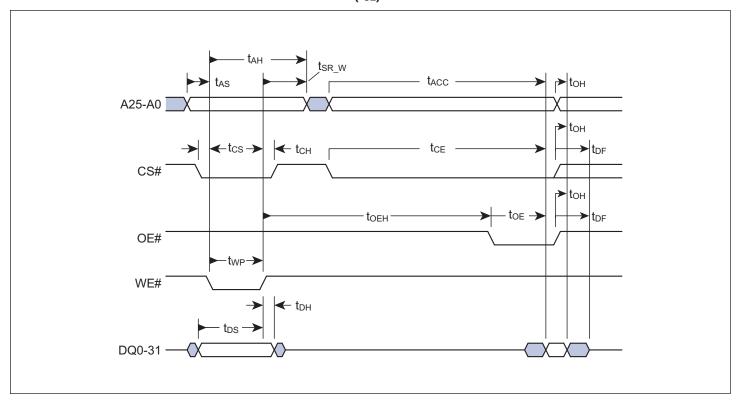

#### FIGURE 5 – AC WAVEFORMS FOR READ OPERATIONS

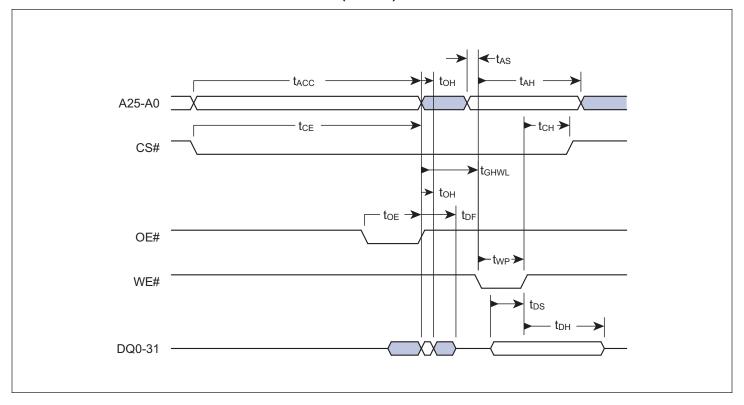

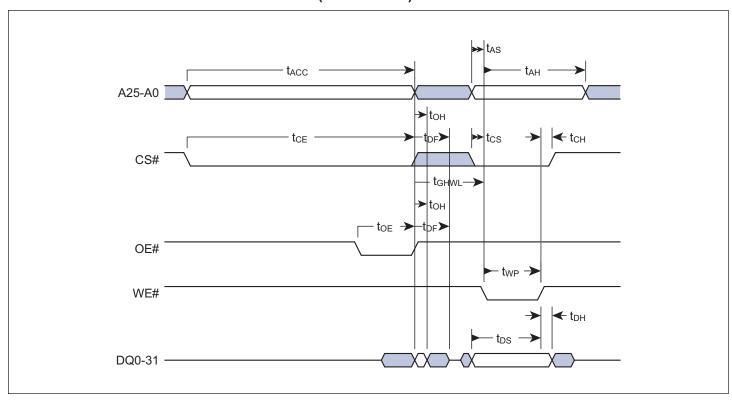

#### FIGURE 6 - PAGE READ TIMING

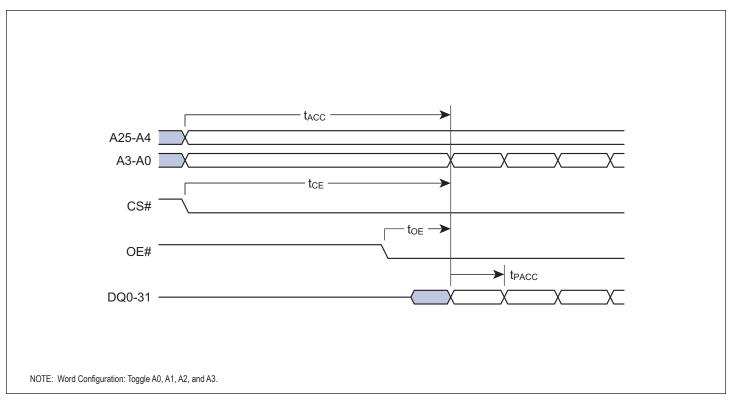

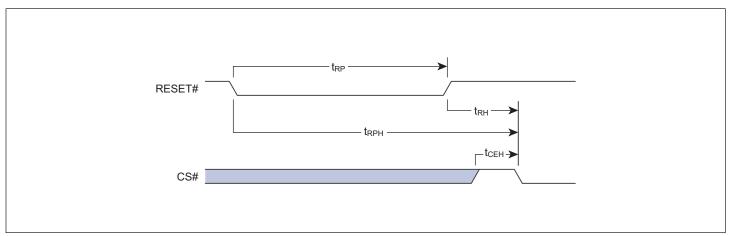

#### **POWER ON AND RESET PARAMETERS**

| Parameter       | Description                                       | Limit | Value | Unit |

|-----------------|---------------------------------------------------|-------|-------|------|

| tvcs            | Vcc Setup Time to first access (1, 2)             | Min   | 300   | μs   |

| tvios           | V <sub>IO</sub> Setup Time to first access (1, 2) | Min   | 300   | μs   |

| trpн            | RESET# Low to CS# Low (1, 2)                      | Min   | 35    | μs   |

| t <sub>RP</sub> | RESET# Pulse Width                                | Min   | 200   | ns   |

| t <sub>RH</sub> | Time between RESET# (High) and CS# (low) (1)      | Min   | 50    | ns   |

| tсен            | CS# Pulse Width High (1)                          | Min   | 20    | ns   |

#### NOTES:

- 1. Not tested.

- 2. Timing measured from  $V_{CC}$  reaching  $V_{CC}$  minimum and  $V_{IO}$  reaching  $V_{IO}$  minimum to  $V_{IH}$  on Reset and  $V_{IL}$  on CS#.

- 3. RESET# Low is optional during POR. If RESET is asserted during POR, the later of treh, trios, or tycs will determine when CS# may go Low. If RESET# remains Low after trios, or tycs is satisfied, treh is measured from the end of trios, or tycs. RESET must also be High treh before CS# goes Low.

- 4.  $V_{CC} \ge V_{IO}$  200 mV during power-up.

- 5. Vcc and Vio ramp rate can be non-linear.

- 6. Sum of  $t_{RP}$  and  $t_{RH}$  must be equal to or greater than  $t_{RPH}$ .

#### FIGURE 7 - POWER-UP DIAGRAM

## FIGURE 8 - HARDWARE RESET

FIGURE 9 - BACK TO BACK WRITE OPERATION TIMING DIAGRAM

FIGURE 10 - BACK TO BACK (CS#VIL) WRITE OPERATION TIMING DIAGRAM

FIGURE 11 – WRITE TO READ (t<sub>ACC</sub>) OPERATION TIMING DIAGRAM

FIGURE 12 - WRITE TO READ (tce) OPERATION TIMING DIAGRAM

FIGURE 13 - READ TO WRITE (CS# VIL) OPERATION TIMING DIAGRAM

FIGURE 14 - READ TO WRITE (CS# TOGGLE) OPERATION TIMING DIAGRAM

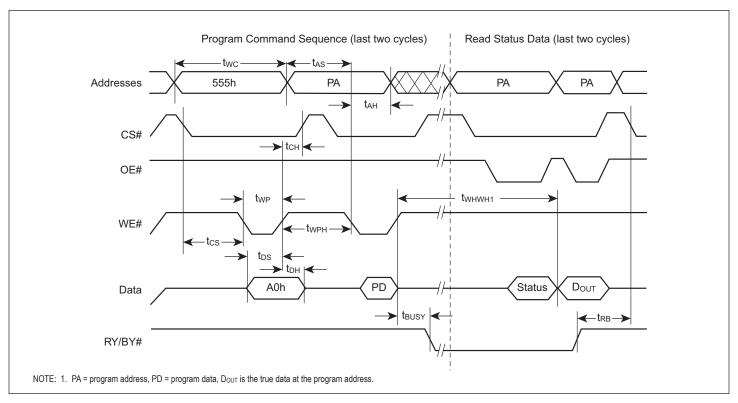

#### **FIGURE 15 – PROGRAM OPERATIONS**

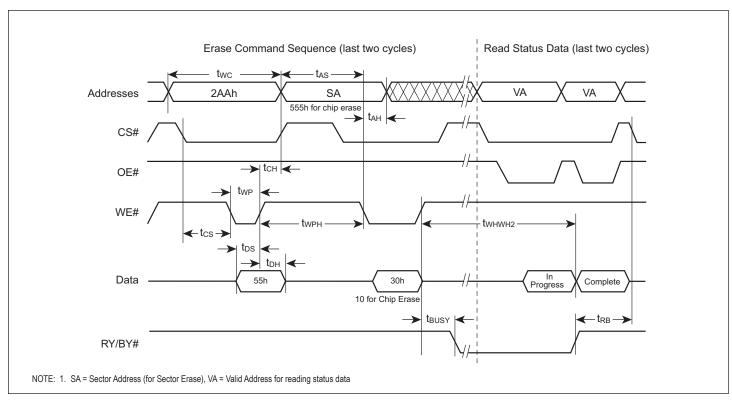

#### FIGURE 16 - CHIP/SECTOR ERASE OPERATION TIMINGS

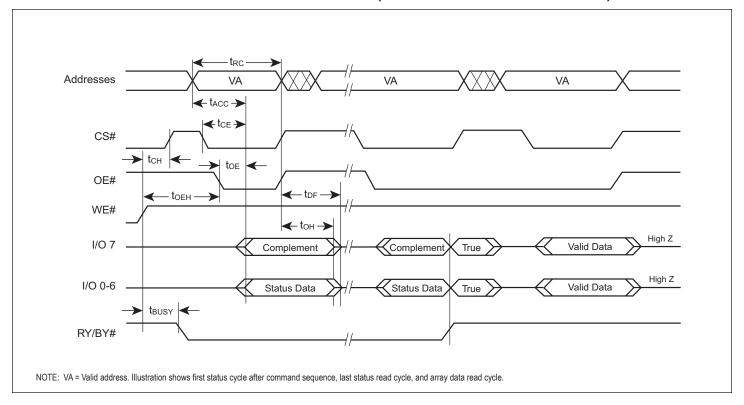

FIGURE 17 – DATA POLLING TIMINGS (DURING EMBEDDED ALGORITHMS)

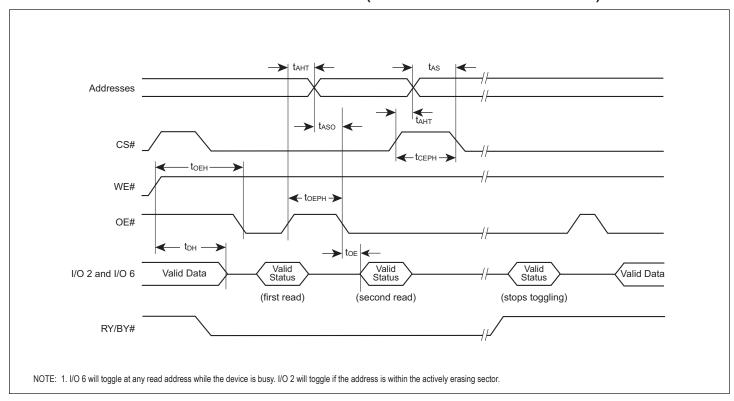

FIGURE 18 - TOGGLE BIT TIMINGS (DURING EMBEDDED ALGORITHMS)

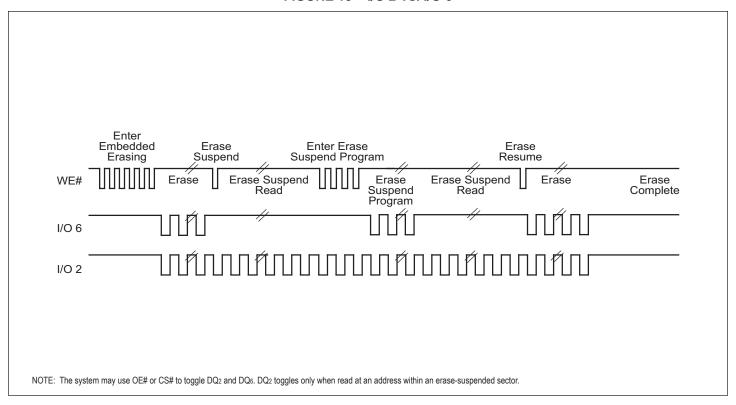

#### FIGURE 19 - I/O 2 Vs. I/O 6

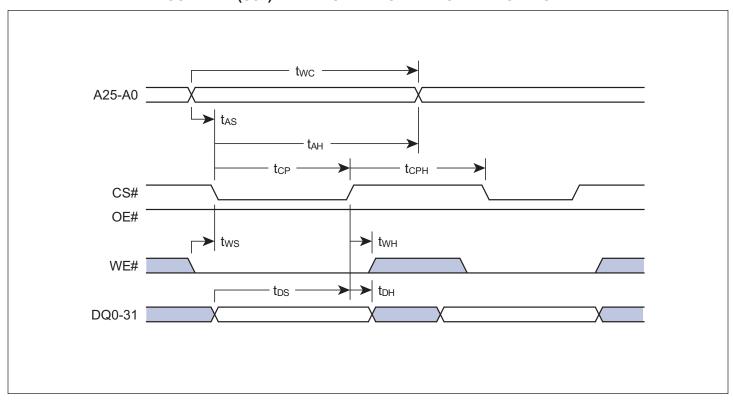

#### AC CHARACTERISTICS – ALTERNATE CS# CONTROLLED ERASE AND PROGRAM OPERATIONS

| Parameter          |                    |                                                                  |     | Speed | Options |      |

|--------------------|--------------------|------------------------------------------------------------------|-----|-------|---------|------|

| JEDEC              | Std                | Description                                                      |     | 110   | 120     | Unit |

| tavav              | twc                | Write Cycle Time                                                 | Min | 60    | 60      | ns   |

| tavwl              | tas                | Address Setup Time                                               | Min | 0     | 0       | ns   |

| telax              | tан                | Address Hold Time                                                | Min | 45    | 45      | ns   |

|                    | taht               | Address Hold Time From CS# or OE# High during toggle bit polling | Min | 0     | 0       | ns   |

| t <sub>DVEH</sub>  | t <sub>DS</sub>    | Data Setup Time                                                  | Min | 30    | 30      | ns   |

| t <sub>EHDX</sub>  | t <sub>DH</sub>    | Data Hold Time                                                   | Min | 0     | 0       | ns   |

|                    | t <sub>CEPH</sub>  | CS# High during toggle bit polling (1)                           | Min | 20    | 20      | ns   |

|                    | toeph              | OE# High during toggle bit polling (1)                           | Min | 20    | 20      | ns   |

| tghel              | tghel              | Read Recovery Time Before Write (OE# High to WE# Low) (1)        | Min | 0     | 0       | ns   |

| twlel              | Tws                | WE# Setup Time                                                   | Min | 0     | 0       | ns   |

| tehwh              | twн                | WE# Hold Time                                                    | Min | 0     | 0       | ns   |

| teleh              | tcp                | CS# Pulse Width                                                  | Min | 25    | 25      | ns   |

| tehel              | tсрн               | CS# Pulse Width High                                             | Min | 20    | 20      | ns   |

| twhwh1             | twhwh1             | Buffer Programming Time                                          | Тур | 180   | 180     | μs   |

| t <sub>WHWH2</sub> | t <sub>WHWH2</sub> | Sector Erase Operation                                           | Тур | 0.3   | 0.3     | sec  |

NOTE: 1. Not tested.

FIGURE 20 – BACK TO BACK (CS#) WRITE OPERATION TIMING DIAGRAM

FIGURE 21 – (CS#) WRITE TO READ OPERATION TIMING DIAGRAM

## W7264M32V1 (512MB) - 107 PBGA (PLASTIC BALL GRID ARRAY)

## W7464M32V1 (1GB) - 107 PBGA (PLASTIC BALL GRID ARRAY)

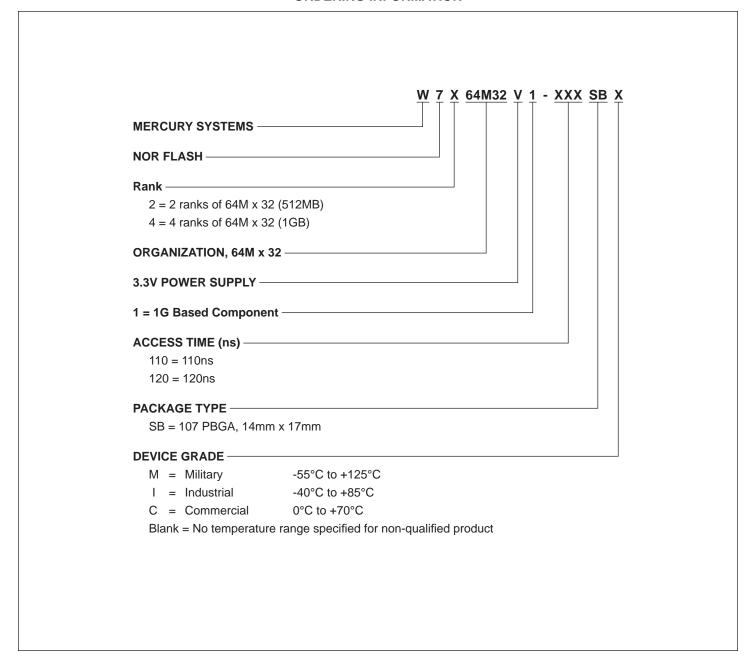

#### **ORDERING INFORMATION**

## **Document Title**

512MB (2 x 64M x 32) / 1GB (4 x 64M x 32) NOR Flash Multi-Chip Package 3V Page Mode Memory

# **Revision History**

| Rev#  | History                                                      | Release Date  | Status      |

|-------|--------------------------------------------------------------|---------------|-------------|

| Rev 0 | Initial Release                                              | December 2012 | Advanced    |

| Rev 1 | Changes (Pgs. 1, 5, 6, 7, 9, 15, 19)                         | December 2013 | Preliminary |

|       | 1.1 Add V <sub>IO</sub> for 1.8V operations                  |               |             |

|       | 1.2 Misc. updates and timings                                |               |             |

|       | 1.3 Change data sheet status to Preliminary                  |               |             |

| Rev 2 | Changes (Pgs. 1, 5, 6, 7, 9, 15, 19)                         | November 2014 | Final       |

|       | 2.1 Remove marking code                                      |               |             |

|       | 2.2 Update DC characteristics table for Icc4 and Icc6        |               |             |

|       | 2.3 Remove marking code from footprint                       |               |             |

|       | 2.4 Remove ES from Access Time list in Ordering Information  |               |             |

|       | 2.5 Change data sheet status to Final                        |               |             |

| Rev 3 | Change (Pg 1)                                                | June 2015     | Final       |

|       | 3.1 Correct data sheet status note on page 1                 |               |             |

| Rev 4 | Change (Pg 5) (ECN #9628)                                    | October 2015  | Final       |

|       | 4.1 Update JB and JC                                         |               |             |

| Rev 5 | Changes (Pg. All) (ECN 10156)                                | August 2016   | Final       |

|       | 5.1 Change document layout from Microsemi to Mercury Systems |               |             |

| Rev 6 | Changes (Pg. All) (ECN 10957)                                | July 2018     | Final       |

|       | 6.1 Update data sheet with new Mercury logo                  |               |             |