# **MIC7401**

# **Configurable Power Management Device for Low-Power FPGA, ASICs, and Processors**

## Features

- Input Voltage: 2.4V to 5.5V

- Five Independent Synchronous Bucks up to 3A

- One Independent Non-Synchronous Boost 200 mA

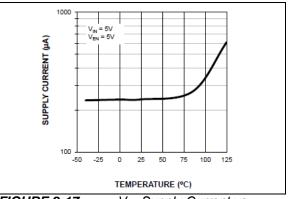

- 200 µA Quiescent Current (All Regulators On)

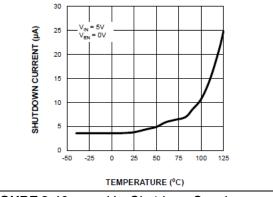

- 5 µA Typical Shutdown Current

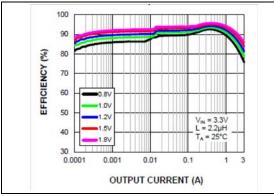

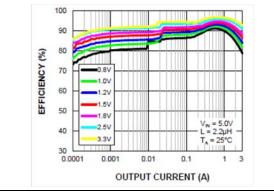

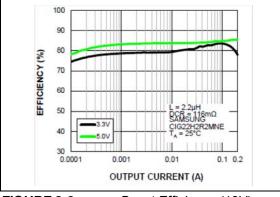

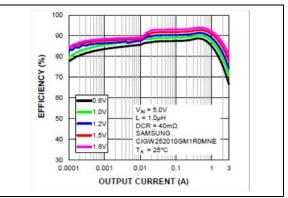

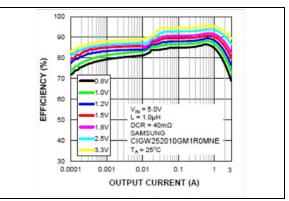

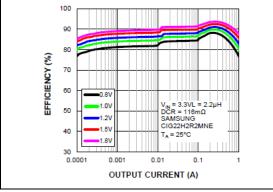

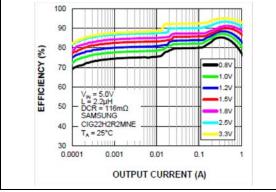

- 93% Peak Buck Efficiency, 85% Typical Efficiency at 1 mA

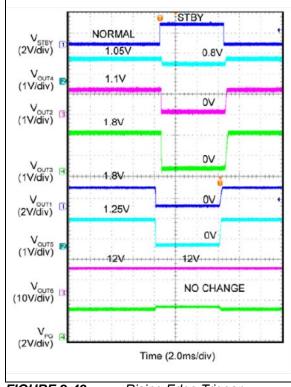

- · Dual Power Modes: Standby and Normal Mode

- I<sup>2</sup>C Interface up to 3.4 MHz

- I<sup>2</sup>C On-the-Fly EEPROM Programmability, Featuring:

- Buck and Boost Output Voltage Scaling

- Power-on-Reset Threshold and Delay

- Power-Up Sequencing/Sequencing Delay

- Buck and Boost Current-Limit

- Buck and Boost Pull-Down when Disabled

- Individual ON, OFF, and Standby Modes

- Soft-Start and Global Power Good Masking

- · 23 µA Buck Typical Quiescent Current

- 70 µA Boost Typical Quiescent Current

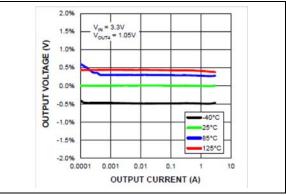

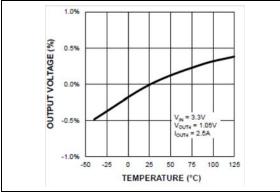

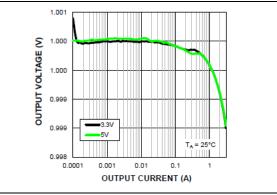

- 1.5% Output Accuracy over Temperature/Line/Load

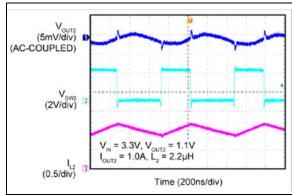

- 2.0 MHz Boost Switching Frequency

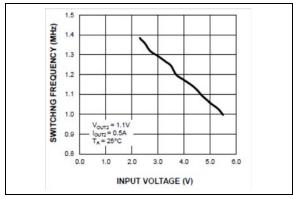

- 1.3 MHz Buck Operation in Continuous Mode

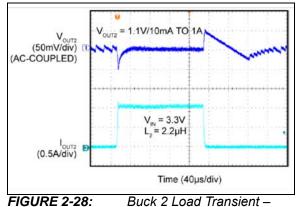

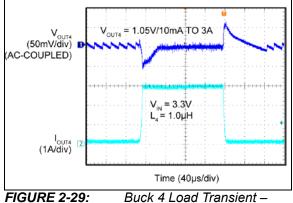

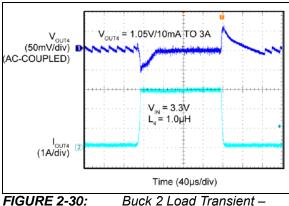

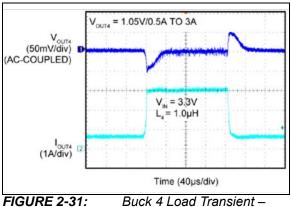

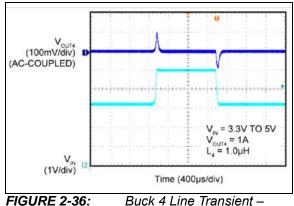

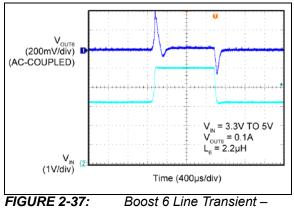

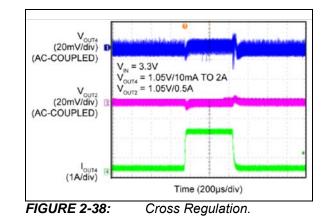

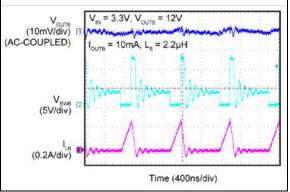

- Ultra-Fast Buck Transient Response

- 12 mm x 8.55 mm x 1.25 mm Solution Size (Top Layer)

- Thermal Shutdown and Current-Limit Protection

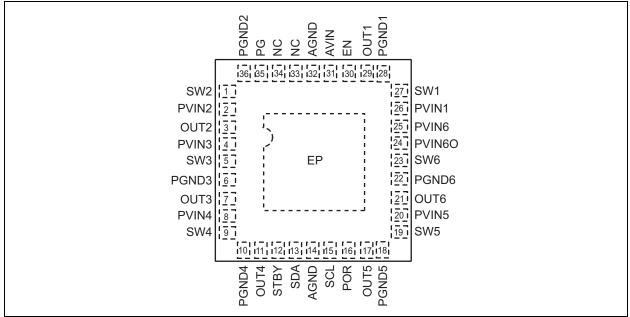

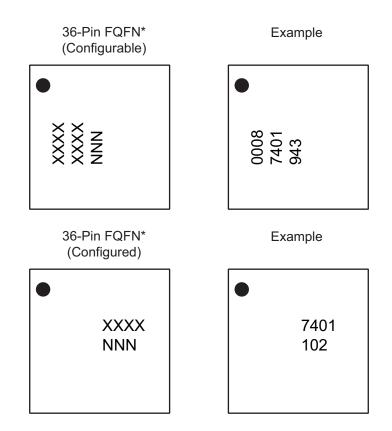

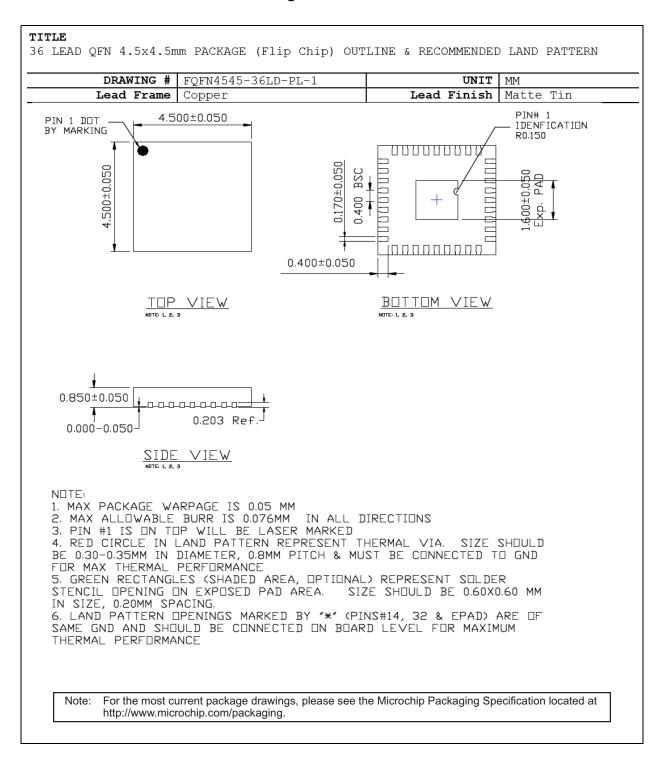

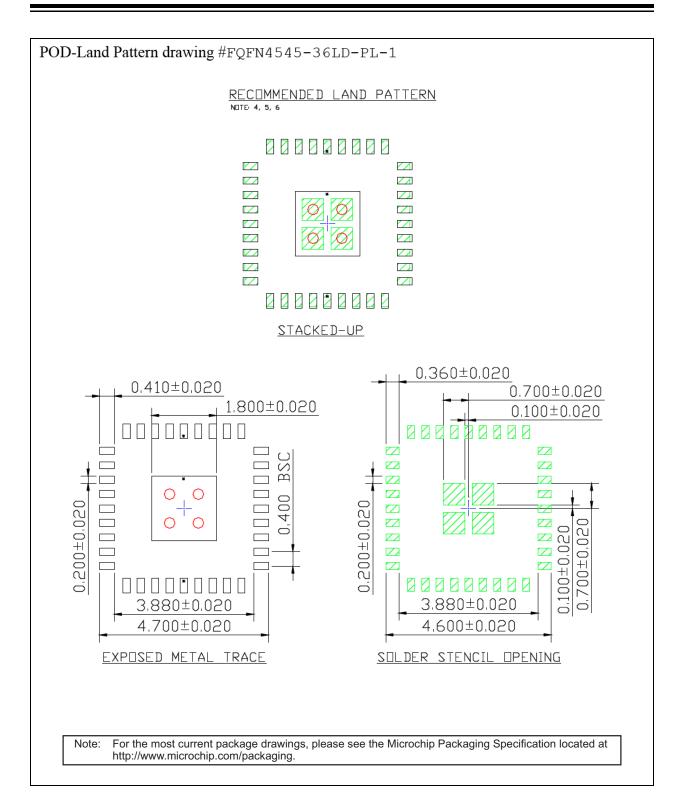

- 36-Pin 4.5 mm x 4.5 mm x 0.85 mm FQFN Package (0.4 mm Pitch)

- -40°C to +125°C Junction Temperature Range

## Applications

- Point-of-Sale (POS)

- Servers

- Network Systems

- 3D Glasses

- Infotainment

## **General Description**

The MIC7401 is a powerful, highly-integrated, configurable, power-management IC (PMIC) featuring five synchronous buck regulators, one boost regulator, and high-speed  $I^2C$  interface with an internal EEPROM.

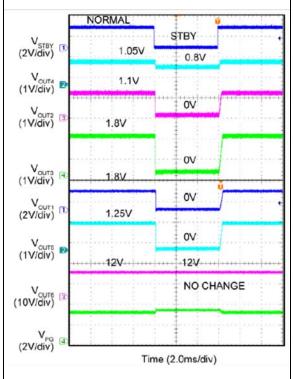

The device offers two distinct modes of operation, Standby mode and Normal mode, intended to provide an energy optimized solution suitable for portable hand-held and infotainment applications.

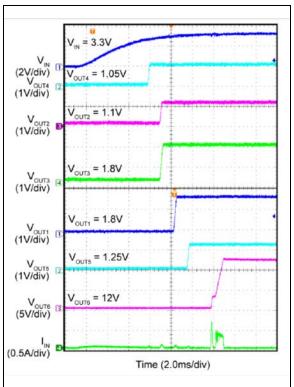

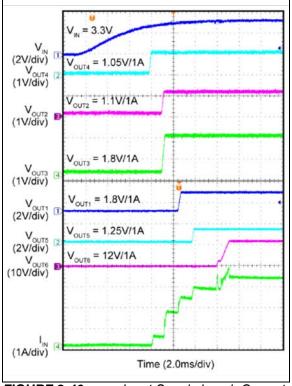

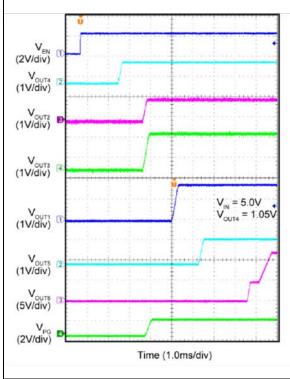

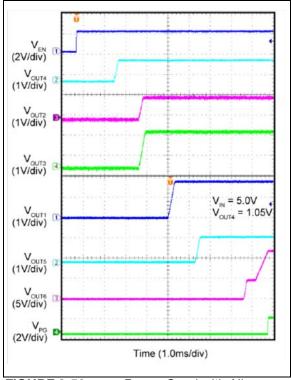

In Normal mode, the programmable switching converters can be configured to support a variety of features, including start-up sequencing, timing, soft-start ramp, output voltage levels, current-limit levels, and output discharge for each channel.

In Standby mode, the PMIC can be configured in a low power state by either disabling an output or by changing the output voltage to a lower level. Independent exit from Standby mode can be achieved either by I<sup>2</sup>C communication or the external STBY pin.

The device has five synchronous buck regulators with high-speed adaptive on-time control supporting even the challenging ultra-fast transient requirement for core supplies. The one boost regulator provides a Flash memory programming supply that delivers up to 200 mA of output current. The boost is equipped with an output disconnect switch that opens if a short-to-ground fault is detected.

An internal EEPROM enables a single-chip solution across many platforms by allowing the designer to customize the PMIC for their design. Modifications can be made without the need to re-approve a new PMIC, saving valuable design resources and time.

All switchers provide light-load efficiency with HyperLight Load<sup>®</sup> mode for buck and PFM mode for boost. An additional benefit of this proprietary architecture is very low output ripple voltage throughout the entire load range with the use of small output capacitors. The MIC7401 is designed for use with small inductors (down to 0.47  $\mu$ H for buck, 1.5  $\mu$ H for boost), and an output capacitor as small as 10  $\mu$ F for buck, enabling a total solution size of 12 mm × 8.5 mm and less than 1 mm height on top layer.

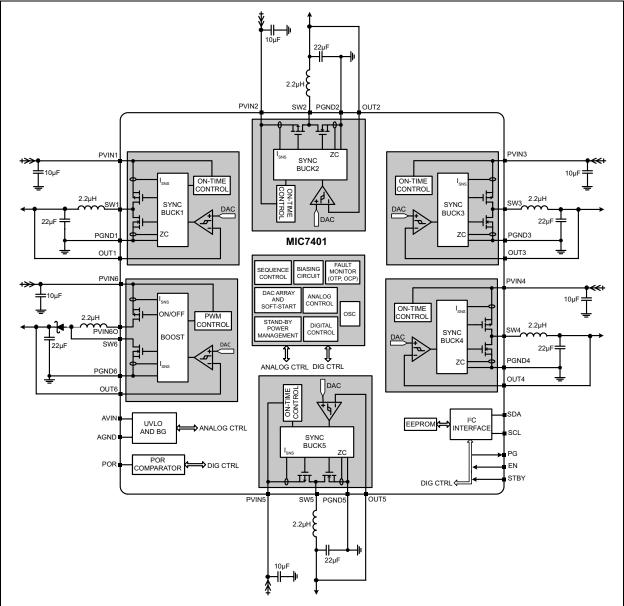

## **Typical Application Circuit**

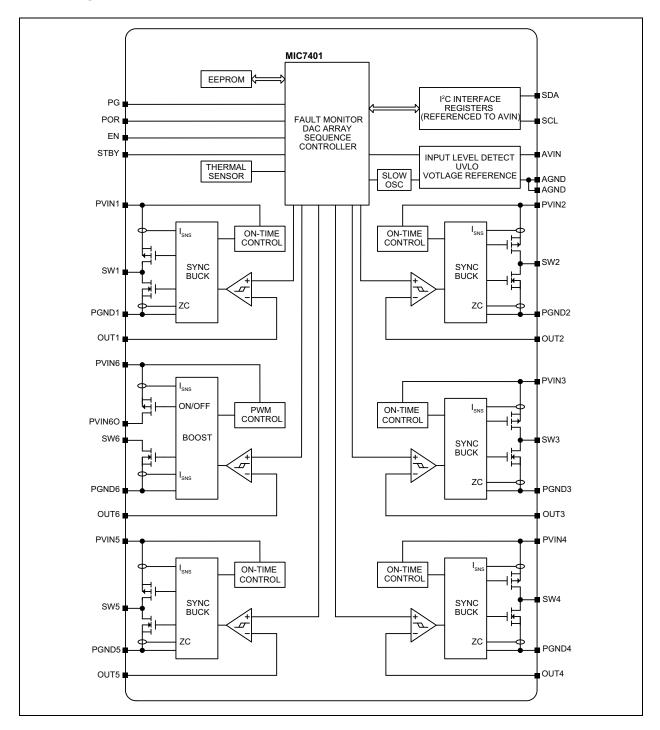

## **Block Diagram**

<sup>© 2018</sup> Microchip Technology Inc.

# 1.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings †

| Supply Voltages (PV <sub>IN[1-6]</sub> )                   | –0.3V to +6V              |

|------------------------------------------------------------|---------------------------|

| Analog Supply Voltage (AVIN)                               | –0.3V to +6V              |

| Buck Output Voltages (V <sub>OUT[1-5]</sub> )              | –0.3V to +6V              |

| Boost Output Voltage (V <sub>OUT6</sub> )                  |                           |

| Buck Switch Voltages (V <sub>SW[1-5]</sub> )               | –0.3V to +6V              |

| Boost Switch Voltage (V <sub>SW6</sub> )                   | –0.3V to +20V             |

| Power Good Voltage (V <sub>PG</sub> )                      | –0.3V to AV <sub>IN</sub> |

| Power-On Reset Output (V <sub>POR</sub> )                  | –0.3V to +6V              |

| Enable Voltage (V <sub>EN</sub> )                          | –0.3V to +6V              |

| Standby Voltage (V <sub>STBY</sub> )                       | –0.3V to +6V              |

| I <sup>2</sup> C IO (V <sub>SDA</sub> , V <sub>SCL</sub> ) | –0.3V to AV <sub>IN</sub> |

| AGND to PGND[1-6]                                          |                           |

| ESD Rating (Note 1)                                        | HBM: 2 kV; MM: 200V       |

## **Operating Ratings ‡**

| Input Voltage (PV <sub>IN[1-6]</sub> )                     | +2.4V to +5.5V         |

|------------------------------------------------------------|------------------------|

| Analog Input Voltage (AVIN)                                |                        |

| Buck Output Voltage Range (V <sub>OUT[1-5]</sub> )         | +0.8V to +3.3V         |

| Boost Output Voltage Range (V <sub>OUT6</sub> )            |                        |

| Power Good Voltage (V <sub>PG</sub> )                      | 0V to AV <sub>IN</sub> |

| Power-On Reset Output (V <sub>POR</sub> )                  | 0V to AV <sub>IN</sub> |

| POR Threshold Voltage (V <sub>VSLT</sub> )                 | 0V to AV <sub>IN</sub> |

| Standby Voltage (V <sub>STBY</sub> )                       | 0V to AV <sub>IN</sub> |

| I <sup>2</sup> C IO (V <sub>SDA</sub> , V <sub>SCL</sub> ) |                        |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability. Specifications are for packaged product only.

**‡ Notice:** The device is not guaranteed to function outside its operating ratings.

Note 1: Devices are ESD sensitive. Handling precautions are recommended. Human body model,  $1.5 \text{ k}\Omega$  in series with 100 pF.

## TABLE 1-1: ELECTRICAL CHARACTERISTICS

**Electrical Characteristics:**  $V_{IN} = AV_{IN} = PV_{IN(1-6)} = 5.0V$ ;  $V_{OUT1} = 1.8V$ ;  $V_{OUT2} = 1.1V$ ;  $V_{OUT3} = 1.8V$ ;  $V_{OUT4} = 1.05V$ ;  $V_{OUT5} = 1.25V$ ;  $V_{OUT6} = 12V$ .  $T_A = +25^{\circ}C$ , unless otherwise noted. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Note 1

| Parameter                                                             | Min.  | Тур. | Max.  | Units             | Conditions                                    |  |

|-----------------------------------------------------------------------|-------|------|-------|-------------------|-----------------------------------------------|--|

| Input Supply (V <sub>IN</sub> )                                       |       | •    | •     | •                 | ·                                             |  |

| Input Voltage Range (AV <sub>IN</sub> , PV <sub>IN[1-6]</sub> )       | 2.4   |      | 5.5   | V                 | —                                             |  |

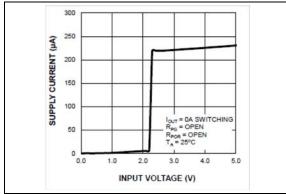

| Operating Quiescent Current into AV <sub>IN</sub><br>(Note 2, Note 3) | _     | 200  | 240   | μA                | V <sub>IN</sub> = 5.0V; I <sub>OUT</sub> = 0A |  |

| Operating Quiescent Current into PV <sub>IN</sub> (Note 2)            | _     | 0.3  | 1.0   | μA                | V <sub>IN</sub> = 5.0V; I <sub>OUT</sub> = 0A |  |

| Shutdown Current into (PV <sub>IN</sub> + AV <sub>IN</sub> )          | —     | 5    | —     | μA                | V <sub>IN</sub> = 5.0V; V <sub>EN</sub> = 0V  |  |

| Undervoltage Lockout Threshold                                        | 2.15  | 2.25 | 2.35  | V                 | AV <sub>IN</sub> Rising                       |  |

| Undervoltage Lockout Hysteresis                                       | —     | 150  | —     | mV                | —                                             |  |

| Standby Input (STBY)                                                  |       |      |       |                   |                                               |  |

| Logic Level High                                                      | 1.2   |      | _     | V                 | —                                             |  |

| Logic Level Low                                                       | —     | _    | 0.4   | V                 | —                                             |  |

| Bias Current into Pin                                                 | _     |      | 200   | nA                | V <sub>STBY</sub> = V <sub>IN</sub>           |  |

| Bias Current out of Pin                                               | _     |      | 200   | nA                | V <sub>STBY</sub> = 0V                        |  |

| Rising/Falling Edge Reset Deglitch                                    | _     | 100  | _     | μs                | —                                             |  |

| Enable Input (EN)                                                     |       |      | •     |                   | •                                             |  |

| Logic Level High                                                      | 1.2   |      | _     | V                 | V <sub>EN</sub> Rising, Regulator Enabled     |  |

| Logic Level Low                                                       | _     |      | 0.4   | V                 | V <sub>EN</sub> Falling, Regulator Shutdown   |  |

| Bias Current Into Pin                                                 | _     |      | 200   | nA                | V <sub>VSLT</sub> = V <sub>IN</sub>           |  |

| Bias Current Out of Pin                                               | _     |      | 200   | nA                | V <sub>VSLT</sub> = 0V                        |  |

| Power-On-Reset (POR) Comparator                                       | •     |      | •     |                   | •                                             |  |

| POR Upper Comparator Range                                            | 2.646 | 2.7  | 2.754 | V                 | AV <sub>IN</sub> Rising                       |  |

| POR Lower Comparator Range                                            | 2.548 | 2.6  | 2.652 | V                 | AV <sub>IN</sub> Falling                      |  |

| Power Reset Output (POR) and Timer                                    | •     |      | •     |                   | •                                             |  |

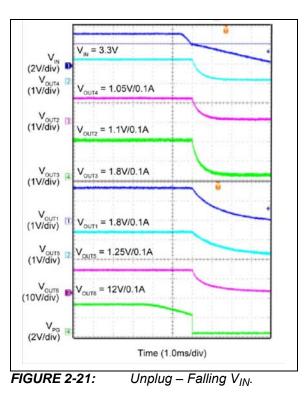

| POR Delay                                                             | 18    | 20   | 22    | ms                | —                                             |  |

| POR Deglitch Delay                                                    |       | 50   | _     | μs                | AV <sub>IN</sub> Falling                      |  |

| POR Output Low Voltage                                                | _     | 75   | 400   | mV                | I <sub>POR</sub> = 10 mA (sinking)            |  |

| POR Leakage Current                                                   | _     |      | 200   | nA                | V <sub>POR</sub> = 5.5V                       |  |

| Global Power Good Output (PG)                                         |       |      | •     |                   | •                                             |  |

| Buck Power Good Threshold Voltage                                     | 87    | 91   | 95    | %V <sub>OUT</sub> | V <sub>OUT[1-5]</sub> Rising                  |  |

| Buck Hysteresis (Note 4)                                              | _     | 4    | _     |                   | V <sub>OUT[1-5]</sub> Falling                 |  |

| Boost Power Good Threshold Voltage                                    | 87    | 91   | 95    | %V <sub>OUT</sub> | V <sub>OUT[6]</sub> Rising                    |  |

| Boost Hysteresis (Note 4)                                             | _     | 380  | _     | mV                | V <sub>OUT[6]</sub> Falling                   |  |

| Power Good Output Low Voltage                                         | _     | 75   | 400   | mV                | I <sub>PG</sub> = 10 mA (sinking)             |  |

| Power Good Leakage Current                                            | —     | 0.01 | 200   | nA                | V <sub>PG</sub> = 5.5V                        |  |

| Power Good Deglitch Delay                                             |       | 100  | _     | μs                | V <sub>OUT[1-6]</sub> Falling                 |  |

| Output Sequencing Delay (Note 4)                                      | 0.96  | 1    | 1.04  | ms                |                                               |  |

| Thermal Protection                                                    |       |      |       |                   |                                               |  |

| Thermal Shutdown                                                      | _     | 160  | _     | °C                | T <sub>J</sub> Rising                         |  |

| Thermal Hysteresis                                                    |       | 20   |       | °C                | —                                             |  |

<sup>© 2018</sup> Microchip Technology Inc.

## TABLE 1-1: ELECTRICAL CHARACTERISTICS (CONTINUED)

**Electrical Characteristics:**  $V_{IN} = AV_{IN} = PV_{IN(1-6)} = 5.0V$ ;  $V_{OUT1} = 1.8V$ ;  $V_{OUT2} = 1.1V$ ;  $V_{OUT3} = 1.8V$ ;  $V_{OUT4} = 1.05V$ ;  $V_{OUT5} = 1.25V$ ;  $V_{OUT6} = 12V$ .  $T_A = +25^{\circ}C$ , unless otherwise noted. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Note 1

| Buck Output Voltage Accuracy (OUT[1-5])Typical Output Voltage 1 Accuracy<br>(Note 5)-1.5-1.5%Includes Load, Line, and Reference<br>(Note 5)Typical Output Voltage 2 Accuracy<br>(Note 5)-1.5-1.5%Includes Load, Line, and Reference<br>(Note 5)Typical Output Voltage 3 Accuracy<br>(Note 5)-1.5-1.5%Includes Load, Line, and Reference<br>(Note 5)Typical Output Voltage 4 Accuracy<br>(Note 5)-1.5-1.5%Includes Load, Line, and Reference<br>(Note 5)Output Voltage 4 Accuracy<br>(Note 5)-1.5-1.5%Includes Load, Line, and Reference<br>(Note 5)Output Voltage 1 Accuracy (Note 5)-1-1%-Output Voltage 4 Accuracy (Note 5)-1-1%-Output Voltage 5 Accuracy (Note 5)-1-1%-Output Voltage 4 Accuracy (Note 5)-1-1%-Dutput Voltage 5 Accuracy (Note 5)-1-1%-Dutput Voltage 4 Accuracy (Note 5)-1-1%-Dutput Voltage 5 Accuracy (Note 5)-1-1%-Buck Statt-0.05-%V_IN = 3.3V to 5.0VBuck Statt <th>Parameter</th> <th>Min.</th> <th>Тур.</th> <th>Max.</th> <th>Units</th> <th>Conditions</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Parameter                                                 | Min.  | Тур. | Max.  | Units   | Conditions                                                              |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------|------|-------|---------|-------------------------------------------------------------------------|--|--|

| Typical Output Voltage 1 Accuracy         -1.5         -         1.5         %         Includes Load, Line, and Reference           Typical Output Voltage 2 Accuracy         -1.5         -         1.5         %         Includes Load, Line, and Reference           Typical Output Voltage 3 Accuracy         -1.5         -         1.5         %         Includes Load, Line, and Reference           Typical Output Voltage 4 Accuracy         -1.5         -         1.5         %         Includes Load, Line, and Reference           Typical Output Voltage 5 Accuracy         -1.5         -         1.5         %         Includes Load, Line, and Reference           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Output Voltage 4 Accuracy (Note 5)         -1         -         1         %         -           Dutpu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Synchronous Buck (V <sub>OUT1</sub> - V <sub>OUT5</sub> ) |       | •    | •     | •       | ·                                                                       |  |  |

| $ \begin{array}{c} (\text{Note 5}) & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -1.3 & -$ | Buck Output Voltage Accuracy (OUT[1-5])                   |       |      |       |         |                                                                         |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Typical Output Voltage 1 Accuracy (Note 5)                | -1.5  | —    | 1.5   | %       | Includes Load, Line, and Reference                                      |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Typical Output Voltage 2 Accuracy (Note 5)                | -1.5  | —    | 1.5   | %       | Includes Load, Line, and Reference                                      |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Typical Output Voltage 3 Accuracy (Note 5)                | -1.5  | _    | 1.5   | %       | Includes Load, Line, and Reference                                      |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Typical Output Voltage 4 Accuracy (Note 5)                | -1.5  | _    | 1.5   | %       | Includes Load, Line, and Reference                                      |  |  |

| Output Voltage 2 Accuracy (Note 5)         -1         -1         %            Output Voltage 3 Accuracy (Note 5)         -1         -1         %            Output Voltage 4 Accuracy (Note 5)         -1         -1         %            Output Voltage 5 Accuracy (Note 5)         -1         -1         %            Output Voltage 5 Accuracy (Note 5)         -1         -1         %            Load Regulation         -         0.1         -         %         IouT = 10 mA to IoUT(MAX)           Line Regulation         -         0.05         -         %         VIN = 3.3V to 5.0V           Buck Soft-Start         -         0.05         -         %         VIN = 3.3V; ISW[1-5] = 200 mA           High-Side On-Resistance         -         54         -         mΩ         VIN = 5.0V; ISW[1-5] = 200 mA           Low-Side On-Resistance         -         37         -         mΩ         VIN = 5.0V; ISW[1-5] = -200 mA           Low-Side On-Resistance         -         30         -         mΩ         VIN = 5.0V; ISW[1-5] = -200 mA           Low-Side On-Resistance         -         30         -         mΩ         VIN = 5.0V; ISW[1-5] = -200 mA           Low-Side On-Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Typical Output Voltage 5 Accuracy (Note 5)                | -1.5  | _    | 1.5   | %       | Includes Load, Line, and Reference                                      |  |  |

| Output Voltage 3 Accuracy (Note 5)-1-1%-Output Voltage 4 Accuracy (Note 5)-1-1%-Output Voltage 5 Accuracy (Note 5)-1-1%-Load Regulation-0.1-% $I_{OUT} = 10 \text{ mA to } I_{OUT}(MAX)$ Line Regulation-0.05-% $V_{IN} = 3.3V \text{ to } 5.0V$ Buck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu s/step$ -Buck Internal MOSFETSHigh-Side On-Resistance-54-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mnQ $V_{IN} = 5.0V; I_{SW$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output Voltage 1 Accuracy (Note 5)                        | -1    |      | 1     | %       | —                                                                       |  |  |

| Output Voltage 4 Accuracy (Note 5)-1-1%-Output Voltage 5 Accuracy (Note 5)-1-1%-Load Regulation-0.1-% $I_{OUT} = 10 \text{ mA to } I_{OUT(MAX)}$ Line Regulation-0.05-% $V_{IN} = 3.3V \text{ to } 5.0V$ Buck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu \text{s/step}$ -Buck Internal MOSFETSHigh-Side On-Resistance-54-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Time (Note 7)-220-nsV_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}Buck Current-Limit (OUT1 - OUT5)-80<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Output Voltage 2 Accuracy (Note 5)                        | -1    |      | 1     | %       | —                                                                       |  |  |

| Output Voltage 5 Accuracy (Note 5)-1-1%-Load Regulation-0.1-% $I_{OUT} = 10 \text{ mA to } I_{OUT(MAX)}$ Line Regulation-0.05-% $V_{IN} = 3.3V \text{ to } 5.0V$ Buck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu s/step$ -Buck Internal MOSFETSHigh-Side On-Resistance-54-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-40-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller Timing-80-ns-Fixed On-Time (Note 7)-220-nsV_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0VMinimum OFF-Time-80-ns-Buck 1 Current-Limit (OUT1 - OUT5)-nsBuck 2 Current-Limit Threshold3.075                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Output Voltage 3 Accuracy (Note 5)                        | -1    |      | 1     | %       | —                                                                       |  |  |

| Load Regulation0.1% $I_{OUT} = 10 \text{ mA to } I_{OUT(MAX)}$ Line Regulation0.05% $V_{IN} = 3.3V \text{ to } 5.0V$ Buck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu s/step$ Buck Internal MOSFETSHigh-Side On-Resistance54mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance40mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance37mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance30mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance30mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance30mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Ω $V_{SW[1-5]} = 0V$ Buck Controller Timing80nsFixed On-Time (Note 7)220nsV_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0VMinimum OFF-Time80nsBuck 1 Current-Limit (OUT1 - OUT5)Buck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG Settings <t< td=""><td>Output Voltage 4 Accuracy (Note 5)</td><td>-1</td><td>—</td><td>1</td><td>%</td><td>—</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output Voltage 4 Accuracy (Note 5)                        | -1    | —    | 1     | %       | —                                                                       |  |  |

| Line Regulation-0.05-% $V_{IN} = 3.3V$ to 5.0VBuck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu$ s/step-Buck Internal MOSFETSHigh-Side On-Resistance-54-mΩ $V_{IN} = 3.3V$ ; $I_{SW[1-5]} = 200$ mAHigh-Side On-Resistance-40-mΩ $V_{IN} = 5.0V$ ; $I_{SW[1-5]} = 200$ mALow-Side On-Resistance-37-mΩ $V_{IN} = 3.3V$ ; $I_{SW[1-5]} = -200$ mALow-Side On-Resistance-30-mΩ $V_{IN} = 5.0V$ ; $I_{SW[1-5]} = -200$ mALow-Side On-Resistance-30-mΩ $V_{IN} = 5.0V$ ; $I_{SW[1-5]} = -200$ mALow-Side On-Resistance-30-mΩ $V_{IN} = 5.0V$ ; $I_{SW[1-5]} = -200$ mAOutput Pull-Down Resistance7590200Ω $V_{SW[1-5]} = 0V$ Buck Controller Timing-80-ns-Fixed On-Time (Note 7)-220-ns-Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)-80-ns-Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Curre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Output Voltage 5 Accuracy (Note 5)                        | -1    |      | 1     | %       | —                                                                       |  |  |

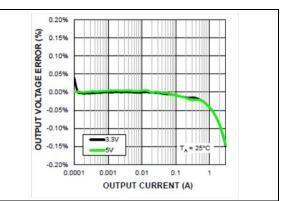

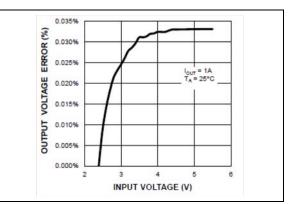

| Buck Soft-StartSoft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu$ s/step—Buck Internal MOSFETSHigh-Side On-Resistance—54—mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ High-Side On-Resistance—40—mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance—37—mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mΩ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Ω $V_{SW[1-5]} = 0V$ Buck Controller Timing——80—nsFixed On-Time (Note 7)—220—ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time—80—ns—Buck 1 Current-Limit (OUT1 - OUT5)Buck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Load Regulation                                           | _     | 0.1  |       | %       | $I_{OUT} = 10 \text{ mA to } I_{OUT(MAX)}$                              |  |  |

| Soft-Start (1-5) LSB (Note 4, Note 6)3.844.04.16 $\mu$ s/step—Buck Internal MOSFETsHigh-Side On-Resistance—54—mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ High-Side On-Resistance—40—mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance—37—mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance—30—mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)—220—ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time—80—ns—Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125A <td>Line Regulation</td> <td>_</td> <td>0.05</td> <td></td> <td>%</td> <td>V<sub>IN</sub> = 3.3V to 5.0V</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Line Regulation                                           | _     | 0.05 |       | %       | V <sub>IN</sub> = 3.3V to 5.0V                                          |  |  |

| Buck Internal MOSFETsHigh-Side On-Resistance-54-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ High-Side On-Resistance-40-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller Timing-80-ns-Fixed On-Time (Note 7)-220-nsV_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0VMinimum OFF-Time-80-ns-Buck 1 Current-Limit (OUT1 - OUT5)Buck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG Settings<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Buck Soft-Start                                           | •     |      |       | •       | •                                                                       |  |  |

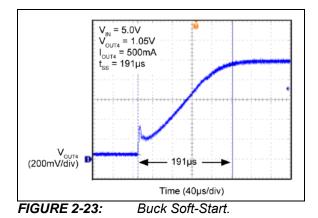

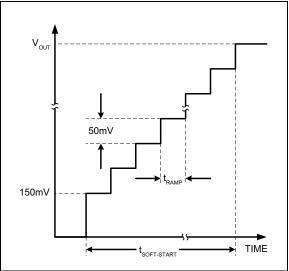

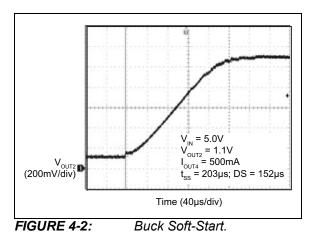

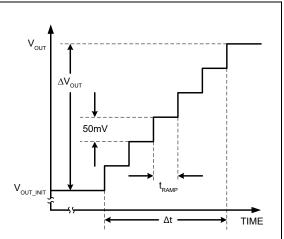

| High-Side On-Resistance-54-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = 200 \text{ mA}$ High-Side On-Resistance-40-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)-220-ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Soft-Start (1-5) LSB (Note 4, Note 6)                     | 3.84  | 4.0  | 4.16  | µs/step | _                                                                       |  |  |

| High-Side On-Resistance40mQ $V_{IN} = 5.0V; I_{SW[1-5]} = 200 \text{ mA}$ Low-Side On-Resistance37mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance30mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)220ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time80nsBuck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125 <t< td=""><td>Buck Internal MOSFETs</td><td></td><td></td><td></td><td></td><td>•</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Buck Internal MOSFETs                                     |       |      |       |         | •                                                                       |  |  |

| Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)-220-ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [X]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-Side On-Resistance                                   | —     | 54   |       | mΩ      | V <sub>IN</sub> = 3.3V; I <sub>SW[1-5]</sub> = 200 mA                   |  |  |

| Low-Side On-Resistance-37-mQ $V_{IN} = 3.3V; I_{SW[1-5]} = -200 \text{ mA}$ Low-Side On-Resistance-30-mQ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Q $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)-220-ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [X]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | High-Side On-Resistance                                   | _     | 40   |       | mΩ      | V <sub>IN</sub> = 5.0V; I <sub>SW[1-5]</sub> = 200 mA                   |  |  |

| Low-Side On-Resistance-30-mΩ $V_{IN} = 5.0V; I_{SW[1-5]} = -200 \text{ mA}$ Output Pull-Down Resistance7590200Ω $V_{SW[1-5]} = 0V$ Buck Controller TimingFixed On-Time (Note 7)-220-ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]- $150$ - $\%$ With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Low-Side On-Resistance                                    | _     | 37   |       | mΩ      |                                                                         |  |  |

| Buck Controller Timing         Fixed On-Time (Note 7)       —       220       —       ns       V <sub>IN</sub> = 3.3; V <sub>OUT</sub> = 1.0V; I <sub>OUT</sub> = 1.0         Minimum OFF-Time       —       80       —       ns       —         Buck Current-Limit (OUT1 - OUT5)         Buck 1 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Buck 2 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Buck 3 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Buck 4 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Buck 5 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Buck 5 Current-Limit Threshold       4.88       6.1       7.32       A       See Table 4-3 for IPROG Settings         Buck 5 Current-Limit Threshold       3.075       4.1       5.125       A       See Table 4-3 for IPROG Settings         Gross High-Side Current-Limit [1-5]       —       150       —       %       With Respect to Buck [x] Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Low-Side On-Resistance                                    | —     | 30   |       | mΩ      |                                                                         |  |  |

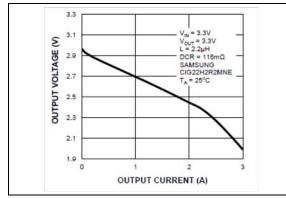

| Fixed On-Time (Note 7)- $220$ -ns $V_{IN} = 3.3; V_{OUT} = 1.0V; I_{OUT} = 1.0V$ Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold $4.88$ $6.1$ $7.32$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold $3.075$ $4.1$ $5.125$ ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]- $150$ -%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Output Pull-Down Resistance                               | 75    | 90   | 200   | Ω       | V <sub>SW[1-5]</sub> = 0V                                               |  |  |

| Minimum OFF-Time-80-ns-Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold4.886.17.32ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Buck Controller Timing                                    |       |      |       |         |                                                                         |  |  |

| Buck Current-Limit (OUT1 - OUT5)Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold4.886.17.32ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fixed On-Time (Note 7)                                    | —     | 220  |       | ns      | V <sub>IN</sub> = 3.3; V <sub>OUT</sub> = 1.0V; I <sub>OUT</sub> = 1.0A |  |  |

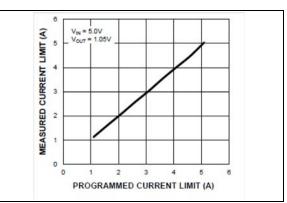

| Buck 1 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold4.886.17.32ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Minimum OFF-Time                                          | _     | 80   |       | ns      | —                                                                       |  |  |

| Buck 2 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold4.886.17.32ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Buck Current-Limit (OUT1 - OUT5)                          |       |      |       |         |                                                                         |  |  |

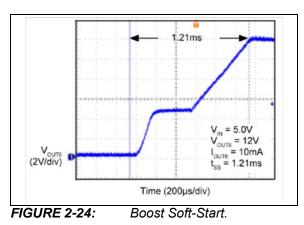

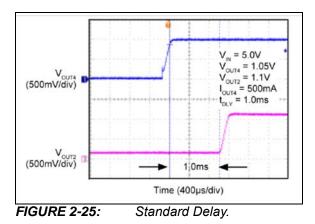

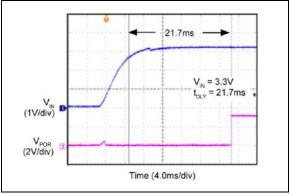

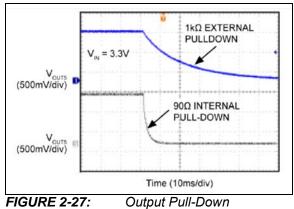

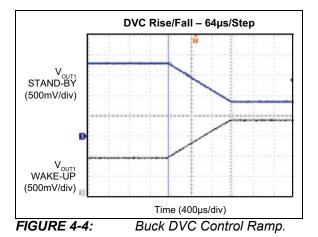

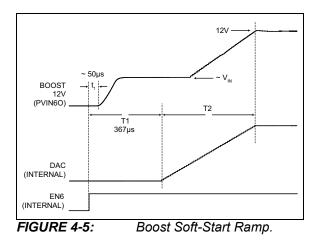

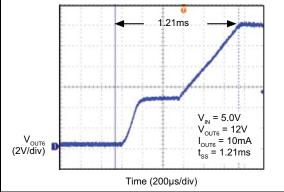

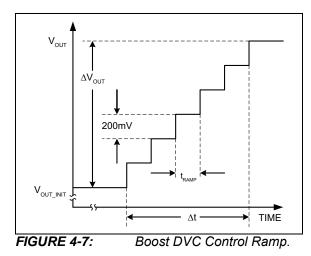

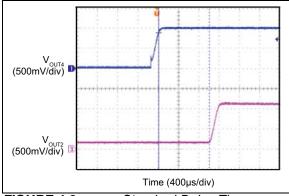

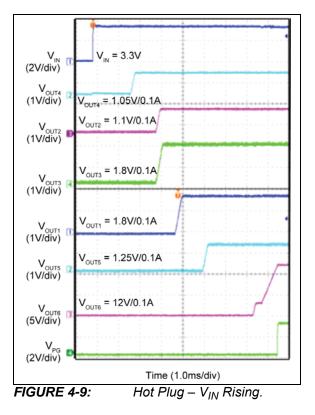

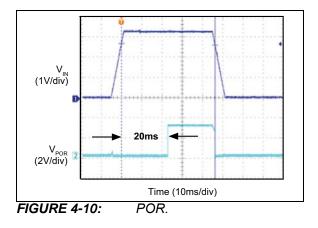

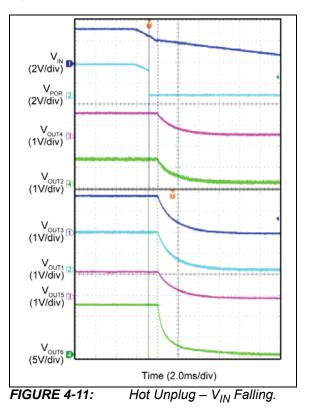

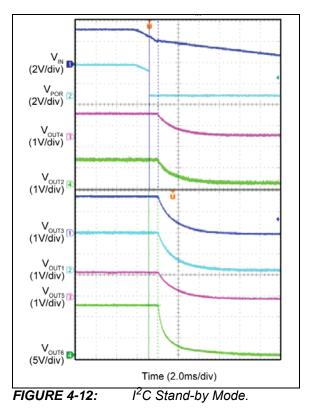

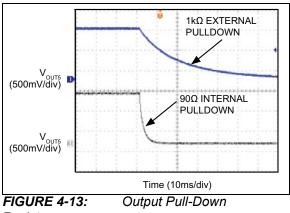

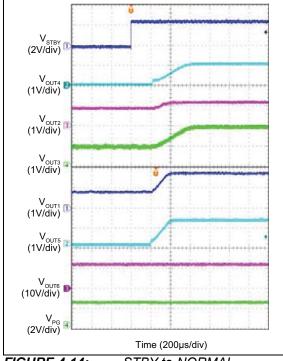

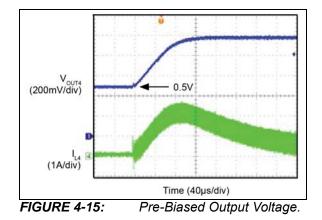

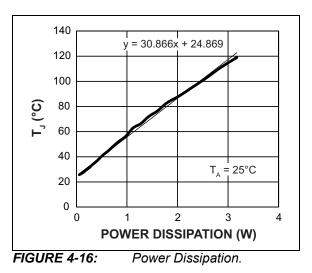

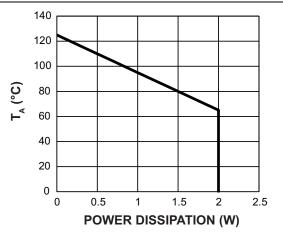

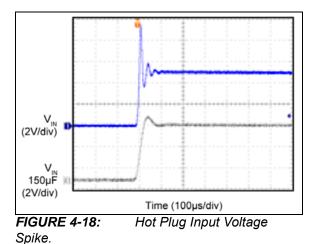

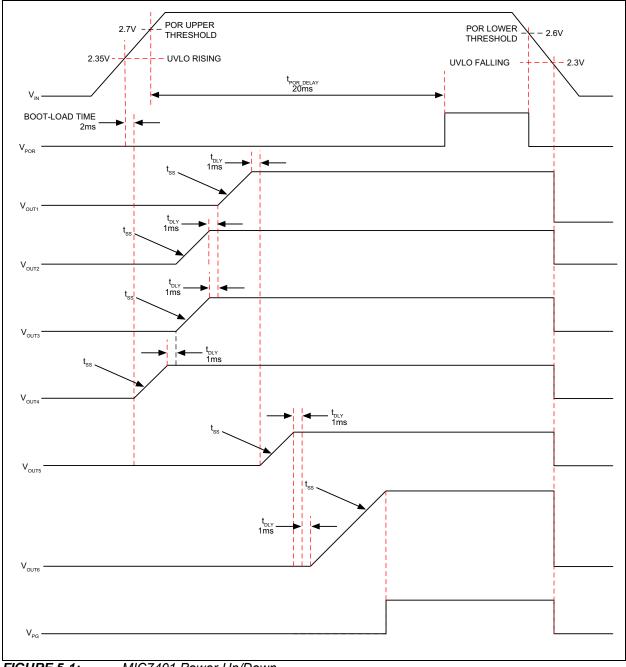

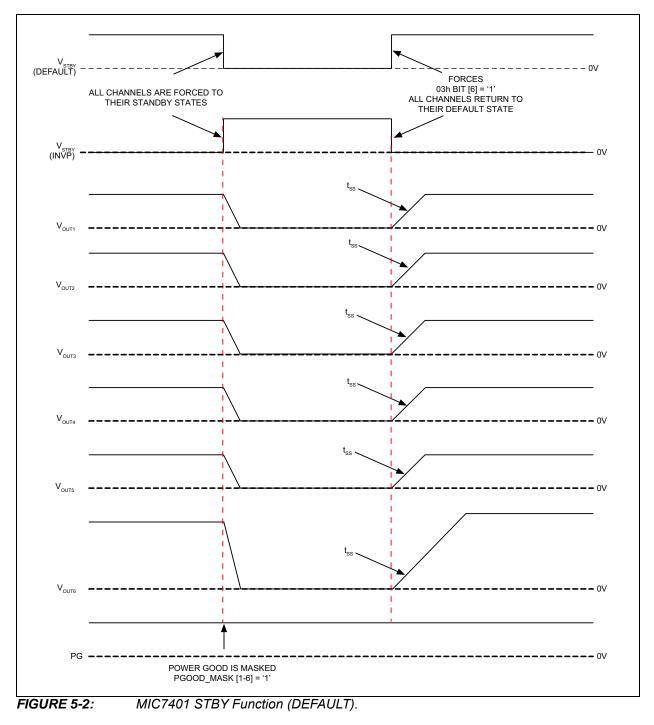

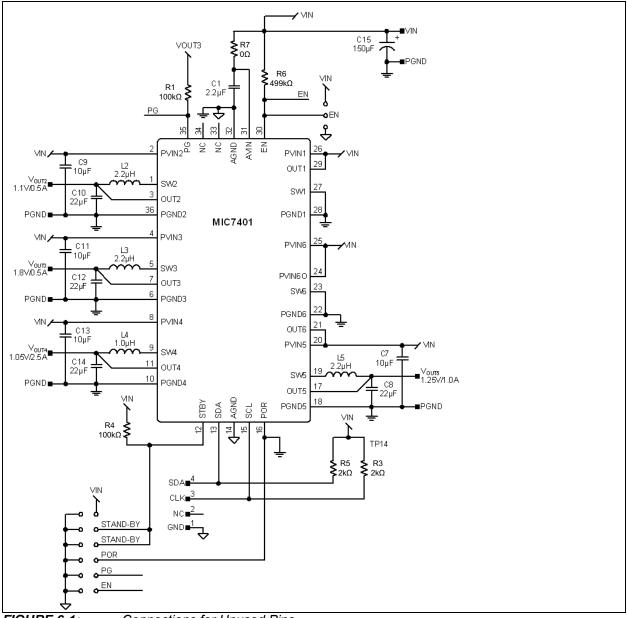

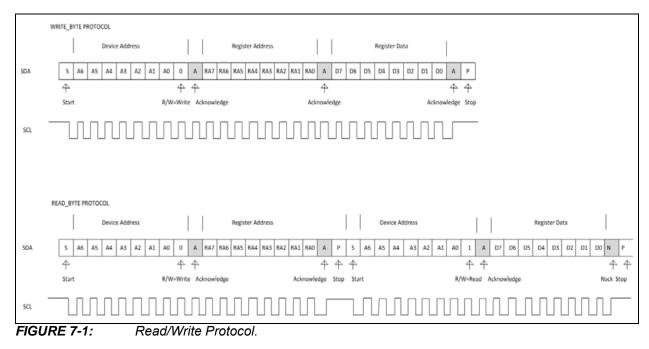

| Buck 3 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 4 Current-Limit Threshold4.886.17.32ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsBuck 5 Current-Limit Threshold3.0754.15.125ASee Table 4-3 for IPROG SettingsGross High-Side Current-Limit [1-5]-150-%With Respect to Buck [x]<br>Current-Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Buck 1 Current-Limit Threshold                            | 3.075 | 4.1  | 5.125 | Α       | See Table 4-3 for IPROG Settings                                        |  |  |