## **MIC2826**

Quad Output PMIC with HyperLight Load™ DC-DC. three LDOs, and I<sup>2</sup>C Control

## **General Description**

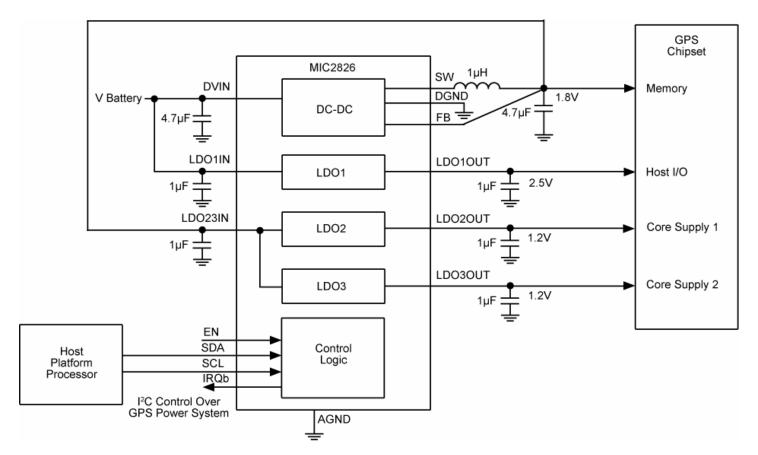

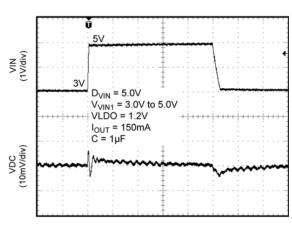

The Micrel MIC2826 is a four output, programmable Power Management IC, optimized for high efficiency power support in Mobile Application Processors, Co-Processors, DSPs, GPS and Media Player chipsets. The device integrates a single 500mA PWM/PFM synchronous buck (step-down) regulator with three Low Dropout Regulators and a 400kHz I²C interface that provides programmable Dynamic Voltage Scaling (DVS), Power Sequencing, and individual output Enable/Disable controls allowing the user to optimally control all four outputs.

The 4MHz synchronous buck regulator features a patented HyperLight Load™ (HLL) architecture which minimizes switching losses and provides low quiescent current operation for high efficiency at light loads. Additional benefits of this proprietary architecture are low output ripple voltage and fast transient response throughout the entire load range with the use of small output capacitors, reducing the overall system size.

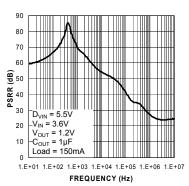

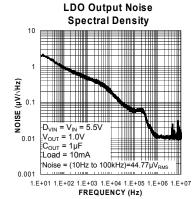

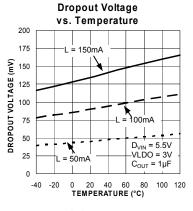

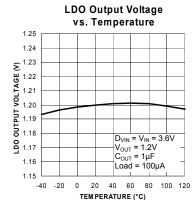

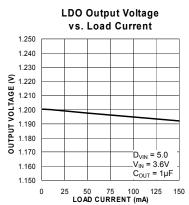

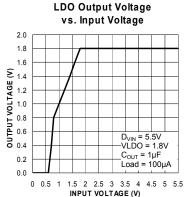

Three high performance LDOs are integrated into the MIC2826 to provide additional system voltages for I/O, memory and other analog functions. Each LDO is capable of sourcing 150mA output current with high PSRR and low output noise. A 2% output voltage accuracy, low dropout voltage (150mV @ 150mA), and low ground current of  $116\mu A$  (all three LDOs operating) makes this device ideally suited for mobile applications.

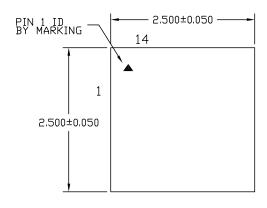

The MIC2826 is available in a tiny 14-pin 2.5mm x 2.5mm Thin  $MLF^{\$}$  with a junction operating range from -40°C to +125°C.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

## **Applications**

- Application processors

- GPS subsystems

- General purpose PMIC

- Mobile phones / PDAs

- Portable media players

- Mobile television receivers

#### **Features**

- Fast-mode I<sup>2</sup>C control interface

- Tiny 14-pin 2.5mm x 2.5mm MLF® package

- Default start-up voltage states and sequencing

- · Fault indication processor flag IRQb

- -40°C to 125°C junction temperature range

- Thermal shutdown and current-limit protection

- Power On After Fault (POAF) function

#### **DC-DC Synchronous Buck**

- 2.7V to 5.5V input voltage range

- 500mA continuous output current

- HyperLight Load™ mode

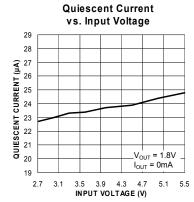

- 25µA quiescent current

- 90% peak efficiency; 85% at 1mA

- Ultra-fast transient response

- Dynamic Voltage Scaling (DVS) range: 0.8V to 1.8V

- 0.8V to 1.2V in 25mV steps

- 1.2V to 1.8V in 50mV steps

- ±2% initial accuracy

- Low output voltage ripple: 20mVpp in HyperLight Load™ mode, 3mV in full PWM mode

#### **LDOs**

- 1.8V to V<sub>DVIN</sub> input voltage range

- 150mA output current (each LDO)

- Dynamic Voltage Scaling (each LDO)

- DVS range: 0.8V to 3.3V in 50mV steps

- ±2% initial accuracy

- Low quiescent current 50µA (each LDO)

- Low dropout voltage 50mV @ 50mA

- Low output noise 45μV<sub>RMS</sub>

- Stable with ceramic output capacitors

- 65dB PSRR at 1kHz

HyperLight Load is a trademark of Micrel, Inc

MLF and MicroLeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

July 2009 M9999-071609-A

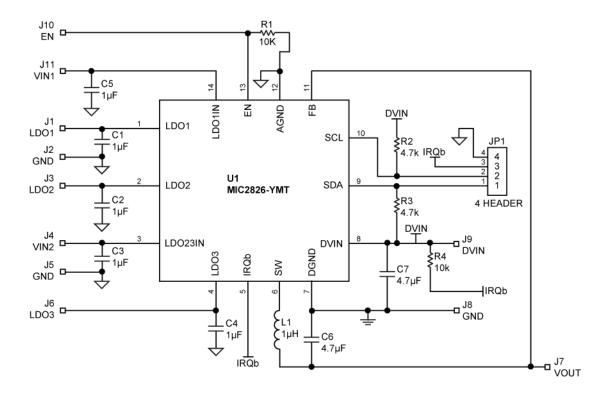

# **Typical Application**

**GPS Subsystem Application**

# **Ordering Information**

| Part Number   | Marking<br>Code <sup>(2)</sup> |      |      | Start U<br>iges <sup>(1)</sup> | р     |    |      | Start U<br>ence <sup>(1)</sup> |      | Junction Temp.<br>Range | Package <sup>(3)</sup>                    |  |

|---------------|--------------------------------|------|------|--------------------------------|-------|----|------|--------------------------------|------|-------------------------|-------------------------------------------|--|

|               |                                | SW   | LDO1 | LDO2                           | LDO3  | SW | LDO1 | LDO2                           | LDO3 | 90                      | 3                                         |  |

| MIC2826-A0YMT | 826A0                          | 1.2V | 2.6V | 1.2V                           | 1.8.V | 2  | 1    | 3                              | 4    | -40°C to +125°C         | 14-Pin 2.5x2.5mm<br>Thin MLF <sup>®</sup> |  |

| MIC2826-D9YMT | 826D9                          | 1.8V | 2.5V | 1.2V                           | 1.2V  | 1  | Off  | Off                            | Off  | -40°C to +125°C         | 14-Pin 2.5x2.5mm<br>Thin MLF <sup>®</sup> |  |

#### Note:

- 1. Other Default voltages and sequences are available on request (Voltages: 0.8V to  $3.3V_{OUT}$  LDOs, and 0.8V to  $1.8V_{OUT}$  PWM). Please contact Micrel Marketing for other voltage ranges.

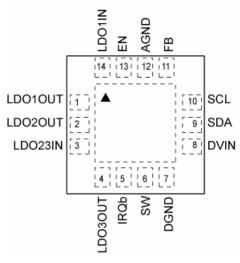

- 2. Thin MLF<sup>®</sup> Pin 1 Identifier symbol is "▲".

- 3. Thin MLF® is a Green RoHS compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

# **Pin Configuration**

14-Pin 2.5mm x 2.5mm Thin  $\mathrm{MLF}^{\otimes}$  (MT) (Top View)

# **Pin Description**

| Pin Number | Pin Name | Pin Function                                                                                                                                                                                               |

|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LDO10UT  | Output of LDO1: Requires a minimum 1µF ceramic capacitor-to-AGND.                                                                                                                                          |

| 2          | LDO2OUT  | Output of LDO2: Requires a minimum 1µF ceramic capacitor-to-AGND.                                                                                                                                          |

| 3          | LDO23IN  | External Input Supply Rail to LDO2 and LDO3. Requires a minimum 1µF ceramic capacitor to AGND.                                                                                                             |

| 4          | LDO3OUT  | Output of LDO3: Connect a minimum 1µF ceramic capacitor to AGND.                                                                                                                                           |

| 5          | IRQb     | Fault Output (open drain).                                                                                                                                                                                 |

| 6          | SW       | Switch (Output): Internal power MOSFET output switches.                                                                                                                                                    |

| 7          | DGND     | Switch Ground Pin.                                                                                                                                                                                         |

| 8          | DVIN     | Input Voltage: Requires a close minimum 2.2µF ceramic capacitor to DGND.                                                                                                                                   |

| 9          | SDA      | Fast-mode 400kHz I <sup>2</sup> C Data Input/Output pin.                                                                                                                                                   |

| 10         | SCL      | Fast-mode 400kHz I <sup>2</sup> C Clock Input pin.                                                                                                                                                         |

| 11         | FB       | Feedback Pin Connected to VOUT to sense output voltage.                                                                                                                                                    |

| 12         | AGND     | Analog Ground. Must be connected externally to DGND.                                                                                                                                                       |

| 13         | EN       | Enable (Input): Executes default startup sequence. Active High. HIGH = ON, LOW = OFF. Do not leave floating. The EN pin function is optional if I <sup>2</sup> C control is used for startup and shutdown. |

| 14         | LDO1IN   | External Input Supply Rail to LDO1. Requires a minimum 1µF ceramic capacitor to AGND.                                                                                                                      |

| EP         | HS PAD   | Exposed Heat-Sink Pad.                                                                                                                                                                                     |

# **Absolute Maximum Ratings**(1)

| Supply Voltage (V <sub>DVIN</sub> , V <sub>LDO1IN</sub> , V <sub>LDO23IN</sub> ) | 0.3V to +6V                       |

|----------------------------------------------------------------------------------|-----------------------------------|

| Enable Voltage (V <sub>EN</sub> )                                                |                                   |

| I <sup>2</sup> C Voltage (V <sub>SDA</sub> , V <sub>SCL</sub> )                  | 0.3V to +6V                       |

| Power Dissipation                                                                | Internally Limited <sup>(3)</sup> |

| Lead Temperature (Soldering, 10 sec.)                                            | 260°C                             |

| Storage Temperature (T <sub>s</sub> )                                            | 65°C ≤ T <sub>J</sub> ≤ +150°C    |

| ESD Rating <sup>(4)</sup>                                                        | 2kV                               |

# Operating Ratings<sup>(2)</sup>

| DV/INI Cumply valtages (V/                                       | 10 7\/ to 15 5\/           |

|------------------------------------------------------------------|----------------------------|

| DVIN Supply voltage (V <sub>DVIN</sub> )                         | +2.7 V 10 +5.5 V           |

| LDO Supply voltage (V <sub>LDO1IN</sub> , V <sub>LDO23IN</sub> ) | +1.8V to V <sub>DVIN</sub> |

| Enable Input Voltage (V <sub>EN</sub> )                          |                            |

| I <sup>2</sup> C Voltage (V <sub>SDA</sub> , V <sub>SCL</sub> )  | 0V to +5.5V                |

| Junction Temperature Range (T <sub>J</sub> )                     |                            |

| Junction Thermal Resistance                                      |                            |

| 2.5mm x 2.5mm Thin MLF-14 ( $\theta_{JA}$ )                      | 89°C/W                     |

# Electrical Characteristics<sup>(5)</sup> – DC/DC Converter

DVIN = EN = 3.6V; LDO1, LDO2, LDO3 disabled; L=1 $\mu$ H, C<sub>OUT</sub> =4.7 $\mu$ F, I<sub>OUT</sub>= 20mA, T<sub>A</sub> = 25°C, unless otherwise specified. **Bold** values indicate -40°C $\leq$ T<sub>J</sub> $\leq$ +125°C.

| Parameter                               | Conditions                                                  | Min  | Тур  | Max  | Units |

|-----------------------------------------|-------------------------------------------------------------|------|------|------|-------|

| Supply Voltage Range                    |                                                             | 2.7  |      | 5.5  | V     |

| Under-Voltage Lockout<br>Threshold      | Rising                                                      | 2.45 | 2.55 | 2.65 | V     |

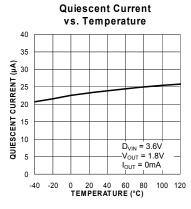

| Switcher Quiescent Current,<br>HLL      | I <sub>OUT</sub> = 0mA, FB > 1.2 * V <sub>OUT</sub> Nominal |      | 25   | 35   | μA    |

| Shutdown Current                        | EN = 0V, DVIN = 5.5V                                        |      | 2    | 5    | μA    |

| Output Voltage Accuracy                 | DVIN = 3.6V; I <sub>LOAD</sub> = 20mA                       | -3   |      | +3   | %     |

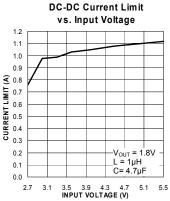

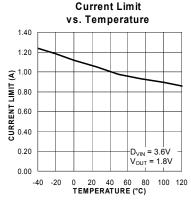

| Current Limit in PWM Mode               | FB = 0.9* V <sub>OUT</sub> (NOM)                            | 0.55 | 1    |      | Α     |

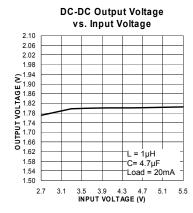

| Output Voltage Line Regulation          | DVIN = 3.0V to 5.5V, I <sub>LOAD</sub> = 20mA               |      | 0.4  |      | %/V   |

| Output Voltage Load Regulation          | 20mA < I <sub>LOAD</sub> < 500mA, DVIN = 3.6V               |      | 0.5  |      | %     |

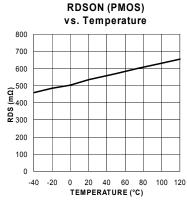

| PWM Switch ON-Resistance                | I <sub>SW</sub> = 100mA PMOS                                |      |      |      | Ω     |

| PWW SWICH ON-Resistance                 | I <sub>SW</sub> = -100mA NMOS                               |      | 0.6  |      | Ω     |

| Frequency                               | I <sub>LOAD</sub> = 120mA                                   |      | 4    |      | MHz   |

| SoftStart Time                          | V <sub>OUT</sub> = 90%                                      |      | 300  |      | μs    |

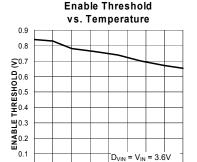

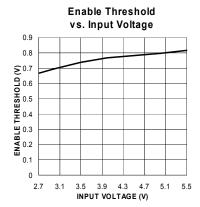

| Enable Voltage                          | OFF                                                         |      |      | 0.2  | V     |

|                                         | ON                                                          | 1.2  |      |      | V     |

| Enable Input Current                    |                                                             |      | 0.1  | 2    | μΑ    |

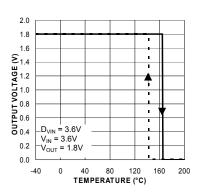

| Over-temperature Shutdown               |                                                             |      | 160  |      | °C    |

| Over-temperature Shutdown<br>Hysteresis |                                                             |      | 20   |      | °C    |

| VPOR Threshold                          | V <sub>OUT</sub> Ramping Up                                 |      | 91   |      | %     |

| % of V <sub>OUT</sub> below Nominal     | V <sub>OUT</sub> Ramping Down                               |      | 89   |      | %     |

| Auto-Discharge NFET resistance          |                                                             |      | 280  |      | Ω     |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- The maximum allowable power dissipation of any T<sub>A</sub> (ambient temperature) is P<sub>D(max)</sub> = (T<sub>J(max)</sub> T<sub>A</sub>) / θ<sub>JA</sub>. Exceeding the maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

- 4. Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5kΩ in series with 100pF.

- 5. Specification for packaged product only.

# Electrical Characteristics - LDO1, LDO2, and LDO3

DVIN = EN = LDO1IN = LDO23IN = 3.6V; DC-DC disabled; LDO  $C_{OUT}$  =1 $\mu$ F, LDO  $I_{OUT}$  = 100 $\mu$ A,  $T_A$  = 25°C, unless otherwise specified. **Bold** values indicate -40°C $\leq$ T $_J$  $\leq$ +125°C.

| Parameter                      | Conditions                                                               | Min  | Тур   | Max                | Units             |

|--------------------------------|--------------------------------------------------------------------------|------|-------|--------------------|-------------------|

| Output Voltage Accuracy        | Variation from nominal V <sub>OUT</sub>                                  | -3.0 |       | +3.0               | %                 |

| Input voltage                  | I <sub>OUT</sub> = 100μA to 150mA;                                       | 2    |       |                    | V                 |

|                                | I <sub>OUT</sub> = 100μA to 100mA; -20°C to +100°C                       | 1.74 |       |                    | V                 |

| Output Voltage DVS Range       | Adjustable through I <sup>2</sup> C Registers                            | 0.8  |       | 3.3                | V                 |

| Line Regulation                | LDO1IN, LDO23IN = V <sub>OUT</sub> +1V to 5.5V; I <sub>OUT</sub> = 100μA |      | 0.014 | 0.1                | %/V               |

| Load Regulation                | I <sub>OUT</sub> = 100μA to 75mA                                         |      | 4     |                    | mV                |

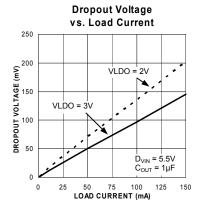

| Dropout Voltage                | I <sub>OUT</sub> = 50mA; V <sub>OUT</sub> = 2V                           |      | 70    |                    | mV                |

|                                | I <sub>OUT</sub> = 150mA; V <sub>OUT</sub> = 2V                          |      | 200   | 350                | mV                |

|                                | $I_{OUT}$ = 50mA; $V_{OUT}$ = 3V                                         |      | 50    |                    | mV                |

|                                | I <sub>OUT</sub> = 150mA; V <sub>OUT</sub> = 3V                          |      | 150   | +3.0<br>3.3<br>0.1 | mV                |

| Ground Pin Current             | EN = DVIN                                                                |      |       |                    |                   |

|                                | 1 LDO enabled                                                            |      | 50    |                    | μΑ                |

|                                | 2 LDOs enabled                                                           |      | 83    |                    | μA                |

|                                | 3 LDOs enabled                                                           |      | 116   |                    | μΑ                |

| Ripple Rejection               | $f = up to 1kHz; C_{OUT} = 1\mu F; V_{OUT} = 2.5V$                       |      | 65    |                    | dB                |

|                                | $f = 1kHz - 10kHz$ ; $C_{OUT} = 1\mu F V_{OUT} = 2.5V$                   |      | 45    |                    | dB                |

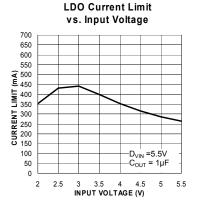

| Current Limit                  | V <sub>OUT</sub> = 0V                                                    | 190  | 400   | 550                | mA                |

| Output Voltage Noise           | C <sub>OUT</sub> = 1µF,10Hz to 100kHz                                    |      | 45    |                    | μV <sub>RMS</sub> |

| Auto-Discharge NFET resistance |                                                                          |      | 280   |                    | Ω                 |

# Electrical Characteristics – I<sup>2</sup>C Interface

DVIN = EN = 3.6V,  $T_A$  = 25°C, unless otherwise specified. **Bold** values indicate -40°C $\leq$ T<sub>J</sub> $\leq$ +125°C.

| Parameter                 | Conditions                                   | Min | Тур | Max | Units |

|---------------------------|----------------------------------------------|-----|-----|-----|-------|

| LOW-Level Input Voltage   |                                              |     |     | 0.2 | V     |

| HIGH-Level Input Voltage  |                                              | 1.2 |     |     | V     |

| SDA Pull-down resistance  | Open drain pull-down on SDA during read back |     | 80  |     | Ω     |

| IRQb Pull-down resistance | Open drain pull-down                         |     | 55  |     | Ω     |

## **Typical Characteristics**

#### Thermal Shutdown

40 60 80

TEMPERATURE (°C)

-40 -20 0 20

LDO Input Voltage PSRR

vs. Temperature

D<sub>VIN</sub> = 5.5V VLDO = 2V

$C_{OUT} = 1\mu F$

20 40 60 80 100 120

TEMPERATURE (°C)

**Dropout Voltage**

250 225

200

175

150 125

100

75

50

25

-40

= 50mA

-20 0

DROPOUT VOLTAGE (mV)

# **Typical Characteristics (continued)**

# **Typical Characteristics (continued)**

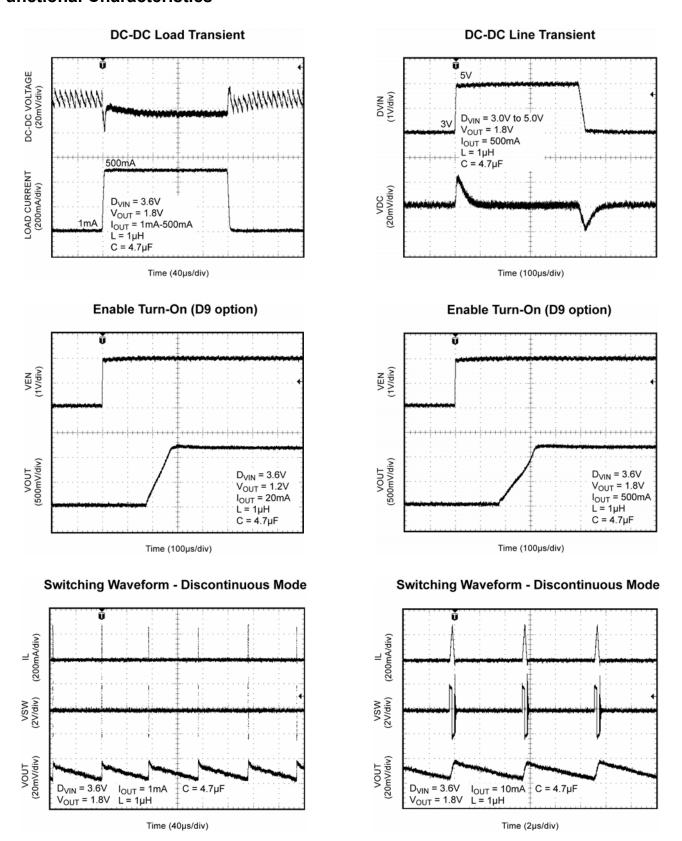

## **Functional Characteristics**

# **Functional Characteristics (continued)**

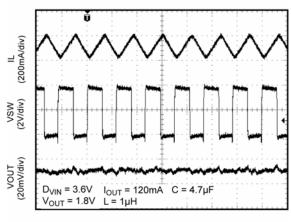

## **Switching Waveform - Continuous Mode**

Time (200ns/div)

# **Switching Waveform - Continuous Mode**

Time (200ns/div)

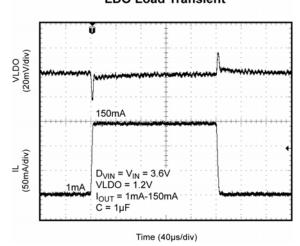

#### **LDO Load Transient**

**LDO Line Transient**

Time (20µs/div)

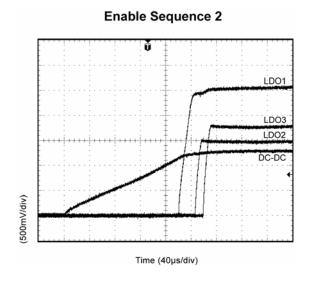

# **Functional Block Diagram**

# Functional Description – Power Control and Sequencing

# Two Types of Part: Sequence-Enabled and No-Sequence

Sequence-Enabled parts support automatic sequencing of the four supplies. Sequence-Enabled parts all have a default sequence (activated by asserting the EN pin). These parts also allow sequencing to be disabled.

While very flexible, sequence-enabled parts require more care in operation. See the later section "Ensuring Clean Switching in Sequence-Enabled Parts".

No-Sequence parts have no built-in sequencing capability. Their default startup turns on only one supply, which requires no sequencing. If the host needs more supplies to come on, this can be accomplished with I<sup>2</sup>C writes which allows a sequence activated by software to be performed.

## **Power-up State**

When battery power is first applied to the MIC2826, all I<sup>2</sup>C registers are loaded with their default (POR) values.

If EN is high, a default startup is executed; otherwise, the part remains in a quiescent state waiting to be started by EN or an I<sup>2</sup>C command.

#### **Enable Pin-Initiated Default Startup**

When EN is asserted, a default startup is executed. This is defined below:

- The voltage registers are loaded with their default values.

- In sequence-enabled parts, the Sequence Control bit is set to low (to allow sequencing to occur). Nosequence parts always have zero for the Sequence Control bit

- The correct set of supply enable bits is loaded into the Enable Register, and the appropriate sequence is then executed.

- The Power-On After Fault (POAF) bit is set to its default state, high.

### **Turning on the Power Supplies**

After power is applied, the MIC2826 offers two methods of turning the four supply outputs on and off:

- 1. Default startup sequencing or shutdown via the EN pin;

- 2. Flexible startup sequencing or shutdown via the I<sup>2</sup>C interface

#### Power-Up via the EN Pin

The EN pin is transition sensitive and not level sensitive (with the exception of hot enable—please see the description below). If the EN pin is toggled low-to-high, the MIC2826 will execute the default startup sequence.

During the startup sequence, the appropriate set of supply enables is loaded into the Enable Register. This allows the part to present a consistent interface to the I<sup>2</sup>C host; if the host reads the Enable Control register, it will see one or more enables on, which is consistent with one or more active supplies.

Individual control of the supplies is now possible via the I<sup>2</sup>C interface.

#### "Hot Enable" Startup

Some systems may choose to tie the EN pin to DVIN, so that the MIC2826 registers an active EN pin as it completes power-on. This is perfectly legal and produces a default startup immediately after power is applied. Depending on the rise time of the input power being applied, the UVLO flag may be set.

#### Power-Down via the EN Pin

If the EN pin is toggled high-to-low, the MIC2826 will shut down all outputs simultaneously. For reasons similar to those above, at the conclusion of the shutdown sequence, all four individual supply enables will be clear in the Enable Control register and the bias will be switched off.

If the MIC2826 startup is initiated by asserting EN and later shutdown is initiated by clearing the Enable Register bits, the part will be quiescent (with all bias currents disabled) but EN will still be high. In this case, de-asserting EN will have no effect, since the part has already completed its shutdown.

#### Power-Up and Power-Down via the Enable Register

The four individual power supply enable bits in the Enable Register (LDO3-EN, LDO2-EN, LDO1-EN, and DC-EN) may be used to enable and disable individual supplies. If the part is sequenced-enabled, and sequencing is permitted by the Sequence Control bit, enabled supplies are turned on in sequence. Any disabled outputs will not participate in the sequence and will be ignored.

See also the "Ensuring Clean Switching in Sequence-Enabled Parts" section.

Under no circumstances should the EN and I<sup>2</sup>C control be used simultaneously. The results would not be deterministic.

If a supply output is enabled and its Voltage Control register is written with a new value, the output voltage changes immediately at the I<sup>2</sup>C acknowledge.

#### **Fault Handling**

A fault is generated from either a thermal shutdown or under-voltage lockout event. If a fault occurs, the activation of the fault condition immediately turns off all output supplies, sets the fault flag bit(s) in the Status Register, and loads default values in the Enable and Voltage Registers. The sequence Control bit SEQ CNT is cleared to enable sequencing for sequence-enabled parts. The POAF bit is unaffected.

The default state of the Enable Register's POAF (Power On After Fault) bit is high, indicating that the MIC2826 will perform a default start up when the fault goes away. If the user instead prefers that the part does not automatically attempt re-start after a fault, the POAF can be programmed to a "0".

The EN pin can be toggled high-to-low at any time to clear the supply enables in the Enable Register and shut down the part. The same can be achieved through I<sup>2</sup>C at any time by disabling all enables in the enable register. Either method can be used to shut down the part during a fault.

Shutdown after a fault will maintain the fault flags in the status register. Only Power-on-Reset or an echo reset of the status register will clear these flags.

#### Thermal Shutdown (TSD)

If the MIC2826's on-chip thermal shutdown detects that the die is too hot, the part will immediately turn off all outputs but maintain the bias to internal circuitry. The thermal event is logged in the Status register which can be read via I<sup>2</sup>C. When the thermal shutdown event is removed, a default startup is executed if POAF is high.

#### **Under Voltage Lock Out (UVLO)**

If the MIC2826's on-chip voltage monitor detects a low voltage on the DVIN supply, the part will immediately turn off all outputs but maintain the bias to internal circuitry. When the UVLO event is removed, the outputs will turn on using the default startup if POAF is high. The UVLO event is logged in the status register which can be read via I<sup>2</sup>C.

If the power on DVIN drops too low, the MIC2826 will no longer be able to function reliably and will enter its power-on reset (POR) state. Any previously raised TSD or UVLO flags will now be cleared at startup

#### **Power Good Indication and Hysteresis**

The status of all four outputs can be read via I<sup>2</sup>C in the status register. A register flag is set for each output when it reaches 90% of its regulated value and cleared when the output falls to about 85%.

#### **Interrupt Operation**

If interrupts are enabled (INT-EN = 1), then the MIC2826's IRQb output will be asserted (driven low) whenever either of the two fault bits, UVLO or TSD, are asserted. Clearing the fault status bit by writing a one to it will clear the interrupt if the fault condition is no longer present. If the fault is still present, the status bit will be asserted again, together with the IRQb output. This operation does not depend on the state of the POAF bit.

The default state of the INT\_EN bit is zero, so the interrupt output is disabled. This is done so that the interrupt pin does not transition in MIC2826 systems which use only the EN pin and not the I<sup>2</sup>C interface.

# Ensuring Clean Switching in Sequence-Enabled Parts

In no-sequence parts, no sequencing ever occurs, and no special rules are required. However, in sequenceenabled parts, care must be taken when using automatic supply startup sequencing.

The sequence-enabled MIC2826 accomplishes supply sequencing by asynchronously using one supply's power good signal to enable the next supply in line. As a consequence "downstream" supplies can momentarily switch off their outputs when "upstream" supplies are switched in and out of the sequencing chain.

#### Example:

Suppose the sequence [DC, 1, 2, 3] is enabled and LDO1 is off, the others are enabled and their status is valid. If LDO1 is now enabled through I<sup>2</sup>C, LDO2 and LDO3 will turn momentarily off, until LDO1 is valid, which then starts LDO2 first and then LDO3.

To avoid this, the following rules should be observed, which apply only to sequence-enabled parts:

- 1. If all supplies are to be turned on, it is fine to use sequencing. This is what happens naturally as part of the EN-initiated default startup. It may also be accomplished by setting all four supply enables simultaneously in the Enable Register, and leaving the Sequence Control bit low to permit sequencing.

- 2. When starting from an all-off condition and a subset of the supplies is to be turned on, sequencing is permitted.

- When one or more supplies are on, and a supply is to be turned off or on, sequencing must be disabled by setting SEQ CNT high.

- 4. When a subset of the supplies has been turned on via the Enable Register, an active transition on the EN pin must not be used to turn on the remaining supplies.

Sequencing rules do not apply to the last supply in the sequencing chain (the supply labeled "4th" in the sequence table). The 4th supply may be turned on and off at any time, since there are no downstream supplies from the 4th.

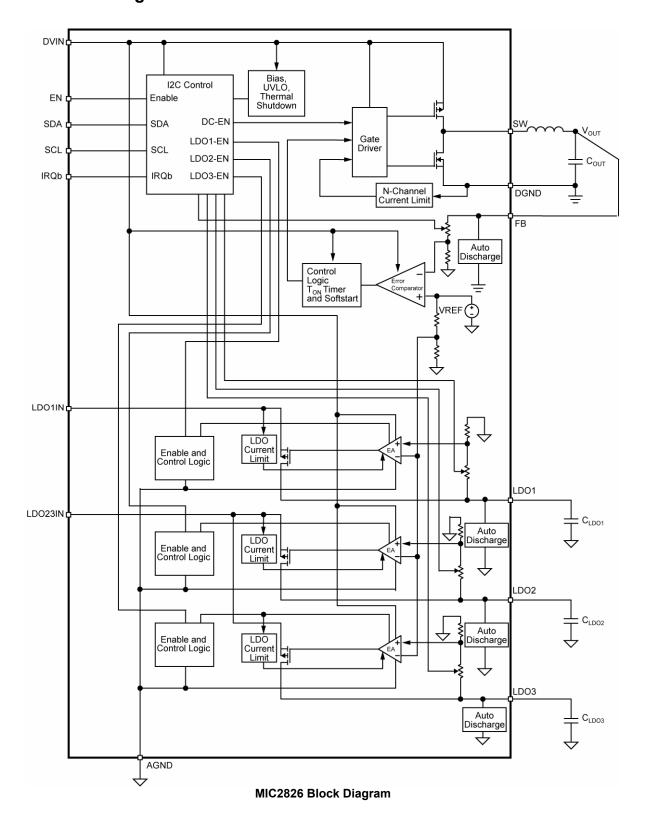

### **Available Default Startup Sequences**

The following table shows available default startup sequences for the MIC2826. Please contact Micrel factory to request customized default startup voltages and sequences.

| Sequence<br>Number | DC-<br>DC | LDO1 | LDO2 | LDO3 | Sequence-<br>Enabled<br>Part? |

|--------------------|-----------|------|------|------|-------------------------------|

| Sequence 0         | 2nd       | 1st  | 3rd  | 4th  | Yes                           |

| Sequence 2         | 1st       | 2nd  | 3rd  | 4th  | Yes                           |

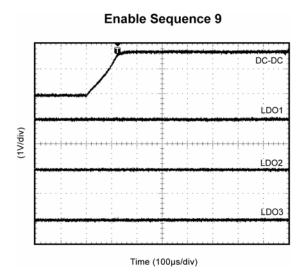

| Sequence 9         | On        | Off  | Off  | Off  | No                            |

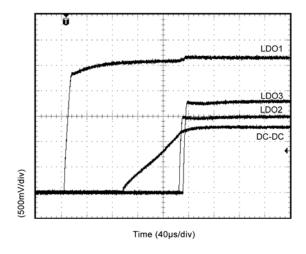

## **Enable Sequence 0**

# Functional Description – Fast-mode I<sup>2</sup>C Interface

#### I<sup>2</sup>C Address

The seven-bit I<sup>2</sup>C address of the MIC2826 is set at the factory to 1011010 binary, which would be identified as B4h using standard I<sup>2</sup>C nomenclature, in which the read/write bit takes the least significant position of the eight-bit address. Other I<sup>2</sup>C base addresses are available; please contact Micrel for details.

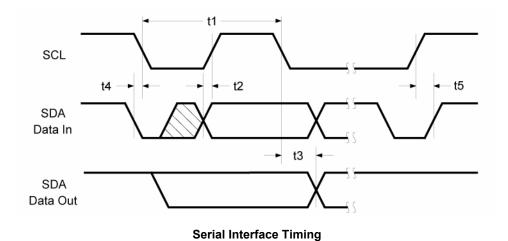

# **Electrical Characteristics – Serial Interface Timing**

$3.0V \le V_{DVIN} \le 3.6V$  unless otherwise noted. **Bold** values indicate -40°C  $\le T_A \le$  +125°C.

| Symbol                | Parameter                         | Conditions | Min | Тур | Max | Units |

|-----------------------|-----------------------------------|------------|-----|-----|-----|-------|

| t <sub>1</sub>        | SCL (clock) period                |            | 2.5 |     |     | μs    |

| t <sub>2</sub>        | Data In Setup Time to SCL High    |            | 100 |     |     | ns    |

| t <sub>3</sub>        | Data Out Stable After SCL Low     |            | 0   |     |     | ns    |

| t <sub>4</sub>        | SDA Low Setup Time to SCL Low     | Start      | 100 |     |     | ns    |

| <b>t</b> <sub>5</sub> | SDA High Hold Time after SCL High | Stop       | 100 |     |     | ns    |

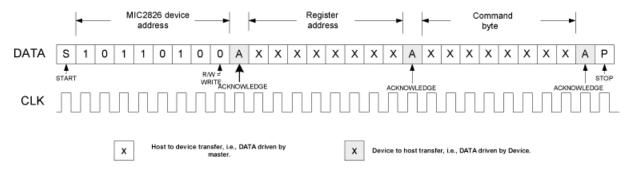

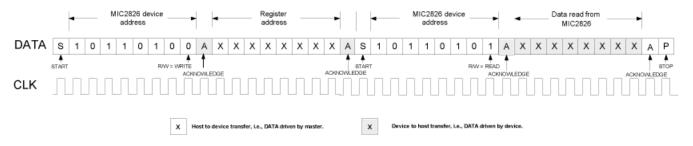

#### **Serial Port Operation**

The MIC2826 uses standard Write\_Byte, Read\_Byte, and Read\_Word operations for communication with its host. The Write\_Byte operation involves sending the device's address (with the R/W bit low to signal a write operation), followed by the register address and the command byte. The Read\_Byte operation is a composite write and read operation: the host first sends the device's address followed by the register address, as in a write operation. A new start bit must then be sent to

the MIC2826, followed by a repeat of the device address with the R/W bit (LSB) set to the high (read) state. The data to be read from the part may then be clocked out. These protocols are shown in Figure 1 and Figure 2.

The Register Address is eight bits (one byte) wide. This byte carries the address of the MIC2826 register to be operated upon. Only the lower three bits are used.

Figure 1: Write\_Byte protocol

Figure 2: Read\_Byte protocol

# Functional Description – I<sup>2</sup>C Control Registers

| Register<br>Address | Register<br>Name | Read/<br>Write | Description                                        |

|---------------------|------------------|----------------|----------------------------------------------------|

| 00h                 | Enable           | R/W            | Enable and startup control register                |

| 01h                 | Status           | R/W            | Regulator output & fault condition status register |

| 02h                 | DC-DC            | R/W            | DC-DC regulator voltage control register           |

| 03h                 | LDO1             | R/W            | LDO1 voltage control register                      |

| 04h                 | LDO2             | R/W            | LDO2 voltage control register                      |

| 05h                 | LDO3             | R/W            | LDO3 voltage control register                      |

### Enable/Startup Control Register (00h):

The Enable Register is used to allow control of the MIC2826's power supplies. It allows each supply to be turned on and off, and whether sequencing is used.

When a default startup is executed as a result of the EN pin being taken from low to high, the Sequence Control, and Supply Enable bits are all set to their default values.

The Sequence Control bit, only implemented in sequence-enabled parts, must be used carefully. See the section on "Ensuring Clean Switching in Sequence-Enabled Parts".

|                            | D7  | D6    | D5                                                                | D4                                                      | D3                        | D2        | D1                | D0 |

|----------------------------|-----|-------|-------------------------------------------------------------------|---------------------------------------------------------|---------------------------|-----------|-------------------|----|

| Name                       | Res | erved | POAF                                                              | SEQ CNT                                                 | LDO3-EN LDO2-EN           |           | LDO2-EN LDO1-EN D |    |

| Access                     | ١   | I/A   | R/W                                                               | R/W                                                     | R/W R/W                   |           | R/W R/W F         |    |

| POR Value                  | (   | 00    | 1                                                                 | 0                                                       | 0                         | 0 0 0     |                   |    |

| Data                       | (   | 00    | 0 = Remain off<br>after fault<br>1 = Restore<br>power after fault | 0 = Sequencing<br>enabled<br>1 = Sequencing<br>disabled | 0 = Disable<br>1 = Enable |           |                   |    |

| Set by Default<br>Startup? | Y   | 'es   | Yes                                                               | Yes                                                     |                           | Y         | es                |    |

| Set by a fault?            | ١   | No    | No                                                                | Yes                                                     |                           | Yes, if I | POAF=1            |    |

### Status Register (01h):

The Status Register allows the state of each supply to be interrogated, supports flags that are set when fault conditions occur, and controls the use of the MIC2826's interrupt pin.

|              | D7       | D6                                               | D5                                                    | D4                                              | D3                                         | D2                                         | D1                                         | D0                                           |

|--------------|----------|--------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|----------------------------------------------|

| Name         | Reserved | INT-EN                                           | UVLO                                                  | TSD                                             | L3-Status                                  | L2-Status                                  | L1-Status                                  | DC-Status                                    |

| Access       | RO       | R/W                                              | Echo<br>reset                                         | Echo reset                                      | RO                                         | RO                                         | RO                                         | RO                                           |

| POR<br>Value | 0        | 0                                                | 0                                                     | 0                                               | 0                                          | 0                                          | 0                                          | 0                                            |

| Data         | 0        | 0: Interrupt is disabled 1: Interrupt is enabled | 0: Normal<br>1: DVIN<br>under-<br>voltage<br>occurred | 0: Normal<br>1: Thermal<br>shutdown<br>occurred | 0 = LDO3<br>Not Valid<br>1 = LDO3<br>Valid | 0 = LDO2<br>Not Valid<br>1 = LDO2<br>Valid | 0 = LDO1<br>Not Valid<br>1 = LDO1<br>Valid | 0 = DC-DC<br>Not Valid<br>1 = DC-DC<br>Valid |

#### Note:

"Echo reset" bits remain set until cleared. Clearing these bits is accomplished by writing a one to that bit location ("echo the one to reset"). If the fault condition (UVLO or thermal shutdown) persists after the echo reset, the corresponding Status Register bit will be set high again immediately.

### DC-DC Regulator Voltage Control Register (02h)

This register controls the output voltage of the DC-DC PWM/PFM Regulator. The DC-DC Regulator employs a dual scale voltage step size to cover a wide range of output voltages from 0.8V to 1.8V. From 0.8V to 1.2V a step size of 25mV allows maximum power saving when the Processor Core is placed into a light load state. From 1.2V to 1.8V, a step size of 50mV provides a wide range of output voltages for power system flexibility.

# **DC-DC Regulator Voltage Control Register Table**DC-DC Regulator Voltage Control Register Address: 02h

| Step Size | Register Value | Output Voltage |

|-----------|----------------|----------------|

| 25mV      | 00h            | 0.800          |

|           | 01h            | 0.825          |

|           | 02h            | 0.850          |

|           | 03h            | 0.875          |

|           | 04h            | 0.900          |

|           | 05h            | 0.925          |

|           | 06h            | 0.950          |

|           | 07h            | 0.975          |

|           | 08h            | 1.000          |

|           | 09h            | 1.025          |

|           | 0Ah            | 1.050          |

|           | 0Bh            | 1.075          |

|           | 0Ch            | 1.100          |

|           | 0Dh            | 1.125          |

|           | 0Eh            | 1.150          |

|           | 0Fh            | 1.175          |

| 50mV      | 10h            | 1.200          |

|           | 11h            | 1.250          |

|           | 12h            | 1.300          |

|           | 13h            | 1.350          |

|           | 14h            | 1.400          |

|           | 15h            | 1.450          |

|           | 16h            | 1.500          |

|           | 17h            | 1.550          |

|           | 18h            | 1.600          |

|           | 19h            | 1.650          |

|           | 1Ah            | 1.700          |

|           | 1Bh            | 1.750          |

|           | 1Ch            | 1.800          |

## LDO1, LDO2, LDO3 Voltage Control Registers Table

LDO1 Regulator Voltage Control Register Address: 03h LDO2 Regulator Voltage Control Register Address: 04h LDO3 Regulator Voltage Control Register Address: 05h

| Step Size | Register Value | Output Voltage | Step Size | Register Value | Output Voltage |

|-----------|----------------|----------------|-----------|----------------|----------------|

| 50mV      | 00h            | 0.800          | 50mV      | BAh            | 2.400          |

|           | 0Bh            | 0.850          |           | BDh            | 2.450          |

|           | 14h            | 0.900          |           | C1h            | 2.500          |

|           | 1Dh            | 0.950          |           | C4h            | 2.550          |

|           | 25h            | 1.000          |           | C7h            | 2.600          |

|           | 2Eh            | 1.050          |           | C9h            | 2.650          |

|           | 37h            | 1.100          |           | CCh            | 2.700          |

|           | 3Eh            | 1.150          |           | CEh            | 2.750          |

|           | 45h            | 1.200          |           | D1h            | 2.800          |

|           | 4Ch            | 1.250          |           | D3h            | 2.850          |

|           | 52h            | 1.300          |           | D6h            | 2.900          |

|           | 57h            | 1.350          |           | D8h            | 2.950          |

|           | 5Ch            | 1.400          |           | DAh            | 3.000          |

|           | 61h            | 1.450          |           | DCh            | 3.050          |

|           | 65h            | 1.500          |           | DEh            | 3.100          |

|           | 69h            | 1.550          |           | E1h            | 3.150          |

|           | 6Dh            | 1.600          |           | E3h            | 3.200          |

|           | 72h            | 1.650          |           | E6h            | 3.250          |

|           | 79h            | 1.700          |           | E8h            | 3.300          |

|           | 7Fh            | 1.750          |           |                |                |

|           | 85h            | 1.800          |           |                |                |

|           | 8Bh            | 1.850          |           |                |                |

|           | 91h            | 1.900          |           |                |                |

|           | 96h            | 1.950          |           |                |                |

|           | 9Ah            | 2.000          |           |                |                |

|           | 9Fh            | 2.050          |           |                |                |

|           | A4h            | 2.100          |           |                |                |

|           | A8h            | 2.150          |           |                |                |

|           | ACh            | 2.200          |           |                |                |

|           | B0h            | 2.250          |           |                |                |

|           | B4h            | 2.300          |           |                |                |

|           | B7h            | 2.350          |           |                |                |

## **Functional Description**

#### **DVIN**

The DVIN pin provides power to the source of the internal switch P-channel MOSFET,  $I^2C$  control and voltage references for the MIC2826. The DVIN operating voltage range is from 2.7V to 5.5V. In order for any MIC2826 outputs to regulate, the appropriate input voltage must be applied to the DVIN pin. Due to the high switching speeds, a  $4.7\mu F$  capacitor is recommended as close as possible to the DVIN and power ground (DGND) pin for bypassing. Please refer to layout recommendations.

#### LDO1IN

LDO1IN provides power to the source of LDO1 P-channel MOSFET. The LDO1IN operating voltage range is from 1.8V to  $V_{\text{DVIN}}$ . The recommended bypass capacitor is 1µF.

#### LDO23IN

LDO23IN provides power to the source of the MIC2826 LDO2 and LDO3 P-channel MOSFET. The LDO23IN operating voltage range is from 1.8V to  $V_{DVIN}$ . The recommended bypass capacitor is  $1\mu F$ .

#### ΕN

The enable pin controls the ON and OFF state of all the outputs of the MIC2826. The EN pin is transition sensitive and not level sensitive. By toggling the enable pin low-to-high, this activates the default startup sequence of the part.

#### **SW**

The switching pin connects directly to one end of the inductor and provides the switching current during switching cycles. The other end of the inductor is connected to the load, output capacitor, and the FB pin. Due to the high speed switching on this pin, the switch node should be routed away from sensitive nodes.

#### FB

The feedback pin provides the control path to control the output. A recommended 4.7 $\mu$ F bypass capacitor should be connected in shunt with the DC-DC output. It is good practice to connect the output bypass capacitor to the DGND and FB should be routed to the top of  $C_{OUT}$ .

#### LD010UT

The LDO10UT pin provides the regulated output voltage of LDO1. Power is provided by LDO1IN. LDO10UT voltage can be dynamically scaled through  $I^2C$  control. The recommended output capacitance is  $1\mu F,$  decoupled to AGND.

#### LDO2OUT

The LDO2OUT pin provides the regulated output voltage of LDO2. Power is provided by LDO23IN. LDO2OUT voltage can be dynamically scaled through  $I^2C$  control. The recommended output capacitance is  $1\mu F,$  decoupled to AGND.

#### LD030UT

The LDO3OUT pin provides the regulated output voltage of LDO3. Power is provided by LDO23IN. LDO3OUT voltage can be dynamically scaled through  $l^2C$  control. The recommended output capacitance is  $1\mu F,$  decoupled to AGND.

#### SCL

The I<sup>2</sup>C clock input pin provides a reference clock for clocking in the data signal. This is a fast-mode 400kHz input pin, and requires a  $4.7k\Omega$  pull-up resistor. Please refer to "Serial Port Operation" for more details.

#### **SDA**

The  $I^2C$  data bidirectional pin allows for data to be written to and read from the MIC2826. This is a fast-mode 400kHz  $I^2C$  pin, and requires a 4.7k $\Omega$  pull-up resistor. Please refer to "Serial Port Operation" for more details.

#### **IRQb**

The IRQb (open drain) pin provides an interrupt for when either the UVLO or TSD faults are asserted. When enabled through I<sup>2</sup>C, the IRQb pin will assert together with the corresponding fault condition. Please refer to the "Interrupt Operation" for more details.

#### **DGND**

Power ground (DGND) is the ground path for the DC-DC MOSFET drive current. The current loop for the Power ground should be as small as possible and separate from the Analog ground (AGND) loop. Refer to the layout consideration for more details.

#### **AGND**

Analog ground (AGND) is the ground path for the biasing and control circuitry. The current loop for the Analog ground should be separate from the Power ground (AGND) loop. Refer to the layout consideration for more details.

## **Application Information**

The Micrel MIC2826 is a four output, programmable Power Management IC, optimized for high efficiency power support. The device integrates a single 500mA PWM/PFM synchronous buck (step-down) regulator with three Low Dropout Regulators and an I<sup>2</sup>C interface that provides programmable Dynamic Voltage Scaling (DVS), Power Sequencing, and individual output Enable/Disable controls allowing the user to optimally control all four outputs.

#### **Input Capacitors**

A 4.7µF ceramic capacitor is recommended on the DVIN pin for bypassing. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore not recommended. Also, tantalum and electrolytic capacitors alone are not recommended because of their reduced RMS current handling, reliability, and ESR increases.

An additional 0.1µF is recommended close to the DVIN and DGND pins for high frequency filtering. Smaller case size capacitors are recommended due to their lower ESR and ESL.

Minimum 1.0 $\mu$ F ceramic capacitors are recommended on the LDO1IN and LDO23IN pins for bypassing. Please refer to layout recommendations for proper layout of the input capacitors.

#### **Output Capacitors**

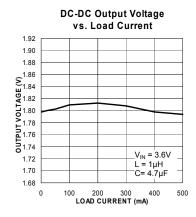

The MIC2826 is designed for a  $2.2\mu F$  or greater ceramic output capacitor for the DC-DC converter and  $1.0\mu F$  for the LDO regulators. Increasing the output capacitance will lower output ripple and improve load transient response but could increase solution size or cost. A low equivalent series resistance (ESR) ceramic output capacitor such as the TDK C1608X5R0J475K, size 0603,  $4.7\mu F$  ceramic capacitor is recommended based upon performance, size and cost. X5R or X7R dielectrics are recommended for the output capacitor. Y5V dielectrics lose most of their capacitance over temperature and are therefore not recommended.

In addition to a  $4.7\mu F$ , a small  $0.1\mu F$  is recommended close to the load for high frequency filtering. Smaller case size capacitors are recommended due to their lower equivalent series ESR and ESL.

#### Inductor

Inductor selection will be determined by the following (not necessarily in the order of importance);

- Inductance

- Rated current value

- Size requirements

- DC resistance (DCR)

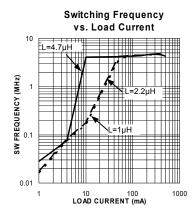

The MIC2826 was designed for use with an inductance range from  $0.47\mu H$  to  $4.7\mu H$ . Typically, a  $1\mu H$  inductor is recommended for a balance of transient response, efficiency and output ripple. For faster transient response a  $0.47\mu H$  inductor may be used. For lower output ripple, a  $4.7\mu H$  is recommended.

Proper selection should ensure the inductor can handle the maximum average and peak currents required by the load. Maximum current ratings of the inductor are generally given in two methods; permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Ensure the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin that the peak current will not saturate the inductor. Peak current can be calculated as follows:

$$I_{PEAK} = \left[I_{OUT} + V_{OUT} \left(\frac{1 - V_{OUT}/V_{IN}}{2 \times f \times L}\right)\right]$$

As shown by the previous calculation, the peak inductor current is inversely proportional to the switching frequency and the inductance; the lower the switching frequency or the inductance the higher the peak current. As input voltage increases, the peak current also increases.

The size of the inductor depends on the requirements of the application. Refer to the Application Circuit and Bill of Material for details.

DC resistance (DCR) is also important. While DCR is inversely proportional to size, DCR can represent a significant efficiency loss. Refer to the Efficiency Considerations.

#### **Efficiency Considerations**

Efficiency is defined as the amount of useful output power, divided by the amount of power supplied.

Efficiency % =

$$\left(\frac{V_{OUT} \times I_{OUT}}{V_{IN} \times I_{IN}}\right) \times 100$$

Maintaining high efficiency serves two purposes. It reduces power dissipation in the power supply, reducing the need for heat sinks and thermal design considerations and it reduces consumption of current for battery powered applications. Reduced current draw from a battery increases the devices operating time and is critical in hand held devices.

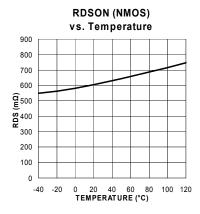

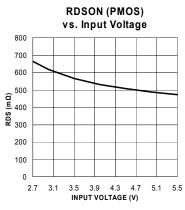

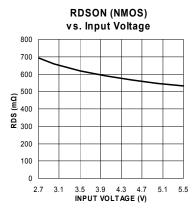

There are two types of losses in switching converters; DC losses and switching losses. DC losses are simply the power dissipation of  $\rm I^2R$ . Power is dissipated in the high side switch during the on cycle. Power loss is equal to the high side MOSFET  $\rm R_{DSON}$  multiplied by the Switch Current squared. During the off cycle, the low side N-channel MOSFET conducts, also dissipating power. Device operating current also reduces efficiency. The

product of the quiescent (operating) current and the supply voltage is another DC loss. The current required driving the gates on and off at a constant 4MHz frequency and the switching transitions make up the switching losses.

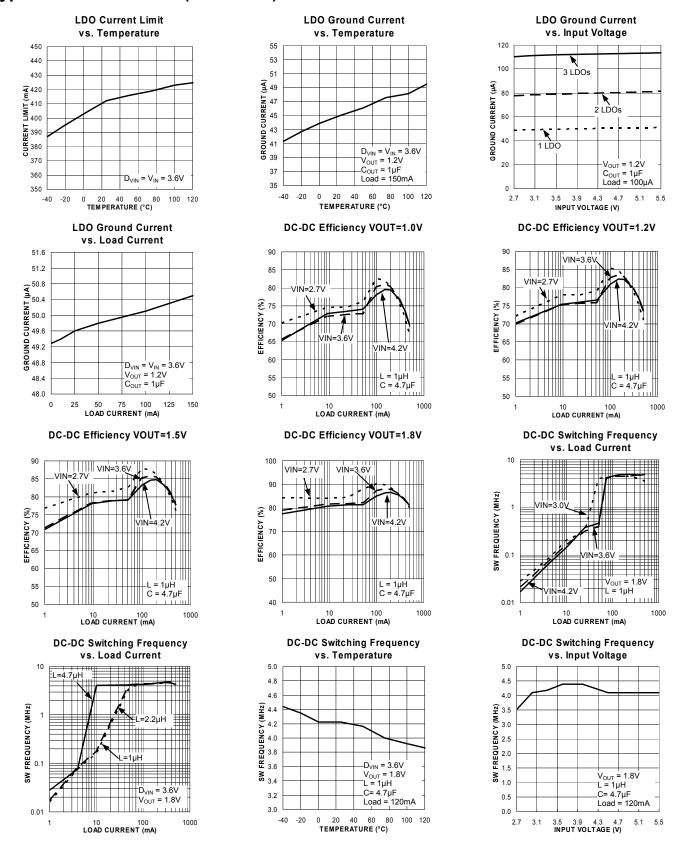

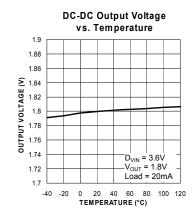

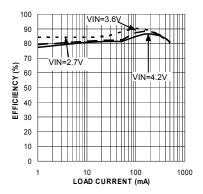

#### Efficiency VOUT=1.8V

The Figure above shows an efficiency curve. From no load to 100mA, efficiency losses are dominated by quiescent current losses, gate drive and transition losses. By using the HyperLight Load™ mode the MIC2826 is able to maintain high efficiency at low output currents.

Over 100mA, efficiency loss is dominated by MOSFET  $R_{\rm DSON}$  and inductor losses. Higher input supply voltages will increase the Gate-to-Source threshold on the internal MOSFETs, thereby reducing the internal  $R_{\rm DSON}$ . This improves efficiency by reducing DC losses in the device. All but the inductor losses are inherent to the device. In which case, inductor selection becomes increasingly critical in efficiency calculations. As the inductors are reduced in size, the DC resistance (DCR) can become quite significant. The DCR losses can be calculated as follows:

DCR Loss =

$$I_{OUT}^2 \times DCR$$

From that, the loss in efficiency due to inductor resistance can be calculated as follows:

$$Efficiency Loss = \left\lceil 1 - \left( \frac{V_{OUT} \times I_{OUT}}{V_{OUT} \times I_{OUT} + L\_P_D} \right) \right\rceil \times 100$$

Efficiency loss due to DCR is minimal at light loads and gains significance as the load is increased. Inductor selection becomes a trade-off between efficiency and size in this case.

#### HyperLight Load Mode™

The MIC2826 uses a minimum on and off time proprietary control loop (patented by Micrel). When the output voltage falls below the regulation threshold, the error comparator begins a switching cycle that turns the

PMOS on and keeps it on for the duration of the minimum-on-time. This increases the output voltage. If the output voltage is over the regulation threshold, then the error comparator turns the PMOS off for a minimumoff-time until the output drops below the threshold. The NMOS acts as an ideal rectifier that conducts when the PMOS is off. Using a NMOS switch instead of a diode allows for lower voltage drop across the switching device when it is on. The asynchronous switching combination between the PMOS and the NMOS allows the control loop to work in discontinuous mode for light load operations. In discontinuous mode, the MIC2826 works in pulse frequency modulation (PFM) to regulate the output. As the output current increases, the off-time decreases, thus providing more energy to the output. This switching scheme improves the efficiency of MIC2826 during light load currents by only switching when it is needed. As the load current increases, the MIC2826 goes into continuous conduction mode (CCM) and switches at a frequency centered at 4MHz. The equation to calculate the load when the MIC2826 goes into continuous conduction mode may be approximated by the following formula:

$$I_{LOAD} > \left(\frac{\left(V_{IN} - V_{OUT}\right) \times D}{2L \times f}\right)$$

As shown in the previous equation, the load at which MIC2826 transitions from HyperLight Load  $^{\rm TM}$  mode to PWM mode is a function of the input voltage (V<sub>IN</sub>), output voltage (V<sub>OUT</sub>), duty cycle (D), inductance (L) and frequency (f). This is illustrated in the graph below. Since the inductance range of MIC2826 is from 0.47µH to 4.7µH, the device may then be tailored to enter HyperLight Load  $^{\rm TM}$  mode or PWM mode at a specific load current by selecting the appropriate inductance. For example, in the graph below, when the inductance is 4.7µH the MIC2826 will transition into PWM mode at a load of approximately 5mA. Under the same condition, when the inductance is 1µH, the MIC2826 will transition into PWM mode at approximately 70mA.

## **Recommended Schematic**

## **Bill of Materials**

| Item                  | Part Number        | Manufacturer                | Description                                                                               | Qty. |  |

|-----------------------|--------------------|-----------------------------|-------------------------------------------------------------------------------------------|------|--|

| C1, C2, C3,<br>C4, C5 | GRM155R61A105KE15D | Murata <sup>(1)</sup>       | Capacitor, 1µF, 10V, X5R, 0402 size                                                       | - 5  |  |

|                       | C1005X5R0J105KT    | TDK <sup>(2)</sup>          | Capacitor, 1µF, 10V, X5R, 0402 size                                                       | 3    |  |

| C6, C7                | GRM188R60J475K     | Murata <sup>(1)</sup>       | Capacitor, 4.7µF, 6.3V, X5R, 0603 size                                                    | 2    |  |

|                       | C1608X5R0J475M     | TDK <sup>(2)</sup>          | Capacitor, 4.7µF, 6.3V, X5R, 0603 size                                                    |      |  |

| R1, R4                | CRCW040210K0FKEA   | Vishay <sup>(3)</sup>       | Resistor, 10kΩ, 1%, 1/16W, 0402 size                                                      | 2    |  |

| R2, R3                | CRCW04024K70FKEA   | Vishay <sup>(3)</sup>       | Resistor, 4.7kΩ, 1%, 1/16W, 0402 size                                                     | 2    |  |

| JP1                   | 0022152046         | Molex <sup>(4)</sup>        | Connector, 2.54mm (0.1") Pitch PCB Connector, 4 circuits                                  | 1    |  |

| L1                    | LQM21PN1R0MC0      | Murata <sup>(1))</sup>      | Inductor, 1.0µH, 0.8A, 2.0 x 1.25 x 0.5mm                                                 | 1    |  |

|                       | MLP2520S1R0L       | TDK <sup>(2)</sup>          | Inductor, 1.0µH, 1.5A, 2.5 x 2.0 x 1.0mm                                                  |      |  |

|                       | XPL2010-102ML      | Coilcraft <sup>(5</sup>     | Inductor, 1.0µH, 1.1A, 2.0 x 1.9 x 1.0mm                                                  |      |  |

|                       | CIG21W1R0MNE       | Samsung <sup>(6)</sup>      | Inductor, 1.0µH, 1.05A, 2.0 x 1.25 x 1.0mm                                                |      |  |

| U1                    | MIC2826-xxYMT      | Micrel, Inc. <sup>(7)</sup> | Quad Output PMIC with HyperLight Load™ DC-DC,<br>Three LDOs, and I <sup>2</sup> C Control | 1    |  |

#### Notes:

- 1. Murata Tel: www.murata.com.

- 2. TDK: www.tdk.com.

- 3. Vishay Tel: www.vishay.com.

- 4. Molex.: www.molex.com.

- 5. Coilcraft: www.coilcraft.com.

- 6. Samsung: www.sem.samsung.com.

- 7. Micrel, Inc.: www.micrel.com.

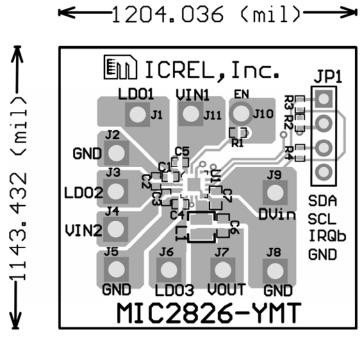

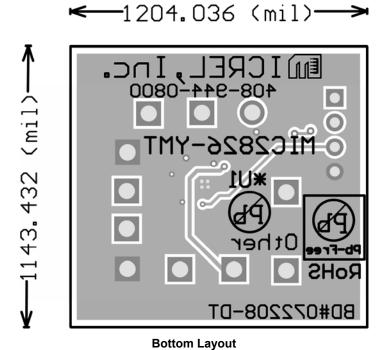

## **Recommended Layout**

**Top Layout**

July 2009 26 M9999-071609-A

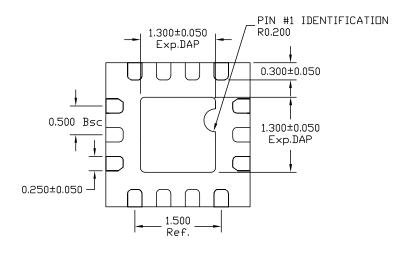

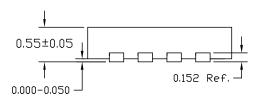

## **Package Information**

TOP VIEW

BOTTOM VIEW

NOTES :

- ALL DIMENSIONS ARE IN MILLIMETERS.

- MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

- PIN #1 ID ON TOP WILL BE LASER MARKED.

SIDE VIEW

14-Pin 2.5mm x 2.5mm Thin MLF® (MT)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2009 Micrel, Incorporated.